SystemVerilog——Axi4Lite_To_Localbus

摘要:用SystemVerilog对Axi4转localbus进行编写与仿真

如果需要从PS端对PL进行寄存器的读写操作,从znyq M_AXI_HPM_FPD出来,经过axi_interconnect 模块分出多个通道(不同的地址),经过一个axi_slave模块,再传到本地的寄存器内。

1. axi_slave

module jb_axi_slave #(parameter AXI_ADDR_WIDTH = 13,parameter AXI_DATA_WIDTH = 32) (input clk,input srst,jb_axi4_lite_if.slave IFP_axi4_lite,jb_axi_regs_if.master IFP_axi_rw

);localparam ADDR_LSB = (AXI_DATA_WIDTH/32) + 1;// AXI4LITE signalslogic [AXI_ADDR_WIDTH-1 : 0] axi_awaddr ='h0 ;logic axi_awready ='h0 ;logic axi_wready ='h0 ;logic [1 : 0] axi_bresp ='h0 ;logic axi_bvalid ='h0 ;logic [AXI_ADDR_WIDTH-1 : 0] axi_araddr ='h0 ;logic axi_arready ='h0 ;logic [AXI_DATA_WIDTH-1 : 0] axi_rdata ='h0 ;logic [1 : 0] axi_rresp ='h0 ;logic axi_rvalid ='h0 ;logic [AXI_DATA_WIDTH-1 : 0] reg_data_out ;logic aw_en = 'h0;// I/O Connections assignmentsassign IFP_axi4_lite.awready = axi_awready;assign IFP_axi4_lite.wready = axi_wready;assign IFP_axi4_lite.bresp = axi_bresp;assign IFP_axi4_lite.bvalid = axi_bvalid;assign IFP_axi4_lite.arready = axi_arready;assign IFP_axi4_lite.rdata = axi_rdata;assign IFP_axi4_lite.rresp = axi_rresp;assign IFP_axi4_lite.rvalid = axi_rvalid;// Assert axi_awready when awvalid & wvalid is highalways @( posedge clk ) beginif ( srst == 1'b1 ) beginaxi_awready <= 1'b0;aw_en <= 1'b1;end else begin if (~axi_awready && IFP_axi4_lite.awvalid && IFP_axi4_lite.wvalid && aw_en) begin// Assumption no outstanding transactionaxi_awready <= 1'b1;aw_en <= 1'b0;endelse if ( IFP_axi4_lite.bready && axi_bvalid) beginaw_en <= 1'b1;axi_awready <= 1'b0;endelse beginaxi_awready <= 1'b0;endend end //Latch the address based on validalways @( posedge clk ) beginif ( srst == 1'b1 ) beginaxi_awaddr <= 0;end else begin if (~axi_awready && IFP_axi4_lite.awvalid && IFP_axi4_lite.wvalid && aw_en) begin// Write Address latching axi_awaddr <= IFP_axi4_lite.awaddr;endend end //Assert wreaddy for a clock cycle when awvalid and wvalid is asserted aw_en is setalways @( posedge clk ) beginif ( srst == 1'b1 ) beginaxi_wready <= 1'b0;end else begin if (~axi_wready && IFP_axi4_lite.awvalid && IFP_axi4_lite.wvalid && aw_en ) begin// axi_wready <= 1'b1;endelse beginaxi_wready <= 1'b0;endend end assign IFP_axi_rw.wren = axi_wready && IFP_axi4_lite.awvalid && IFP_axi4_lite.wvalid && axi_awready;//BVALID AND BRESP SETTINGSalways @( posedge clk ) begin if ( srst == 1'b1 ) beginaxi_bvalid <= 0;axi_bresp <= 2'b0;end else begin if (axi_awready && IFP_axi4_lite.awvalid && ~axi_bvalid && axi_wready && IFP_axi4_lite.wvalid) begin// indicates a valid write response is availableaxi_bvalid <= 1'b1;axi_bresp <= 2'b0; // 'OKAY' response end // work error responses in futureelse beginif (IFP_axi4_lite.bready && axi_bvalid) begin //check if bready is asserted while bvalid is high) //(there is a possibility that bready is always asserted high)axi_bvalid <= 1'b0; end endendend // READ LOGIC /always @( posedge clk ) begin if ( srst == 1'b1 ) beginaxi_arready <= 1'b0;axi_araddr <= 32'b0;end else begin if (~axi_arready && IFP_axi4_lite.arvalid) begin// indicates that the slave has acceped the valid read addressaxi_arready <= 1'b1;// Latch Read addressaxi_araddr <= IFP_axi4_lite.araddr;endelse beginaxi_arready <= 1'b0;endend end //Latch the address based on validalways @( posedge clk ) beginif ( srst == 1'b1 ) beginaxi_rvalid <= 0;axi_rresp <= 0;end else begin if (axi_arready && IFP_axi4_lite.arvalid && ~axi_rvalid) begin// Valid read data is available at the read data busaxi_rvalid <= 1'b1;axi_rresp <= 2'b0; // 'OKAY' responseend else if (axi_rvalid && IFP_axi4_lite.rready) begin// Read data is accepted by the masteraxi_rvalid <= 1'b0;end endend assign IFP_axi_rw.rden = axi_arready & IFP_axi4_lite.arvalid & ~axi_rvalid; // Output register or memory read data//Latch the address based on validalways @( posedge clk ) beginif ( srst == 1'b1 ) beginaxi_rdata <= 0;end else begin if (IFP_axi_rw.rden) beginaxi_rdata <= reg_data_out; // register read dataend endend assign reg_data_out = IFP_axi_rw.rdata; ///WRITE LOGIC assign IFP_axi_rw.wr_offset = axi_awaddr[AXI_ADDR_WIDTH-1:ADDR_LSB];

// assign IFP_axi_rw.wr_offset = axi_awaddr;///READ LOGIC assign IFP_axi_rw.rd_offset = axi_araddr[AXI_ADDR_WIDTH-1:ADDR_LSB];

// assign IFP_axi_rw.rd_offset = axi_araddr;assign IFP_axi_rw.wdata = IFP_axi4_lite.wdata;endmodule这段代码的核心就是对axi_lite进行握手操作,同时得到:

IFP_axi_rw.rden、IFP_axi_rw.rdata、IFP_axi_rw.wren、IFP_axi_rw.wdata、IFP_axi_rw.wr_offset、IFP_axi_rw.rd_offset

用这些信号将数据送入寄存器中或者从寄存器中读出数据。

2. regs

module jb_helpchip_regs ( input clk, input srst, jb_axi_regs_if.slave IFP_axi_rw, jb_helpchip_ctrl_if.ctrl IFP_helpchip_ctrl

);`include "jb_db_HC_params.svh"Register Field Declarations//logic [15:0] HC_VERSION_REGISTER_hc_revision_num;// Revision numberlogic [7:0] HC_VERSION_REGISTER_hc_minor_version;// minor versionlogic [7:0] HC_VERSION_REGISTER_hc_major_version;// major versionlogic [31:0] HC_DEBUG_REVISION_hc_debug_revision;// Debug build version. Should be 0 for official builds. logic [31:0] HC_DEBUG_RW_0_hc_debug_rw_0;// debug ethernet loopbacklogic [31:0] HC_DEBUG_RW_1_hc_debug_rw_1;// debug ethernet restart_tx_rxlogic [31:0] HC_DEBUG_RW_2_hc_debug_rw_2;// debug ethernet sys_resetlogic [31:0] HC_DEBUG_RW_3_hc_debug_rw_3;// logic [31:0] HC_DEBUG_RW_4_hc_debug_rw_4;// logic [31:0] HC_DEBUG_RW_5_hc_debug_rw_5;// logic [31:0] HC_DEBUG_RW_6_hc_debug_rw_6;// logic [31:0] HC_DEBUG_RW_7_hc_debug_rw_7;// logic [31:0] HC_DEBUG_RW_8_hc_debug_rw_8;// logic [31:0] HC_DEBUG_RW_9_hc_debug_rw_9;// logic [31:0] HC_DEBUG_RW_10_hc_debug_rw_10;// logic [31:0] HC_DEBUG_RW_11_hc_debug_rw_11;// logic [31:0] HC_DEBUG_RW_12_hc_debug_rw_12;// logic [31:0] HC_DEBUG_RW_13_hc_debug_rw_13;// logic [31:0] HC_DEBUG_RW_14_hc_debug_rw_14;// logic [31:0] HC_DEBUG_RW_15_hc_debug_rw_15;// logic [31:0] HC_DEBUG_RW_16_hc_debug_rw_16;// logic [31:0] HC_DEBUG_RW_17_hc_debug_rw_17;// logic [31:0] HC_DEBUG_RW_18_hc_debug_rw_18;// logic [31:0] HC_DEBUG_RW_19_hc_debug_rw_19;// logic [31:0] HC_DEBUG_RW_20_hc_debug_rw_20;// logic [31:0] HC_DEBUG_RW_21_hc_debug_rw_21;// logic [31:0] HC_DEBUG_RW_22_hc_debug_rw_22;// logic [31:0] HC_DEBUG_RW_23_hc_debug_rw_23;// logic [31:0] HC_DEBUG_RW_24_hc_debug_rw_24;// logic [31:0] HC_DEBUG_RW_25_hc_debug_rw_25;// logic [31:0] HC_DEBUG_RW_26_hc_debug_rw_26;// logic [31:0] HC_DEBUG_RW_27_hc_debug_rw_27;// logic [31:0] HC_DEBUG_RW_28_hc_debug_rw_28;// logic [31:0] HC_DEBUG_RW_29_hc_debug_rw_29;// logic [31:0] HC_DEBUG_RW_30_hc_debug_rw_30;// logic [31:0] HC_DBG_SCRATCH_hc_dbg_scratch;// ASSIGN PARAMETERS//assign HC_VERSION_REGISTER_hc_revision_num = HC_REVISION_NUM;assign HC_VERSION_REGISTER_hc_minor_version = HC_MINOR_VERSION;assign HC_VERSION_REGISTER_hc_major_version = HC_MAJOR_VERSION;assign HC_DEBUG_REVISION_hc_debug_revision = HC_DEBUG_REVISION;ASSIGN CONTROL RW INTF FIELDS//assign IFP_helpchip_ctrl.debug_rw[0] = HC_DEBUG_RW_0_hc_debug_rw_0;assign IFP_helpchip_ctrl.debug_rw[1] = HC_DEBUG_RW_1_hc_debug_rw_1;assign IFP_helpchip_ctrl.debug_rw[2] = HC_DEBUG_RW_2_hc_debug_rw_2;assign IFP_helpchip_ctrl.debug_rw[3] = HC_DEBUG_RW_3_hc_debug_rw_3;assign IFP_helpchip_ctrl.debug_rw[4] = HC_DEBUG_RW_4_hc_debug_rw_4;assign IFP_helpchip_ctrl.debug_rw[5] = HC_DEBUG_RW_5_hc_debug_rw_5;assign IFP_helpchip_ctrl.debug_rw[6] = HC_DEBUG_RW_6_hc_debug_rw_6;assign IFP_helpchip_ctrl.debug_rw[7] = HC_DEBUG_RW_7_hc_debug_rw_7;assign IFP_helpchip_ctrl.debug_rw[8] = HC_DEBUG_RW_8_hc_debug_rw_8;assign IFP_helpchip_ctrl.debug_rw[9] = HC_DEBUG_RW_9_hc_debug_rw_9;assign IFP_helpchip_ctrl.debug_rw[10] = HC_DEBUG_RW_10_hc_debug_rw_10;assign IFP_helpchip_ctrl.debug_rw[11] = HC_DEBUG_RW_11_hc_debug_rw_11;assign IFP_helpchip_ctrl.debug_rw[12] = HC_DEBUG_RW_12_hc_debug_rw_12;assign IFP_helpchip_ctrl.debug_rw[13] = HC_DEBUG_RW_13_hc_debug_rw_13;assign IFP_helpchip_ctrl.debug_rw[14] = HC_DEBUG_RW_14_hc_debug_rw_14;assign IFP_helpchip_ctrl.debug_rw[15] = HC_DEBUG_RW_15_hc_debug_rw_15;assign IFP_helpchip_ctrl.debug_rw[16] = HC_DEBUG_RW_16_hc_debug_rw_16;assign IFP_helpchip_ctrl.debug_rw[17] = HC_DEBUG_RW_17_hc_debug_rw_17;assign IFP_helpchip_ctrl.debug_rw[18] = HC_DEBUG_RW_18_hc_debug_rw_18;assign IFP_helpchip_ctrl.debug_rw[19] = HC_DEBUG_RW_19_hc_debug_rw_19;assign IFP_helpchip_ctrl.debug_rw[20] = HC_DEBUG_RW_20_hc_debug_rw_20;assign IFP_helpchip_ctrl.debug_rw[21] = HC_DEBUG_RW_21_hc_debug_rw_21;assign IFP_helpchip_ctrl.debug_rw[22] = HC_DEBUG_RW_22_hc_debug_rw_22;assign IFP_helpchip_ctrl.debug_rw[23] = HC_DEBUG_RW_23_hc_debug_rw_23;assign IFP_helpchip_ctrl.debug_rw[24] = HC_DEBUG_RW_24_hc_debug_rw_24;assign IFP_helpchip_ctrl.debug_rw[25] = HC_DEBUG_RW_25_hc_debug_rw_25;assign IFP_helpchip_ctrl.debug_rw[26] = HC_DEBUG_RW_26_hc_debug_rw_26;assign IFP_helpchip_ctrl.debug_rw[27] = HC_DEBUG_RW_27_hc_debug_rw_27;assign IFP_helpchip_ctrl.debug_rw[28] = HC_DEBUG_RW_28_hc_debug_rw_28;assign IFP_helpchip_ctrl.debug_rw[29] = HC_DEBUG_RW_29_hc_debug_rw_29;assign IFP_helpchip_ctrl.debug_rw[30] = HC_DEBUG_RW_30_hc_debug_rw_30;ASSIGN STATUS RO INTF FIELDS/////WRITE LOGIC always @(posedge clk) beginif (srst) beginHC_DEBUG_RW_0_hc_debug_rw_0 <= 'h0; // debug ethernet loopbackHC_DEBUG_RW_1_hc_debug_rw_1 <= 'h1; // debug ethernet restart_tx_rxHC_DEBUG_RW_2_hc_debug_rw_2 <= 'h1; // debug ethernet sys_resetHC_DEBUG_RW_3_hc_debug_rw_3 <= 'h0; // HC_DEBUG_RW_4_hc_debug_rw_4 <= 'h0; // HC_DEBUG_RW_5_hc_debug_rw_5 <= 'h0; // HC_DEBUG_RW_6_hc_debug_rw_6 <= 'h0; // HC_DEBUG_RW_7_hc_debug_rw_7 <= 'h0; // HC_DEBUG_RW_8_hc_debug_rw_8 <= 'h0; // HC_DEBUG_RW_9_hc_debug_rw_9 <= 'h0; // HC_DEBUG_RW_10_hc_debug_rw_10 <= 'h0; // HC_DEBUG_RW_11_hc_debug_rw_11 <= 'h0; // HC_DEBUG_RW_12_hc_debug_rw_12 <= 'h0; // HC_DEBUG_RW_13_hc_debug_rw_13 <= 'h0; // HC_DEBUG_RW_14_hc_debug_rw_14 <= 'h0; // HC_DEBUG_RW_15_hc_debug_rw_15 <= 'h0; // HC_DEBUG_RW_16_hc_debug_rw_16 <= 'h0; // HC_DEBUG_RW_17_hc_debug_rw_17 <= 'h0; // HC_DEBUG_RW_18_hc_debug_rw_18 <= 'h0; // HC_DEBUG_RW_19_hc_debug_rw_19 <= 'h0; // HC_DEBUG_RW_20_hc_debug_rw_20 <= 'h0; // HC_DEBUG_RW_21_hc_debug_rw_21 <= 'h0; // HC_DEBUG_RW_22_hc_debug_rw_22 <= 'h0; // HC_DEBUG_RW_23_hc_debug_rw_23 <= 'h0; // HC_DEBUG_RW_24_hc_debug_rw_24 <= 'h0; // HC_DEBUG_RW_25_hc_debug_rw_25 <= 'h0; // HC_DEBUG_RW_26_hc_debug_rw_26 <= 'h0; // HC_DEBUG_RW_27_hc_debug_rw_27 <= 'h0; // HC_DEBUG_RW_28_hc_debug_rw_28 <= 'h0; // HC_DEBUG_RW_29_hc_debug_rw_29 <= 'h0; // HC_DEBUG_RW_30_hc_debug_rw_30 <= 'h0; // HC_DBG_SCRATCH_hc_dbg_scratch <= 'h3333_cccc; // endelse if (IFP_axi_rw.wren) begincase(IFP_axi_rw.wr_offset)15'h7c0 : begin //'h1F00HC_DEBUG_RW_0_hc_debug_rw_0 <= IFP_axi_rw.wdata[31:0]; // debug ethernet loopbackend15'h7c1 : begin //'h1F04HC_DEBUG_RW_1_hc_debug_rw_1 <= IFP_axi_rw.wdata[31:0]; // debug ethernet restart_tx_rxend15'h7c2 : begin //'h1F08HC_DEBUG_RW_2_hc_debug_rw_2 <= IFP_axi_rw.wdata[31:0]; // debug ethernet sys_resetend15'h7c3 : begin //'h1F0CHC_DEBUG_RW_3_hc_debug_rw_3 <= IFP_axi_rw.wdata[31:0]; // end11'h7c4 : begin //'h1F10HC_DEBUG_RW_4_hc_debug_rw_4 <= IFP_axi_rw.wdata[31:0]; // end11'h7c5 : begin //'h1F14HC_DEBUG_RW_5_hc_debug_rw_5 <= IFP_axi_rw.wdata[31:0]; // end11'h7c6 : begin //'h1F18HC_DEBUG_RW_6_hc_debug_rw_6 <= IFP_axi_rw.wdata[31:0]; // end11'h7c7 : begin //'h1F1CHC_DEBUG_RW_7_hc_debug_rw_7 <= IFP_axi_rw.wdata[31:0]; // end11'h7c8 : begin //'h1F20HC_DEBUG_RW_8_hc_debug_rw_8 <= IFP_axi_rw.wdata[31:0]; // end11'h7c9 : begin //'h1F24HC_DEBUG_RW_9_hc_debug_rw_9 <= IFP_axi_rw.wdata[31:0]; // end11'h7ca : begin //'h1F28HC_DEBUG_RW_10_hc_debug_rw_10 <= IFP_axi_rw.wdata[31:0]; // end11'h7cb : begin //'h1F2CHC_DEBUG_RW_11_hc_debug_rw_11 <= IFP_axi_rw.wdata[31:0]; // end11'h7cc : begin //'h1F30HC_DEBUG_RW_12_hc_debug_rw_12 <= IFP_axi_rw.wdata[31:0]; // end11'h7cd : begin //'h1F34HC_DEBUG_RW_13_hc_debug_rw_13 <= IFP_axi_rw.wdata[31:0]; // end11'h7ce : begin //'h1F38HC_DEBUG_RW_14_hc_debug_rw_14 <= IFP_axi_rw.wdata[31:0]; // end11'h7cf : begin //'h1F3CHC_DEBUG_RW_15_hc_debug_rw_15 <= IFP_axi_rw.wdata[31:0]; // end11'h7d0 : begin //'h1F40HC_DEBUG_RW_16_hc_debug_rw_16 <= IFP_axi_rw.wdata[31:0]; // end11'h7d1 : begin //'h1F44HC_DEBUG_RW_17_hc_debug_rw_17 <= IFP_axi_rw.wdata[31:0]; // end11'h7d2 : begin //'h1F48HC_DEBUG_RW_18_hc_debug_rw_18 <= IFP_axi_rw.wdata[31:0]; // end11'h7d3 : begin //'h1F4CHC_DEBUG_RW_19_hc_debug_rw_19 <= IFP_axi_rw.wdata[31:0]; // end11'h7d4 : begin //'h1F50HC_DEBUG_RW_20_hc_debug_rw_20 <= IFP_axi_rw.wdata[31:0]; // end11'h7d5 : begin //'h1F54HC_DEBUG_RW_21_hc_debug_rw_21 <= IFP_axi_rw.wdata[31:0]; // end11'h7d6 : begin //'h1F58HC_DEBUG_RW_22_hc_debug_rw_22 <= IFP_axi_rw.wdata[31:0]; // end11'h7d7 : begin //'h1F5CHC_DEBUG_RW_23_hc_debug_rw_23 <= IFP_axi_rw.wdata[31:0]; // end11'h7d8 : begin //'h1F60HC_DEBUG_RW_24_hc_debug_rw_24 <= IFP_axi_rw.wdata[31:0]; // end11'h7d9 : begin //'h1F64HC_DEBUG_RW_25_hc_debug_rw_25 <= IFP_axi_rw.wdata[31:0]; // end11'h7da : begin //'h1F68HC_DEBUG_RW_26_hc_debug_rw_26 <= IFP_axi_rw.wdata[31:0]; // end11'h7db : begin //'h1F6CHC_DEBUG_RW_27_hc_debug_rw_27 <= IFP_axi_rw.wdata[31:0]; // end11'h7dc : begin //'h1F70HC_DEBUG_RW_28_hc_debug_rw_28 <= IFP_axi_rw.wdata[31:0]; // end11'h7dd : begin //'h1F74HC_DEBUG_RW_29_hc_debug_rw_29 <= IFP_axi_rw.wdata[31:0]; // end11'h7de : begin //'h1F78HC_DEBUG_RW_30_hc_debug_rw_30 <= IFP_axi_rw.wdata[31:0]; // end11'h7ff : begin //'h1FFCHC_DBG_SCRATCH_hc_dbg_scratch <= IFP_axi_rw.wdata[31:0]; // endendcaseendend

//////READ LOGIC always @(*) beginIFP_axi_rw.rdata = 0;if (IFP_axi_rw.rden) begincase(IFP_axi_rw.rd_offset)15'h0 : begin//'h0IFP_axi_rw.rdata[15:0] = HC_VERSION_REGISTER_hc_revision_num; // Revision numberIFP_axi_rw.rdata[23:16] = HC_VERSION_REGISTER_hc_minor_version; // minor versionIFP_axi_rw.rdata[31:24] = HC_VERSION_REGISTER_hc_major_version; // major versionend15'h1 : begin//'h4IFP_axi_rw.rdata[31:0] = HC_DEBUG_REVISION_hc_debug_revision; // Debug build version. Should be 0 for official builds. end15'h7c0 : begin//'h1F00IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_0_hc_debug_rw_0; // debug ethernet loopbackend15'h7c1 : begin//'h1F04IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_1_hc_debug_rw_1; // debug ethernet restart_tx_rxend15'h7c2 : begin//'h1F08IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_2_hc_debug_rw_2; // debug ethernet sys_resetend11'h7c3 : begin//'h1F0CIFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_3_hc_debug_rw_3; // end11'h7c4 : begin//'h1F10IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_4_hc_debug_rw_4; // end11'h7c5 : begin//'h1F14IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_5_hc_debug_rw_5; // end11'h7c6 : begin//'h1F18IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_6_hc_debug_rw_6; // end11'h7c7 : begin//'h1F1CIFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_7_hc_debug_rw_7; // end11'h7c8 : begin//'h1F20IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_8_hc_debug_rw_8; // end11'h7c9 : begin//'h1F24IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_9_hc_debug_rw_9; // end11'h7ca : begin//'h1F28IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_10_hc_debug_rw_10; // end11'h7cb : begin//'h1F2CIFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_11_hc_debug_rw_11; // end11'h7cc : begin//'h1F30IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_12_hc_debug_rw_12; // end11'h7cd : begin//'h1F34IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_13_hc_debug_rw_13; // end11'h7ce : begin//'h1F38IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_14_hc_debug_rw_14; // end11'h7cf : begin//'h1F3CIFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_15_hc_debug_rw_15; // end11'h7d0 : begin//'h1F40IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_16_hc_debug_rw_16; // end11'h7d1 : begin//'h1F44IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_17_hc_debug_rw_17; // end11'h7d2 : begin//'h1F48IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_18_hc_debug_rw_18; // end11'h7d3 : begin//'h1F4CIFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_19_hc_debug_rw_19; // end11'h7d4 : begin//'h1F50IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_20_hc_debug_rw_20; // end11'h7d5 : begin//'h1F54IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_21_hc_debug_rw_21; // end11'h7d6 : begin//'h1F58IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_22_hc_debug_rw_22; // end11'h7d7 : begin//'h1F5CIFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_23_hc_debug_rw_23; // end11'h7d8 : begin//'h1F60IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_24_hc_debug_rw_24; // end11'h7d9 : begin//'h1F64IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_25_hc_debug_rw_25; // end11'h7da : begin//'h1F68IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_26_hc_debug_rw_26; // end11'h7db : begin//'h1F6CIFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_27_hc_debug_rw_27; // end11'h7dc : begin//'h1F70IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_28_hc_debug_rw_28; // end11'h7dd : begin//'h1F74IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_29_hc_debug_rw_29; // end11'h7de : begin//'h1F78IFP_axi_rw.rdata[31:0] = HC_DEBUG_RW_30_hc_debug_rw_30; // end11'h7ff : begin//'h1FFCIFP_axi_rw.rdata[31:0] = HC_DBG_SCRATCH_hc_dbg_scratch; // endendcaseendend

///endmodule///利用wren和ren对寄存器进行读写操作。

3.仿真

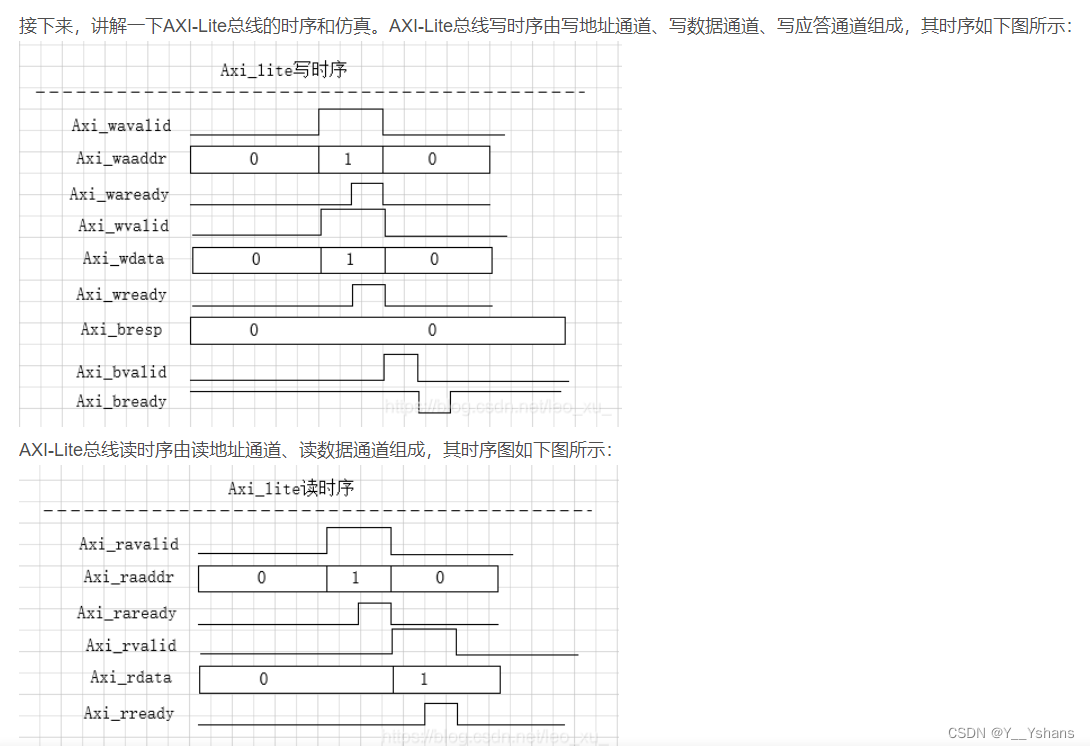

我的task时序是按照这张图来的,除开response返回值

`timescale 1ns / 1ps

//

//

// Create Date: 02/16/2023 09:43:30 AM

// Design Name: Jade

// Module Name: tb_top_ctrl_helpchip

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module tb_top_ctrl_helpchip();typedef struct packed{logic [31:0] awaddr;logic awvalid;logic awready;logic [31:0] wdata;logic [3:0] wstrb;logic wvalid;logic wready;logic [1:0] bresp;logic bvalid;logic bready;logic [31:0] araddr;logic arvalid;logic arready;logic [31:0] rdata;logic [1:0] rresp;logic rvalid;logic rready;} axi4_lite_t;logic ptp_clk ;

logic ptp_reset ;logic clk ; //491.52MHz 2.017

logic reset ;

axi4_lite_t axi4_lite = 0;always #1 ptp_clk = ~ptp_clk;

always #1.017 clk = ~clk;jb_axi4_lite_if #(.ADDR_WIDTH(16), .DATA_WIDTH(32)) IFP_axi_lite_helpchip_out();jb_helpchip_ctrl_if IFP_helpchip_ctrl();jb_top_ctrl_helpchip #(.AXI_ADDR_WIDTH (16),.AXI_DATA_WIDTH (32))u_jb_top_ctrl_helpchip(.clk (clk),.srst (reset),.IFP_axi4_lite (IFP_axi_lite_helpchip_out),.IFP_helpchip_ctrl (IFP_helpchip_ctrl)

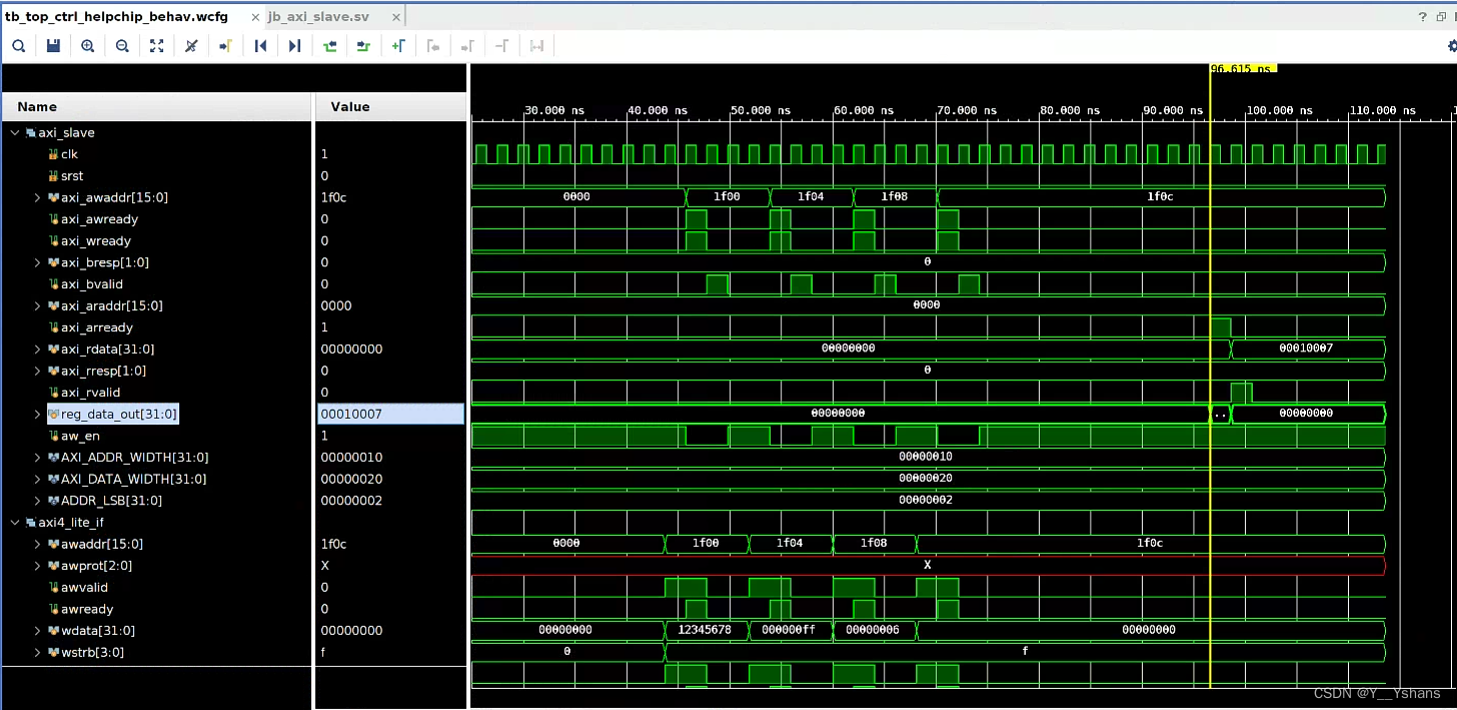

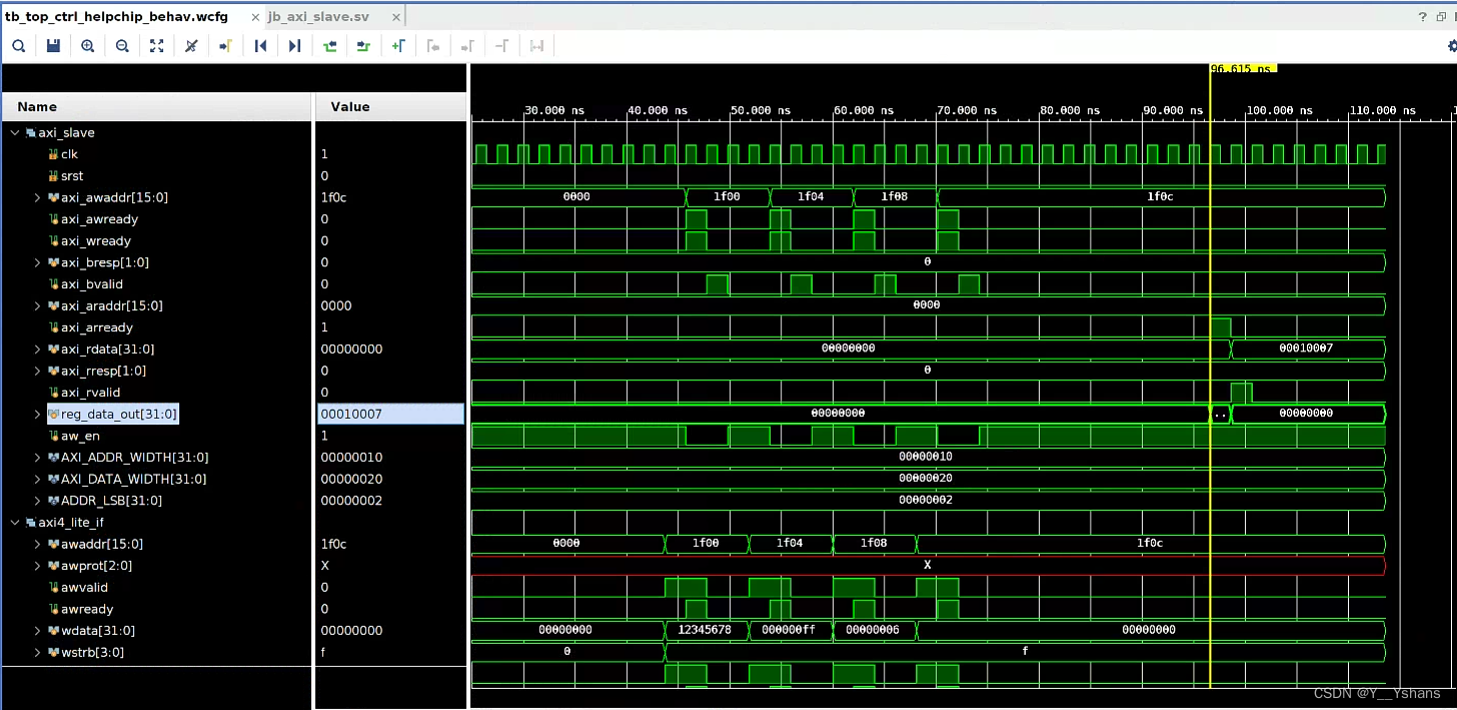

);initial beginptp_clk <= 0;ptp_reset <= 1;clk <= 0;reset <= 1;/* ----------------------------------------------- */ #20ptp_reset <= 0;reset <= 0;#20;axi4_write(32'hA0291F00, 32'h12345678);axi4_write(32'hA0291F04, 32'hFF);axi4_write(32'hA0291F08, 32'h6);axi4_write(32'hA0291F0C, 32'h0);#20axi4_read(32'hA0290000);//axi4_read(32'hA0291F00);//axi4_read(32'hA0291F04);//axi4_read(32'hA0291F08);//axi4_read(32'hA0291F0C);#15 $stop;

endalways @ (posedge clk) beginif(reset) beginIFP_axi_lite_helpchip_out.awaddr <= 'h0;IFP_axi_lite_helpchip_out.awvalid <= 'h0;IFP_axi_lite_helpchip_out.awready <= 'h0;IFP_axi_lite_helpchip_out.wdata <= 'h0;IFP_axi_lite_helpchip_out.wstrb <= 'h0;IFP_axi_lite_helpchip_out.wvalid <= 'h0;IFP_axi_lite_helpchip_out.wready <= 'h0;IFP_axi_lite_helpchip_out.bresp <= 'h0;IFP_axi_lite_helpchip_out.bvalid <= 'h0;IFP_axi_lite_helpchip_out.bready <= 'h0;IFP_axi_lite_helpchip_out.araddr <= 'h0;IFP_axi_lite_helpchip_out.arvalid <= 'h0;IFP_axi_lite_helpchip_out.arready <= 'h0;IFP_axi_lite_helpchip_out.rdata <= 'h0;IFP_axi_lite_helpchip_out.rresp <= 'h0;IFP_axi_lite_helpchip_out.rvalid <= 'h0;IFP_axi_lite_helpchip_out.rready <= 'h0;endelse beginIFP_axi_lite_helpchip_out.awaddr <= axi4_lite.awaddr ;IFP_axi_lite_helpchip_out.awvalid <= axi4_lite.awvalid;IFP_axi_lite_helpchip_out.awready <= axi4_lite.awready;IFP_axi_lite_helpchip_out.wdata <= axi4_lite.wdata ;IFP_axi_lite_helpchip_out.wstrb <= axi4_lite.wstrb ;IFP_axi_lite_helpchip_out.wvalid <= axi4_lite.wvalid ;IFP_axi_lite_helpchip_out.wready <= axi4_lite.wready ;IFP_axi_lite_helpchip_out.bresp <= axi4_lite.bresp ;IFP_axi_lite_helpchip_out.bvalid <= axi4_lite.bvalid ;IFP_axi_lite_helpchip_out.bready <= axi4_lite.bready ;IFP_axi_lite_helpchip_out.araddr <= axi4_lite.araddr ;IFP_axi_lite_helpchip_out.arvalid <= axi4_lite.arvalid;IFP_axi_lite_helpchip_out.arready <= axi4_lite.arready;IFP_axi_lite_helpchip_out.rdata <= axi4_lite.rdata ;IFP_axi_lite_helpchip_out.rresp <= axi4_lite.rresp ;IFP_axi_lite_helpchip_out.rvalid <= axi4_lite.rvalid ;IFP_axi_lite_helpchip_out.rready <= axi4_lite.rready ;end

endtask automatic axi4_read(int addr);beginaxi4_lite.rready <= 1'd0;@(posedge clk);axi4_lite.araddr <= addr[31:0];axi4_lite.arvalid <= 1'd1;@(posedge clk);@(posedge clk);while (axi4_lite.arready)@(posedge clk);axi4_lite.arvalid <= 1'd0;while(axi4_lite.rvalid)@(posedge clk);axi4_lite.rready <= 1'd1;if (axi4_lite.rresp == 2'd0)$display("Read ok, Raddr - %x, Rdata - %x", axi4_lite.araddr, axi4_lite.rdata);else$display("Read failed, Raddr - %x, Rresp - %x", axi4_lite.araddr, axi4_lite.rresp);@(posedge clk);axi4_lite.rready <= 1'd0;endendtasktask automatic axi4_write(int addr, data);beginaxi4_lite.bready <= 1'd0;@(posedge clk);axi4_lite.awaddr <= addr[31:0];axi4_lite.awvalid <= 1'd1;axi4_lite.wdata <= data[31:0];axi4_lite.wvalid <= 1'd1;axi4_lite.wstrb <= 4'd15;@(posedge clk);while (axi4_lite.awready)@(posedge clk);@(posedge clk);axi4_lite.awvalid <= 1'd0;while (axi4_lite.wready)@(posedge clk);axi4_lite.wvalid <= 1'd0;while (axi4_lite.bvalid)@(posedge clk);axi4_lite.bready <= 1'd1;@(posedge clk);axi4_lite.bready <= 1'd0;if (axi4_lite.bresp != 2'b00)$display("Write failure...%d", axi4_lite.bresp);endendtaskendmodule

熟悉了一下systemverilog的一些用法,以及systemverilog写测试激励。

总结

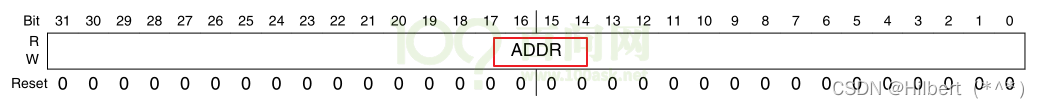

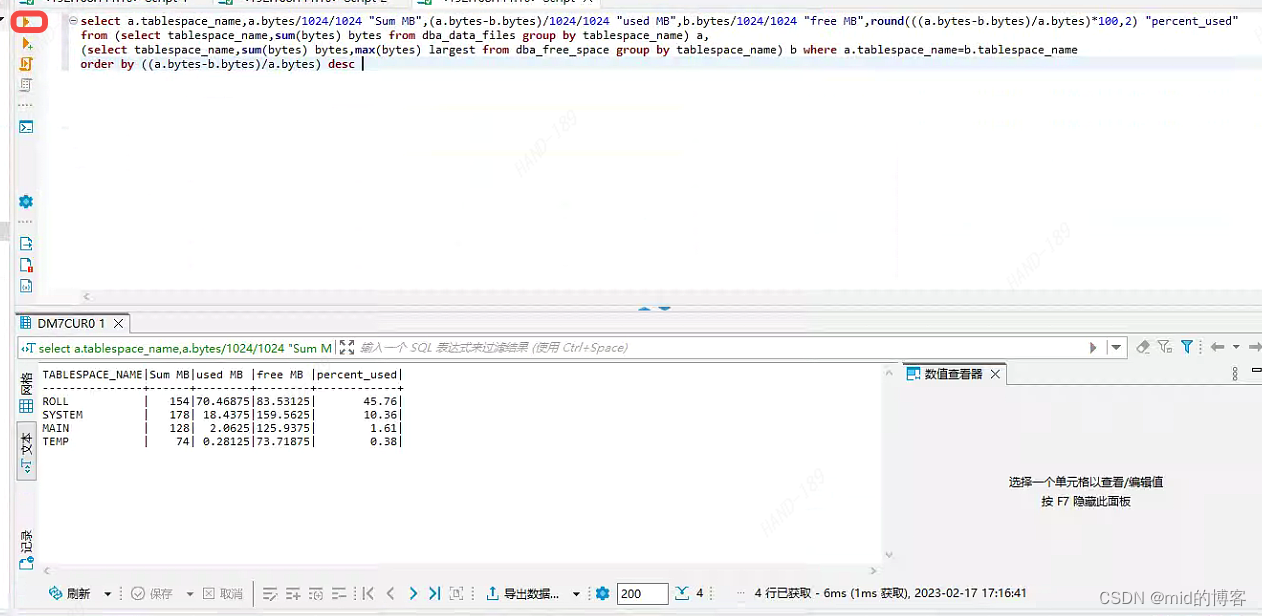

当时需要从zu67传一个128k(0xA0280000、0xA0290000)的地址到ku3p,但是这个代码里面需要修改两处,才能保证一切正确:

需要非常注意偏移地址

///WRITE LOGIC

assign IFP_axi_rw.wr_offset = axi_awaddr[AXI_ADDR_WIDTH-2:ADDR_LSB];

///READ LOGIC

assign IFP_axi_rw.rd_offset = axi_araddr[AXI_ADDR_WIDTH-2:ADDR_LSB];

把parameter AXI_ADDR_WIDTH改成17就可以了

工程代码:

https://download.csdn.net/download/Y__Yshans/87454767

参考文章:

AXI总线之AXI-LITE总线分析与实现_bibogo的博客-CSDN博客_axi-lite

相关文章:

SystemVerilog——Axi4Lite_To_Localbus

摘要:用SystemVerilog对Axi4转localbus进行编写与仿真 如果需要从PS端对PL进行寄存器的读写操作,从znyq M_AXI_HPM_FPD出来,经过axi_interconnect 模块分出多个通道(不同的地址),经过一个axi_slave模块&am…...

硬件_IMX6ULL的LCD控制器

硬件_IMX6ULL的LCD控制器 文章目录硬件_IMX6ULL的LCD控制器一、 LCD控制器模块介绍1.1 硬件框图1.2 数据传输与处理1.3 时序控制二、 LCD控制器寄存器简介2.1 LCDIF_CTRL寄存器2.2 LCDIF_CTRL1寄存器2.3 LCDIF_TRANSFER_COUNT寄存器2.4 LCDIF_VDCTRL0寄存器2.5 LCDIF_VDCTRL1寄…...

ICLR 2022—你不应该错过的 10 篇论文(下)

CV - 计算机视觉 | ML - 机器学习 | RL - 强化学习 | NLP 自然语言处理 ICLR 2023已经放榜,但是今天我们先来回顾一下去年的ICLR 2022! ICLR 2022将于2022年 4 月 25 日星期一至 4 月 29 日星期五在线举行(连续第三年!&#x…...

国内外优秀程序员的私域博客大全

文章目录 国内外优秀程序员的私域博客大全**国内的优秀程序员****国外的优秀程序员**结语国内外优秀程序员的私域博客大全 国内的优秀程序员 1、风雪之隅-惠新宸 擅长领域:PHP、PECL等 Laruance惠新宸——国内最有影响力的PHP技术专家,PHP开发组核心成员, Zend顾问, PHP7及…...

【C++ Primer Plus】第六章:分支语句和逻辑运算符

文章目录第六章 分支语句和逻辑运算符6.1 字符函数库cctype6.2 ?:运算符6.3 读取数字的输入6.4 cin的处理过程char类型intdoublechar数组使用char数组来存储输入6.5 写入到文本文件中6.6 读取文本文件6.7 总结第六章 分支语句和逻辑运算符 6.1 字符函数库cctype C从C语言继承…...

堡垒机的主要功能是什么?为什么需要堡垒机?

堡垒机是一种用于管理和控制服务器的工具,其主要功能是为管理人员提供安全、便捷的远程管理和操作方式。为什么需要堡垒机呢?下面我们将详细阐述堡垒机的主要功能和必要性。 一、堡垒机的主要功能: ①、用户认证和授权管理:堡垒机…...

记录spring中Transactional事务注解失效的六个场景

记录spring中Transactional事务注解失效的六个场景 方法内的自调用 原因:通过this内部调用其他带有Transactional注解的方法,是通过this进行调用,并没有通过cglib代理对象进行调用,导致方法未被增强导致无法检测内部事务 解决方…...

【23种设计模式】行为型模式详细介绍(下)

前言 本文为 【23种设计模式】行为型模式 相关内容介绍,下边将对访问者模式,模板模式,策略模式,状态模式,观察者模式,备忘录模式,中介者模式,迭代器模式,解释器模式&…...

dbeaver工具连接达梦数据库

、一 概述 DBeaver 是一个基于 Java 开发,免费开源的通用数据库管理和开发,DBeaver 采用 Eclipse 框架开发,支持插件扩展,并且提供了许多数据库管理工具:ER 图、数据导入/导出、数据库比较、模拟数据生成等࿰…...

比Teambition、Worktile 更适合研发团队的几大工具盘点

Worktile 和 Teambitiom 哪个更好?两个产品各有特点。1.Teambition 优势:操作简单、个人版永不收费、更适合小型团队;2.Teambition 劣势:无法满足中大型团队复杂的项目管理、自定义能力弱、无法与钉钉以外的工具打通等;…...

matlab图像处理常用功能以及函数

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录前言一、matlab灰度处理相关二、形态学的一些函数1.腐蚀2.膨胀3.开运算4.闭运算三、其他一些可能会用到的方法1.使用hough进行直线检测2.圆检测3.闭合形状检测4.寻找…...

eBPF 之 ProgramType、AttachType和InputContext

1. ProgramType 定义定义在 include/uapi/linux/bpf.h 文件中,不同 Linux 版本会有变化,以下是 Linux 5.19 版本定义:enum bpf_prog_type {BPF_PROG_TYPE_UNSPEC,BPF_PROG_TYPE_SOCKET_FILTER,BPF_PROG_TYPE_KPROBE,BPF_PROG_TYPE_SCHED_CLS,…...

C++运行时类型识别RTTI

C技能 runtime type identification(RTTI) 运行时类型识别在使用多态的时候经常用到。本文将会介绍RTTI的几个特征。1. 运行时类型转换下面的程序模仿了dynamic_cast<type_id>()类型转化符号,根据每个类的id来判断当前的类型,如果id不匹配…...

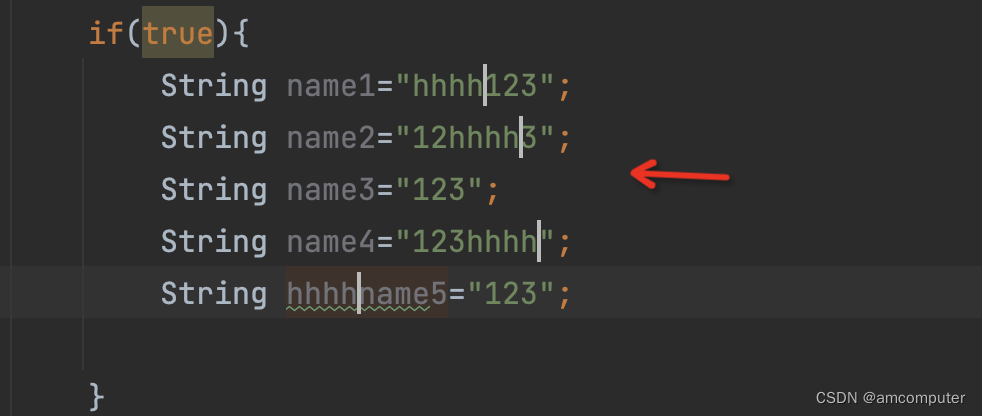

idea多时编辑多行-winmac都支持

1背景介绍 idea编辑器非常强大,其中一个功能非常优秀,很多程序员也非常喜欢用。这个功能能够大大大提高工作效率-------------多行代码同时编辑 2win 2.1方法1 按住alt鼠标左键上/下拖动即可 这样选中多行后,可以直接多行编辑。 优点&a…...

BI是报表?BI是可视化?BI到底是什么?

很多企业认为只要买一个前端商业智能BI分析工具就可以解决企业级的商业智能BI所有问题,这个看法实际上也不可行的。可能在最开始分析场景相对简单,对接数据的复杂度不是很高的情况下这类商业智能BI分析工具没有问题。但是在企业的商业智能BI项目建设有一…...

Python基础-数据类型之元组

一、元组的定义 nums (1, 2, 3, 4, 5) 元组是序列的其中一种,每个元素都以逗号分隔,用()包围。 当元组中只有一个元素时,需要在元素后面加逗号分隔,nums (1,),否则括号会被当成运算符 nums (1) print(type(nums…...

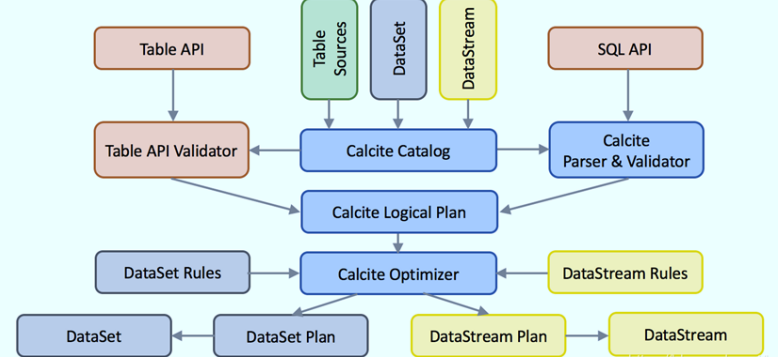

大数据面试小抄

项目地址:https://github.com/GTyingzi/BigDATA 该项目是自己在学习大数据过程中整理、总结下来的一份面试小抄。涵盖Hadoop、Spark、Flink、Hive、HBae、Kafka、ES、Zookeeper等。 开源给大家,若感觉不错欢迎star~ 摘取Flink部分如下文章目录FlinkFli…...

Vue封装的过度与动画)

Vue:(三十一)Vue封装的过度与动画

上一篇订阅与发布不够过瘾,接着再来一篇,come on!!!作用:在插入、更新或移除DOM元素时,在合适的时候给元素添加样式类名写法:过度:元素进入的样式:v-enter&am…...

文本处理:字符串替换

方法1:str.replace str.replace(old, new[, count]) Return a copy of the string with all occurrences of substring old replaced by new. If the optional argument count is given, only the first count occurrences are replaced. 该方法逻辑大致如下所示&am…...

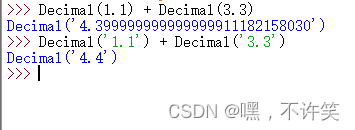

python 调用 dll 出现精度问题

问题:python 在调用dll 的时候出现了精度问题 总结:使用decimal库进行转换就可以正常传递。 ‘ 心急的朋友可以略过下文了。 心急的朋友可以略过下文了。 心急的朋友可以略过下文了。 心急的朋友可以略过下文了。 ’ 遇到的问题具体情况 dll 生成函数…...

结构体的进阶应用)

基于算法竞赛的c++编程(28)结构体的进阶应用

结构体的嵌套与复杂数据组织 在C中,结构体可以嵌套使用,形成更复杂的数据结构。例如,可以通过嵌套结构体描述多层级数据关系: struct Address {string city;string street;int zipCode; };struct Employee {string name;int id;…...

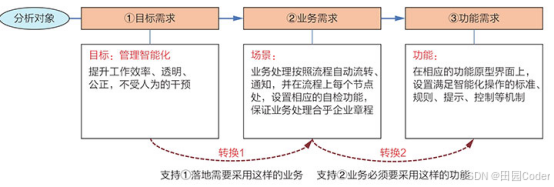

大话软工笔记—需求分析概述

需求分析,就是要对需求调研收集到的资料信息逐个地进行拆分、研究,从大量的不确定“需求”中确定出哪些需求最终要转换为确定的“功能需求”。 需求分析的作用非常重要,后续设计的依据主要来自于需求分析的成果,包括: 项目的目的…...

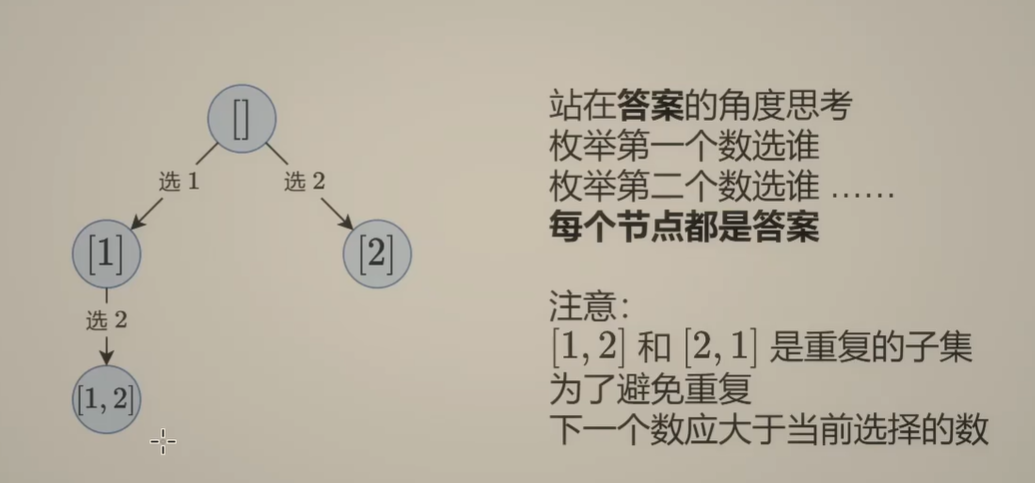

Day131 | 灵神 | 回溯算法 | 子集型 子集

Day131 | 灵神 | 回溯算法 | 子集型 子集 78.子集 78. 子集 - 力扣(LeetCode) 思路: 笔者写过很多次这道题了,不想写题解了,大家看灵神讲解吧 回溯算法套路①子集型回溯【基础算法精讲 14】_哔哩哔哩_bilibili 完…...

测试markdown--肇兴

day1: 1、去程:7:04 --11:32高铁 高铁右转上售票大厅2楼,穿过候车厅下一楼,上大巴车 ¥10/人 **2、到达:**12点多到达寨子,买门票,美团/抖音:¥78人 3、中饭&a…...

智能在线客服平台:数字化时代企业连接用户的 AI 中枢

随着互联网技术的飞速发展,消费者期望能够随时随地与企业进行交流。在线客服平台作为连接企业与客户的重要桥梁,不仅优化了客户体验,还提升了企业的服务效率和市场竞争力。本文将探讨在线客服平台的重要性、技术进展、实际应用,并…...

五年级数学知识边界总结思考-下册

目录 一、背景二、过程1.观察物体小学五年级下册“观察物体”知识点详解:由来、作用与意义**一、知识点核心内容****二、知识点的由来:从生活实践到数学抽象****三、知识的作用:解决实际问题的工具****四、学习的意义:培养核心素养…...

第 86 场周赛:矩阵中的幻方、钥匙和房间、将数组拆分成斐波那契序列、猜猜这个单词

Q1、[中等] 矩阵中的幻方 1、题目描述 3 x 3 的幻方是一个填充有 从 1 到 9 的不同数字的 3 x 3 矩阵,其中每行,每列以及两条对角线上的各数之和都相等。 给定一个由整数组成的row x col 的 grid,其中有多少个 3 3 的 “幻方” 子矩阵&am…...

蓝桥杯 冶炼金属

原题目链接 🔧 冶炼金属转换率推测题解 📜 原题描述 小蓝有一个神奇的炉子用于将普通金属 O O O 冶炼成为一种特殊金属 X X X。这个炉子有一个属性叫转换率 V V V,是一个正整数,表示每 V V V 个普通金属 O O O 可以冶炼出 …...

springboot整合VUE之在线教育管理系统简介

可以学习到的技能 学会常用技术栈的使用 独立开发项目 学会前端的开发流程 学会后端的开发流程 学会数据库的设计 学会前后端接口调用方式 学会多模块之间的关联 学会数据的处理 适用人群 在校学生,小白用户,想学习知识的 有点基础,想要通过项…...

AirSim/Cosys-AirSim 游戏开发(四)外部固定位置监控相机

这个博客介绍了如何通过 settings.json 文件添加一个无人机外的 固定位置监控相机,因为在使用过程中发现 Airsim 对外部监控相机的描述模糊,而 Cosys-Airsim 在官方文档中没有提供外部监控相机设置,最后在源码示例中找到了,所以感…...