tcl学习之路(五)(Vivado时序约束)

1.主时钟约束

主时钟通常是FPGA器件外部的板机时钟或FPGA的高速收发器输出数据的同步恢复时钟信号等。下面这句语法大家一定不会陌生。该语句用于对主时钟的名称、周期、占空比以及对应物理引脚进行约束。

create_clock -name <clock_name> -periood <period> -waveform {<rise_time> <fall_time>} [get_ports <port_name>]

在设计中,未约束的时钟可以通过时钟网络报告和时钟确认报告查看。在打开综合和实现设计后,输入如下指令:

report_clock_networks

check_timing

对于将高速传输器(gt)的输出时钟网络作为主时钟约束,命令如下:

creat_clock -name rxclk -period 6.667 [get_nets gt0/RXOUTCLK]

对于一些硬件原语的输出时钟引脚,若与其输入时钟之间没有很强的因果关联性,也可以将这个硬件原语的输出引脚作为时钟源进行主时钟约束。

对于差分时钟,只需要对差分缓冲器的输入正端(sys_clk_p)进行主时钟约束即可。若同时对正负端进行约束,会导致不真实的CDC(clock domain crossing)路径产生。

对于MMCM和PLL,系统会自动生成相应的约束文件,不需要手动约束。

在一些时序路径中,如一些引脚上的数据信号,其同步时钟只存在于外部芯片,并不存在于FPGA器件内。这种情况下,为了时序分析的需要也必须定义一个时钟用于描述时序数据引脚的外部时钟信号,这个时钟就是虚拟时钟。虚拟时钟的约束不需要引脚。

create_clock -name clk_virt -period 10

2.时钟特性约束

对于时钟抖动的约束有以下两条 ,其中set_input_jitter只能约束主时钟,set_system_jitter对系统抖动进行定义。

set_input_jitter [get_clocks <clock_name>] <jitter_in_ns>

set_system_jitter <clock_name> <jitter_in_ns>

除时钟抖动以为的所有可能影响时钟周期性偏差的因素,都可以使用set_clock_uncertainty命令进行约束定义。也称用户不确定性。

set_clock_uncertainty -<setup/hold/空出来表示两者都有> -from [get_clocks <clock0_name>] -to [get_clocks <clock1_name>] <uncertainty_value>

对于时钟延时约束,有以下命令:

set_clock_latency [-clock <args>] [-rise] [-fall] [-min/max/空出来表示两者都有] [-source] <latency> <objects>

3.衍生时钟约束

衍生时钟主要是指由已有的主时钟进行分频、倍频或者相移而产生出来的时钟信号,如由MMCM或一些设计逻辑所驱动产生的时钟信号。一般Vivado的时序工具能够自动产生正确的衍生时钟,若设计者认为自动产生的衍生时钟有误,也可以手动进行衍生时钟的约束。

create_generated_clock -name <generated_clock_name> -source <master_clock_source_pin_or_port> -multiply_by <mult_factor>\-divide_by <div_factor> <pin_or_port>

4.IO接口约束

IO接口的时序约束主要包括set_input_delay和set_output_delay,输入输出约束差不多,主要约束如下:

set_input_delay -clock<args> -reference_pin<args> -clock_fall -rise -max -add_delay <delay> <objects>

#下面对命令进行解释

-clock 用于指定约束引脚的同步时钟(源时钟),其后的<args>即需要指定的同步时钟名称,这个时钟可以是设计中事先定义的主时钟或虚拟时钟。

-reference_pin 用于指定延时值<delay>的参考时钟,其后的<args>即需要指定的参考时钟名称。该项是可选项,不指定该选项,则指定延时值的参考时钟就是-clock指定的同步时钟。

-clock_fall 指定输入延时约束取值相对于同步时钟的下降沿。若不指定,默认为-clock_rise

-rise 指定约束信号相对时钟的边沿关系是上升沿,也可以用-fall指定为下降沿

-max 设定最大延时值,也可以是-min最小值。若不指定,则是最大最小值都包括

-add_delay 用于多组参考组合的输入引脚约束

<delay> 设定延时值

<objects> 指定约束的目标输入引脚名称

关于输入延时的计算如下:

set_input_delay(max)= -Tc2j_pcb(min) + Tco(max) + Td_pcb(max)

set_input_delay(min)= -Tc2j_pcb(min) + Tco(max) + Td_pcb(min)

其中c2j_pcb代表时钟源在pcb上的走线延时,d_pcb为数据在pcb上的走线延时,co为外部芯片数据引脚输出数据所经过的延时,查芯片手册可以获得。

set_output_delay(max)= Td_pcb(max) - Tc2j_pcb(min) + Tsu

set_output_delay(min)= Td_pcb(min) - Tc2j_pcb(min) - Th

5.时钟例外约束

进行时序例外约束的原因:时序分析工具默认的时序检查方式可能与工程实现的实际情况不符合(通常是约束过紧,可能导致时序失败)。因此,设计者需要额外增加一些约束命令,用于调整既有的时序检查方式,以保证时序工具的时序检查与实际情况一致。

进行时序例外约束的典型例子:1.异步时钟域路径,通常可以使用时钟分组约束或虚假路径约束以及多周期约束。2.某些逻辑的时序单元并非每个时钟周期都及进行数据采样传输,此时可以使用多周期约束,适当放宽这些路径的约束 。3.有时设计中希望对时序路径施加更紧的约束,以获得更大的时序余量,此时可以使用最大/最小延时约束。4.某些组合路径是静态的(赋值不变)或不需要进行时序约束,此时可以使用虚假路径约束忽略这些路径。

5.1多周期约束

多周期约束语法如下:

set_multicycle_path <path_multiplier> -setup/hold -start/end -from <startpoints> -to <endpoints> -through <pins/cells/nets>

#

-start和-end用于指定约束命令的周期参数是以源时钟还是以目标时钟作为参考时钟。

对于源时钟和目标时钟同频同相的时序路径分析,是否使用-start和-end是没有头差异的。

保持时间的时钟周期数=建立时间的<path_multiplier>参数-1-保持时间的<path_multiplier>参数。在一般情况下,若只对setup进行set_multicycle_path约束,则保持时间的<path_multiplier>参数默认为0,也就是保持时间的时钟周期数默认和建立时间的<path_multiplier>参数相差一个时钟周期。那么仅对setup进行约束,则建立时间和保持时间关系同时向右移动<path_multiplier>参数-1个时钟周期,若加上对hold的<path_multiplier>参数约束,则保持时间关系会向左移动hold的<path_multiplier>参数个时钟周期,从而达到多周期约束的效果。

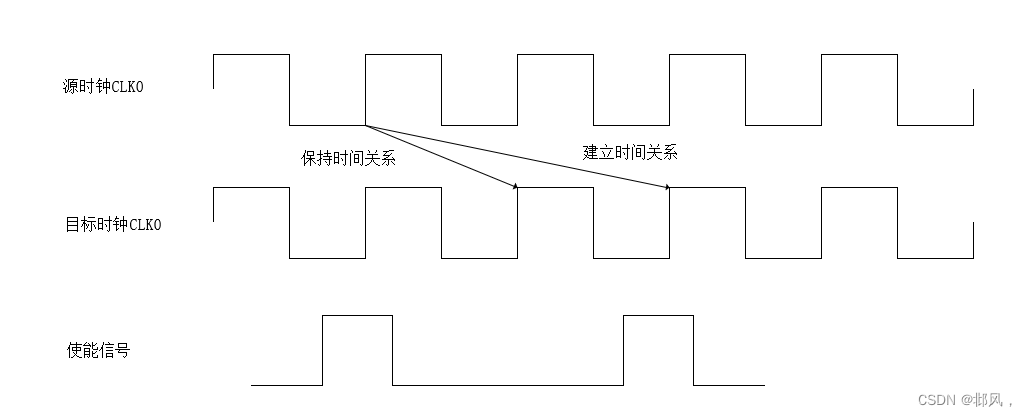

下面给出示意图。

当约束仅为set_multicycle_path 2 -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]时,图形如下:

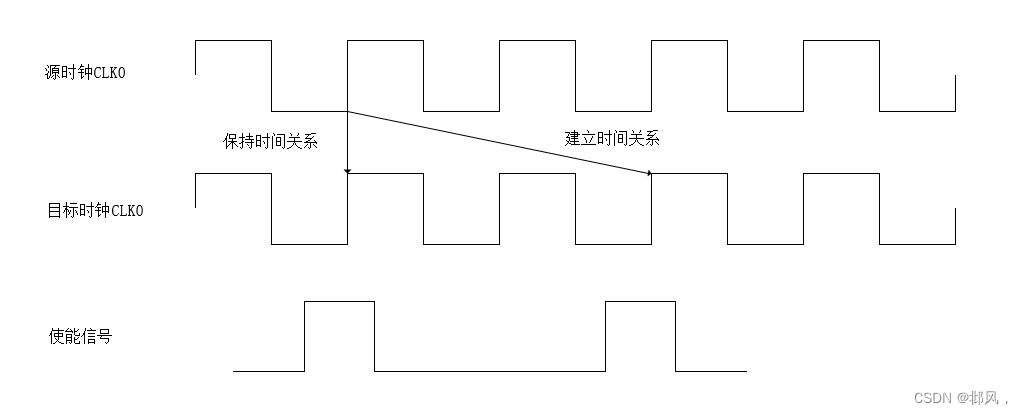

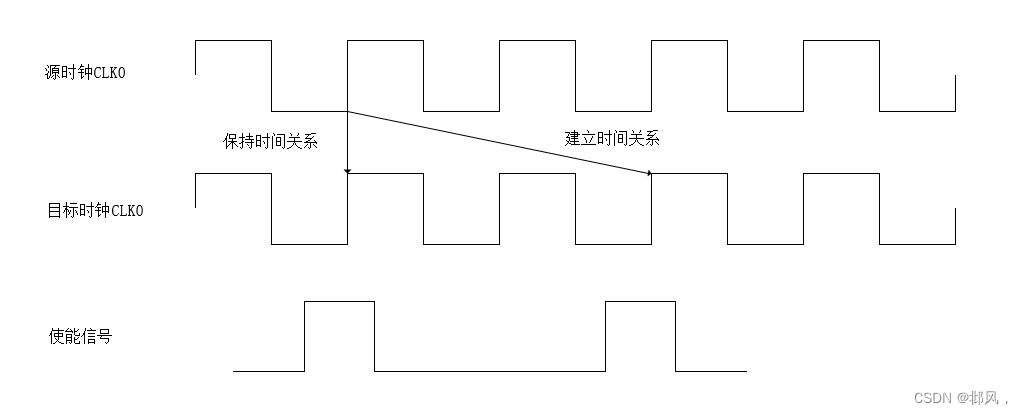

当约束为set_multicycle_path 2 -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]和set_multicycle_path 1 -hold -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]时,图形如下:

当约束为set_multicycle_path 2 -setup -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]和set_multicycle_path 1 -hold -from [get_pins data0_reg/C] -to [get_pins data1_reg/D]时,图形如下:

对于同频异相的时钟,在默认情况下时序工具会寻找与clk1相邻最近的clk2时钟上升沿,并以clk1和clk2相对时间最短(时序要求最高,即最坏情况)的一组时钟沿的时序路径进行分析。此时,使用如下约束命令进行调整:

对于同频异相的时钟,在默认情况下时序工具会寻找与clk1相邻最近的clk2时钟上升沿,并以clk1和clk2相对时间最短(时序要求最高,即最坏情况)的一组时钟沿的时序路径进行分析。此时,使用如下约束命令进行调整:

set_multicycle_path 2 -setup -from [get_clocks CLK1] -to [get_clocks CLK2]

对于慢时钟域到快时钟域或者快时钟域到慢时钟域有异曲同工之妙,需要注意的是-start和-end的确认,下面给出这两种情况的通用约束方法。

#慢-快

set_multicycle_path N -setup -end -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path N-1 -hold -end -from [get_clocks CLK1] -to [get_clocks CLK2]

#快-慢

set_multicycle_path N -setup -start -from [get_clocks CLK1] -to [get_clocks CLK2]

set_multicycle_path N-1 -hold -start -from [get_clocks CLK1] -to [get_clocks CLK2]

5.2虚假路径约束

所谓虚假路径,是指该路径是设计中的非功能路径或没有任何时序要求的路径。做虚假路径约束的原因:可以减少编译时间,同时腾出有限的布局布线资源,用于提升整体的时序性能。常见的虚假路径包括:1.已经做过同步处理的跨时钟域路径。2.上电后只做一次初始化写入 寄存器路径。3.复位或测试逻辑路径。4.某些实际并不存在的时序路径。例如,设计中的两个异步是哦只能怪域之间的数据通信已经使用双寄存器锁存等方式进行同步了,就可以使用虚假路径约束关闭这两个时钟之间的数据路径检查。约束的基本语法如下:

set_false_path -setup/hold -from <node_list> -to <node_list> -through <node_list>

#对于两个或多个相斥时钟做约束推荐用法

set_clock_groups -group CLKA -group CLKB

5.3最大/最小延时约束

最大延时约束将覆盖默认的建立时间分析的最大路径延时值。最小延时约束将覆盖默认的保持时间分析的最小路径延时值。基本约束语法如下:

set_max_delay <delay> -datapath_only -from <node_list> -to <node_list> -through <node_list>

set_min_delay <delay> -from <node_list> -to <node_list> -through <node_list>

其中,-datapath_only只能用于含有-from选项的set_max_delay约束命令中。该选项会将时钟偏斜考虑移除,同时会将约束路径的保持时间检查设置为false路径,相当于同时对此路径自动生成了set_false_path -hold约束。也就是说,若对同一路径进行set_min_delay约束,将会被忽略。

相关文章:

tcl学习之路(五)(Vivado时序约束)

1.主时钟约束 主时钟通常是FPGA器件外部的板机时钟或FPGA的高速收发器输出数据的同步恢复时钟信号等。下面这句语法大家一定不会陌生。该语句用于对主时钟的名称、周期、占空比以及对应物理引脚进行约束。 create_clock -name <clock_name> -periood <period> -wa…...

Hlang-中英双语言编程语言使用手册

文章目录 介绍Hlang基本使用下载配置环境变量特性中文关键字支持中文符号混合编程中文错误提示终端多行输入基本数据类型整数浮点数列表字符串基本操作变量定义逻辑判断基本运算条件判断循环函数介绍 Hlang是一款基于Python编写的支持中英文混合编程的动态语言。其简单易上手,…...

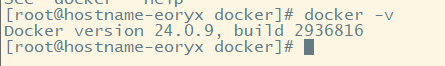

centos 7 安装docker

系统配置: CentOS关闭selinux sed -i s/SELINUXenforcing/SELINUXdisabled/g /etc/selinux/config关闭防火墙(可选)或者放行相应端口 systemctl stop firewalld.service && systemctl disable firewalld.service配置内核IP 转发 net.ipv4.ip_forward1 dock…...

Spring环境搭建、SpringIOC容器基础、SpringDI基础

文章目录 Spring环境搭建、SpringIOC容器基础、SpringDI基础一、SpringIOC核心思想二、搭建Spring环境步骤三、SpringIOC容器使用步骤四、SpringIOC 总结五、SpringDI(依赖注入)1、基本概念2、实现方式(1)set 注入(2&a…...

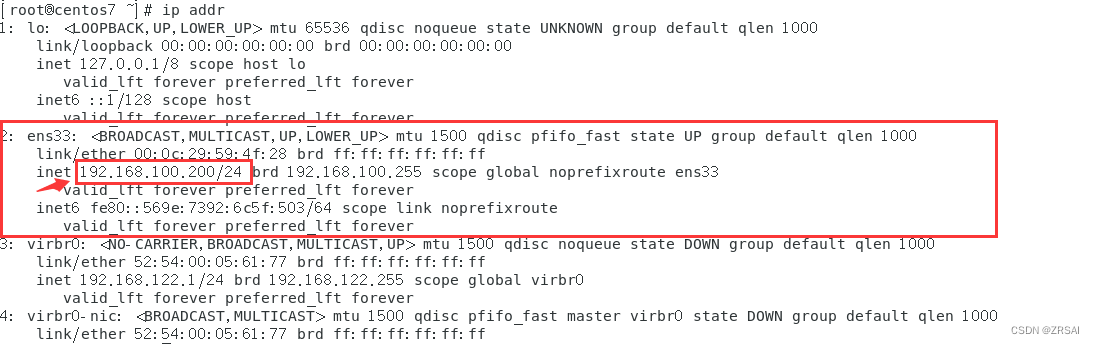

CentOS7.9手工配置静态网络流程

进入网卡配置文件 vim /etc/sysconfig/network-scripts/ifcfg-ens33 配置 TYPE"Ethernet" PROXY_METHOD"none" BROWSER_ONLY"no" BOOTPROTO"static" //static 配置静态网络 DEFROUTE"yes" IPV4_FAILURE_FATAL"no…...

JVM面试题-1

1、什么是JVM内存结构? jvm将虚拟机分为5大区域,程序计数器、虚拟机栈、本地方法栈、java堆、方法区; 程序计数器:线程私有的,是一块很小的内存空间,作为当前线程的行号指示器,用于记录当前虚拟…...

漫谈红黑树:红黑树的奇妙演化

漫谈红黑树:红黑树的奇妙演化 一、红黑树的提出二、红黑树性质的简单推导三、结论 博主简介 💡一个热爱分享高性能服务器后台开发知识的博主,目标是通过理论与代码实践的结合,让世界上看似难以掌握的技术变得易于理解与掌握。技能…...

docker启动rabbitmq,但是页面加载不出来问题解决

首先docker启动rabbitmq docker run -d -p 5672:5672 -p 15672:15672 --name rabbitmq rabbitmq -d 后台运行 -p 映射外部端口 -- name 取名(方便管理) 然后发现,成功启动rabbitmq,却加载不进去 因为你下载的是rabbitmq的latest…...

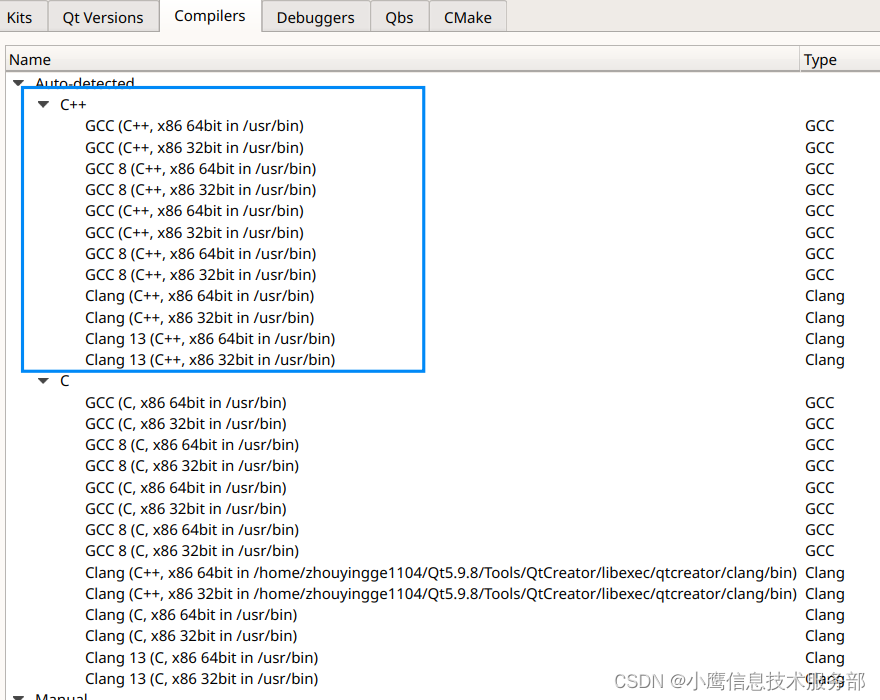

Qt项目报错:Cannot run compiler ‘clang++‘. /bin/sh: 1: clang++: not found

在一台旧电脑上装了深度系统,装了Qt,导入项目, build提示 clang找不到: Project ERROR: Cannot run compiler clang. Output: /bin/sh: 1: clang: not found Maybe you forgot to setup the environment? Error while parsing …...

奇舞周刊第503期:图解串一串 webpack 的历史和核心功能

记得点击文章末尾的“ 阅读原文 ”查看哟~ 下面先一起看下本期周刊 摘要 吧~ 奇舞推荐 ■ ■ ■ 图解串一串 webpack 的历史和核心功能 提到打包工具,可能你会首先想到 webpack。那没有 webpack 之前,都是怎么打包的呢?webpack 都有哪些功能&…...

6.redis面试题和坑

1.哨兵模式 多少个节点多少个哨兵(如果全部哨兵检测到已经master dead,重新选举)写sentinel.conf,监控的主机 票数 sentinel monitor myredis 127.0.0.1 6379 1启动哨兵 redis-sentinel sentinel.conf关闭主机 failover sdown info replication shutdown优点 1.基于主从复制模式…...

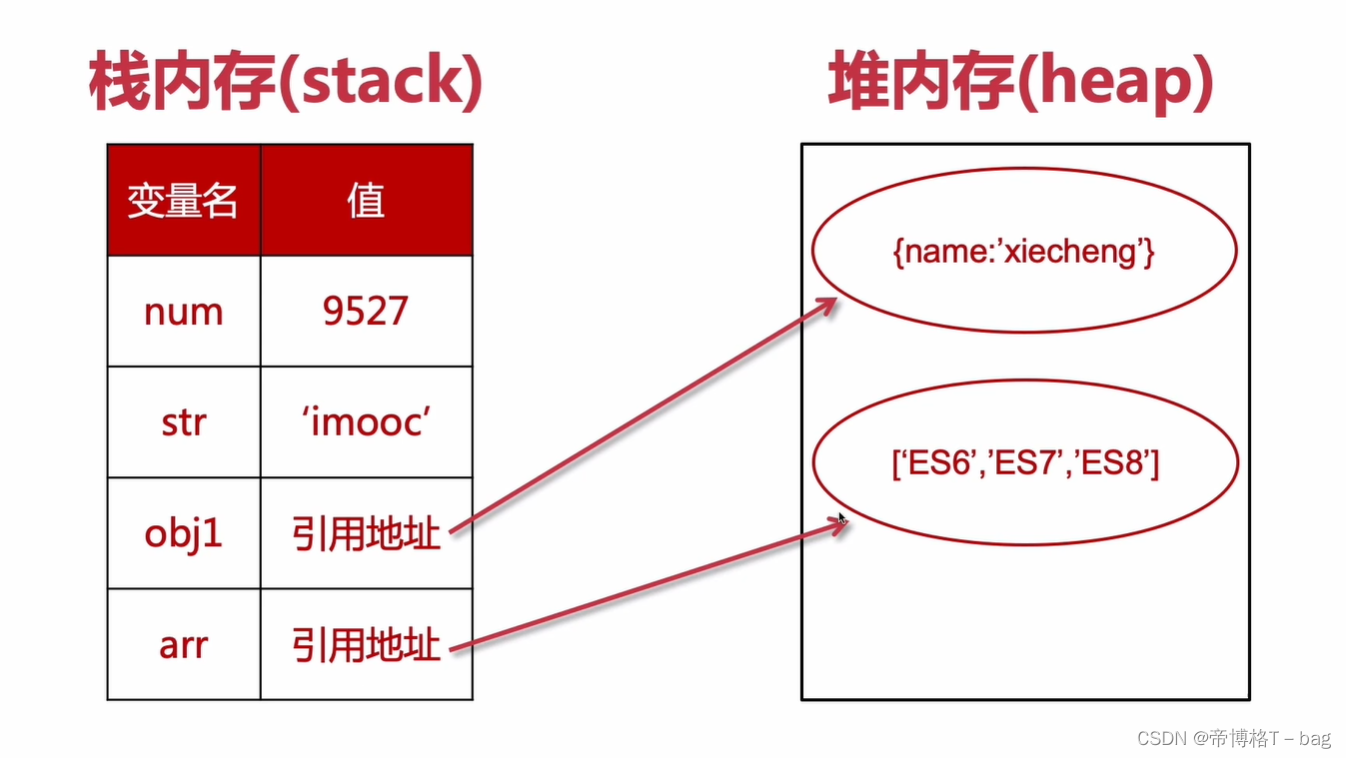

【ES6】—使用 const 声明

一、不属于顶层对象window 使用const关键字 声明的变量,不会挂载到window属性上 const a 5 console.log(a) console.log(window.a) // 5 // undefined二、不允许重复声明 使用const关键字不允许重复声明相同的变量 cosnt a 5 cosnt a 6 // Uncaught SyntaxEr…...

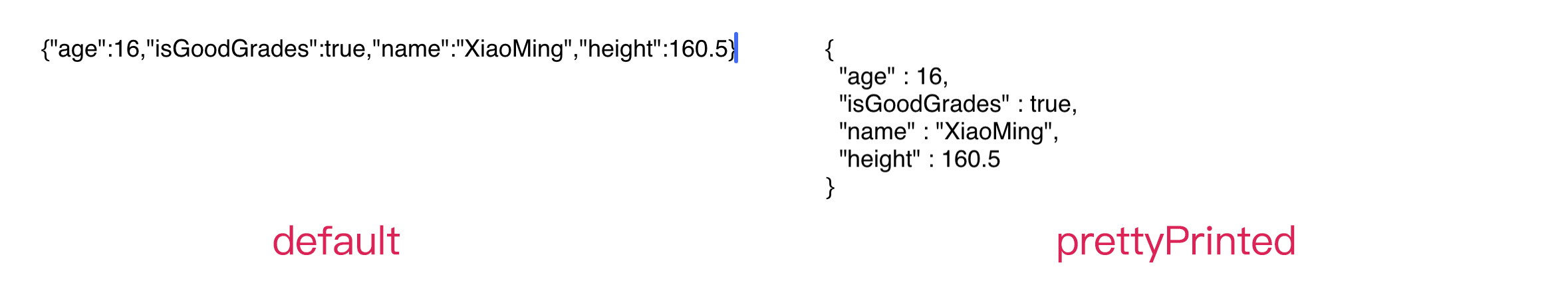

iOS开发 - Swift Codable协议实战:快速、简单、高效地完成JSON和Model转换!

前言 Codable 是 Swift 4.0 引入的一种协议,它是一个组合协议,由 Decodable 和 Encodable 两个协议组成。它的作用是将模型对象转换为 JSON 或者是其它的数据格式,也可以反过来将 JSON 数据转换为模型对象。 Encodable 和 Decodable 分别定…...

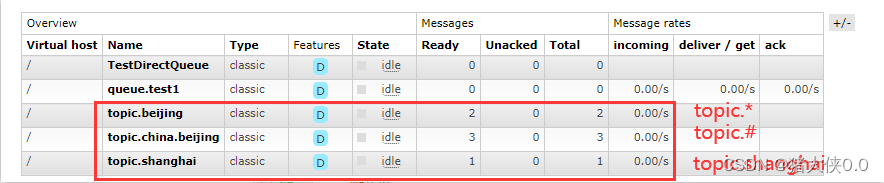

RabbitMq:Topic exchange(主题交换机)的理解和使用

RabbitMq:Topic exchange(主题交换机)的理解和使用 在RabbitMq中,生产者的消息都是通过交换机来接收,然后再从交换机分发到不同的队列中去,在分发的过程中交换机类型会影响分发的逻辑,下面主要讲解一下主题交换机。 主题交换…...

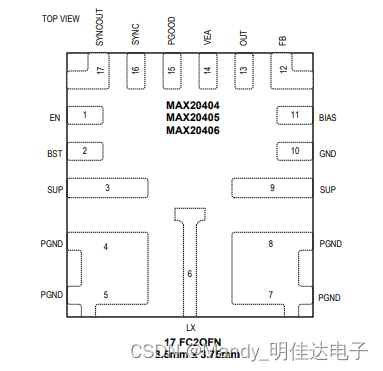

汽车级36V、4A同步降压转换器MAX20404AFOD/VY、MAX20404AFOC/VY、MAX20404AFOA/VY开关稳压器

MAX20404是小型同步降压转换器,集成了高端和低端开关。这些IC均设计为可在3V到36V的宽输入电压范围内提供高达4A的电流。电压质量可以通过观察PGOOD信号来监测。该器件可以在99%的占空比下运行,非常适合汽车和工业应用。 MAX20404提供可编程输出电压或5…...

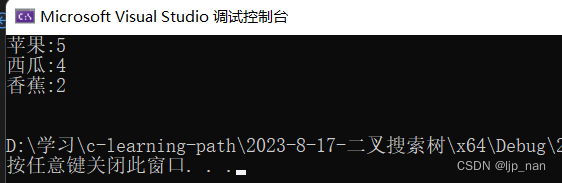

C++------利用C++实现二叉搜索树【数据结构】

文章目录 二叉搜索树概念二叉搜索树的操作查找插入删除 二叉搜索树的应用 二叉搜索树 概念 什么是二叉搜索树,二叉搜索树就是指左孩子永远比根小右孩子永远比根大。这个规则适用于所有的子树。 上面的就是一棵二叉搜索树,我们还可以发现这棵树走一个中…...

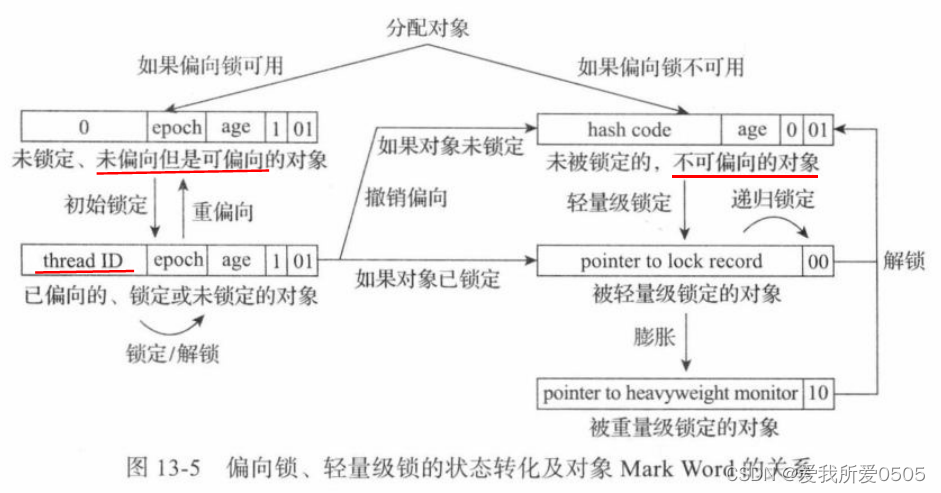

HotSpot虚拟机之内存模型与线程安全

目录 一、线程内存模型 1. 内存模型 2. 内存模型操作 二、Happens-Before原则 三、Java线程 1. 线程实现方式 2. Java线程状态 四、Java线程安全 1. 线程安全程度 2. 锁优化 五、参考资料 一、线程内存模型 1. 内存模型 内存模型主要目的是定义共享变量的访问规则&…...

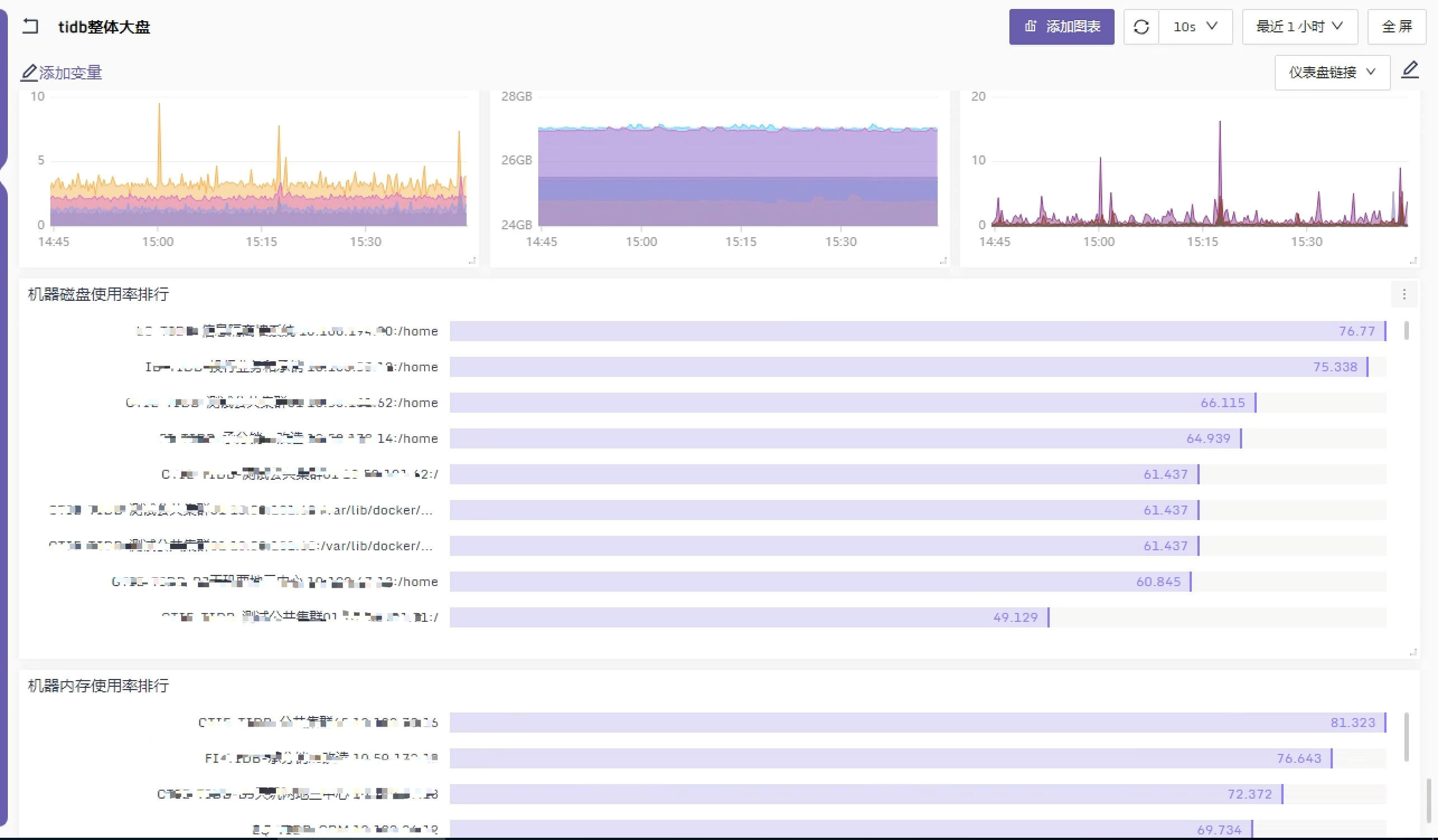

TiDB 多集群告警监控-中章-融合多集群 Grafana

作者: longzhuquan 原文来源: https://tidb.net/blog/ac730b0f 背景 随着公司XC改造步伐的前进,越来越多的业务选择 TiDB,由于各个业务之间需要物理隔离,避免不了的 TiDB 集群数量越来越多。虽然每套 TiDB 集群均有…...

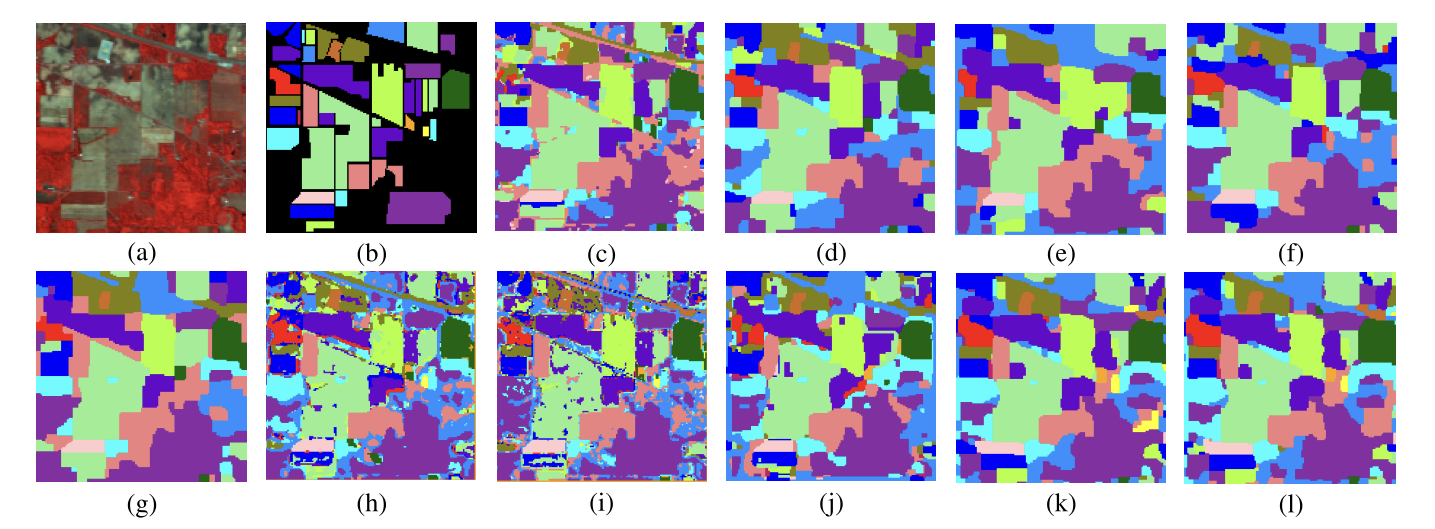

【图像分类】基于卷积神经网络和主动学习的高光谱图像分类(Matlab代码实现)

💥💥💞💞欢迎来到本博客❤️❤️💥💥 🏆博主优势:🌞🌞🌞博客内容尽量做到思维缜密,逻辑清晰,为了方便读者。 ⛳️座右铭&a…...

notepad++ verilog关键字自动补全

新建verilog.xml放在安装目录下 D:\Program Files (x86)\Notepad\autoCompletion <?xml version"1.0" encoding"Windows-1252" ?> <NotepadPlus><AutoComplete><KeyWord name"accept_on" /><KeyWord name"a…...

Docker 离线安装指南

参考文章 1、确认操作系统类型及内核版本 Docker依赖于Linux内核的一些特性,不同版本的Docker对内核版本有不同要求。例如,Docker 17.06及之后的版本通常需要Linux内核3.10及以上版本,Docker17.09及更高版本对应Linux内核4.9.x及更高版本。…...

[2025CVPR]DeepVideo-R1:基于难度感知回归GRPO的视频强化微调框架详解

突破视频大语言模型推理瓶颈,在多个视频基准上实现SOTA性能 一、核心问题与创新亮点 1.1 GRPO在视频任务中的两大挑战 安全措施依赖问题 GRPO使用min和clip函数限制策略更新幅度,导致: 梯度抑制:当新旧策略差异过大时梯度消失收敛困难:策略无法充分优化# 传统GRPO的梯…...

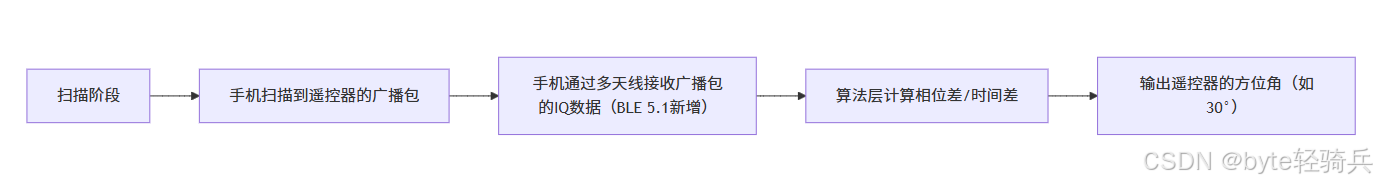

蓝牙 BLE 扫描面试题大全(2):进阶面试题与实战演练

前文覆盖了 BLE 扫描的基础概念与经典问题蓝牙 BLE 扫描面试题大全(1):从基础到实战的深度解析-CSDN博客,但实际面试中,企业更关注候选人对复杂场景的应对能力(如多设备并发扫描、低功耗与高发现率的平衡)和前沿技术的…...

转转集团旗下首家二手多品类循环仓店“超级转转”开业

6月9日,国内领先的循环经济企业转转集团旗下首家二手多品类循环仓店“超级转转”正式开业。 转转集团创始人兼CEO黄炜、转转循环时尚发起人朱珠、转转集团COO兼红布林CEO胡伟琨、王府井集团副总裁祝捷等出席了开业剪彩仪式。 据「TMT星球」了解,“超级…...

页面渲染流程与性能优化

页面渲染流程与性能优化详解(完整版) 一、现代浏览器渲染流程(详细说明) 1. 构建DOM树 浏览器接收到HTML文档后,会逐步解析并构建DOM(Document Object Model)树。具体过程如下: (…...

数据链路层的主要功能是什么

数据链路层(OSI模型第2层)的核心功能是在相邻网络节点(如交换机、主机)间提供可靠的数据帧传输服务,主要职责包括: 🔑 核心功能详解: 帧封装与解封装 封装: 将网络层下发…...

【AI学习】三、AI算法中的向量

在人工智能(AI)算法中,向量(Vector)是一种将现实世界中的数据(如图像、文本、音频等)转化为计算机可处理的数值型特征表示的工具。它是连接人类认知(如语义、视觉特征)与…...

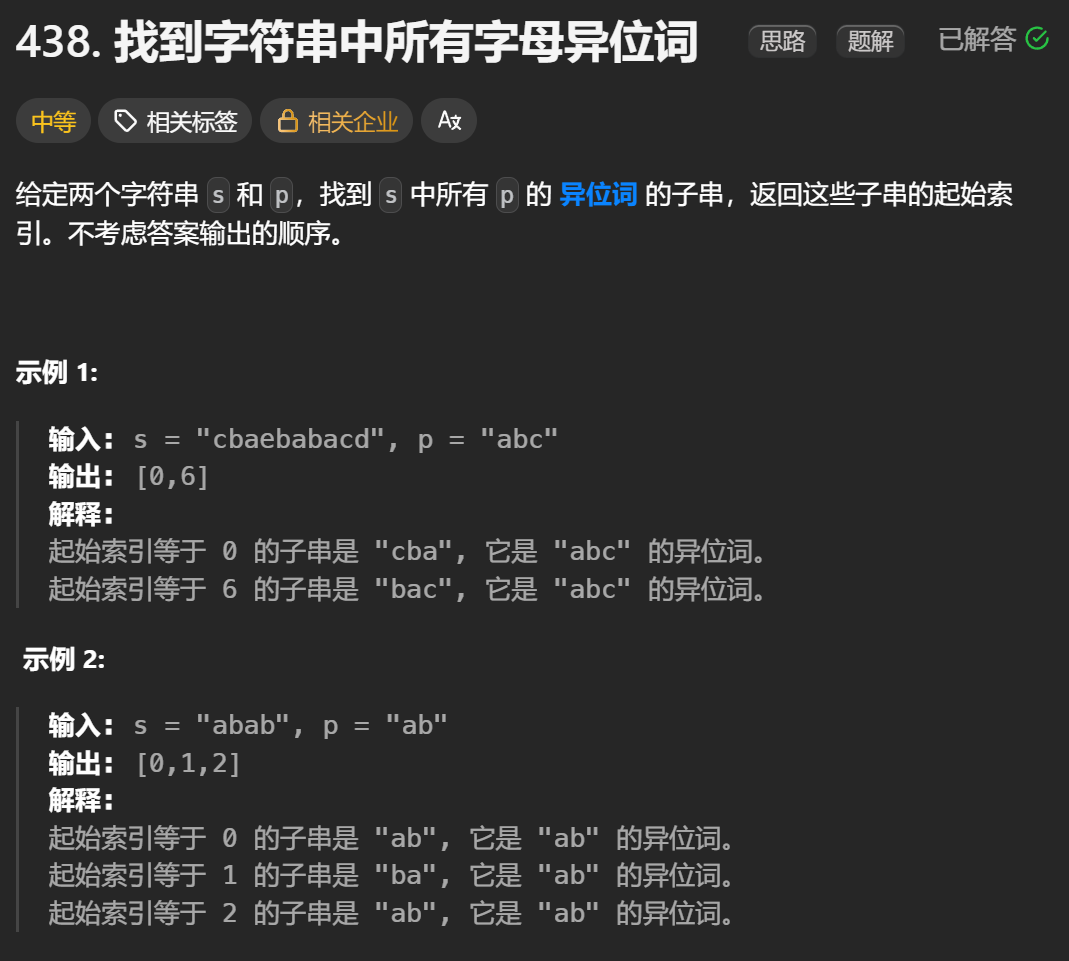

12.找到字符串中所有字母异位词

🧠 题目解析 题目描述: 给定两个字符串 s 和 p,找出 s 中所有 p 的字母异位词的起始索引。 返回的答案以数组形式表示。 字母异位词定义: 若两个字符串包含的字符种类和出现次数完全相同,顺序无所谓,则互为…...

高防服务器能够抵御哪些网络攻击呢?

高防服务器作为一种有着高度防御能力的服务器,可以帮助网站应对分布式拒绝服务攻击,有效识别和清理一些恶意的网络流量,为用户提供安全且稳定的网络环境,那么,高防服务器一般都可以抵御哪些网络攻击呢?下面…...

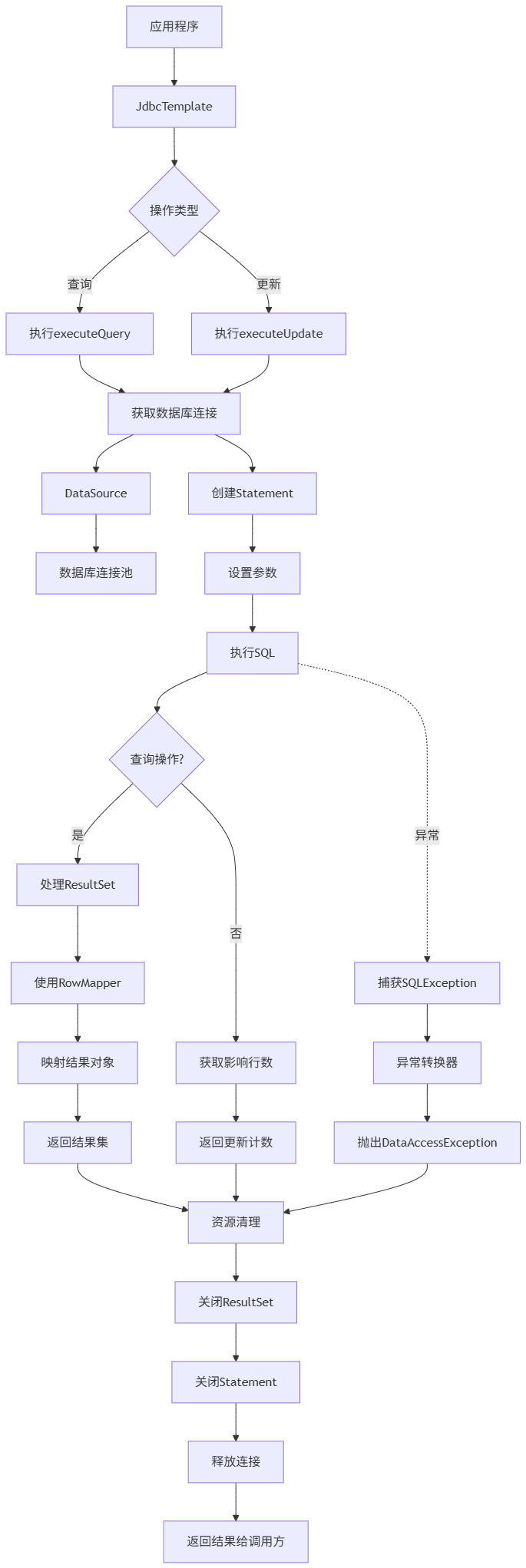

Spring数据访问模块设计

前面我们已经完成了IoC和web模块的设计,聪明的码友立马就知道了,该到数据访问模块了,要不就这俩玩个6啊,查库势在必行,至此,它来了。 一、核心设计理念 1、痛点在哪 应用离不开数据(数据库、No…...