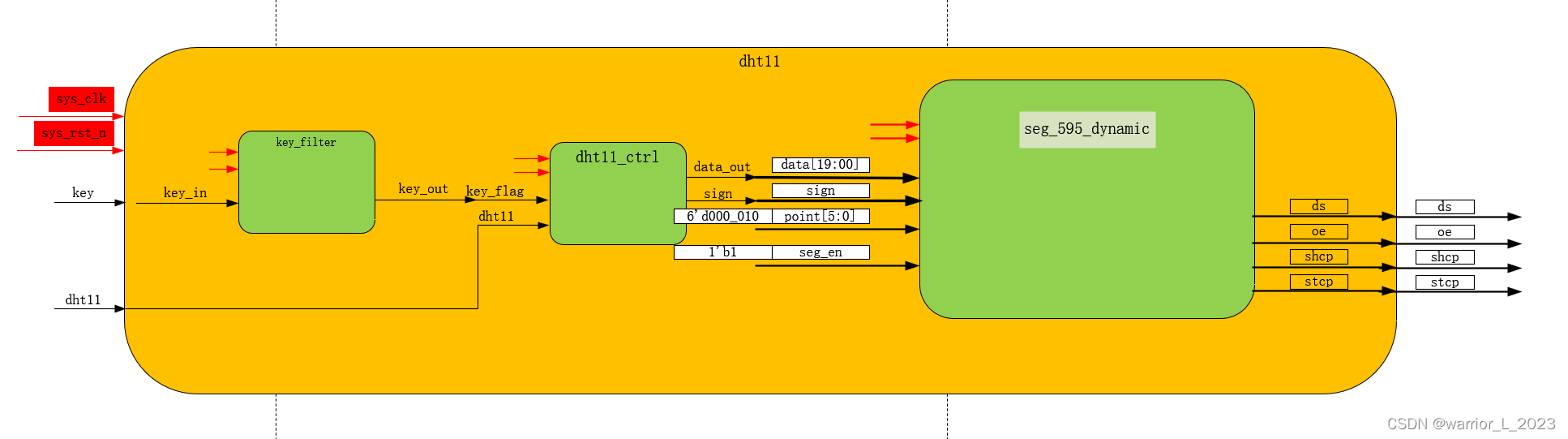

FPGA project : dht11 温湿度传感器

没有硬件,过几天上板测试。

module dht11(input wire sys_clk ,input wire sys_rst_n ,input wire key ,inout wire dht11 ,output wire ds ,output wire oe ,output wire shcp ,output wire stcp

);// 例化连线wire key_out_w ;wire [19:00] data_w ;wire sign_w ;wire [ 5: 0] point_w ;wire en_w ;

key_filter key_filter_insert(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_in ( key ) ,.key_out ( key_out_w )

);dht11_ctrl dht11_ctrl_insert(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_flag ( key_out_w ) ,.dht11 ( dht11 ) ,.data_out ( data_w ) ,.sign ( sign_w )

);seg_595_dynamic seg_595_dynamic_insert(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.data ( data_w ) , .point ( point_w ) ,.sign ( sign_w ) , .seg_en ( en_w ) ,.ds ( ds ) ,.oe ( oe ) ,.shcp ( shcp ) ,.stcp ( stcp )

);endmodulemodule dht11_ctrl (input wire sys_clk ,input wire sys_rst_n ,input wire key_flag ,inout wire dht11 ,output reg [19:0] data_out ,output reg sign

);// reg signal define// 产生us时钟reg clk_us ;reg [4:0] cnt_clk_us ;// 内部信号(用于产生状态转移条件与输出信号)reg [19:0] cnt_us ;reg [ 6:0] cnt_low ;reg dht11_reg1 ;reg dht11_reg2 ;wire dht11_fall ;wire dht11_rise ;reg [ 5:0] bit_cnt ;reg [39:0] data_temp ;reg [31:0] data ;reg data_flag ;// 三态输出reg dht11_en ;wire dht11_out ;// [4:0] cnt_clk_us ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) begincnt_clk_us <= 5'd0 ;end else beginif(cnt_clk_us == 5'd24) begincnt_clk_us <= 5'd0 ;end else begincnt_clk_us <= cnt_clk_us + 1'b1 ;endendend// clk_us ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) beginclk_us <= 1'b0 ;end else beginif(cnt_clk_us == 5'd24) beginclk_us <= ~clk_us ;end else beginclk_us <= clk_us ;endendend// reg signal define// 在clk_us时钟域下// 状态机 三段式写法(现态与次态描述)(状态转移条件描述)(输出信号描述)localparam WAIT_1S = 6'b000_001 ,START = 6'b000_010 ,DELAY_1 = 6'b000_100 ,REPLAY = 6'b001_000 ,DELAY_2 = 6'b010_000 ,RD_DATA = 6'b100_000 ;reg [5:0] state_c ;reg [5:0] state_n ;wire WAIT_1StoSTART ;wire STARTtoDELAY_1 ;wire DELAY_1toREPLAY ;wire REPLAYtoDELAY_2 ;wire REPLAYtoSTART ;wire DELAY_2toRD_DATA ;wire DELAY_2toSTART ;always @(posedge clk_us or negedge sys_rst_n) beginif(~sys_rst_n) beginstate_c <= 6'd0 ;end else beginstate_c <= state_n ;endendalways @(*) begincase (state_c)WAIT_1S:beginif(WAIT_1StoSTART) begin state_n <= START ;end else beginstate_n <= WAIT_1S ;endendSTART :beginif(STARTtoDELAY_1) beginstate_n <= DELAY_1 ;end else beginstate_n <= START ;endendDELAY_1:beginif(DELAY_1toREPLAY) beginstate_n <= REPLAY ;end else beginstate_n <= DELAY_1 ;endendREPLAY :beginif(REPLAYtoDELAY_2) begin state_n <= DELAY_2 ;end else beginif(REPLAYtoSTART) beginstate_n <= START ;end else beginstate_n <= REPLAY ;endendendDELAY_2:beginif(DELAY_2toRD_DATA) begin state_n <= RD_DATA ;end else beginstate_n <= DELAY_2 ;endendRD_DATA:beginif(DELAY_2toSTART) beginstate_n <= START ;end else beginstate_n <= RD_DATA ;endenddefault: state_n <= START ;endcaseend// 状态机第二段描述assign WAIT_1StoSTART = (state_c == WAIT_1S && cnt_us == 20'd999_999) ? 1'b1 : 1'b0 ;assign STARTtoDELAY_1 = (state_c == START && cnt_us == 20'd17_999) ? 1'b1 : 1'b0 ;assign DELAY_1toREPLAY = (state_c == DELAY_1 && cnt_us == 20'd10) ? 1'b1 : 1'b0 ;assign REPLAYtoDELAY_2 = (state_c == REPLAY && dht11_rise == 1'b1 && cnt_low <= 7'd85 && cnt_low >= 7'd81) ? 1'b1 : 1'b0;assign REPLAYtoSTART = (state_c == REPLAY && dht11_rise == 1'b1 && (cnt_us >= 20'd100 || cnt_us <= 20'd70)) ? 1'b1 : 1'b0 ;assign DELAY_2toRD_DATA= (state_c == DELAY_2 && dht11_fall == 1'b1 && cnt_us >= 20'd85 && cnt_us <= 20'd88) ? 1'b1 : 1'b0 ;assign DELAY_2toSTART = (state_c == RD_DATA && bit_cnt == 6'd40 && dht11_rise == 1'b1) ? 1'b1 : 1'b0 ;// // 内部信号(用于产生状态转移条件与输出信号)// reg [19:0] cnt_us ;always @(posedge clk_us or negedge sys_rst_n) beginif(~sys_rst_n) begincnt_us <= 20'd0 ;end else beginif((state_c == WAIT_1S && cnt_us == 20'd999_999) || (state_c == START && cnt_us == 20'd17_999) || (state_c == DELAY_1 && cnt_us == 20'd10) || (state_c == REPLAY && dht11_rise == 1'b1)|| (state_c == DELAY_2 && dht11_fall == 1'b1)|| (state_c == RD_DATA && (dht11_fall || dht11_rise)))begin // 记得最后加大括号cnt_us <= 20'd0 ;end else begincnt_us <= cnt_us + 1'b1 ;endendend// reg [ 6:0] cnt_low ;always @(posedge clk_us or negedge sys_rst_n) beginif(~sys_rst_n) begincnt_low <= 7'd0 ;end else beginif(state_c == REPLAY && dht11_reg1 == 1'b0) begincnt_low <= cnt_low + 1'b1 ;end else begincnt_low <= 7'd0 ;endendend// reg dht11_reg1 ;// reg dht11_reg2 ;always @(posedge clk_us or negedge sys_rst_n) beginif(~sys_rst_n) begindht11_reg1 <= 1'b1 ;dht11_reg2 <= 1'b1 ;end else begindht11_reg1 <= dht11 ;dht11_reg2 <= dht11_reg1 ;endend// wire dht11_fall ;// wire dht11_rise ;assign dht11_fall = ~dht11_reg1 && dht11_reg2 ;assign dht11_rise = dht11_reg1 && ~dht11_reg2 ;// reg [ 5:0] bit_cnt ;always @(posedge clk_us or negedge sys_rst_n) beginif(~sys_rst_n) beginbit_cnt <= 6'd0 ;end else beginif(dht11_rise && bit_cnt == 6'd40 ) beginbit_cnt <= 6'd0 ;end else beginif(state_c == RD_DATA && dht11_fall) beginbit_cnt <= bit_cnt + 1'b1 ;end else beginbit_cnt <= bit_cnt ;endendendend// reg [39:0] data_temp ;always @(posedge clk_us or negedge sys_rst_n) begin if(~sys_rst_n) begindata_temp <= 40'd0 ;end else beginif(state_c == RD_DATA && dht11_fall && bit_cnt <= 39) beginif(cnt_us >= 20'd50) begin // 也可以是68data_temp[39 - bit_cnt] <= 1'b1 ;end else begindata_temp[39 - bit_cnt] <= 1'b0 ;endend else begindata_temp <= data_temp ;endendend// reg [31:0] data ;always @(posedge clk_us or negedge sys_rst_n) beginif(~sys_rst_n) begindata <= 32'd0 ;end else beginif(data_temp[7:0] == (data_temp[15:8] + data_temp[23:16] + data_temp[31:24] + data_temp[39:32])) begindata <= data_temp[39:8] ;end else begindata <= data ;endendend// reg data_flag ; sys_clk时钟域下always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) begindata_flag <= 1'b0 ;end else beginif(key_flag) begindata_flag <= ~data_flag ;end else begindata_flag <= data_flag ;endendend// // 三态输出// wire dht11_out ;assign dht11 = (dht11_en == 1'b1) ? dht11_out : 1'bz ;assign dht11_out = 1'b0 ;// reg dht11_en ;always @(posedge clk_us or negedge sys_rst_n) beginif(~sys_rst_n) begindht11_en <= 1'd0 ;end else beginif(state_c == START) begindht11_en <= 1'b1 ;end else begindht11_en <= 1'b0 ;endendend// output signal// reg [19:0] data_out ,always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) begindata_out <= 20'd0 ;end else beginif(data_flag == 1'b0) begin // 显示湿度data_out <= data[31:24] * 16'd10 ;end else begindata_out <= data[15:8] * 16'd10 + data[3:0] ;endendend // reg sign always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) beginsign <= 1'b0 ;end else beginif(key_flag == 1'b1 && data[7] == 1'b1) beginsign <= 1'b1 ;end else beginsign <= 1'b0 ;endendend

endmodule其他模块都是之前的,就不发了。

相关文章:

FPGA project : dht11 温湿度传感器

没有硬件,过几天上板测试。 module dht11(input wire sys_clk ,input wire sys_rst_n ,input wire key ,inout wire dht11 ,output wire ds ,output wire …...

std::string和QString的区别以及互转

一 区别 1.字符编码支持 std::string:默认情况下,使用 ASCII 或 UTF-8 编码。不直接提供对多字节字符的内置支持。 QString:提供对多种字符编码的支持,包括 ASCII、UTF-8、UTF-16 等。它更适合处理国际化和本地化的字符串。 2.…...

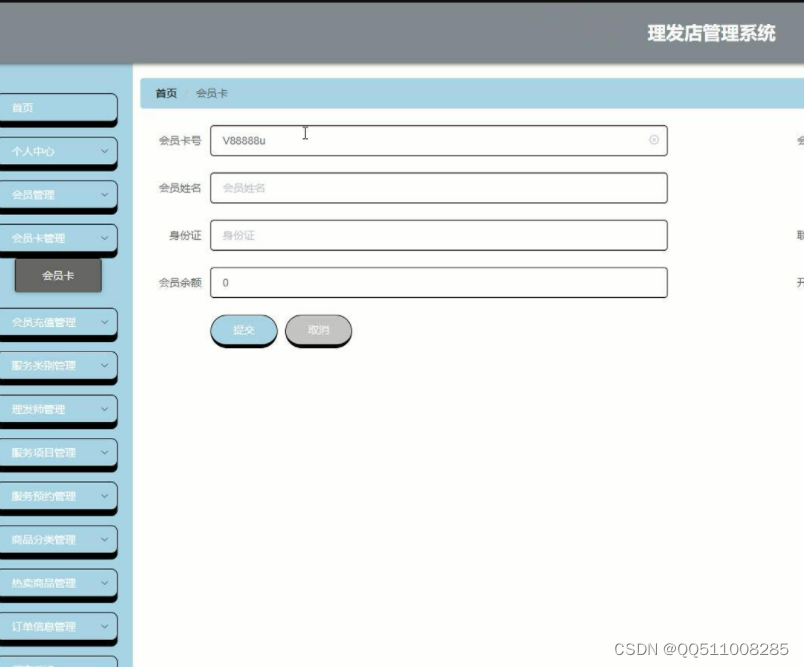

python+vue理发店管理系统

理发店管理系统主要实现角色有管理员和会员,管理员在后台管理用户表模块、token表模块、收藏表模块、商品分类模块、热卖商品模块、活动公告模块、留言反馈模块、理发师模块、会员卡模块、会员充值模块、会员模块、服务预约模块、服务项目模块、服务类别模块、热卖商品评论表模…...

基于微信小程序的个人健康管理系统的设计与实现(源码+lw+部署文档+讲解等)

前言 💗博主介绍:✌全网粉丝10W,CSDN特邀作者、博客专家、CSDN新星计划导师、全栈领域优质创作者,博客之星、掘金/华为云/阿里云/InfoQ等平台优质作者、专注于Java、小程序技术领域和毕业项目实战✌💗 👇🏻…...

共聚焦显微镜在化学机械抛光课题研究中的应用

两个物体表面相互接触即会产生相互作用力,研究具有相对运动的相互作用表面间的摩擦、润滑与磨损及其三者之间关系即为摩擦学,目前摩擦学已涵盖了化学机械抛光、生物摩擦、流体摩擦等多个细分研究方向,其研究的数值量级也涵盖了亚纳米到百微米…...

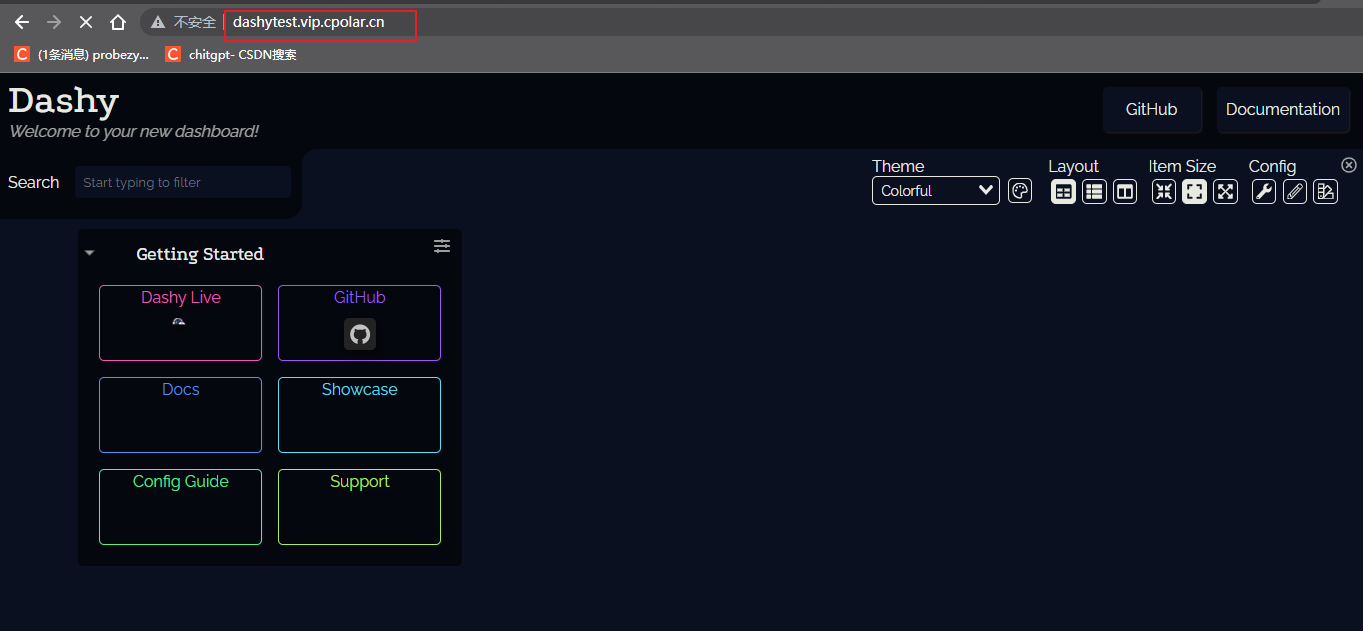

本地Linux 部署 Dashy 并远程访问

文章目录 简介1. 安装Dashy2. 安装cpolar3.配置公网访问地址4. 固定域名访问 转载自cpolar极点云文章:本地Linux 部署 Dashy 并远程访问 简介 Dashy 是一个开源的自托管的导航页配置服务,具有易于使用的可视化编辑器、状态检查、小工具和主题等功能。你…...

)

互联网摸鱼日报(2023-09-18)

互联网摸鱼日报(2023-09-18) 36氪新闻 最前线 | 号外电摩12.68万元起订,配16.9度一体压铸电池包 本周双碳大事:CCER交易管理办法获生态环境部原则通过;明阳斥资100亿元加码光伏项目;“全路程”获2亿元D轮融资 200亿,…...

Kotlin中函数的基本用法以及函数类型

函数的基本用法 1、函数的基本格式 2、函数的缺省值 可以为函数设置指定的初始值,而不必要传入值 private fun fix(name: String,age: Int 2){println(name age) }fun main(args: Array<String>) {fix("张三") }输出结果为:张三2 …...

在macOS使用VMware踩过的坑

目录 MAC提示将对您的电脑造成伤害/MAC OS 升级到10.15.3后vmware虚拟机黑屏 mac系统下,vm虚拟机提示打不开/dev/vmmon mac VMware Workstation 在此主机上不支持嵌套虚拟化 mac VMware清理虚拟机空间 MAC提示将对您的电脑造成伤害/MAC OS 升级到…...

构建健壮的Spring MVC应用:JSON响应与异常处理

目录 1. 引言 2. JSON 1. 轻量级和可读性 2. 易于编写和解析 3. 自描述性 4. 支持多种数据类型 5. 平台无关性 6. 易于集成 7. 社区支持和标准化 3. 高效处理异常 综合案例 异常处理方式一 异常处理方式二 异常处理方式三 1. 引言 探讨Spring MVC中关键的JSON数据…...

那些配置服务器踩的坑

最近在配置内网,无外网的服务器,纯纯记录一下踩得坑,希望看到的人不要再走这条弯路。 ------------------------------------------------------------------------------------------------------------------------------- 任务ÿ…...

交换机端口镜像详解

交换机端口镜像是一种网络监控技术,它允许将一个或多个交换机端口的网络流量复制并重定向到另一个端口上,以便进行流量监测、分析和记录。通过端口镜像,管理员可以实时查看特定端口上的流量,以进行网络故障排查、安全审计和性能优…...

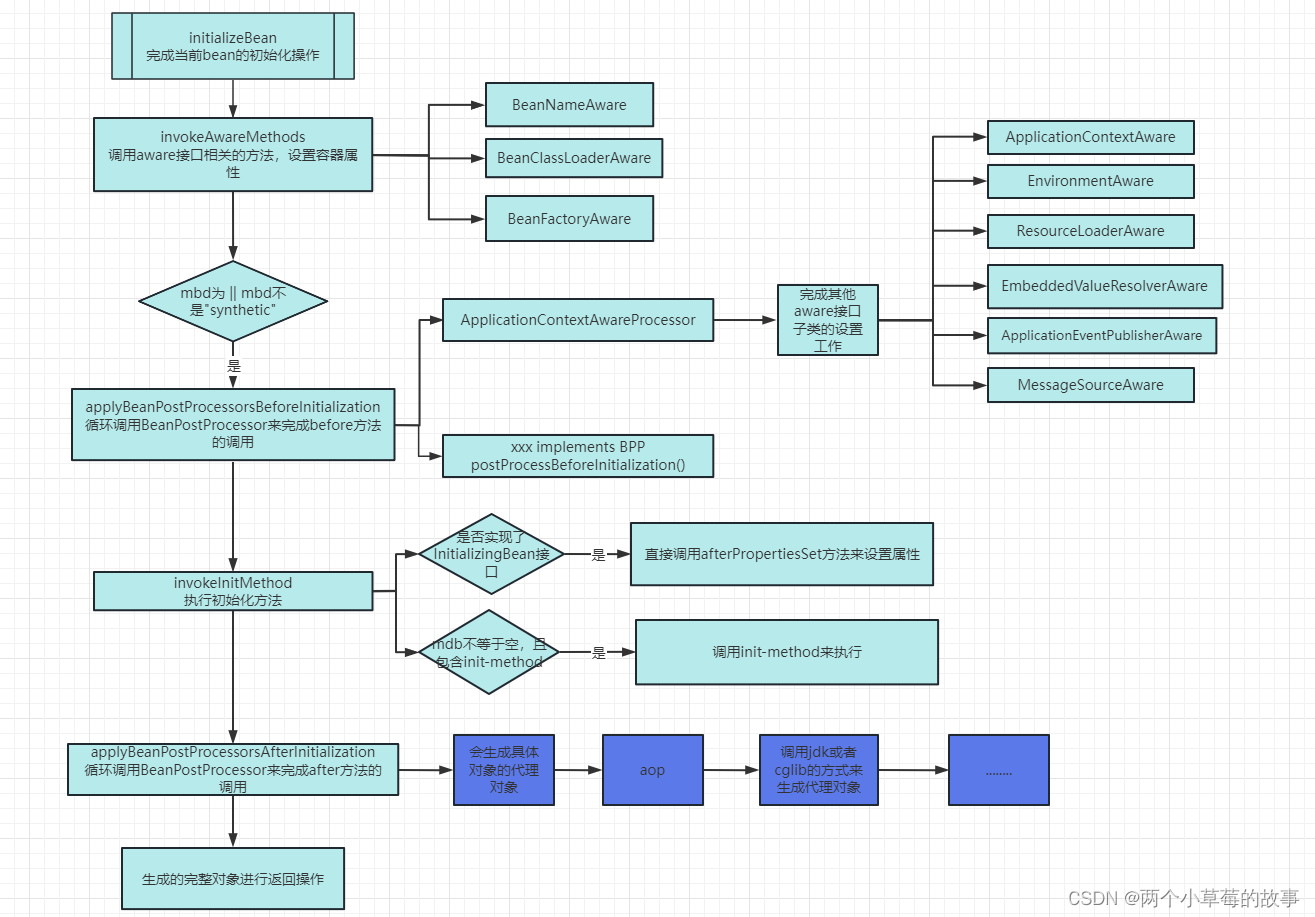

Spring源码分析(三) IOC 之 createBean()和doCreateBean()

a、在createBean中又是主要做了什么事情? 完成bean得创建,填充属性、循环依赖 、aop等一系列过程 1、createBean() 在createBean中主要干了3件事情 1、解析class -> resolveBeanClass() 2、验证及准备覆盖的方法,lookup-method replace-method -> …...

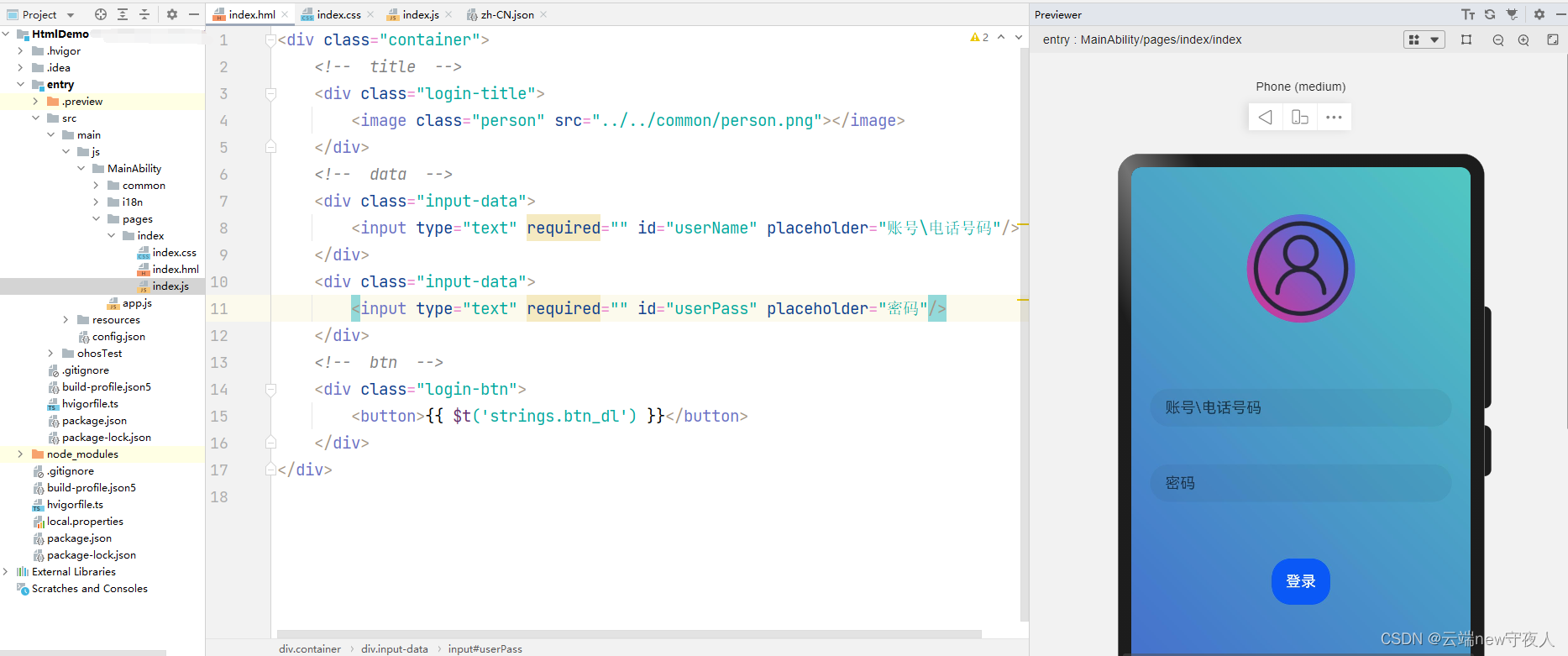

【鸿蒙(HarmonyOS)】UI开发的两种范式:ArkTS、JS(以登录界面开发为例进行对比)

文章目录 一、引言1、开发环境2、整体架构图 二、认识ArkUI1、基本概念2、开发范式(附:案例)(1)ArkTS(2)JS 三、附件 一、引言 1、开发环境 之后关于HarmonyOS技术的分享,将会持续使…...

Flink中的批和流

批处理的特点是有界、持久、大量,非常适合需要访问全部记录才能完成的计算工作,一般用于离线统计。 流处理的特点是无界、实时, 无需针对整个数据集执行操作,而是对通过系统传输的每个数据项执行操作,一般用于实时统计。 而在Flin…...

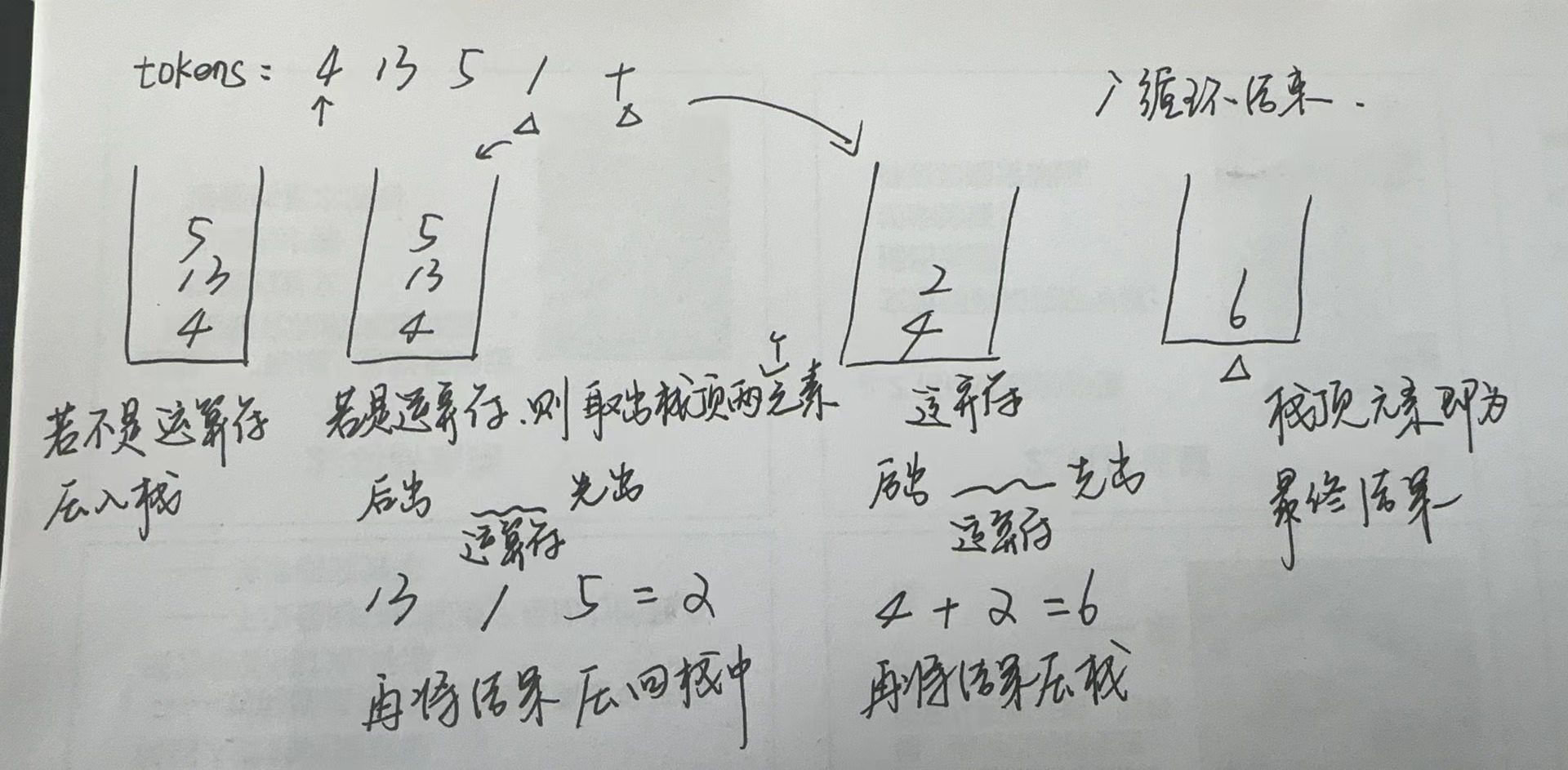

【LeetCode-中等题】150. 逆波兰表达式求值

文章目录 题目方法一:栈 题目 方法一:栈 class Solution {public int evalRPN(String[] tokens) {Deque<Integer> deque new LinkedList<>();String rpn "-*/";//符号集 用来判断扫描的是否为运算符int sum 0;for(int i 0 ; i…...

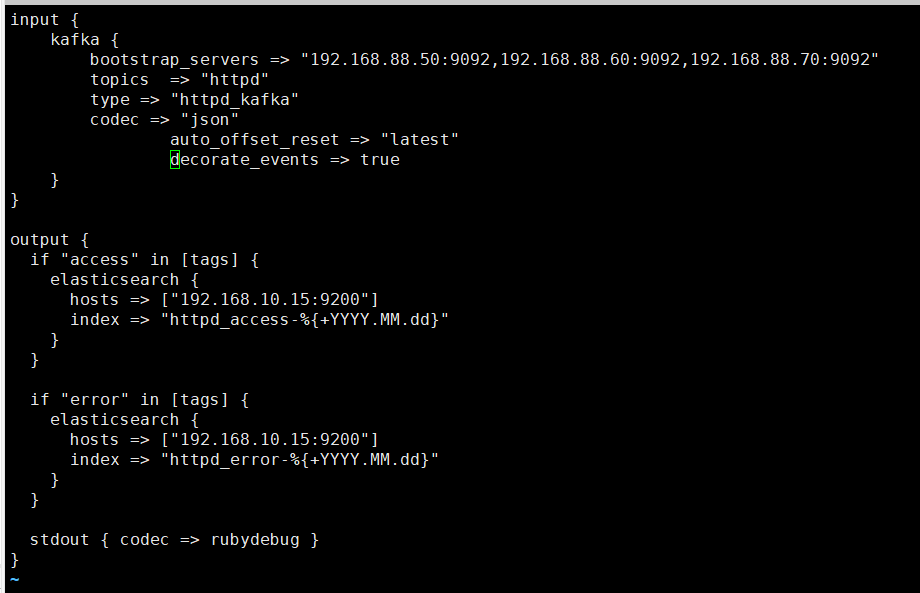

搭建ELK+Filebead+zookeeper+kafka实验

部署 Zookeeper 集群 准备 3 台服务器做 Zookeeper 集群 192.168.10.17 192.168.10.21 192.168.10.22 1.安装前准备 关闭防火墙 systemctl stop firewalld systemctl disable firewalld setenforce 0 安装 JDK yum install -y java-1.8.0-openjdk java-1.8.0-openjdk-…...

)

java专题练习(抢红包)

package 专题练习;import java.util.Random;public class grab_red_packet {/* 需求:直播抽奖,分别由{2,588,888,1000,10000}五个奖金,请用代码模拟抽奖,奖项出现顺序要随机且不重复打印效果:588元的奖金被抽出*///思路://1. 先用数组把奖金定义好//2. 用random方法给出随机数索…...

AVR 单片机 调试环境 JTAG MKII

注意 驱动 的厂家: 如果驱动备改变为其他厂家的驱动 就与 AVR Studio7不兼容 保证驱动选择正确是 能够使用硬件调试的关键 如果驱动不对,使用 USB驱动修改工具 修改 比如 UsbDriverTool.exe...

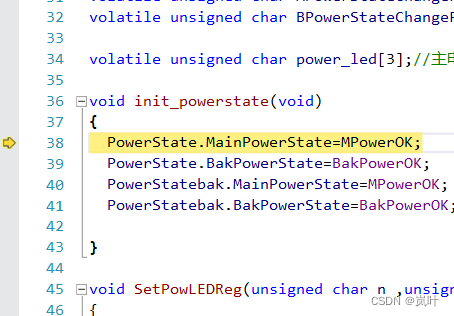

C++ - AVL树实现(下篇)- 调试小技巧

前言 本博客是 AVL树的下篇,上篇请看:C - AVL 树 介绍 和 实现 (上篇)_chihiro1122的博客-CSDN博客 上篇当中写插入操作,和其中涉及的 旋转等等细节,还有AVL树的大体框架。 调试小技巧 条件断点 在大项目…...

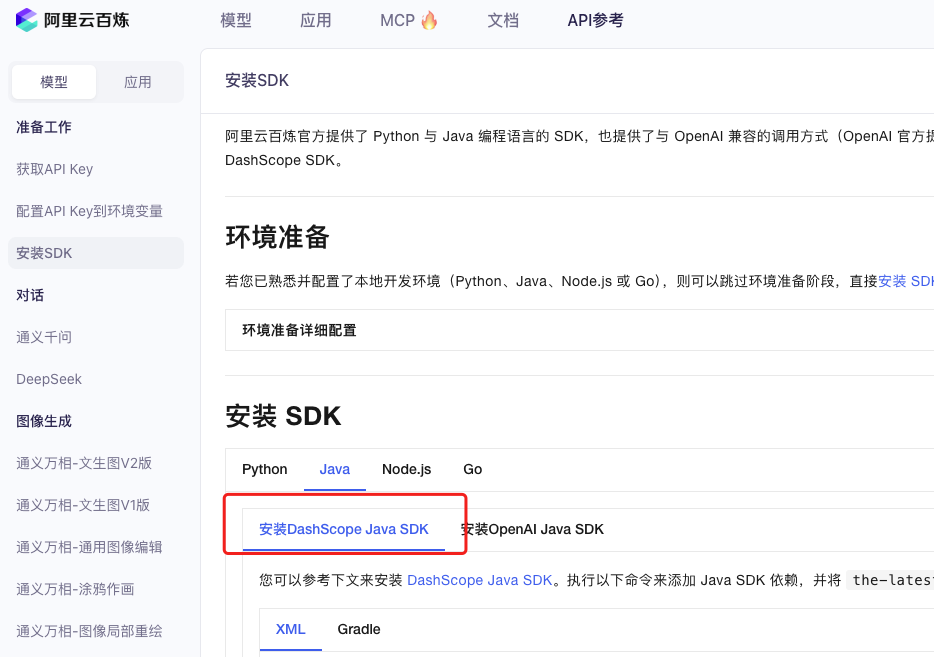

业务系统对接大模型的基础方案:架构设计与关键步骤

业务系统对接大模型:架构设计与关键步骤 在当今数字化转型的浪潮中,大语言模型(LLM)已成为企业提升业务效率和创新能力的关键技术之一。将大模型集成到业务系统中,不仅可以优化用户体验,还能为业务决策提供…...

TDengine 快速体验(Docker 镜像方式)

简介 TDengine 可以通过安装包、Docker 镜像 及云服务快速体验 TDengine 的功能,本节首先介绍如何通过 Docker 快速体验 TDengine,然后介绍如何在 Docker 环境下体验 TDengine 的写入和查询功能。如果你不熟悉 Docker,请使用 安装包的方式快…...

Admin.Net中的消息通信SignalR解释

定义集线器接口 IOnlineUserHub public interface IOnlineUserHub {/// 在线用户列表Task OnlineUserList(OnlineUserList context);/// 强制下线Task ForceOffline(object context);/// 发布站内消息Task PublicNotice(SysNotice context);/// 接收消息Task ReceiveMessage(…...

MongoDB学习和应用(高效的非关系型数据库)

一丶 MongoDB简介 对于社交类软件的功能,我们需要对它的功能特点进行分析: 数据量会随着用户数增大而增大读多写少价值较低非好友看不到其动态信息地理位置的查询… 针对以上特点进行分析各大存储工具: mysql:关系型数据库&am…...

在HarmonyOS ArkTS ArkUI-X 5.0及以上版本中,手势开发全攻略:

在 HarmonyOS 应用开发中,手势交互是连接用户与设备的核心纽带。ArkTS 框架提供了丰富的手势处理能力,既支持点击、长按、拖拽等基础单一手势的精细控制,也能通过多种绑定策略解决父子组件的手势竞争问题。本文将结合官方开发文档,…...

质量体系的重要

质量体系是为确保产品、服务或过程质量满足规定要求,由相互关联的要素构成的有机整体。其核心内容可归纳为以下五个方面: 🏛️ 一、组织架构与职责 质量体系明确组织内各部门、岗位的职责与权限,形成层级清晰的管理网络…...

将对透视变换后的图像使用Otsu进行阈值化,来分离黑色和白色像素。这句话中的Otsu是什么意思?

Otsu 是一种自动阈值化方法,用于将图像分割为前景和背景。它通过最小化图像的类内方差或等价地最大化类间方差来选择最佳阈值。这种方法特别适用于图像的二值化处理,能够自动确定一个阈值,将图像中的像素分为黑色和白色两类。 Otsu 方法的原…...

【算法训练营Day07】字符串part1

文章目录 反转字符串反转字符串II替换数字 反转字符串 题目链接:344. 反转字符串 双指针法,两个指针的元素直接调转即可 class Solution {public void reverseString(char[] s) {int head 0;int end s.length - 1;while(head < end) {char temp …...

:爬虫完整流程)

Python爬虫(二):爬虫完整流程

爬虫完整流程详解(7大核心步骤实战技巧) 一、爬虫完整工作流程 以下是爬虫开发的完整流程,我将结合具体技术点和实战经验展开说明: 1. 目标分析与前期准备 网站技术分析: 使用浏览器开发者工具(F12&…...

大模型多显卡多服务器并行计算方法与实践指南

一、分布式训练概述 大规模语言模型的训练通常需要分布式计算技术,以解决单机资源不足的问题。分布式训练主要分为两种模式: 数据并行:将数据分片到不同设备,每个设备拥有完整的模型副本 模型并行:将模型分割到不同设备,每个设备处理部分模型计算 现代大模型训练通常结合…...