【XILINX】记录ISE/Vivado使用过程中遇到的一些warning及解决方案

前言

XILINX/AMD是大家常用的FPGA,但是在使用其开发工具ISE/Vivado时免不了会遇到很多warning,(大家是不是发现程序越大warning越多?),并且还有很多warning根据消除不了,看着特心烦?

我这里汇总一些我遇到的和记录的,给大家参考,祝大家都是0warning选手。

列表

warning:HDLCompiler:1499 - "*\RAM_16b_1k.v" Line 39: Empty module remains a black box.

在《Xilinx ISE 5.x 使用详解》中翻到如下内容:P71

书上有云:

“IP核在综合时一般被认为是黑盒子(Black Box),综合器不对黑盒子做任何编译。将IP核加入工程有两种方法,一为在工程中新建Coregen IP类型资源,另一种是针对第三方综合工具而言,同时避免了在新工程中需要重新加入IP核资源的麻烦。也就是将IP核声明成黑盒子,具体操作时可以利用IP核生成时生成的仿真文件和IP核实例化文件(.veo,.vho),将仿真文件中的IP核的相关部分原封不动地拷贝到顶层文件中去,声明IP核模块,然后将实例化文件内容粘贴到模块的实例化部分。

然面,使用Synplify Pro等综合工具综合IP核等Xilinx硬件原语时,需要调用相应Xilinx器件的硬件原语声明文件。位于Synpliy\lib\Xilinx”子目录中的virtex.v/vhd,virtexe.v/vhd,virtex2.v/vhd,virtex2p.v/vhd等文件就是硬件原语声明文件。调用时用"include"命令。

(转帖)Xilinx CORE Generator心得 - cdy200824的日志 - 电子工程世界-论坛

在生成核开头的注释中加上如下注释

//synthesis attribute box_type "black_box"

warning: HDLCompiler:413 - "*\NUC_RAM_INT.v" Line 145: Result of 10-bit expression is truncated to fit in 9-bit target.

计数器的累加值前加上

cnt 1'b1;

"WARNING:Route:455 - CLK Net:trn_clk_OBUF may have excessive skew because 0 CLK pins and 1 NON_CLK pins failed to route using a CLK template."

Solution

This message informs the user that some loads on the clock net are not clock pins. Therefore, the clock template that is normally used to connect clock pins will not be used to connect the loads. A different routing that involves local routing will be used, potentially inducing some skew on the clock net.

Opening your design in FPGA EDITOR will allow you to see what loads are connected to the clock net, and the cause of the warnings. The amount of skew on the net will be reported in the Place and Route report. If the loads on the net shown in FPGA Editor are in accord with your design, the skew reported in the PAR report is not critical for the design, and the timing constraint requirement on that net is met, then this warning can be safely ignored.

实例原因:在代码中用到这样的语句时( aa’event and aa=’1’), aa 不是时钟信号,最多只是时钟信号产生的一类周期信号, aa 被作为了另一个 进程或模块的类似周期信号的作用。(我是在行场信号发生器中 出现的这样的问题,用产生的行同步信号(行同步信号是由全局时钟信号驱动产生的)再去驱动产生场同步信号,产生的场同步信号相对与输入的全局时钟,有一定 的倾斜)

"WARNING:Xst:647 - Input is never used."or"WARNING:Xst:648 - Output is never used."Solution This particular port has been declared in your HDL description, but does not drive or is not driven by any internal logic. Unused input ports will remain in the design, but they will be completely unconnected. If the port is not intended to be used, this message can be safely ignored. To avoid this message, remove any loadless or sourceless elements from your HDL description. Output ports will remain in the final netlist and will be driven by a logic 0. To avoid the message and to save the port resource, remove the unused output port from your HDL description.

实例原因:一般输入端口不要预留,即使不使用,在代码中定义的输入端口就一定要有输入的;而输出端口不用到的可以用 OPEN 封上,最常见的是在利用 DLL 和 DCM 时,CLK90,CLK180,CLK270 等一般不用,在端口连接的时候都用 OPEN 封上。

Place:866 - Not enough valid sites to place the following IOBs:

IO Standard: Name = LVCMOS25, VREF = NR, VCCO = 2.50, TERM = NONE, DIR = BIDIR, DRIVE_STR = 12IO

This may be due to either an insufficient number of sites available on the device, too many prohibited sites,or incompatible I/O Standards locked or range constrained to I/O Banks with valid sites.

This situation could possibly be resolved by one (or all) of the following actions:

a) Grouping IOBs of similar standards into a minimum amount of I/O Banks by using LOC or range constraints.

b) Maximizing available I/O Banks resources for special IOBs by choosing lower capacity I/O Banks if possible.

c) If applicable, decreasing the number of user prohibited sites or using a larger device.

Pack:1654 - The timing-driven placement phase encountered an error.

原因:

Pack:1654 - The timing-driven placement phase encountered an error.

这个错位是由上一个错位866引起的。

866是因为顶层文件中输出信号名mcb1_rzq,但是ddr_mig中rzq的输出信号写的是rzq,这就导致rzq的输出连不上。

Xst:1895 - Due to other FF/Latch trimming, FF/Latch (without init value) has a constant value of 0 in block . This FF/Latch will be trimmed during the optimization process.

Xst:1896 - Due to other FF/Latch trimming, FF/Latch has a constant value of 0 in block . This FF/Latch will be trimmed during the optimization process.

Xst:1898 - Due to constant pushing, FF/Latch is unconnected in block .

解决方案:(*KEEP = "TRUE" *)reg [23:0] data_white_ori;

这些寄存器可以设置保留不被优化。

Xst:2677 - Node of sequential type is unconnected in block .

解决办法:That warning is caused by lot of things.....

One main reason is if your outputs are not connected..ie if you are not reading the module outputs the ise optimisation step removes all signal inside your block and fire a 2677 warning...

check the module outputs。

方法1:把定义多的,用不到的寄存器位宽改成合适大小。

方法2:(*KEEP = "TRUE" *)reg [15:0] ram_rd_data_reg=16'b0; 定义初值,并保持不被优化 有些添加后会出现其他类型的警告

Xst:1710 - FF/Latch (without init value) has a constant value of 0 in block . This FF/Latch will be trimmed during the optimization process.

解决:(*KEEP = "TRUE" *)reg [ 7: 0] register_addr=8'b0;给初始值

HDLCompiler:634 - "*\rtl\ddr2_mig_6p.v" Line 365: Net does not have a driver.

线网没有驱动,那就给加个初值吧。

wire c3_p3_rd_clk=1'b0;

Xst:653 - Signal is used but never assigned. This sourceless signal will be automatically connected to value GND.

信号被用到,但是没有赋初值,所以默认接到GND

加初值,解决问题 assign rd_franum = 9'd0;

HDLCompiler:189 - "*\poc_framavg.v" Line 298: Size mismatch in connection of port . Formal port size is 9-bit while actual signal size is 16-bit.

给输入接口的位宽不对,addra定义为9bit,给了10bit,改变输入数据的位宽为9bit。

ERROR:HDLParsers:3562 - pepExtractor.prj line 1 Expecting 'vhd ' or 'verilog' keyword, found 'work'。 SolutionThis occurs when there are spaces embedded in the project location.

A bad example for project location would be:C:/Documents and Settings/User/example.ise.

A good example fpr project location would be:C:/ISE_tests/example.ise.

实例原因:在 ISE9.1 的版本里,在行为仿真和使用约束编辑器的时候会遇到,主要原因是工程的路径名里有空格一类的不被要求的非英文字符。

"ERROR:Xst:2587 Port of instance has different

type in definition " .

Solution

Compare the component declaration and instantiation to the submodule that is instantiated. When this error occurs, the declaration matches the instantiation, but does not match the port declarations of the submodule.Change either the port declarations in the declaration/instantiation pair or the submodule port declarations so that they match. This error is specific to the types of ports in the submodule.

实例原因:一般是子模块宣称和子模块的实体定义中端口的宽度和类型(in, out, inout,buffer)不匹配造成的。

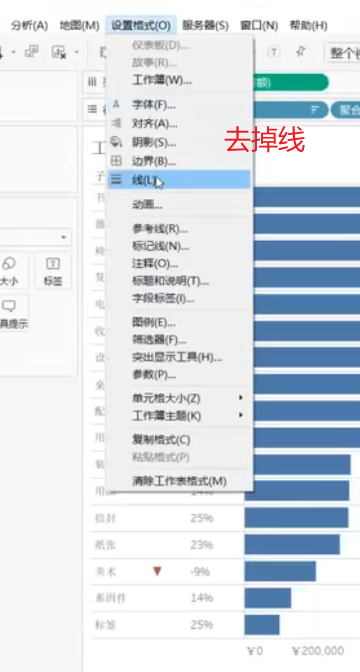

XST can generate very large log files for certain designs. In some cases, the generation of these log files can even cause an increase in runtime. How can I eliminate or hide certain frequently generated messages?

Solution

For users of XST via Project Navigator Starting in ISE 7.1i, Project Navigator has the capability to do message filtering for all Xilinx tools. Please refer to the Project Navigator help on how to use this method.

For users of XST via command line You can hide specific messages generated by XST at the HDL or Low-Level Synthesis steps in specific situations by using the XIL_XST_HIDEMESSAGES

environment variable. This environment variable can have one of the following values:

-- none: maximum verbosity. All messages are printed out. This is the default.

-- hdl_level: reduce verbosity during VHDL/Verilog Analysis and HDL Basic and Advanced Synthesis.

-- low_level: reduce verbosity during Low-level Synthesis

-- hdl_and_low_levels: reduce verbosity at all stages

The following messages are hidden when hdl_level or hdl_and_low_levels values are specified for the XIL_XST_HIDEMESSAGES environment variable:

WARNING:HDLCompilers:38 - design.v line xx Macro 'my_macro' redefined

NOTE: This message is issued by the Verilog compiler only.

WARNING:Xst:916 - design.vhd line xx: Delay is ignored for synthesis.

WARNING:Xst:766 - design.vhd line xx: Generating a Black Box for component comp.

Instantiating component comp from Library lib.

Set user-defined property "LOC = X1Y1" for instance inst in unit block.

Set user-defined property "RLOC = X1Y1" for instance inst in unit block.

Set user-defined property "INIT = 1" for instance inst in unit block.

Register reg1 equivalent to reg2 has been removed. The following messages are hidden when low_level or hdl_and_low_levels values are specified for the XIL_XST_HIDEMESSAGES environment variable:

WARNING:Xst:382 - Register reg1 is equivalent to reg2. Register reg1 equivalent to reg2 has been removed.

WARNING:Xst:1710 - FF/Latch reg (without init value) is constant in block block.

WARNING:Xst 1293 - FF/Latch reg is constant in block block.

WARNING:Xst:1291 - FF/Latch reg is unconnected in block block.

WARNING:Xst:1426 - The value init of the FF/Latch reg hinders the constant

cleaning in the block block. You could achieve better results by setting this init to value.

实例原因:在综合时,有很多的综合警告是可以忽略的,以上大致的罗列几项。

"WARNING:Xst:737 - Found n-bit latch for signal ." The listing for "n" is the width of the latch.If latch inference is intended, you can safely ignore this message.However, some inefficient coding styles can lead to accidental latch inference. You should analyze your code to see if this result is intended. The examples below illustrate how you can avoid latch inference.

实例原因:一般出现这样的问题都是代码出现了锁存器,因避免这样的代码写法,电路会不稳定,因利用触发器去寄存数据在时钟沿。

Solution 1

Include all possible cases in the case statement

Verilog

always @ (SEL or DIN1 or DIN2)begincase (SEL)2'b00 : DOUT2'b01 : DOUT2'b10 : DOUTendcaseend

VHDL

process (SEL, DIN1, DIN2)begincase SEL iswhen "00" => DOUTwhen "01" => DOUTwhen "10" => DOUTend case;end process;These two examples create latches because there is no provision for the

case when SEL = "11." To eliminate the latches, add another entry to deal

with this possibility.

Verilog

2'b11 : DOUT

VHDL

when "11" => DOUT

Using the "DEFAULT" (Verilog) or "WHEN OTHERS" (VHDL) clause always works,

but this can create extraneous logic. This is always the safest

methodology, but might produce a larger and slower design since any

unknown state has logic that is needed to bring it to a known state.

Solution 2

Assign to all the same outputs in each case.

Verilog

always @ (SEL or DIN1 or DIN2)begincase (SEL)2'b00 : DOUT2'b01 : DOUT2'b10 : DOUT2'b11 :beginDOUTTEMPendendcaseendVHDL

process (SEL, DIN1, DIN2)begincase SEL iswhen "00" => DOUTwhen "01" => DOUTwhen "10" => DOUTwhen "11" =>DOUTTEMPend case;end process;These examples infer latches because the "11" case assigns two outputs,

while the others assign only one. Looking at this case from TEMP's point

of view, only one of four possible cases are specified, so it is

incomplete. You can avoid this situation by assigning values to the exact

same list of outputs for each case.

Solution 3

Make sure any "if / else if" statements have a concluding "else" clause:

VHDL:

process (ge, din)beginif (ge = '1') thendout_aelsedout_a"else" statement.end if;end process;Verilog:

always @(ge or din)if (ge) dout_aelse dout_astatement.在不影响电路功能的情况下,要写完整的 if--else 语句。(对于时钟沿触发时,是不要 else

的)

ERROR:Place:1018 - A clock IOB / clock component pair have been found that are not

placed at an optimal clock IOB / clock site pair. The clock component is

placed at site . The IO component is placed at site

. This will not allow the use of the fast path between the IO and the Clock buffer. If

this sub optimal condition is acceptable for this design, you may use the

CLOCK_DEDICATED_ROUTE constraint in the .ucf file to demote this message to a

WARNING and allow your design to continue. However, the use of this override is highly

discouraged as it may lead to very poor timing results. It is recommended that this error

condition be corrected in the design. A list of all the COMP.PINs used in this clock

placement rule is listed below. These examples can be used directly in the .ucf file to

override this clock rule. < NET "Ref_Clk_p" CLOCK_DEDICATED_ROUTE = FALSE; >

解决方法: CLK16_inst 和 Ref_Clk 只都用 BUFG,或都用 IBUFG.(个人验证解决问题,但

不保证一定解决问题)

WARNING:PhysDesignRules:781 - PULLUP on an active net. PULLUP of comp

Flash_rst_n is set but the tri state is not configured. Your problem is in the source code,not your constraints. It's complainingthat you don't ever tristate the signal, either because your equations don't have a tristate term or because that term has been optimised away.

就是非输入加上拉后,没有配置三态。这是程序的出错,不关 constraints。

相关文章:

【XILINX】记录ISE/Vivado使用过程中遇到的一些warning及解决方案

前言 XILINX/AMD是大家常用的FPGA,但是在使用其开发工具ISE/Vivado时免不了会遇到很多warning,(大家是不是发现程序越大warning越多?),并且还有很多warning根据消除不了,看着特心烦? 我这里汇总一些我遇到的…...

Tableau进阶--Tableau数据故事慧(20)解构Tableau的绘图逻辑

官网介绍 官网连接如下: https://www.tableau.com/zh-cn tableau的产品包括如下: 参考:https://zhuanlan.zhihu.com/p/341882097 Tableau是功能强大、灵活且安全些很高的端到端的数据分析平台,它提供了从数据准备、连接、分析、协作到查阅…...

)

45.0/HTML 简介(详细版)

目录 45.1 互联网简介 45.2 网页技术与分类 45.3 HTML 简介 45.3.1 什么是 HTML?(面试题) 45.3.2 HTML 文件结构 45.3.3 HTML 语法 45.3.4 实例演练步骤(面试题) 45.4 head 中的常用标签 45.4.1 title 标记 45.4.2 meta 标记 45.4.3 45.4.4 45.4.4(面试题)总结: 45…...

Python 如何进行游戏开发?

游戏开发是一个广泛的领域,Python 作为一门灵活的编程语言,可以用于不同类型的游戏开发。以下是一些建议和步骤,帮助你开始使用 Python 进行游戏开发: 1、选择游戏开发库/框架: Pygame: Pygame 是一个用于…...

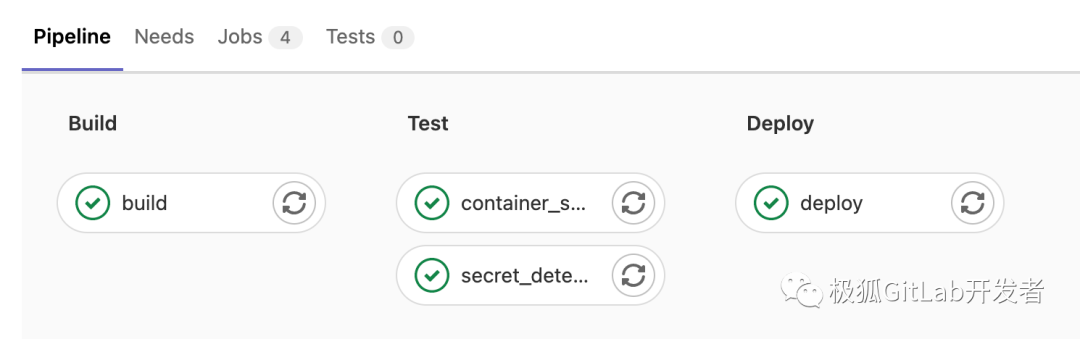

到底什么是DevOps

DevOps不是一组工具,也不是一个特定的岗位。在我看来DevOps更像是一种软件开发文化,一种实现快速交付能力的手段。 DevOps 强调的是高效组织团队之间如何通过自动化的工具协作和沟通来完成软件的生命周期管理,从而更快、更频繁地交付更稳定的…...

Keil生成bin文件

Keil生成bin文件_keil5生成bin文件-CSDN博客...

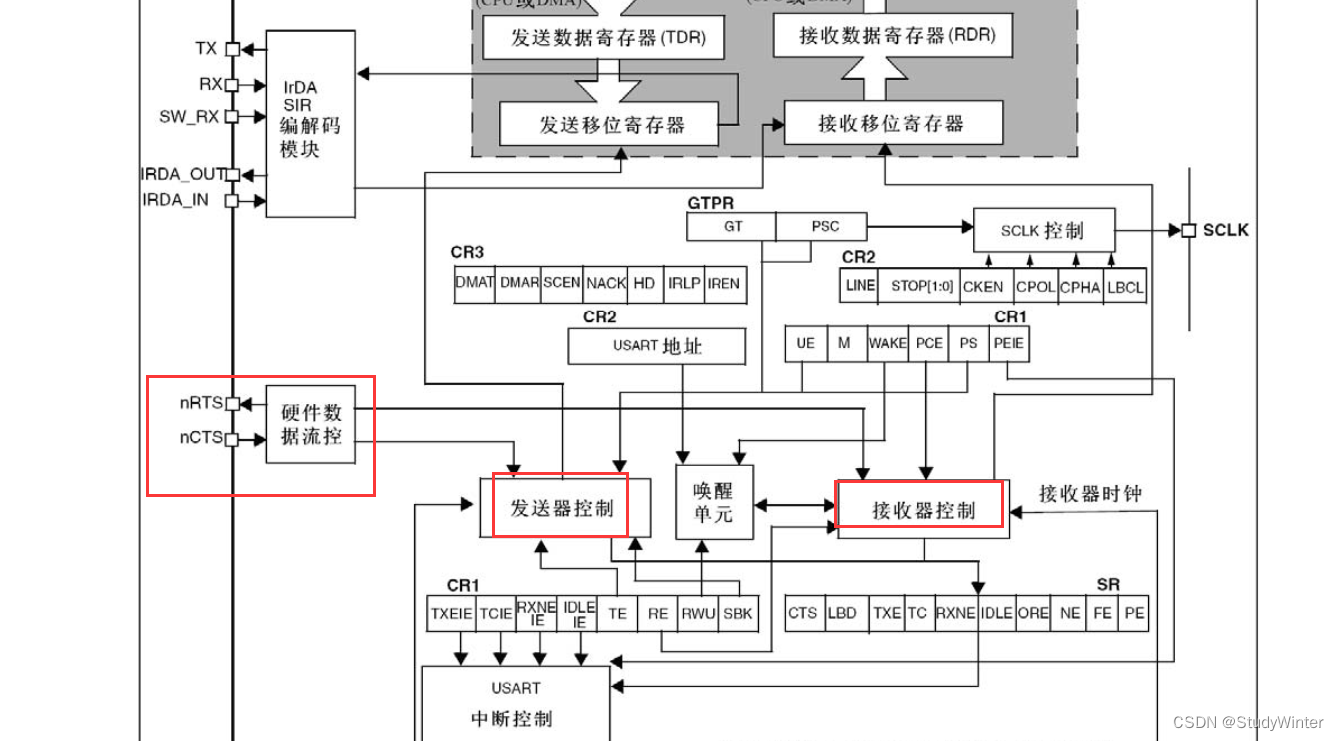

【STM32】USART串口协议

1 通信接口 通信的目的:将一个设备的数据传送到另一个设备,扩展硬件系统 通信协议:制定通信的规则,通信双方按照协议规则进行数据收发 USRT:TX是数据发送引脚,RX是数据接受引脚; I2C…...

淋雨试验箱

产品概述 KDZD-IPX34淋雨试验箱是对户外电子电工产品的防水性能测试的一种装置。该设备通过不同尺寸的喷嘴喷水,产品外壳表面淋水冲洗来检测防水性能。在测试物品时,将样品放在转台上,试验启动时,水流通过压力计和流量计控制水…...

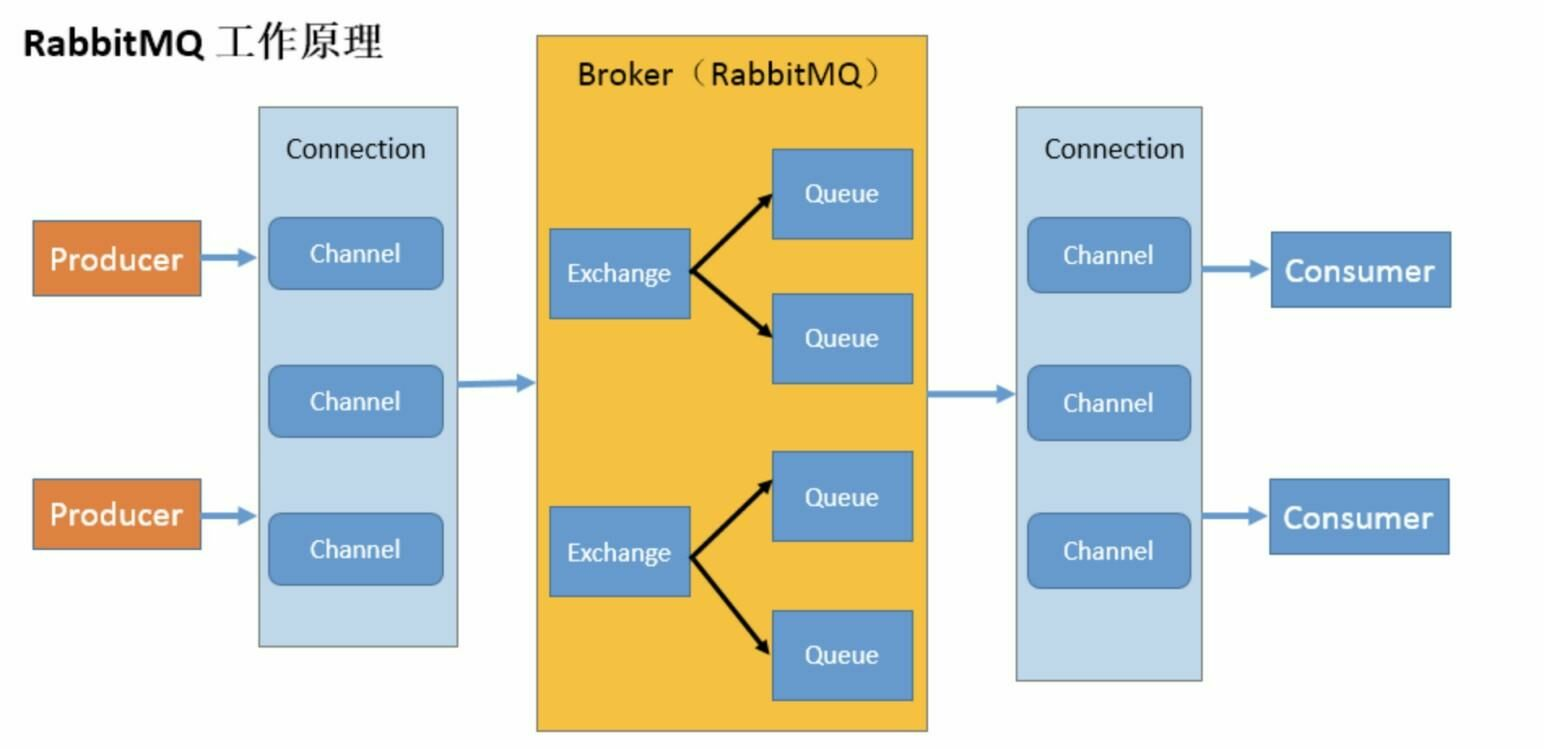

02-MQ入门之RabbitMQ简单概念说明

二:RabbitMQ 介绍 1.RabbitMQ的概念 RabbitMQ 是一个消息中间件:它接受并转发消息。你可以把它当做一个快递站点,当你要发送一个包裹时,你把你的包裹放到快递站,快递员最终会把你的快递送到收件人那里,按…...

敏感信息泄漏怎么破?来试试极狐GitLab 的密钥检测吧

前言 在应用程序开发过程中,一个很常见的问题就是:开发人员为了本地 debug 方便,会 hardcode 一些信息,比如连接数据库的用户名、密码、连接第三方 app 的 token、certificate 等,如果在提交代码的时候没有及时删除 ha…...

go学习之网络编程

文章目录 网络编程1、网络编程的基本介绍2.网络编程的基础知识1)协议(tcp/ip)2)OSI与TCP/ip参考模型3)ip地址4)端口(port)介绍5)tcp socket编程的客户端和服务器端 3.socket编程快速入门4.经典项目-海量用户即时通讯系…...

将数组中的数逆序存放

本题要求编写程序,将给定的n个整数存入数组中,将数组中的这n个数逆序存放,再按顺序输出数组中的元素。 输入格式: 输入在第一行中给出一个正整数n(1≤n≤10)。第二行输入n个整数,用空格分开。 输出格式:…...

Unity Web 浏览器-3D WebView中有关于CanvasWebViewPrefab

一、CanvasWebViewPrefab默认设置 这个是在2_CanvasWebViewDemo示例场景文件中可以可以查看得到,可以看出CanvasWebViewPrefab的默认配置如下。 二、Web 浏览器网页和Unity内置UI的渲染顺序 1、如果你勾选了以下这个Native 2D Mode选项的话,那么Unit…...

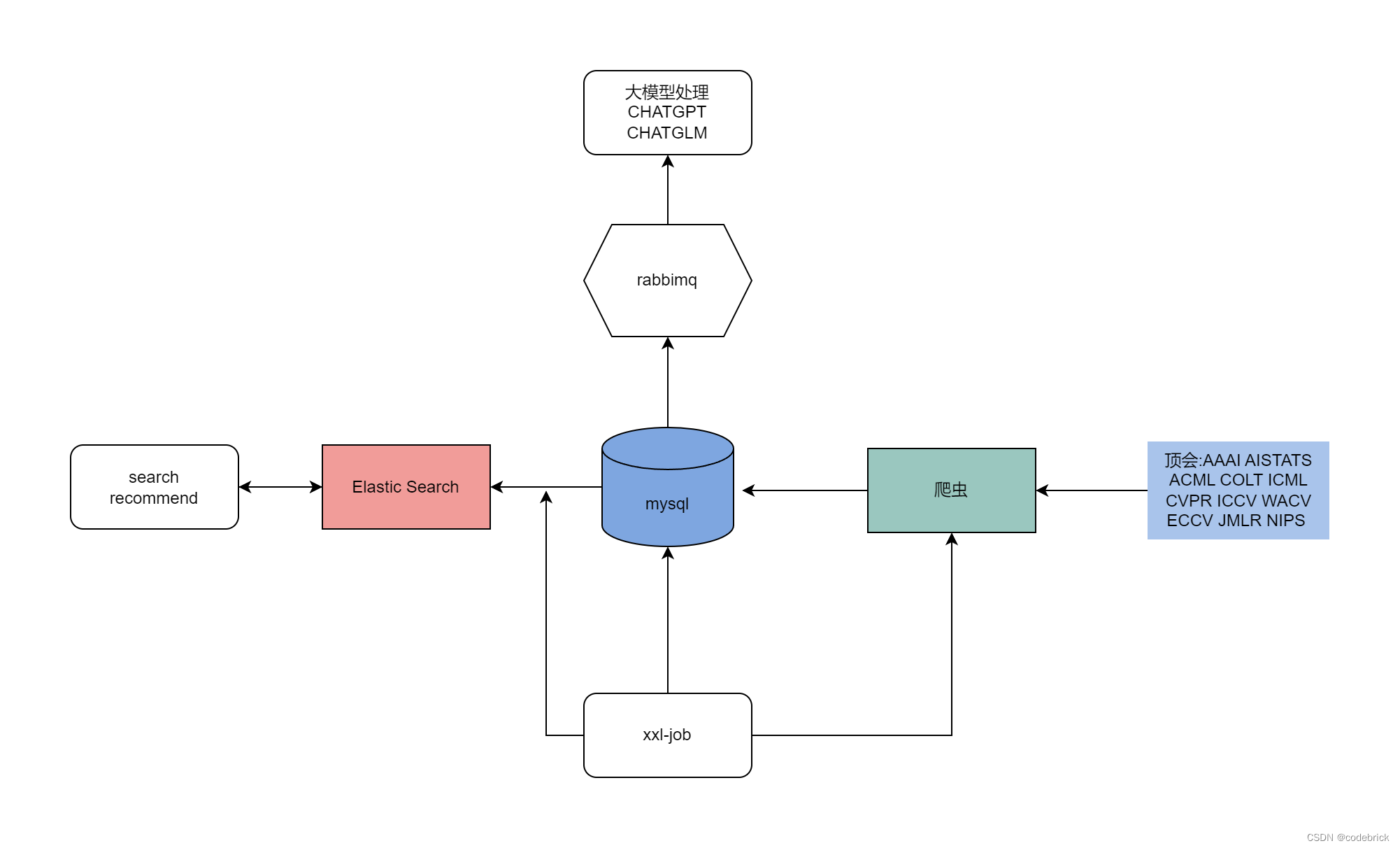

一款计算机顶会爬取解析系统 paper info

一款计算机顶会爬取解析系统 paper info 背景项目实现的功能 技术方案架构设计项目使用的技术选型 使用方法本地项目部署使用ChatGPT等大模型创建一个ChatGPT助手使用阿里云 顶会数据量 百度网盘pfd文件json文件 Q&A github链接 :https://github.com/codebricki…...

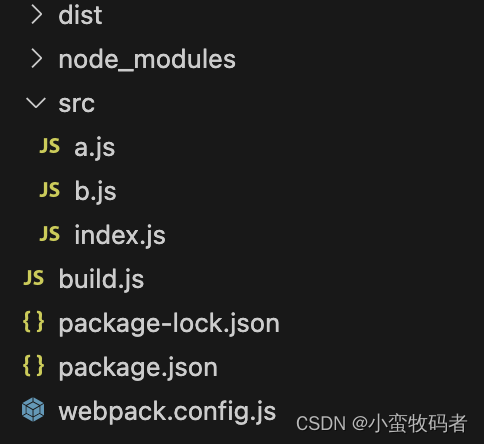

CommonJs模块化实现原理ES Module模块化原理

CommonJs模块化实现原理 首先看一个案例 初始化项目 npm init npm i webpack -D目录结构如下: webpack.config.js const path require("path"); module.exports {mode: "development",entry: "./src/index.js",output: {path: p…...

实验4.1 静态路由的配置

实验4.1 静态路由的配置 一、任务描述二、任务分析三、具体要求四、实验拓扑五、任务实施1.设置交换机和路由器的基本配置。2.使用display ip interface brief命令查看接口配置信息。3.配置静态路由,实现全网互通。 六、任务验收七、任务小结 一、任务描述 某公司刚…...

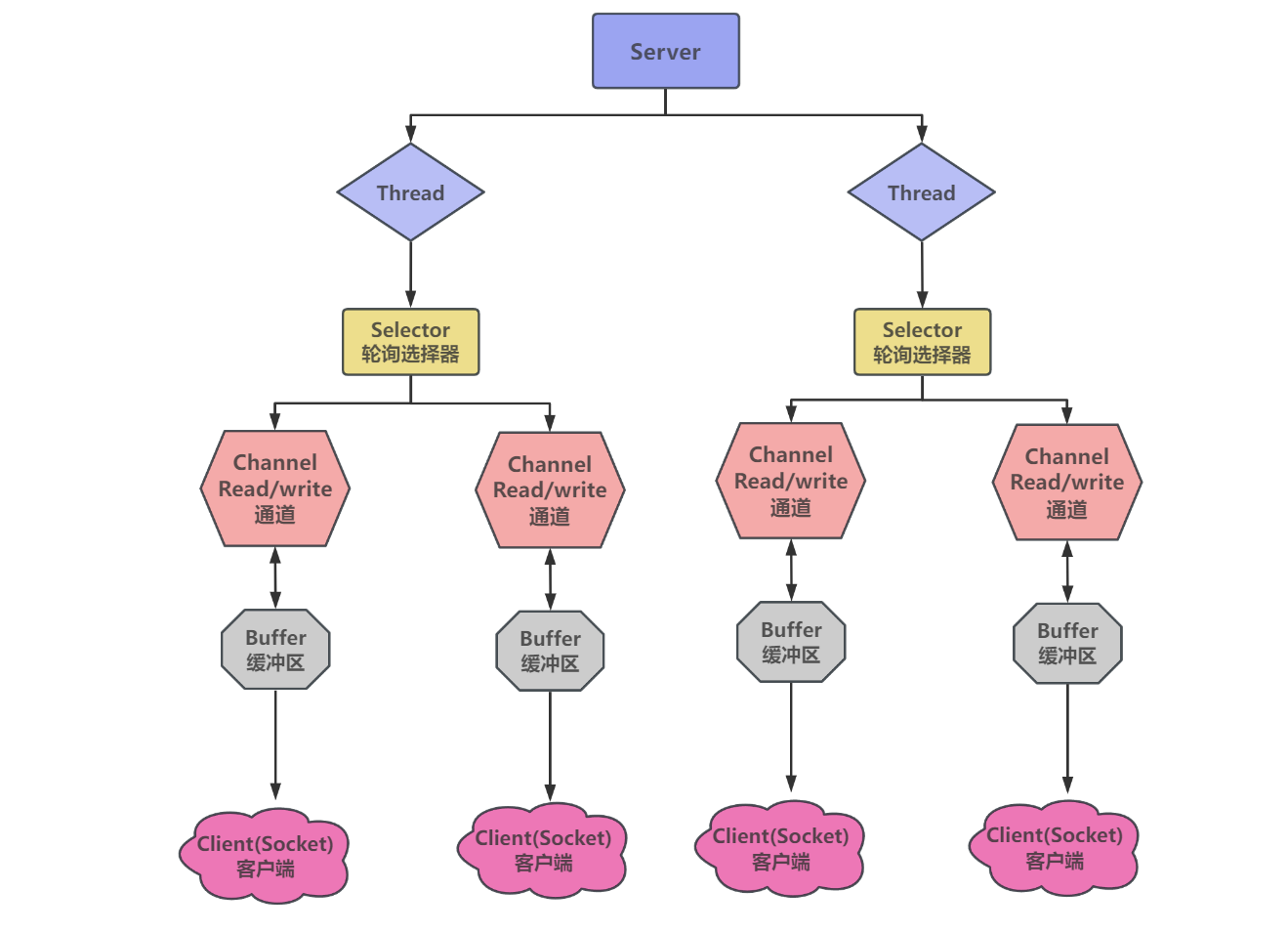

Java网络编程-深入理解BIO、NIO

深入理解BIO与NIO BIO BIO 为 Blocked-IO(阻塞 IO),在 JDK1.4 之前建立网络连接时,只能使用 BIO 使用 BIO 时,服务端会对客户端的每个请求都建立一个线程进行处理,客户端向服务端发送请求后,…...

ShenYu网关注册中心之HTTP注册原理

文章目录 1、客户端注册流程1.1、读取配置1.1.1、用于注册的 HttpClientRegisterRepository1.1.2、用于扫描构建 元数据 和 URI 的 SpringMvcClientEventListener 1.2、扫描注解,注册元数据和URI1.2.1、构建URI并写入Disruptor1.2.2、构建元数据并写入Disruptor1.2.…...

探索GameFi:区块链与游戏的未来融合

在过去的几年里,区块链技术逐渐渗透到各个领域,为不同行业带来了前所未有的变革。其中,游戏行业成为了一个引人注目的焦点,而这种结合被称为GameFi,即游戏金融。GameFi不仅仅是一个概念,更是一场区块链和游…...

Windows下使用CMake编译lua

Lua 是一个功能强大、高效、轻量级、可嵌入的脚本语言。它支持程序编程、面向对象程序设计、函数式编程、数据驱动编程和数据描述。 Lua的官方网站上只提供了源码,需要使用Make进行编译,具体的编译方法为 curl -R -O http://www.lua.org/ftp/lua-5.4.6.…...

进程与线程的核心区别:一篇看懂,告别混淆

在编程学习中,尤其是接触 C 多线程、操作系统相关知识时,进程(Process)和线程(Thread)是两个绕不开的概念。很多新手会把二者混为一谈,甚至像之前我被问到的那样,疑惑“进程是不是线…...

PHP电商系统扛不住大促?揭秘Redis+协程+异步队列三级熔断体系:3小时压测调优全记录

第一章:PHP电商系统扛不住大促?揭秘Redis协程异步队列三级熔断体系:3小时压测调优全记录面对双11级流量洪峰,某基于Laravel构建的PHP电商系统在5000 QPS下频繁出现502超时、库存扣减超卖、支付回调堆积等故障。我们未选择简单扩容…...

nli-distilroberta-base部署教程:Kubernetes集群中水平扩展NLI推理服务

nli-distilroberta-base部署教程:Kubernetes集群中水平扩展NLI推理服务 1. 项目概述 nli-distilroberta-base是一个基于DistilRoBERTa模型的自然语言推理(NLI)Web服务,专门用于判断两个句子之间的逻辑关系。这个轻量级模型继承了RoBERTa的强大性能&…...

物联网入门:从会动的小灯泡起步,普通人轻松上手,一篇文章快速入门

物联网开发入门指南:从零开始,手把手带你玩转物联网 一、物联网专业到底学些啥? 物联网专业听起来高大上,其实说白了,就是教你如何把身边的各种“东西”连上网,让它们能“说话”、能“听话”、能“思考”…...

DDD难落地?就让AI干吧! - cleanddd-skills介绍衔

AI训练存储选型的演进路线 第一阶段:单机直连时代 早期的深度学习数据集较小,模型训练通常在单台服务器或单张GPU卡上完成。此时直接将数据存储在训练机器的本地NVMe SSD/HDD上。 其优势在于IO延迟最低,吞吐量极高,也就是“数据离…...

WRKFLW性能优化:如何加速大型矩阵构建和工作流执行?

WRKFLW性能优化:如何加速大型矩阵构建和工作流执行? 【免费下载链接】wrkflw Validate and Run GitHub Actions locally. 项目地址: https://gitcode.com/gh_mirrors/wr/wrkflw WRKFLW是一个强大的GitHub Actions本地验证和运行工具,能…...

排序算法指南:归并排序

前言:归并排序的核心思想是利用分治法(Divide and Conquer)策略,它将一个大的问题分解成小的、容易解决的子问题,然后将子问题的解合并起来,从而得到原问题的解。一、归并排序的核心思想分(Divi…...

番茄小说下载器高效使用全攻略:轻松获取并管理你喜爱的小说

番茄小说下载器高效使用全攻略:轻松获取并管理你喜爱的小说 【免费下载链接】fanqienovel-downloader 下载番茄小说 项目地址: https://gitcode.com/gh_mirrors/fa/fanqienovel-downloader 在数字阅读时代,拥有一款可靠的小说下载工具能极大提升阅…...

drawio-desktop终极指南:免费跨平台打开和编辑Visio VSDX文件

drawio-desktop终极指南:免费跨平台打开和编辑Visio VSDX文件 【免费下载链接】drawio-desktop Official electron build of draw.io 项目地址: https://gitcode.com/GitHub_Trending/dr/drawio-desktop 还在为不同操作系统间的Visio文件兼容性问题而烦恼吗&…...

一站式机器学习环境配置:从操作系统到运行NLP-StructBERT

一站式机器学习环境配置:从操作系统到运行NLP-StructBERT 刚接触AI开发,是不是感觉第一步就卡住了?看着网上各种教程,又是装系统,又是配环境,还要搞什么CUDA驱动,头都大了。别担心,…...