【FPGA】Verilog:MSI/LSI 组合电路之解码器 | 多路分解器

写在前面:本章将理解编码器与解码器、多路复用器与多路分解器的概念,通过使用 Verilog 实现多样的解码器与多路分解器,通过 FPGA 并使用 Verilog 实现。

Ⅰ. 前置知识

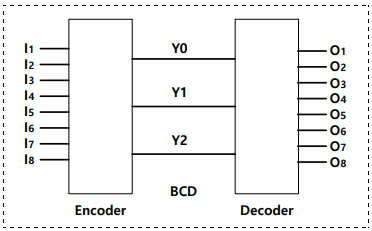

0x00 解码器与编码器(Decoder / Encoder)

解码器 (Decoder):执行转换和处理过程以将 Encoding 数据恢复到之前的电路。

编码器 (Encoder):将特定数据转换和处理为其他形式或格式的电路,以确保安全或缩小数据的大小。

编码器和解码器用于将任意两种符号体系相互转换。

0x01 多路复用器 MUX 与 多路分解器 DeMUX

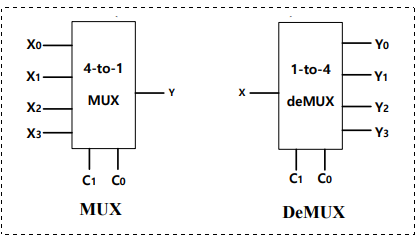

多路复用器 MUX (Multiplexer),能接收多个输入信号,按每个输入信号可恢复方式合成单个输出信号。复用器是一种综合系统,通常包含一定数目的数据输入,有一个单独的输出。

多路分解器 DeMUX (DeMultiplexer),是从一个输入接收资料,根据多条输出线中的输入,连接到预先选定的一条输出线的电路。

通常与带有 enable line 的解码器相同。

由于各自的功能特性,MUX 也被称为 Data Selctor(数据选择器),DeMUX 也被称为 Data Distributor(数据分配器)。

Ⅱ. 练习(Assignment)

0x00 2 to 4 Decoder

使用 AND 对电路进行 Verilog 编码,使用 NAND 结构对电路进行 Verilog 编码,通过 Verilog 的模拟结果完成真值表(2种),并比较两种形式的解码器。

💬 Design source:

`timescale 1ns / 1psmodule two_to_four_decoder(input A, B,output D1, D2, D3, D4);assign D1 = ~A&~B;assign D2 = ~A&B;assign D3 = A&~B;assign D4 = A&B;endmodule

💬 Testbench:

`timescale 1ns / 1psmodule two_to_four_decode_tb;

reg AA, BB;

wire D1, D2, D3, D4;two_to_four_decoder u_two_to_four_decoder(.A(AA),.B(BB),.D1(D2),.D2(D2),.D3(D3),.D4(D4));initial AA = 1'b0;

initial BB = 1'b0;always AA = #100 ~AA;

always BB = #200 ~BB;initial begin#1000$finish;

endendmodule

🚩 运行结果如下:

0x01 4 to 2 Encoder

使用 OR 对电路进行 Verilog 编码,通过 Verilog 的仿真结果完成真值表。

💬 Design source:

`timescale 1ns / 1psmodule four_to_two_encoder(input a, b, c, d,output e0, e1);assign e0 = a|b;assign e1 = a|c;endmodule

💬 Testbench:

`timescale 1ns / 1psmodule four_to_two_encoder_tb;

reg aa, bb, cc, dd;

wire e0, e1;four_to_two_encoder u_four_to_two_encoder(.a(aa),.b(bb),.c(cc),.d(dd),.e0(e0),.e1(e1));initial aa = 1'b0;

initial bb = 1'b0;

initial cc = 1'b0;

initial dd = 1'b0;always aa = #100 ~aa;

always bb = #200 ~bb;

always cc = #400 ~cc;

always dd = #800 ~dd;initial begin#1000$finish;

endendmodule

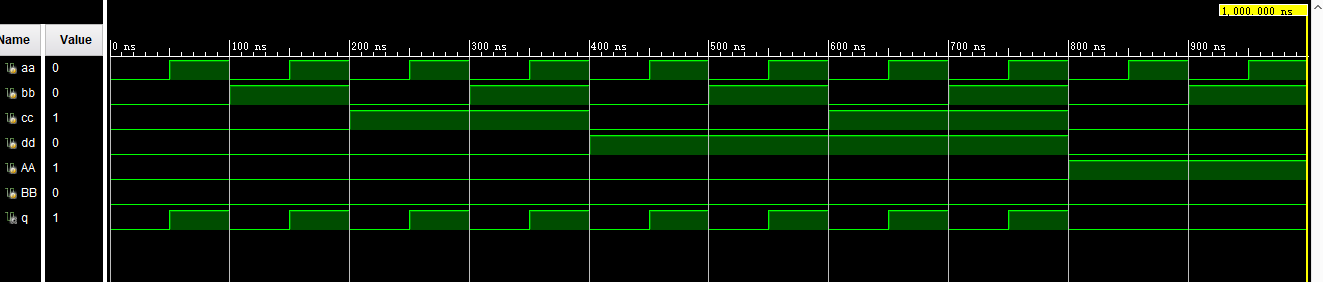

🚩 运行结果如下:

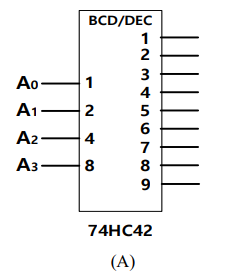

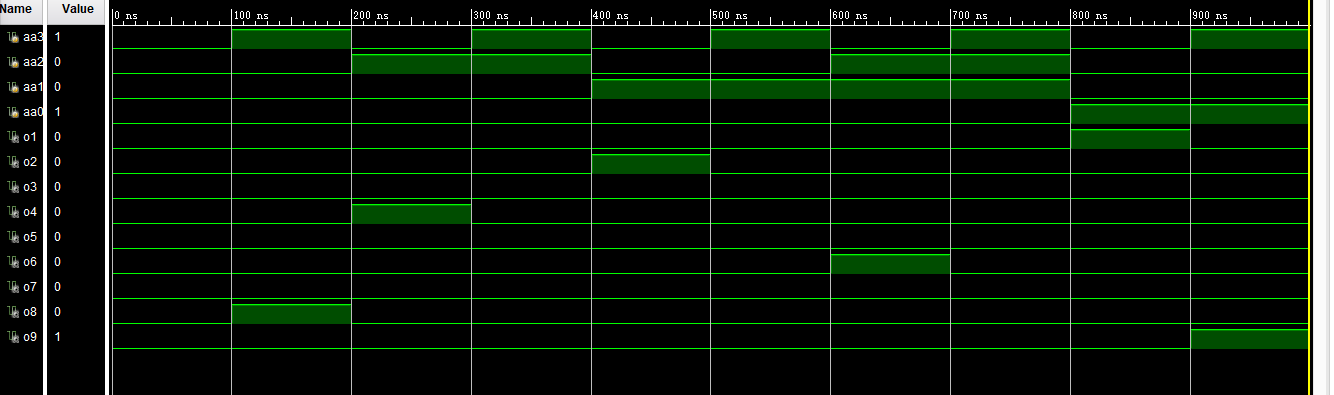

0x02 BCD to Decimal Decoder

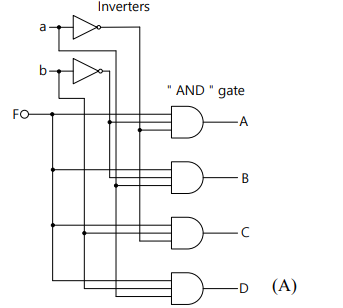

通过 Verilog 编码实现(A)的结构,通过 Verilog 的仿真结果完成真值表,并确认是否与理论中的Boolean 函数一致。

💬 Design source:

`timescale 1ns / 1psmodule bcd_decoder(input a3, a2, a1, a0,output o1, o2, o3, o4, o5, o6, o7, o8, o9);assign o1 = ~a3&~a2&~a1&a0;assign o2 = ~a3&~a2&a1&~a0;assign o3 = ~a3&~a2&a1&a0;assign o4 = ~a3&a2&~a1&~a0;assign o5 = ~a3&a2&~a1&a0;assign o6 = ~a3&a2&a1&~a0;assign o7 = ~a3&a2&a1&a0;assign o8 = a3&~a2&~a1&~a0;assign o9 = a3&~a2&~a1&a0;endmodule

💬 Testbench:

`timescale 1ns / 1psmodule bcd_decoder_tb;

reg aa3, aa2, aa1, aa0;

wire o1, o2, o3, o4, o5, o6, o7, o8, o9;bcd_decoder u_bcd_decoder(.a3(aa3),.a2(aa2),.a1(aa1),.a0(aa0),.o1(o1),.o2(o2),.o3(o3),.o4(o4),.o5(o5),.o6(o6),.o7(o7),.o8(o8),.o9(o9));initial aa3 = 1'b0;

initial aa2 = 1'b0;

initial aa1 = 1'b0;

initial aa0 = 1'b0;always aa3 = #100 ~aa3;

always aa2 = #200 ~aa2;

always aa1 = #400 ~aa1;

always aa0 = #800 ~aa0;initial begin#1000$finish;

endendmodule

🚩 运行结果如下:

0x03 4 to 1 line MUX

以(A)的结构对电路进行 Verilog 编码,通过 Verilog 的仿真结果完成真值表。并确认是否与理论中的 Boolean 函数一致。

💬 Design source:

`timescale 1ns / 1psmodule four_to_one_mux(input a, b, c, d, A, B,output q);assign q = (a&~B&~A)|(b&B&~A)|(c&~B&A)|(d&B&A);endmodule

💬 Testbench:

`timescale 1ns / 1psmodule four_to_one_mux_tb;

reg aa, bb, cc, dd, AA, BB;

wire q;four_to_one_mux u_four_to_one_mux(.a(aa),.b(bb),.c(cc),.d(dd),.A(AA),.B(BB),.q(q));initial aa = 1'b0;

initial bb = 1'b0;

initial cc = 1'b0;

initial dd = 1'b0;

initial AA = 1'b0;

initial BB = 1'b0;always aa = #50 ~aa;

always bb = #100 ~bb;

always cc = #200 ~cc;

always dd = #400 ~dd;

always AA = #800 ~AA;

always BB = #1600 ~BB;initial begin#2000$finish;

endendmodule

🚩 运行结果如下:

0x04 1 to 4 line deMUX

以(A)的结构对电路进行 Verilog 编码,通过 Verilog 的仿真结果完成真值表,确认是否与理论中的 Boolean 函数一致。

💬 Design source:

`timescale 1ns / 1psmodule one_to_four_mux(input A, B, f,output a, b, c, d);assign a = f&(~A&~B);assign b = f&(~A&B);assign c = f&(A&~B);assign d = f&(A&B);endmodule

💬 Testbench:

`timescale 1ns / 1psmodule one_to_four_mux_tb;

reg AA, BB, ff;

wire a, b, c, d;one_to_four_mux u_one_to_four_mux(.A(AA),.B(BB),.f(ff),.a(a),.b(b),.c(c),.d(d));initial AA = 1'b0;

initial BB = 1'b0;

initial ff = 1'b0;always AA = #100 ~AA;

always BB = #200 ~BB;

always ff = #400 ~ff;initial begin#1000$finish;

endendmodule

🚩 运行结果如下:

📌 [ 笔者 ] Foxny,Akam

📃 [ 更新 ] 2023.3.5

❌ [ 勘误 ] /* 暂无 */

📜 [ 声明 ] 由于作者水平有限,本文有错误和不准确之处在所难免,本人也很想知道这些错误,恳望读者批评指正!| 📜 参考资料 Introduction to Logic and Computer Design, Alan Marcovitz, McGrawHill, 2008 Microsoft. MSDN(Microsoft Developer Network)[EB/OL]. []. . 百度百科[EB/OL]. []. https://baike.baidu.com/. |

相关文章:

【FPGA】Verilog:MSI/LSI 组合电路之解码器 | 多路分解器

写在前面:本章将理解编码器与解码器、多路复用器与多路分解器的概念,通过使用 Verilog 实现多样的解码器与多路分解器,通过 FPGA 并使用 Verilog 实现。 Ⅰ. 前置知识 0x00 解码器与编码器(Decoder / Encoder) 解码器…...

深入理解JDK动态代理原理,使用javassist动手写一个动态代理框架

文章目录一、动手实现一个动态代理框架1、初识javassist2、使用javassist实现一个动态代理框架二、JDK动态代理1、编码实现2、基本原理(1)getProxyClass0方法(2)总结写在后面一、动手实现一个动态代理框架 1、初识javassist Jav…...

一、策略模式的使用

1、策略模式定义: 策略模式(Strategy Pattern)定义了一组策略,分别在不同类中封装起来,每种策略都可以根据当前场景相互替换,从而使策略的变化可以独立于操作者。比如我们要去某个地方,会根据距…...

Verilog使用always块实现时序逻辑

这篇文章将讨论 verilog 中一个重要的结构---- always 块(always block)。verilog 中可以实现的数字电路主要分为两类----组合逻辑电路和时序逻辑电路。与组合逻辑电路相反,时序电路电路使用时钟并一定需要触发器等存储元件。因此,…...

面向对象设计模式:行为型模式之迭代器模式

一、迭代器模式,Iterator Pattern aka:Cursor Pattern 1.1 Intent 意图 Provide a way to access the elements of an aggregate object sequentially without exposing its underlying representation. 提供一种按顺序访问聚合对象的元素而不公开其基…...

如何快速在企业网盘中找到想要的文件

现在越来越多的企业采用企业网盘来存储文档和资料,而且现在市面上的企业网盘各种各样。在使用企业网盘过程中,很多用户会问到企业网盘中如何快速搜索文件的问题。但是无论是“标签”功能还是普通的“关键词搜索”功能,都是单层级的࿰…...

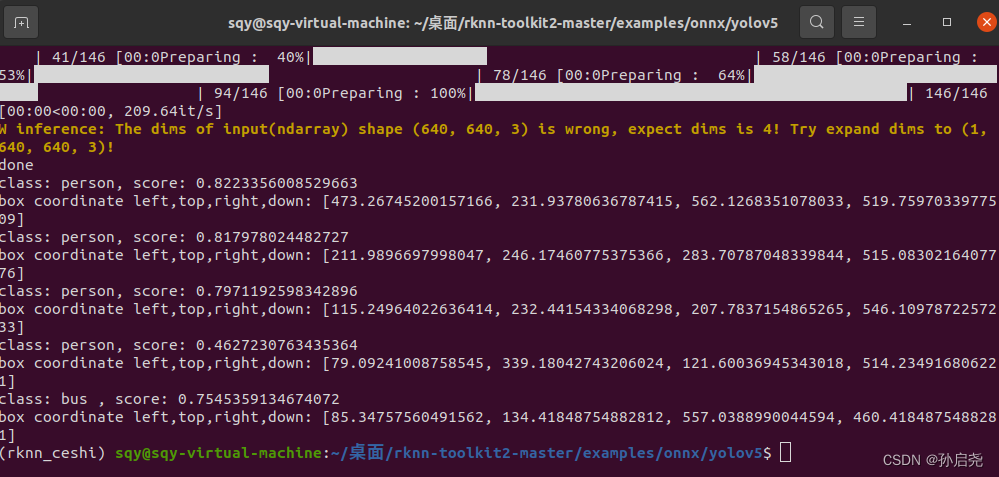

香橙派5使用NPU加速yolov5的实时视频推理(二)

三、将best.onnx转为RKNN格式 这一步就需要我们进入到Ubuntu20.04系统中了,我的Ubuntu系统中已经下载好了anaconda,使用anaconda的好处就是可以方便的安装一些库,而且还可以利用conda来配置虚拟环境,做到环境与环境之间相互独立。…...

)

算法练习-二分查找(一)

算法练习-二分查找 1 代码实现 1.1 非递归实现 public int bsearch(int[] a, int n, int value) {int low 0;int high n - 1;while (low < high) {int mid (low high) / 2;if (a[mid] value) {return mid;} else if (a[mid] < value) {low mid 1} else {high …...

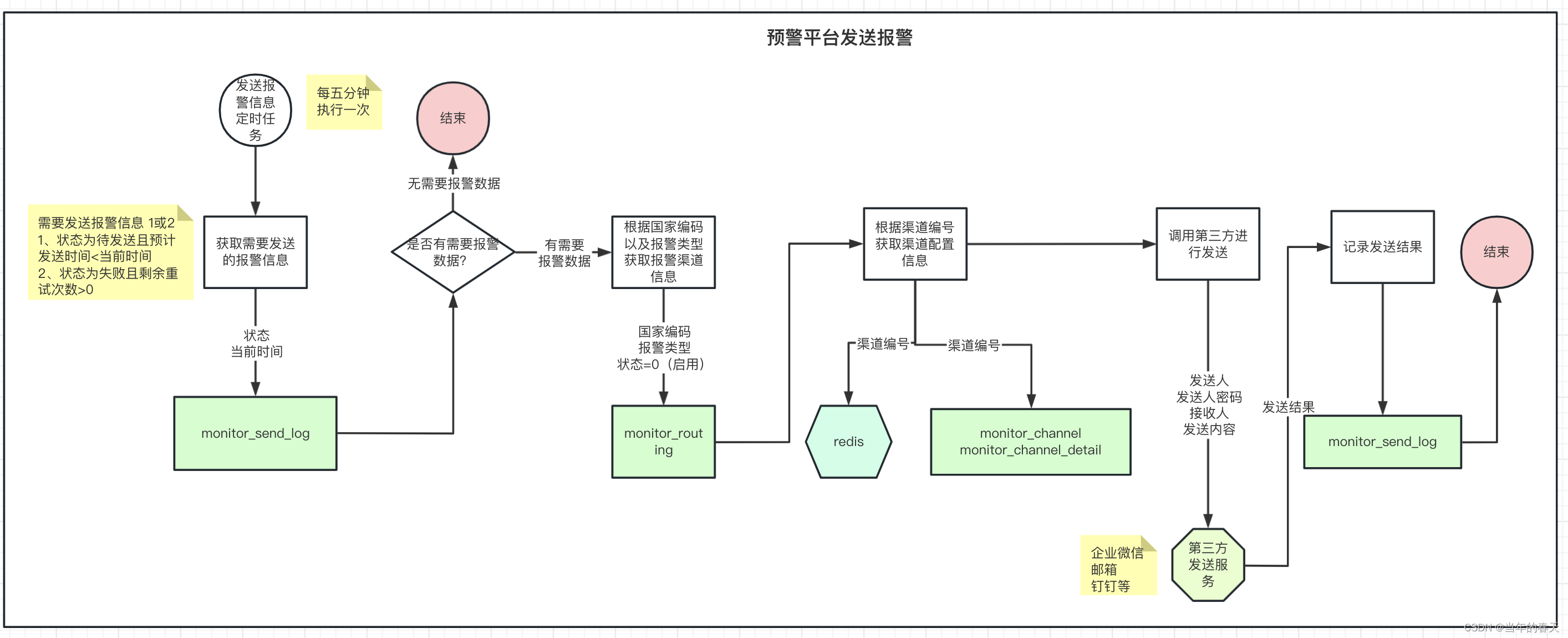

通用业务平台设计(五):预警平台建设

前言 在上家公司,随着业务的不断拓展(从支持单个国家单个主体演变成支持多个国家多个主体),对预警的诉求越来越紧迫;如何保障业务的稳定性那?预警可以帮我们提前甄别风险,从而让我们可以在风险来临前将其消灭ÿ…...

Windows openssl-1.1.1d vs2017编译

工具: 1. perl(https://strawberryperl.com/) 2. nasm(https://nasm.us/) 3. openssl源码(https://www.openssl.org/) 可以自己去下载 或者我的网盘提供下载: 链接:…...

【深蓝学院】手写VIO第2章--IMU传感器--笔记

0. 内容 1. 旋转运动学 角速度的推导: 左ω∧\omega^{\wedge}ω∧,而ω\omegaω是在z轴方向运动,θ′[0,0,1]T\theta^{\prime}[0,0,1]^Tθ′[0,0,1]T 两边取模后得到结论: 线速度大小半径 * 角速度大小 其中,对旋转矩…...

网络基础(二)之HTTP与HTTPS

应用层 再谈 "协议" 协议是一种 "约定". socket api的接口, 在读写数据时, 都是按 "字符串" 的方式来发送接收的. 如果我们要传输一些"结构化的数据" 怎么办呢? 为什么要转换呢? 如果我们将struct message里面的信息…...

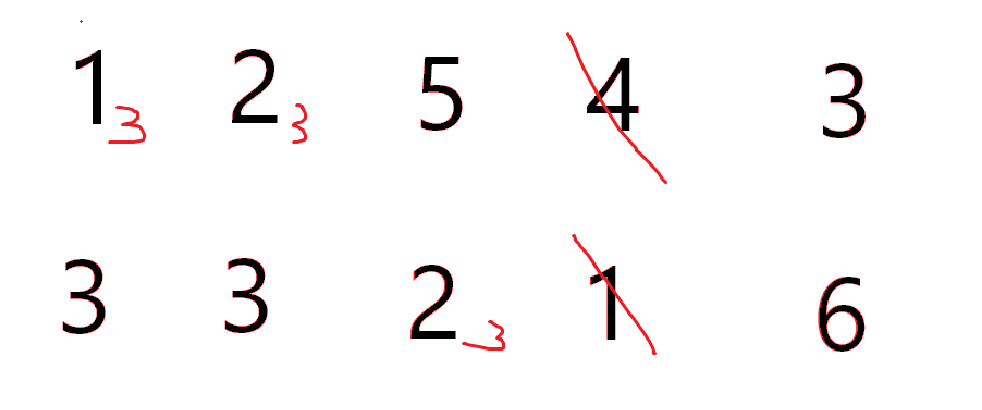

Python每日一练(20230306)

目录 1. 翻转二叉树 ★★ 2. 最长公共前缀 ★★ 3. 2的幂 ★ 1. 翻转二叉树 翻转一棵二叉树。 示例 1: 输入: 4/ \2 7/ \ / \ 1 3 6 9 输出: 4/ \7 2/ \ / \ 9 6 3 1示例 2: 输入: 1…...

C/C++每日一练(20230305)

目录 1. 整数分解 ☆ 2. 二叉树的最小深度 ★★ 3. 找x ★★ 1. 整数分解 输入一个正整数,将其按7进制位分解为各乘式的累加和。 示例 1: 输入:49 输出:497^2示例 2: 输入:720 输出:720…...

SAS字典的应用

数据字典中常用信息检索DICTIONARY.COLUMNS、DICTIONARY.TABLES以及DICTIONARY.MEMBERS等字典表的内容。在编程实践中,如何以SAS字典表来提高效率。 1、DICTIONARY.COLUMNS 对于当前SAS任务的全部数据集,表格DICTIONARY.COLUMNS包含了诸如变量的名称、类…...

Mysql中的函数和触发器

函数函数是什么?多用于查询语句,实现了某种功能;用途与存储过程不同,但语法是类似的;函数语法create function 函数名([参数列表]) returns 数据类型 begin DECLARE 变量; sql 语句; return 值; end; 设置函…...

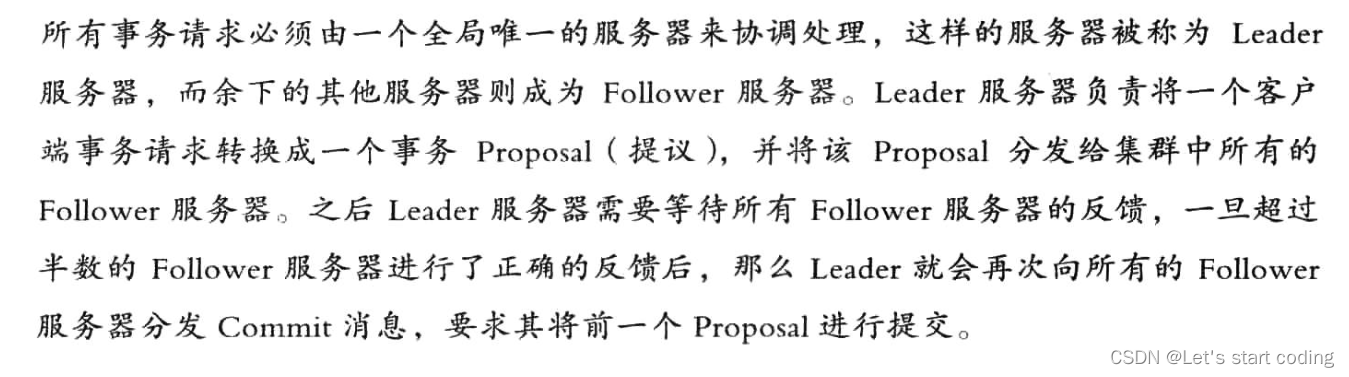

分布式架构之(Zookeeper原理)

Zookeeper是一个典型的分布式数据一致性的结局方案,分布式应用程序可以基于它实现注入数据发布、订阅、负载均衡、命名服务、分布式协调/通知、集群管理、Master选举、分布式锁和分布式队列等功能, Zookeeper可以保证如下分布式一致性特性: 顺…...

Java框架学习 | MyBatis

问题导向学习MyBatis 为什么要有MyBatis框架? 避免Java开发者直接使用 JDBC重复做数据库操作,同时更便捷地实现想要的数据库相关功能,让Java专注于开发业务。 MyBatis框架如何实现该目的? MyBatis是半自动化持久层ORM框架&#x…...

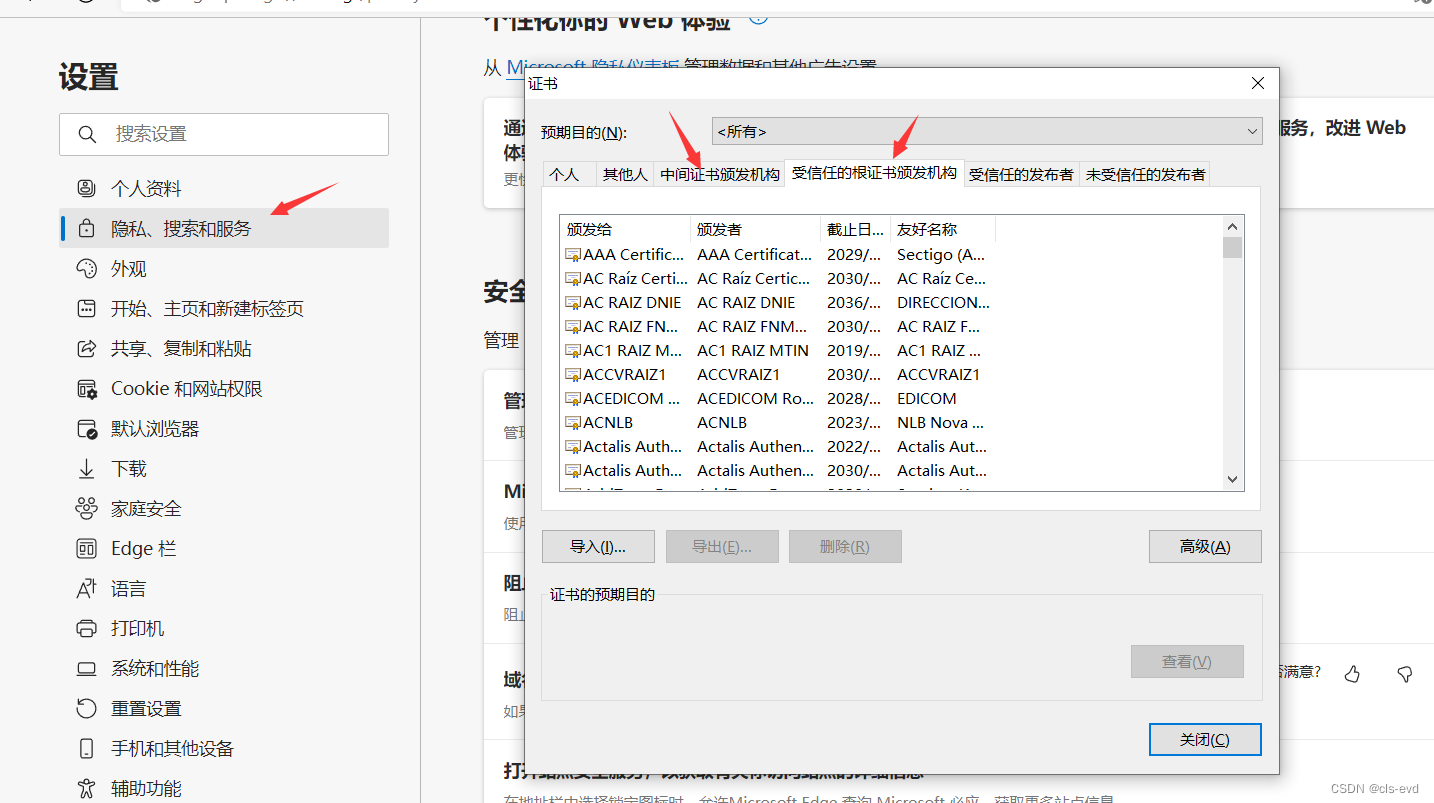

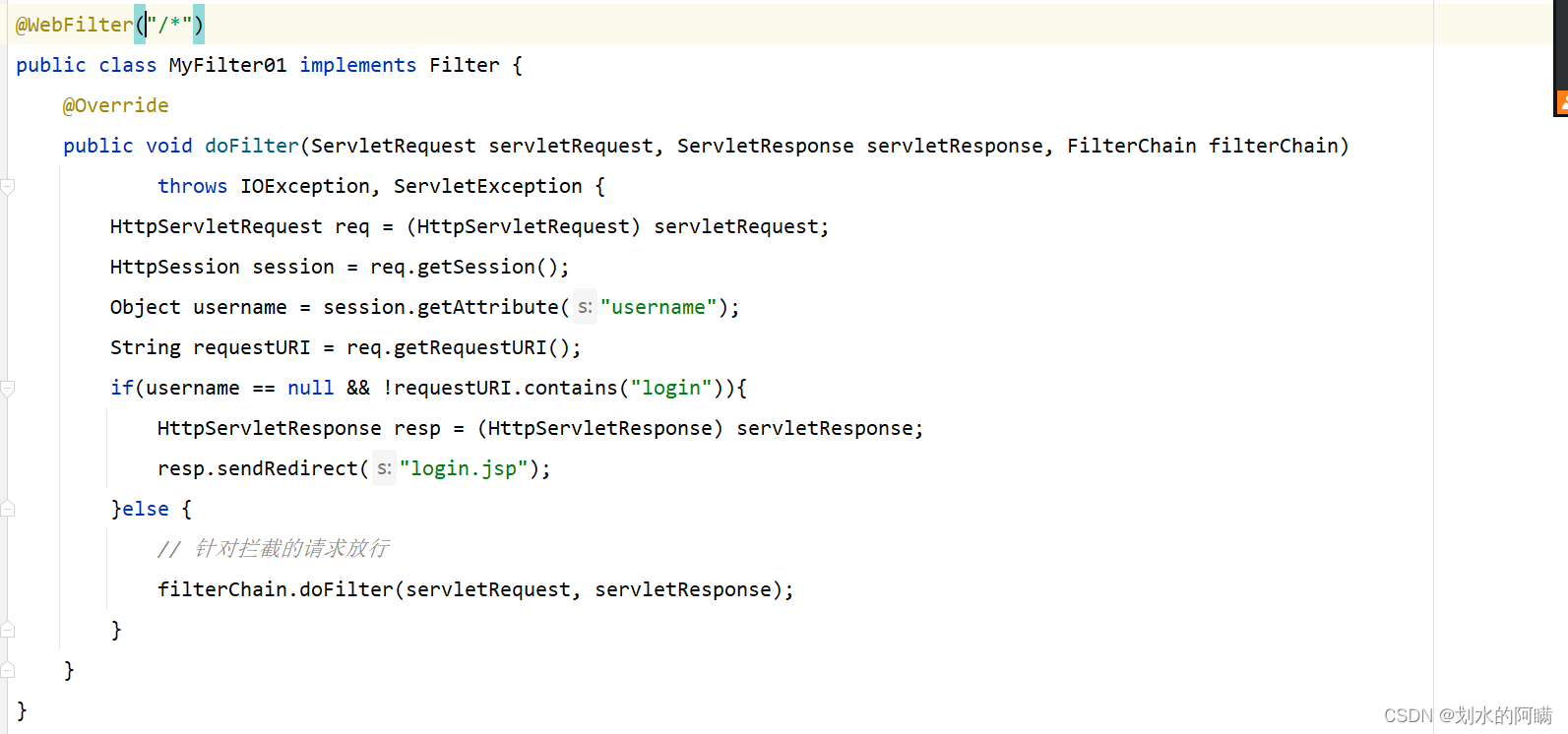

Cookie+Session详解

文章目录批量删除会话技术简介CookieCookie 查看Cookie 的删除Cookie 使用页面获取 cookie 信息cookie 特点Sessionsession 的使用Session 登录权限验证过滤器简介过滤器的使用WebFilter 注解过滤放行登录权限验证批量删除 servlet 类 dao 层 会话技术 简介 在计算机领域…...

CAPL脚本要注意区分elcount和strlen求数组长度的区别,不然要吃大亏

🍅 我是蚂蚁小兵,专注于车载诊断领域,尤其擅长于对CANoe工具的使用🍅 寻找组织 ,答疑解惑,摸鱼聊天,博客源码,点击加入👉【相亲相爱一家人】🍅 玩转CANoe&…...

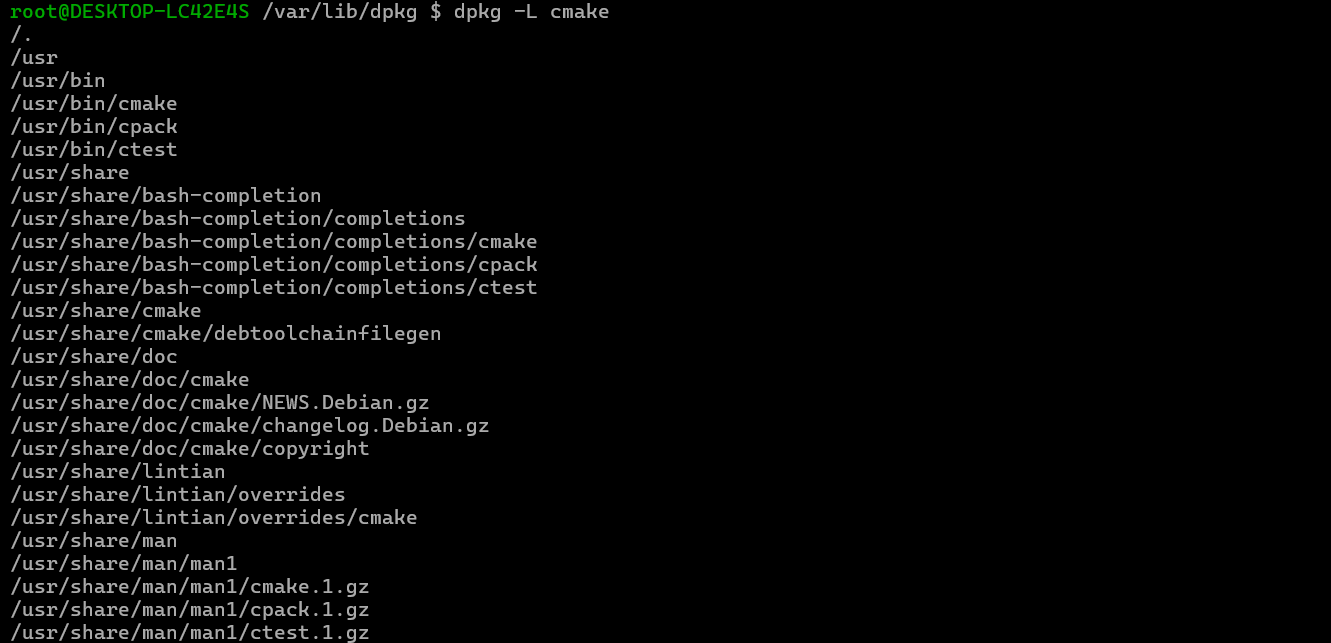

Debian系统简介

目录 Debian系统介绍 Debian版本介绍 Debian软件源介绍 软件包管理工具dpkg dpkg核心指令详解 安装软件包 卸载软件包 查询软件包状态 验证软件包完整性 手动处理依赖关系 dpkg vs apt Debian系统介绍 Debian 和 Ubuntu 都是基于 Debian内核 的 Linux 发行版ÿ…...

java调用dll出现unsatisfiedLinkError以及JNA和JNI的区别

UnsatisfiedLinkError 在对接硬件设备中,我们会遇到使用 java 调用 dll文件 的情况,此时大概率出现UnsatisfiedLinkError链接错误,原因可能有如下几种 类名错误包名错误方法名参数错误使用 JNI 协议调用,结果 dll 未实现 JNI 协…...

cf2117E

原题链接:https://codeforces.com/contest/2117/problem/E 题目背景: 给定两个数组a,b,可以执行多次以下操作:选择 i (1 < i < n - 1),并设置 或,也可以在执行上述操作前执行一次删除任意 和 。求…...

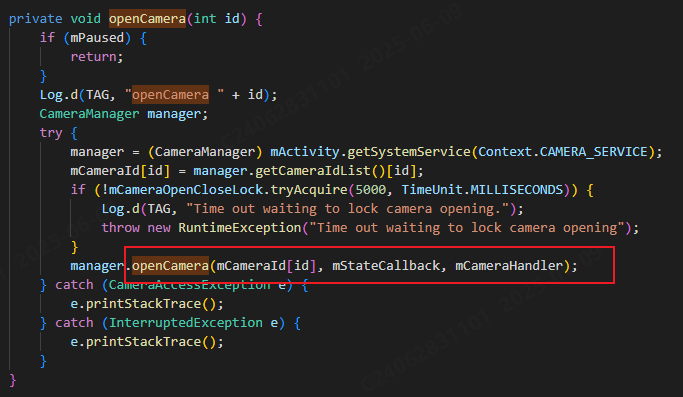

相机从app启动流程

一、流程框架图 二、具体流程分析 1、得到cameralist和对应的静态信息 目录如下: 重点代码分析: 启动相机前,先要通过getCameraIdList获取camera的个数以及id,然后可以通过getCameraCharacteristics获取对应id camera的capabilities(静态信息)进行一些openCamera前的…...

【git】把本地更改提交远程新分支feature_g

创建并切换新分支 git checkout -b feature_g 添加并提交更改 git add . git commit -m “实现图片上传功能” 推送到远程 git push -u origin feature_g...

图表类系列各种样式PPT模版分享

图标图表系列PPT模版,柱状图PPT模版,线状图PPT模版,折线图PPT模版,饼状图PPT模版,雷达图PPT模版,树状图PPT模版 图表类系列各种样式PPT模版分享:图表系列PPT模板https://pan.quark.cn/s/20d40aa…...

boost::filesystem::path文件路径使用详解和示例

boost::filesystem::path 是 Boost 库中用于跨平台操作文件路径的类,封装了路径的拼接、分割、提取、判断等常用功能。下面是对它的使用详解,包括常用接口与完整示例。 1. 引入头文件与命名空间 #include <boost/filesystem.hpp> namespace fs b…...

2.2.2 ASPICE的需求分析

ASPICE的需求分析是汽车软件开发过程中至关重要的一环,它涉及到对需求进行详细分析、验证和确认,以确保软件产品能够满足客户和用户的需求。在ASPICE中,需求分析的关键步骤包括: 需求细化:将从需求收集阶段获得的高层需…...

RLHF vs RLVR:对齐学习中的两种强化方式详解

在语言模型对齐(alignment)中,强化学习(RL)是一种重要的策略。而其中两种典型形式——RLHF(Reinforcement Learning with Human Feedback) 与 RLVR(Reinforcement Learning with Ver…...

)

零基础在实践中学习网络安全-皮卡丘靶场(第十一期-目录遍历模块)

经过前面几期的内容我们学习了很多网络安全的知识,而这期内容就涉及到了前面的第六期-RCE模块,第七期-File inclusion模块,第八期-Unsafe Filedownload模块。 什么是"遍历"呢:对学过一些开发语言的朋友来说应该知道&…...