Verilog 学习第八节(数码管段码显示)

共阴极数码管:低电平端接的都是0,高电平端哪里设置为1 ,哪里就亮~

共阳极数码管与之相反~

视觉暂留:

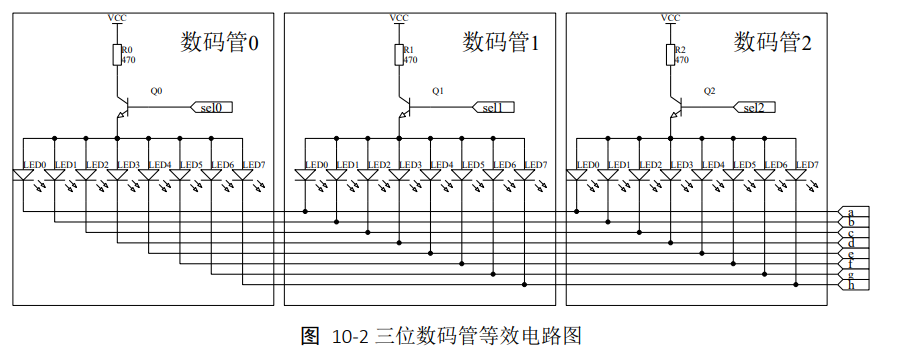

对于三位的共阴极数码管

第0.01s:让数码管0的a段亮,其他数码管全灭

Sel0为高电平,sel1和sel2为低电平

A段为低电平

第0.02s:让数码管1的b、c段亮,其他数码管全灭

Sel1为高电平,sel0和sel2为低电平

B和C段为低电平

第0.03s:让数码管2的e段亮,其他数码管全灭

Sel2为高电平,sel0和sel1为低电平

E段为低电平

数码管动态扫描

所以,通过这种方式,可以节约引脚~

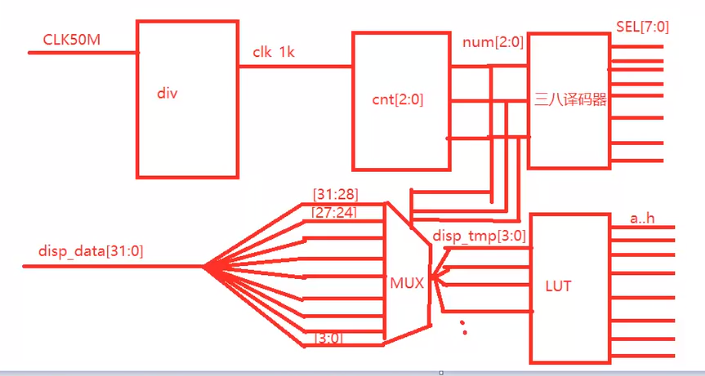

抽象原理图:

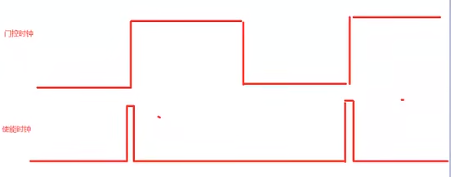

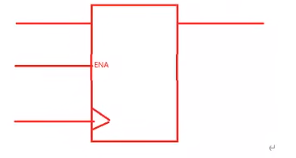

在fpga设计中尽量使用使能时钟去驱动寄存器,而不是门控时钟,因为门控时钟的质量非常差

使用门控时钟,将门控时钟直接作为DFF的工作时钟,没有ENA的情况下忽略ENA

使用使能时钟的情况,DFF的工作时钟继续全局高质量时钟,而将使能时钟作为DFF的使能信号使用

在能使用时序逻辑的情况下,尽量使用时序逻辑

顶层模块:

module hex8_test(input Clk,input Reset,output [7:0]SEL,output [7:0]SEG);wire [31:0]Disp_Data;hex8_2 hex8_2(Clk,Reset,Disp_Data,SEL,SEG);assign Disp_Data=32'h12359bdf;endmodule主模块

module hex8(input Clk,input Reset,input [31:0]Disp_Data,output reg [7:0]SEL,output reg [7:0]SEG//seg[0]对应a,seg[1]对应b~~~~seg[7]对应h);reg clk_1k;reg [14:0]div_cnt;always@(posedge Clk or negedge Reset)beginif(!Reset)div_cnt<=0;else if(div_cnt>=25000-1)div_cnt<=0;elsediv_cnt<=div_cnt+1;endalways@(posedge Clk or negedge Reset)beginif(!Reset)clk_1k<=0;else if(div_cnt>=25000-1)clk_1k<=~clk_1k;endreg[2:0]reg_num;always@(posedge clk_1k or negedge Reset)beginif(!Reset)reg_num<=0;else if(reg_num>=7)reg_num<=0;elsereg_num<=reg_num+1;endalways@(*)begincase(reg_num)0:SEL=8'b0000_0001;1:SEL=8'b0000_0010;2:SEL=8'b0000_0100;3:SEL=8'b0000_1000;4:SEL=8'b0001_0000;5:SEL=8'b0010_0000;6:SEL=8'b0100_0000;7:SEL=8'b1000_0000;endcaseendreg[3:0] disp_temp;always@(*)begincase(reg_num)7:disp_temp=Disp_Data[31:28];6:disp_temp=Disp_Data[27:24];5:disp_temp=Disp_Data[23:20];4:disp_temp=Disp_Data[19:16];3:disp_temp=Disp_Data[15:12];2:disp_temp=Disp_Data[11:8];1:disp_temp=Disp_Data[7:4];0:disp_temp=Disp_Data[3:0];endcaseendalways@(*)begincase(disp_temp)0:SEG=8'hc0;1:SEG=8'hf9;2:SEG=8'ha4;3:SEG=8'hb0;4:SEG=8'h99;5:SEG=8'h92;6:SEG=8'h82;7:SEG=8'hf8;8:SEG=8'h80;9:SEG=8'h90;4'ha:SEG=8'h88;4'hb:SEG=8'h83;4'hc:SEG=8'hc6;4'hd:SEG=8'ha1;4'he:SEG=8'h86;4'hf:SEG=8'h8e;endcaseend

endmodule

改进后的主模块

module hex8_2(input Clk,input Reset,input [31:0]Disp_Data,output reg [7:0]SEL,output reg [7:0]SEG//seg[0]对应a,seg[1]对应b~~~~seg[7]对应h);reg clk_1k;reg [15:0]div_cnt;always@(posedge Clk or negedge Reset)beginif(!Reset)div_cnt<=0;else if(div_cnt>=50000-1)div_cnt<=0;elsediv_cnt<=div_cnt+1;endalways@(posedge Clk or negedge Reset)beginif(!Reset)clk_1k<=0;else if(div_cnt>=50000-1)clk_1k<=1;elseclk_1k<=0;endreg[2:0]reg_num;always@(posedge Clk or negedge Reset)beginif(!Reset)reg_num<=0;else if(clk_1k)reg_num<=reg_num+1;elsereg_num<=reg_num;endalways@(posedge Clk)begincase(reg_num)7:SEL=8'b0000_0001;6:SEL=8'b0000_0010;5:SEL=8'b0000_0100;4:SEL=8'b0000_1000;3:SEL=8'b0001_0000;2:SEL=8'b0010_0000;1:SEL=8'b0100_0000;0:SEL=8'b1000_0000;endcaseendreg[3:0] disp_temp;always@(posedge Clk)begincase(reg_num)0:disp_temp=Disp_Data[31:28];1:disp_temp=Disp_Data[27:24];2:disp_temp=Disp_Data[23:20];3:disp_temp=Disp_Data[19:16];4:disp_temp=Disp_Data[15:12];5:disp_temp=Disp_Data[11:8];6:disp_temp=Disp_Data[7:4];7:disp_temp=Disp_Data[3:0];endcaseendalways@(posedge Clk)begincase(disp_temp)0:SEG=8'hc0;1:SEG=8'hf9;2:SEG=8'ha4;3:SEG=8'hb0;4:SEG=8'h99;5:SEG=8'h92;6:SEG=8'h82;7:SEG=8'hf8;8:SEG=8'h80;9:SEG=8'h90;4'ha:SEG=8'h88;4'hb:SEG=8'h83;4'hc:SEG=8'hc6;4'hd:SEG=8'ha1;4'he:SEG=8'h86;4'hf:SEG=8'h8e;endcaseend

endmodule测试模块

`timescale 1ns / 1psmodule hex8_tb();reg Clk;reg Reset;reg [31:0]Disp_Data;wire [7:0]SEL;wire [7:0]SEG;hex8 hex8(Clk,Reset,Disp_Data,SEL,SEG//seg[0]对应a,seg[1]对应b~~~~seg[7]对应h);initial Clk=0;always#10 Clk=!Clk;initial beginReset=0;Disp_Data=32'h0000_0000;#201Reset=1;#2000Disp_Data=32'h1234_5678;#10000000Disp_Data=32'h9abc_def0;#10000000$stop;end

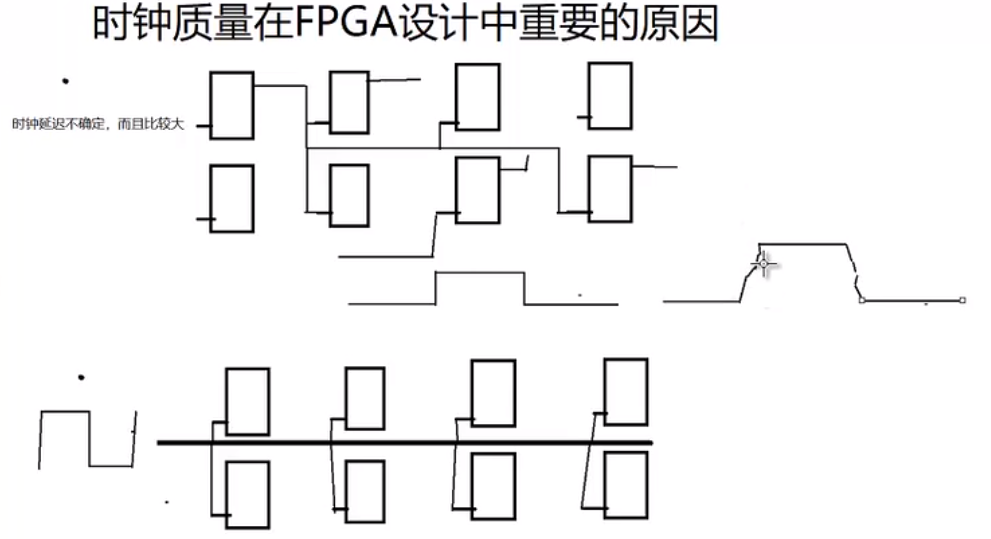

endmodule时钟质量在FPGA设计中重要的原因

1:时钟延迟不确定,而且比较大

2:使得时钟的波形变差

3:驱动能力

相关文章:

Verilog 学习第八节(数码管段码显示)

共阴极数码管:低电平端接的都是0,高电平端哪里设置为1 ,哪里就亮~ 共阳极数码管与之相反~ 视觉暂留: 对于三位的共阴极数码管 第0.01s:让数码管0的a段亮,其他数码管全灭 Sel0为高电平,sel1和sel…...

方案开发|快递吊钩电子秤方案

物流的发展为我们提供了生活的便利,足不出户仍可以感受天南地北的美食的特产,在现在这个时代已经是现实并发展成为常态的事情了。在物流发展的每一个环节中,吊钩电子秤也是它必不可缺的一环。人们在寄出物品前需要通过吊钩电子秤称量过重量&a…...

Spring-IOC容器初始化过程

Spring IOC容器的初始化过程:Resource定位,BeanDefinition载入,向IOC容器注册BeanDefinition。整个过程由refresh()方法触发,三个过程由不同的模块完成,使用户更加灵活的对这三个过程剪裁和扩展。 BeanDefinition 就是POJO对象在IOC容器中的抽象。通过BeanDefinition 这个…...

AspCms标签手册

网站通用标签{aspcms:sitepath} 网站终极目录(可放在二级目录,其它语言则在三级目录){aspcms:languagepath} 语言目录{aspcms:siteurl} 网站地址{aspcms:sitelogo} LOGO地址{aspcms:sitetitle} 网站标题{aspcms:additiontitle} 网站附加标题{aspcms:sitekeywords} 网站关键词{a…...

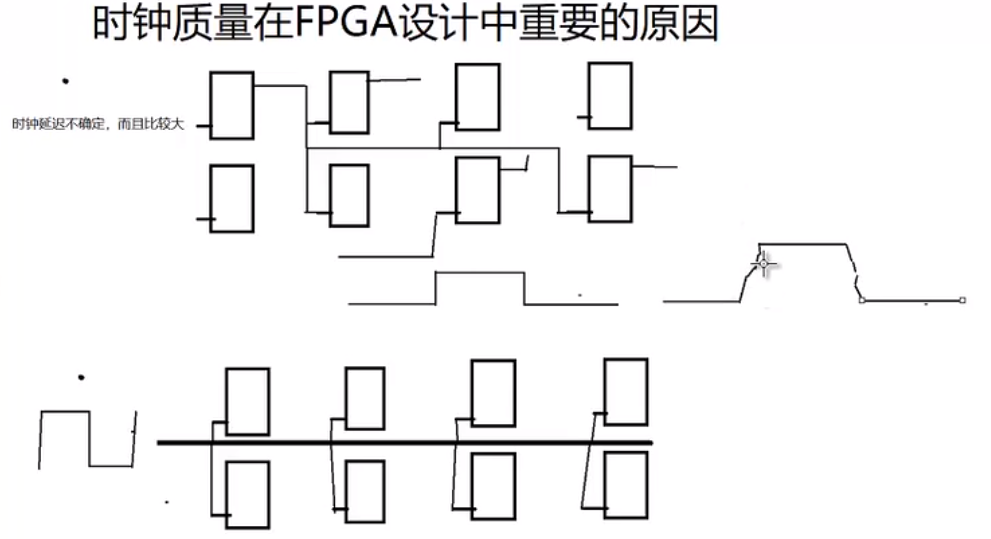

什么是Netty

一.Netty介绍 1.什么是netty Netty 是由 JBOSS 提供的一个 Java 开源框架。Netty 提供异步的、基于事件驱动的网络应用程序框架,用以快速开发高性能、高可靠性的网络 IO 程序,是目前最流行的 NIO 框架,Netty 在互联网领域、大数据分布式计算…...

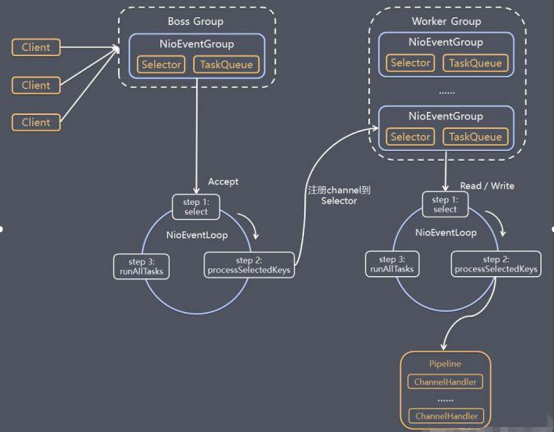

SpringCloud:统一网关Gateway

目录 1、网关介绍 2、搭建网关服务 3、路由断言工厂 4、路由过滤器 5、全局过滤器GlobalFilter 6、过滤器执行顺序 7、跨域问题处理 1、网关介绍 网关(Gateway)又称网间连接器、协议转换器。网关在网络层以上实现网络互连,是复杂的网络互 连设备࿰…...

)

【独家】华为OD机试 - 最差产品奖(C 语言解题)

最近更新的博客 华为od 2023 | 什么是华为od,od 薪资待遇,od机试题清单华为OD机试真题大全,用 Python 解华为机试题 | 机试宝典【华为OD机试】全流程解析+经验分享,题型分享,防作弊指南)华为od机试,独家整理 已参加机试人员的实战技巧文章目录 最近更新的博客使用说明本期…...

力扣解法汇总1599. 经营摩天轮的最大利润

目录链接: 力扣编程题-解法汇总_分享记录-CSDN博客 GitHub同步刷题项目: https://github.com/September26/java-algorithms 原题链接:力扣 描述: 你正在经营一座摩天轮,该摩天轮共有 4 个座舱 ,每个座舱…...

MySQL-常见的五种索引

什么是索引? 百度百科:在关系数据库中,索引是一种单独的、物理的对数据库表中一列或多列的值进行排序的一种存储结构,它是某个表中一列或若干列值的集合和相应的指向表中物理标识这些值的数据页的逻辑指针清单。索引的作用相当于…...

Linux学习第二十三节-压缩和解压缩和tar打包工具

1.压缩与解压缩(不常用)①Linux独有压缩格式及命令工具: gzip---> .gz bzip2---> .bz2 xz---> .xz②压缩命令格式: 压缩命令:gzip [选项] 文件名 常用选项:-d 解压缩 压缩命令:bzip2 [选项] 文件名…...

没有钱怎么创业?一分钱没有如何能创业成功?

限制人创业成功的从来都不是资金,而是能力,这个道理很多人都可能不懂,多数人习惯了庸庸碌碌、日复一日地打工行为,却不知如何创业,那么,没有钱怎么创业?一分钱没有如何能创业成功呢?…...

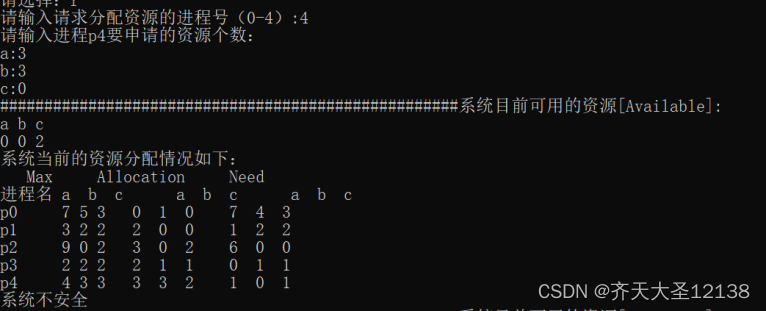

【操作系统原理实验】银行家算法模拟实现

选择一种高级语言如C/C等,编写一个银行家算法的模拟实现程序。1) 设计相关数据结构;2) 实现系统资源状态查看、资源请求的输入等模块;3) 实现资源的预分配及确认或回滚程序;4) 实现系统状态安全检查程序;5) 组装各模块…...

java医院云HIS系统:融合B/S版电子病历系统 能与公卫、PACS等各类外部系统融合

医院HIS系统源码 云HIS系统源码:SaaS运维平台完整文档 有源码,有演示 java基层医院云his系统 融合B/S版电子病历系统,支持电子病历4级 拥有自主知识产权。 看演示及源码可私信我哦! 一、系统概述 一款满足二甲医院、基层医疗机构…...

单线激光雷达(SICK)驱动安装及时空标定

一、引言 1、AGV需要同时具备定位、避障与导航的功能,其中避障对于雷达本身的分辨率、精度要求并不是很高,只需要能够根据预设定的雷达扫描范围准确避开障碍物即可,故本文以TIM240(SICK激光类雷达)为例介绍实现多雷达…...

Java IO流

Java IO流 文章目录Java IO流什么是IO流InputStreamFlieInputStream示例OutputStream示例字符的读取与写入READER方法WRITER方法利用Scanner和PrintWriter简化字符的读写ScannerPrintWriter什么是IO流 前面我们介绍了Java中对文件的操作以及file类的了解,但是file类…...

LeetCode - 1653 使字符串平衡的最少删除次数

目录 题目来源 题目描述 示例 提示 题目解析 算法源码 题目来源 1653. 使字符串平衡的最少删除次数 - 力扣(LeetCode) 题目描述 给你一个字符串 s ,它仅包含字符 a 和 b 。 你可以删除 s 中任意数目的字符,使得 …...

【微信小程序】-- 页面事件 - 上拉触底 - 案例(二十七)

💌 所属专栏:【微信小程序开发教程】 😀 作 者:我是夜阑的狗🐶 🚀 个人简介:一个正在努力学技术的CV工程师,专注基础和实战分享 ,欢迎咨询! &…...

)

《超导电子技术及其应用》学习日志(二)

约瑟夫森效应 约瑟夫森理论 约瑟夫森方程 (1)每一个库柏对都可视为质量为2m、电量为2e的复合载流子,定向运动速度v就是库柏相对质心的速度。处于超导态的库柏对凝聚于同一量子态,运载电流时具有完全相同的动量P。用微观波函数来…...

微信小程序this指向问题

前言 最近在开发微信小程序时不时会遇到一个很奇怪的问题,有些情况下用 this.setData 可以改变视图显示,有些情况下使用 this.setData 无效,这又是为什么呢? 问题描述 在解释这个问题前,我们先来看两段代码࿱…...

【报错】paddle相关报错和处理方法

1 报错 😱😱😱 ModuleNotFoundError: No module named paddle 2 解决方法 💉💉💉 pip --default-timeout=100 install paddlepaddle -i http://pypi.douban.com/simple --trusted-host pypi.douban.com 🎉🎉🎉🎉🎉🎉 1 报错 😱😱😱 from paddl…...

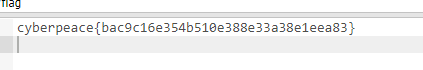

XCTF-web-easyupload

试了试php,php7,pht,phtml等,都没有用 尝试.user.ini 抓包修改将.user.ini修改为jpg图片 在上传一个123.jpg 用蚁剑连接,得到flag...

基于ASP.NET+ SQL Server实现(Web)医院信息管理系统

医院信息管理系统 1. 课程设计内容 在 visual studio 2017 平台上,开发一个“医院信息管理系统”Web 程序。 2. 课程设计目的 综合运用 c#.net 知识,在 vs 2017 平台上,进行 ASP.NET 应用程序和简易网站的开发;初步熟悉开发一…...

` 方法)

深入浅出:JavaScript 中的 `window.crypto.getRandomValues()` 方法

深入浅出:JavaScript 中的 window.crypto.getRandomValues() 方法 在现代 Web 开发中,随机数的生成看似简单,却隐藏着许多玄机。无论是生成密码、加密密钥,还是创建安全令牌,随机数的质量直接关系到系统的安全性。Jav…...

java调用dll出现unsatisfiedLinkError以及JNA和JNI的区别

UnsatisfiedLinkError 在对接硬件设备中,我们会遇到使用 java 调用 dll文件 的情况,此时大概率出现UnsatisfiedLinkError链接错误,原因可能有如下几种 类名错误包名错误方法名参数错误使用 JNI 协议调用,结果 dll 未实现 JNI 协…...

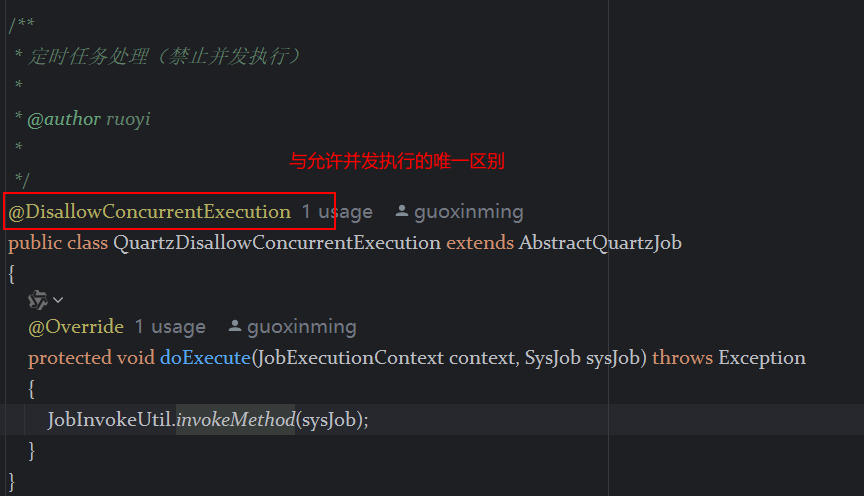

定时器任务——若依源码分析

分析util包下面的工具类schedule utils: ScheduleUtils 是若依中用于与 Quartz 框架交互的工具类,封装了定时任务的 创建、更新、暂停、删除等核心逻辑。 createScheduleJob createScheduleJob 用于将任务注册到 Quartz,先构建任务的 JobD…...

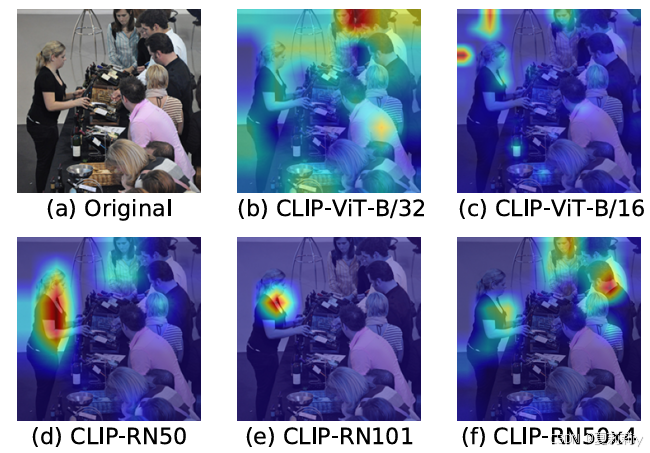

[ICLR 2022]How Much Can CLIP Benefit Vision-and-Language Tasks?

论文网址:pdf 英文是纯手打的!论文原文的summarizing and paraphrasing。可能会出现难以避免的拼写错误和语法错误,若有发现欢迎评论指正!文章偏向于笔记,谨慎食用 目录 1. 心得 2. 论文逐段精读 2.1. Abstract 2…...

Spring AI 入门:Java 开发者的生成式 AI 实践之路

一、Spring AI 简介 在人工智能技术快速迭代的今天,Spring AI 作为 Spring 生态系统的新生力量,正在成为 Java 开发者拥抱生成式 AI 的最佳选择。该框架通过模块化设计实现了与主流 AI 服务(如 OpenAI、Anthropic)的无缝对接&…...

【C++从零实现Json-Rpc框架】第六弹 —— 服务端模块划分

一、项目背景回顾 前五弹完成了Json-Rpc协议解析、请求处理、客户端调用等基础模块搭建。 本弹重点聚焦于服务端的模块划分与架构设计,提升代码结构的可维护性与扩展性。 二、服务端模块设计目标 高内聚低耦合:各模块职责清晰,便于独立开发…...

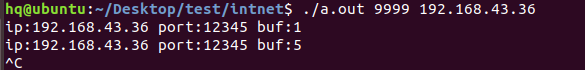

网络编程(UDP编程)

思维导图 UDP基础编程(单播) 1.流程图 服务器:短信的接收方 创建套接字 (socket)-----------------------------------------》有手机指定网络信息-----------------------------------------------》有号码绑定套接字 (bind)--------------…...

学习STC51单片机32(芯片为STC89C52RCRC)OLED显示屏2

每日一言 今天的每一份坚持,都是在为未来积攒底气。 案例:OLED显示一个A 这边观察到一个点,怎么雪花了就是都是乱七八糟的占满了屏幕。。 解释 : 如果代码里信号切换太快(比如 SDA 刚变,SCL 立刻变&#…...