FPGA结构与片上资源

文章目录

- 0.总览

- 1.可配置逻辑块CLB

- 1.1 6输入查找表(LUT6)

- 1.2 选择器(MUX)

- 1.3 进位链(Carry Chain)

- 1.4 触发器(Flip-Flop)

- 2.可编程I/O单元

- 2.1 I/O物理级

- 2.2 I/O逻辑级

- 3.布线资源

- 4.其他资源介绍

- 5.Vivado中资源查看步骤

- 资源总览

- 结构名称查看

- CLB

- SLICE

- I/O

- GTX

- BRAM

- DSP48

- 布线资源查看

- 真值表查看

- 时钟区域查看

- 参考资料

0.总览

可编程逻辑单元CLB(Configurable Logic Block)、可编程I/O单元和布线资源构成了FPGA内部三大主要资源。

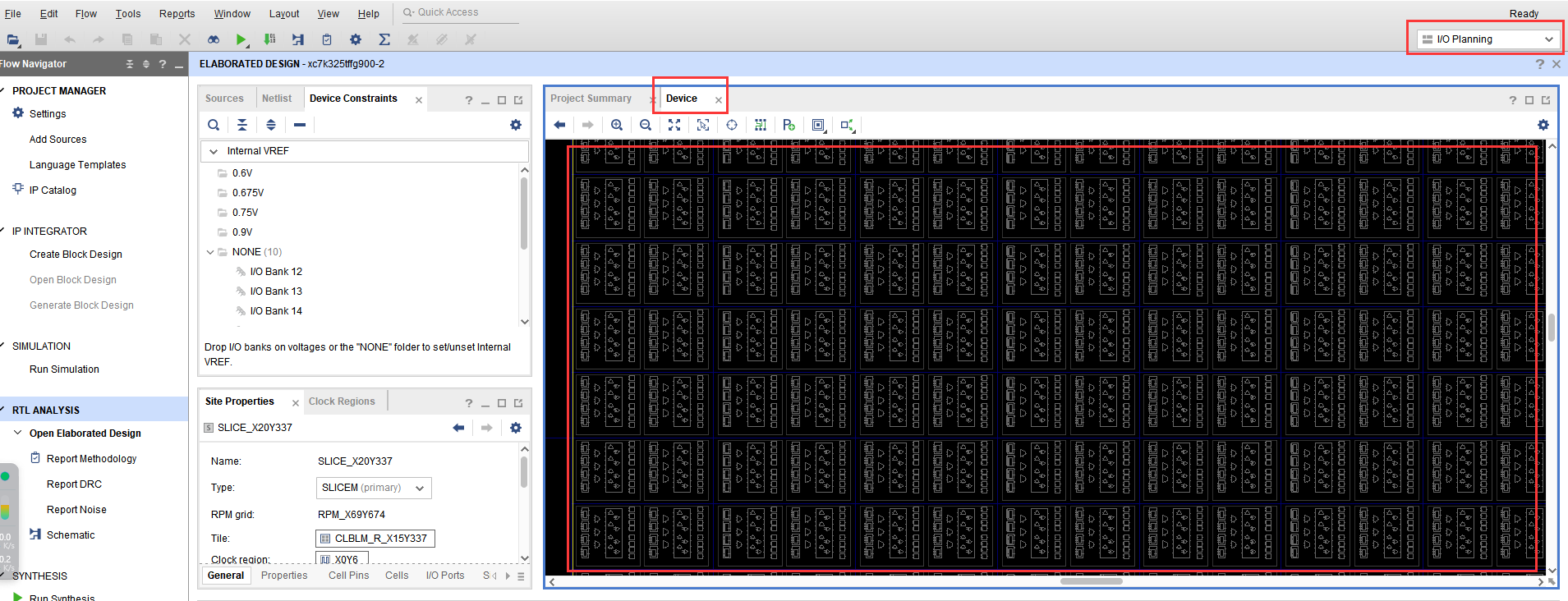

本文以Xilinx 7系列FPGA为例进行FPGA结构和片上资源讲解,其采用28nm工艺节点。

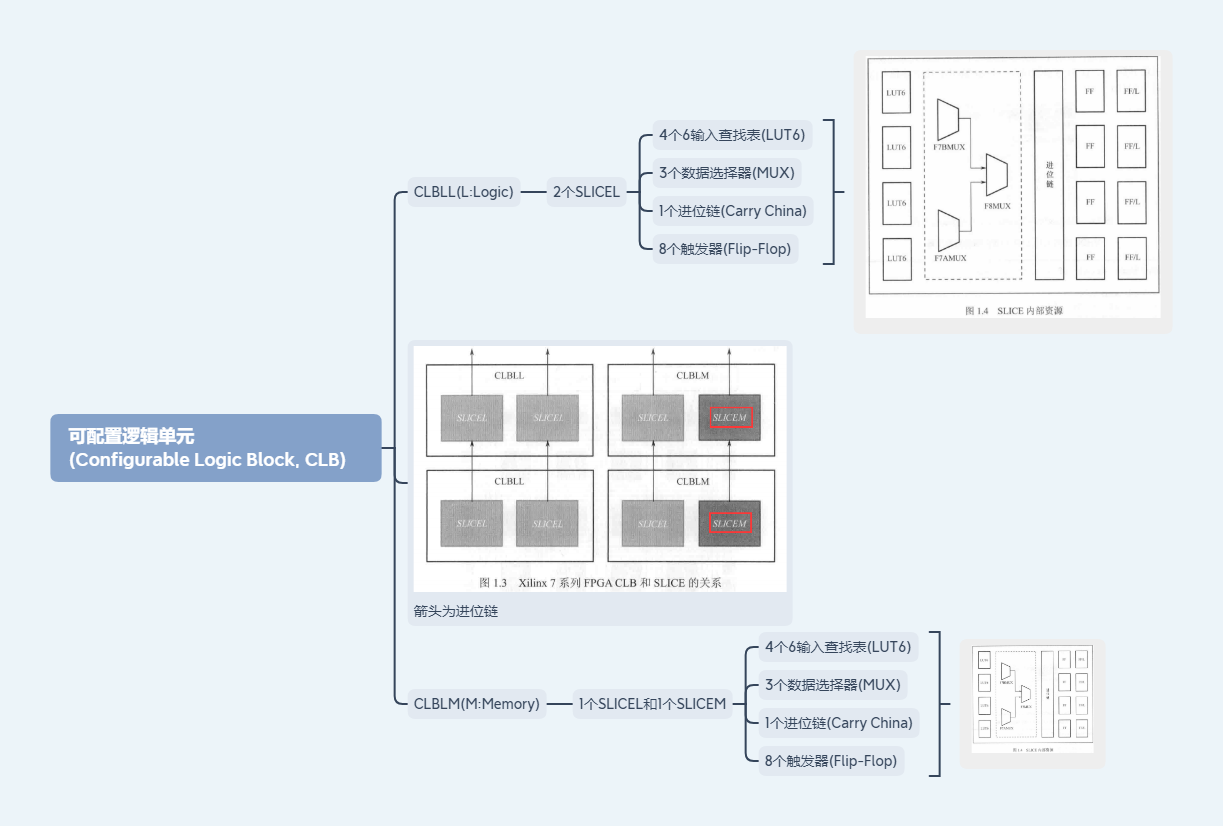

1.可配置逻辑块CLB

可配置的逻辑块(CLB)是主要的逻辑资源,用于实现时序和组合逻辑电路。

可配置逻辑单元(CLB)在 FPGA 中最为丰富,由两个 SLICE 组成。由于 SLICE 有 SLICEL(L:Logic)和 SLICEM(M:Memory)之分,因此 CLB 可分为 CLBLL 和 CLBLM 两类。

一个CLB包含两个SLICE:2个SLICEL或者1个SLICEL+一个SLICEM。

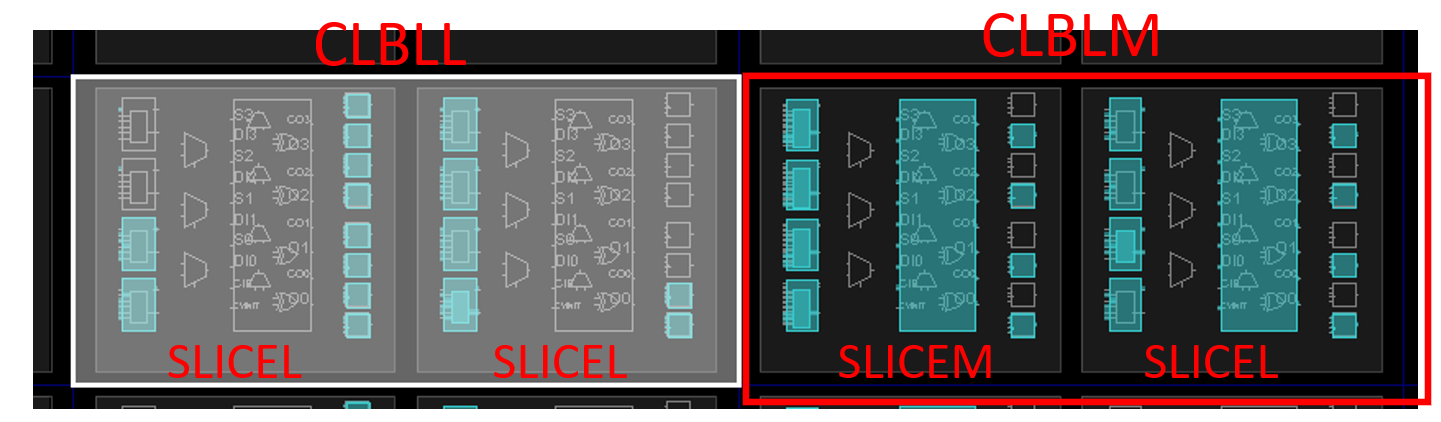

SLICEL和SLICEM内部都包含4个6输入查找表(Look-Up-Table,LUT6)、3个数据选择器(MUX)、1个进位链(Carry Chain)和8个触发器(Flip-Flop)。

1.1 6输入查找表(LUT6)

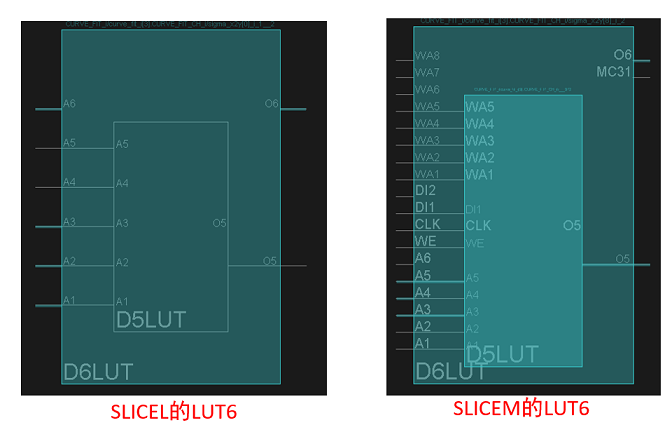

查找表Look-up Table,本质上就是1个6输入,64深度的ROM (SLICEM中的则是RAM,因为可读)。通过将所有结果保存在其内部,使用时通过由输入构建的地址线对其进行查找,从而实现6输入的函数逻辑。需要注意的是SLICEM中的查找表,除了读功能外还具备写功能,这就使得其内部的LUT由一个ROM变成了一个RAM,这也是其实现移位寄存器功能和分布式DRAM功能的原因。

虽然SLICEL和SLICEM的结构组成一样,但两者更细化的结构上略有不同,区别在于LUT6上(如下图所示),从而导致LUT6的功能有所不同(如下表格所示)。

| LUT功能 | SLICEL | SLICEM |

|---|---|---|

| 逻辑函数发生器 | √ | √ |

| ROM | √ | √ |

| 分布式RAM | √ | |

| 移位寄存器 | √ |

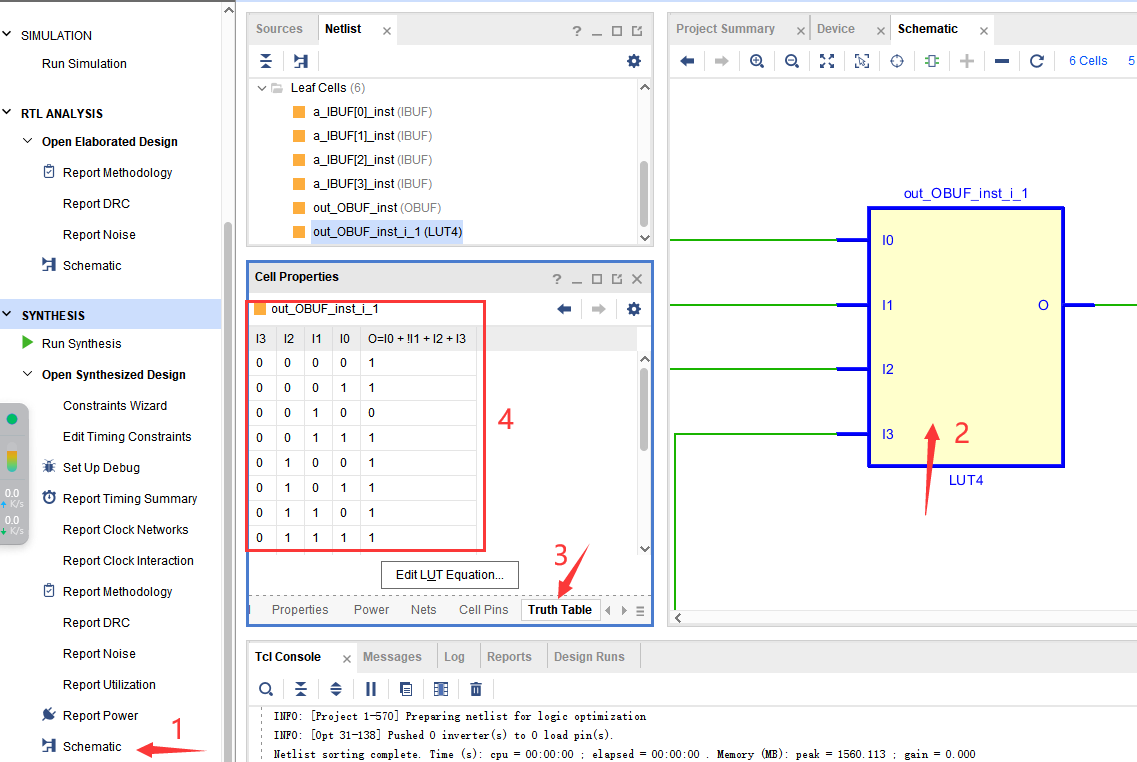

逻辑函数发生器:用作逻辑函数发生器时,查找表就扮演着真值表的角色,真值表的内容可在Vivado中查看。

ROM:不论是 SLICEL 还是 SLICEM,他们的 LUT6 都可以作为 ROM 使用,配置为 64x1(占用 1 个 LUT6,64 代表深度,1 代表宽度)、128x1(占用 2 个 LUT6)和 256(占用 4 个 LUT6)的 ROM。

分布式RAM: SLICEM中的查找表可配置为RAM ( Random Access Memory),称为分布式RAM。其中 RAM 的写操作为同步,而读操作是异步的,即与时钟信号无关。如果要实现同步读操作,则要额外占用一个触发器,从而增加了意识时钟的延迟(Latency),但提升了系统的性能。这就解释了为什么我们实现RAM同步读写的时候,读出输出要延迟一个 clk。对于布式存储单元(RAM和ROM),Vivado 提供了相应的IP: Distributed Memory Generator。

移位寄存器:SLICEM 中的 LUT 还可以配置为移位寄存器,每个 LUT6 可实现深度为 32 的移位寄存器,(注意:只能左移)。这样,每个LUT可以将串行数据延迟1到32个时钟周期。移位输入D(LUT DI1脚)和移位输出Q31 (LUT MC31脚)可以进行级联,以形成更大的移位寄存器。一个SLICEM的4个LUT6级且同一个 SLICEM 中的 LUT6(4个)可级联实现 128 深度的移位寄存器。移位寄存器的典型应用是延迟补偿和同步FIFO。需要注意的是,这里的移位寄存器均没有复位端,这是因为LUT6本身不支持复位。一旦代码描述中使用了复位,无论是同步复位还是异步复位,都会导致移位寄存器采用触发器级联的方式实现。

1.2 选择器(MUX)

SLICE 中的三个 MUX(Multiplexer)两个F7MUX:F7AMUX,F7BMUX +一个 F8MUX。可以和 LUT6 联合共同实现更大的MUX。

一个 LUT6 可实现 4 选 1 的 MUX。

SLICE 中的 F7MUX(F7AMUX 和 F7BMUX)的输入数据来自于相邻的两个 LUT6 的 O6 端口。每个SLICE中都有2个MUXF7,其输入只能为LUT6的输出,而输出只能接到MUXF8;每个SLICE中都有1个MUXF8,其输入只能为MUXF7的输出。

一个 F7MUX 和相邻的两个 LUT6 可实现一个 8 选 1 的 MUX。因此,一个 SLICE 可实现 2 个 8 选 1 的 MUX。

4 个 LUT6、F7AMUX、F7BMUX 和 F8MUX 可实现一个 16 选 1 的 MUX。因此,一个 SLICE 可实现一个 16 选 1 的 MUX。

1.3 进位链(Carry Chain)

进位链用于实现加法和减法运行。它内部实际还包含 4 个 MUX 和 4 个 2 输入异或门(XOR)。每个CLB Slice都有一个专用的加法器CARRY4, 可以实现两个4bit数的加减法运算。CARRY4是一种超前进位的加法器(或者说减法器),是FPGA内部用来实现加减法运算的基本运算单元,但同时也可以实现一些其他的函数功能。

1.4 触发器(Flip-Flop)

每个 SLICE 中有 8 个触发器。

Slice中的存储单元便是我们前面提到的寄存器FF,FF是实现时序逻辑最基本的单元。需要注意的是,这 8 个触发器可分为两大类:4 个只能配置为边沿敏感的 D 触发器(Flip-Flop)和 4 个即可配置为边沿敏感的 D 触发器又可配置为电平敏感的锁存器(Flop & Latch)。但后四个一旦被配置为锁存器后,则前4个触发器也不能使用了,会造成一定的资源浪费。

当后者被用作锁存器的时候,前者将无法使用。

当这8个触发器都用作D触发器时,他们的控制端口包括使能端CE、置位/复位端口S/R和时钟端口CLK是对应共享的,也就是就是说共用的。{CE,S/R,CLK}称为触发器的控制集。显然,在具体的设计中,控制集种类越少越好,这样可以提高触发器的利用率。那么怎样减少控制集种类呢?我的理解是:

- 减少时钟种类,即频率越少越好;

- 统一规范的设计逻辑,如复位。

S/R端口可配置为同步/异步置位或同步/异步复位,且高有效,因此可形成4种D触发器,如下表所示。

| 原语(Primitive) | 功能描述 | 原语(Primitive) | 功能描述 |

|---|---|---|---|

| FDCE | 同步使能,异步复位 | FDRE | 同步使能,同步复位 |

| FDPE | 同步使能,异步置位 | FDSE | 同步使能,同步置位 |

在我们的常规设计中,FDCE和FDPE占了绝大多数。

说到高有效,让我想起了一个大家习以为常,但很少深究的问题:为什么一开始接触FPGA的时候,都告诉我们低电平复位?后来查了一些资料,有说从功耗、噪声可靠性方面考虑等等,但是偶然看到Xilinx和Altera两家芯片的触发器不一样!如下图所示,Xilinx的触发器是高电平复位,而Altera的触发器时低电平复位。所以这也是需要考虑的一点吗?

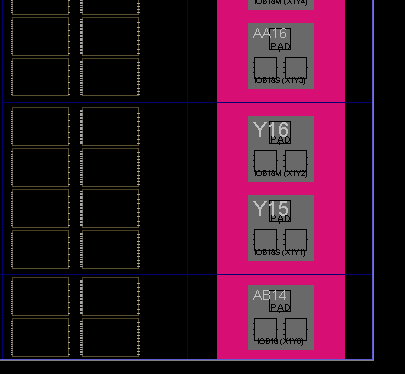

2.可编程I/O单元

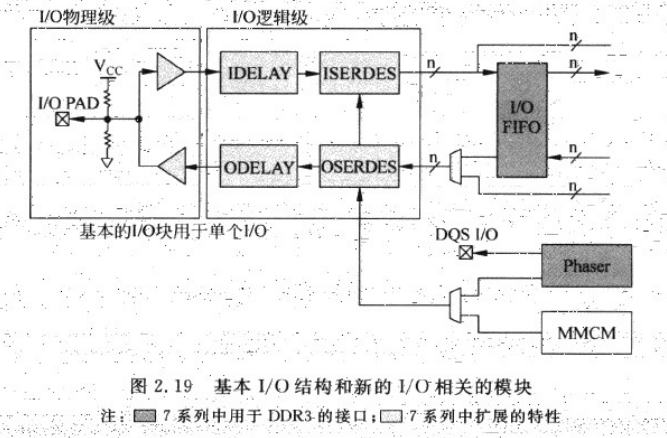

7系列FPGA的输人输出(I/O)进行了优化,用来在物理级和逻辑级上满足不同的要求,这些要求包括:高速存储器、网络、视频平板和传感器接口,高速的ADC/DAC连接,以及传统接口。7系列FPGA使用了Xilinx统一的I/O结构。

物理I/O能力和结构提供了一个I/O标准范围、端接和节省能量模式。每个I/O组的I/O数量、它们相对应的时钟、新的I/O资源的放置,以及I/O在FPGA晶圆上的排列都是同等重要的。此外,详细的I/O绑定逻辑功能,比如输人/输出延迟和串行化/解串行化功能,对于所支持的I/O应用是非常关键的。所添加的最新功能结构,比如移相器,PLL和I/O FIFO完整接口特性,支持最高性能的DDR3.及其他存储器接口。下图给出了基本的I/O结构和与新I/O相关的模块。

2.1 I/O物理级

在物理级上,I/O要求支持一个范围的驱动电压(或电平)和驱动强度,以及接收功能接口的不同I/O标准。I/O也支持不同的输人/输出端接特性,它可以动态地确认和移除。

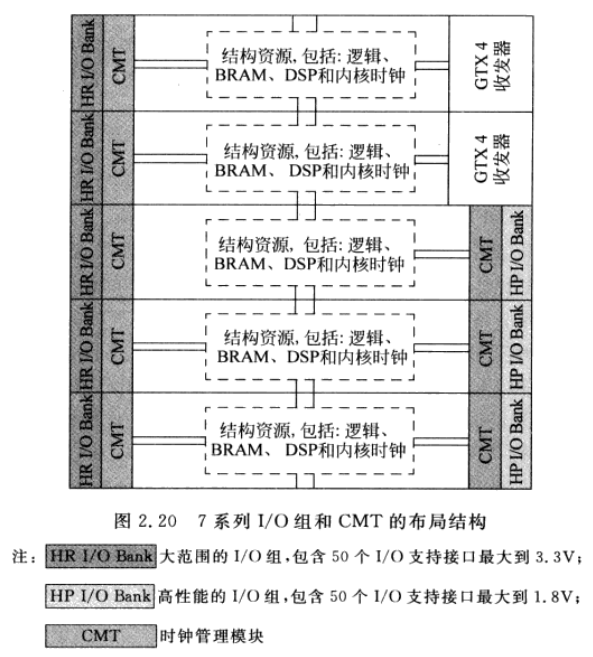

7系列的结构有两种类型的I/O:

(1)高性能(High Performance)I/O,在组中称为HP I/O组;

(2)宽范围(High Range,HR)I/O(支持宽范围的I/O标准),在组中称为HR I/O组。

所有的I/O类型都是基于Virtex-6的结构,但是扩展了功能和所支持的电压范围。这两种I/O类型被绑定到一个有50个I/O的整个I/O组。Artix-7 FPGA只有3.3V的HR I/O组,Virtex-7和Kintex FPGA既有HP I/O组,也有HR I/O组。下面详细介绍HP I/O和HP I/O组。下图给出了Kintex-7XC7K160T的I/O组和CMT的布局结构图。

用于存储器接口的I/O电源主要有3个元件:

(1)DCI:用于匹配PCB布线的阻抗。

(2)参考输人接收器:用于调整I/O电压到核电压。

(3)IDELAY:用于同步信号到时钟。

2.2 I/O逻辑级

所有的I/O都能被配置成组合或者寄存方式。所有的输入/输出支持双数据率(double data rate, DDR)模式。任何一个输人和一些输出可以通过编程IDEALY和ODELAY进行延迟。

每个I/O 块包含一个可编程的绝对延迟原语IDELAY2。IDELAY可以连接到ILOGICE2/ISERDESE2或者ILOGICE3/ISERDESE2模块。

每个HP I/O组包含一个可编程绝对延迟原语称为ODELAY2(HR I/O组不可用)。

很多应用连接了高速、位串行的I/O,以及FPGA内低速并行操作的逻辑。这就要求在I/O结构内有一个串行化器和解串行化器。每个I/O引脚包含8位IOSERDES,能执行串行-并行或并行-串行转换。

7系列内用于精确实现ISERDES的原语是ISERDESE2,精确实现OSERDES的原语是OSERDESE2。

3.布线资源

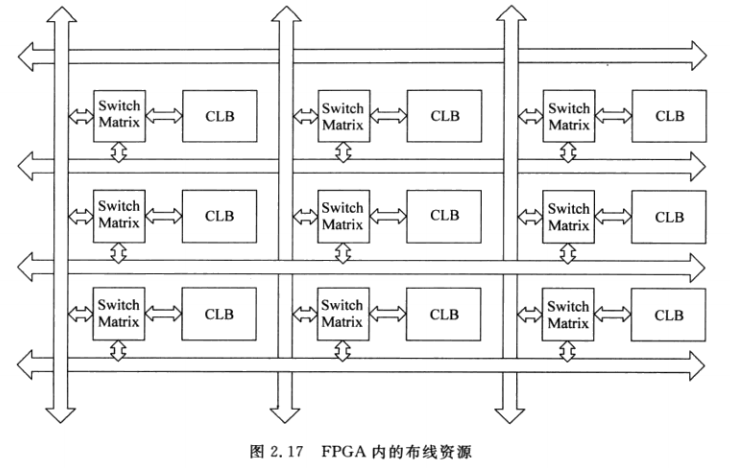

互联是FPGA内用于连接功能元件,比如IOB、CLB、DSP和BRAM,输人和输出信号通路的可编程网络。互联也称为布线,被分段用于最优的连接。

7系列FPGA CLB在FPGA内以规则的阵列排列。如图所示,每个到开关矩阵的连接用来访问通用的布线资源。

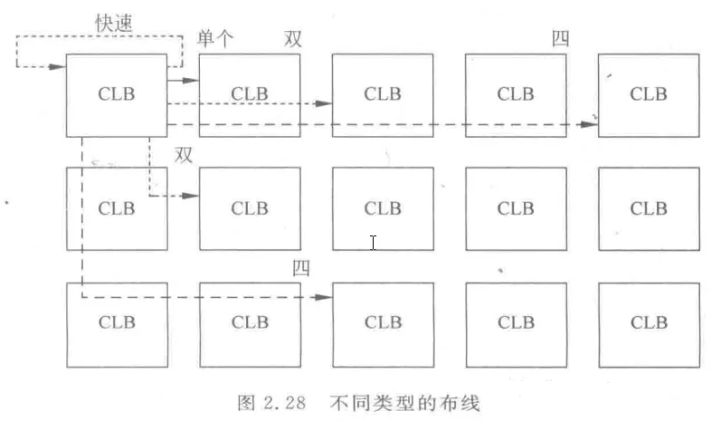

FPGA内部定义了不同类型的布线,这些布线通过长度来定义。较长的路径元素对于较长的距离来说速度更快。互联类型有快速连接、单连接、双连接和四连接。

- 快速连接:快速连接将模块的输出布线回模块的输入。与较大的CLB一起,快速连接为较简单的功能提供了高性能布线。

- 单连接:单连接用于在垂直和水平方向上,布线到相邻的单元。

- 双连接:双连接在所有4个方向上,水平和垂直连接到所有其他的单元和对角线相邻的单元。

- 四连接:四连接在水平和垂直方向,每隔4个CLB连接一个或者对角线连接到两行和两列的距离的单元。与前几代的单通道长线相比,四连接线具有更好的灵活性。

4.其他资源介绍

《Xilinx FPGA设计权威指南》2.2 FPGA原理及结构

《FPGA深度解析》第2章 FPGA结构与片上资源

5.Vivado中资源查看步骤

资源总览

上方选择Window-Device,打开Device布局图可以看到FPGA的内部结构资源。

结构名称查看

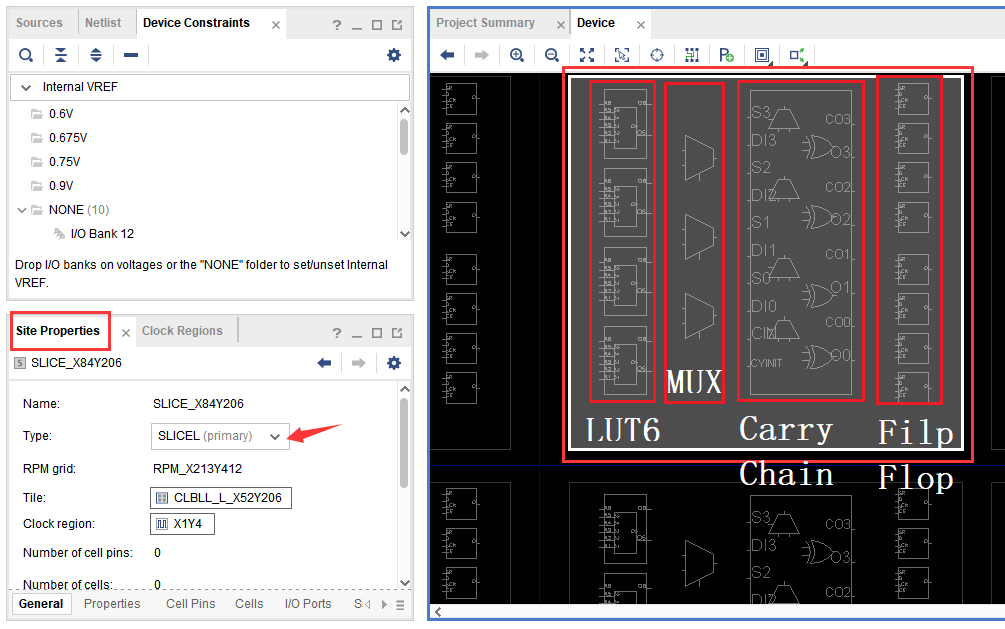

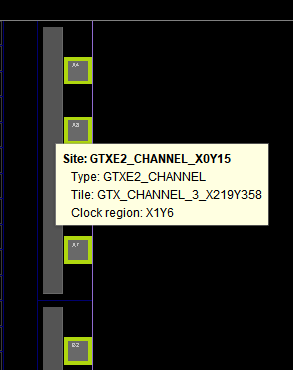

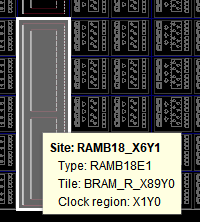

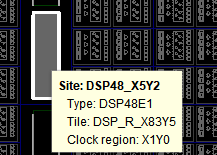

放大后点击具体结构可在左侧Site Properties中看到具体的结构名称等信息。

CLB

SLICE

I/O

GTX

BRAM

DSP48

等等。

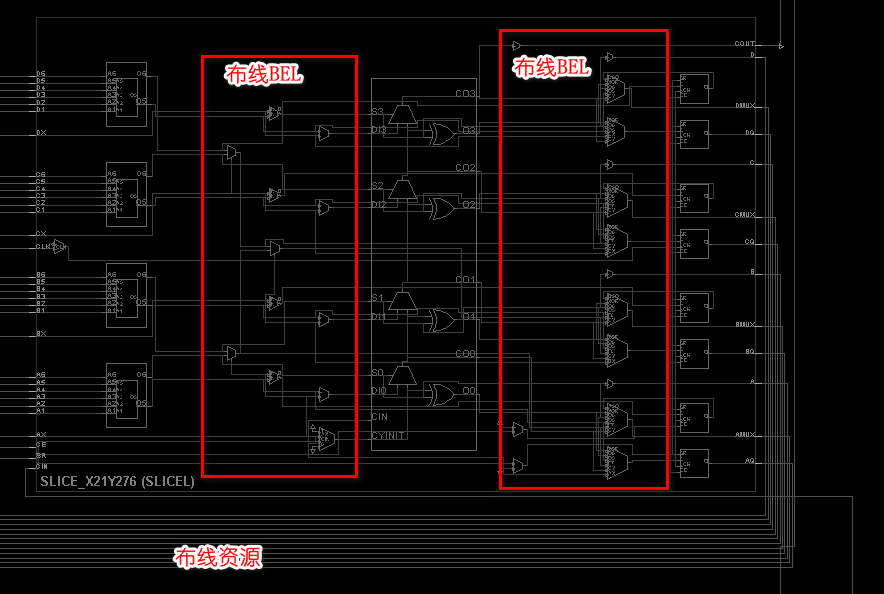

布线资源查看

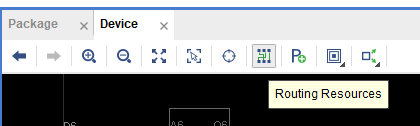

布线BEL则不实现逻辑功能,而只用来实现布线功能。要看到布线EBL,首先需要把模式改成Routing Resource这个选项勾上:

放大界面看可以看到布线BEL(Basic Element of Logic):可以看到在原来的SLICE块基础上多了互联线和一些布线选择块。

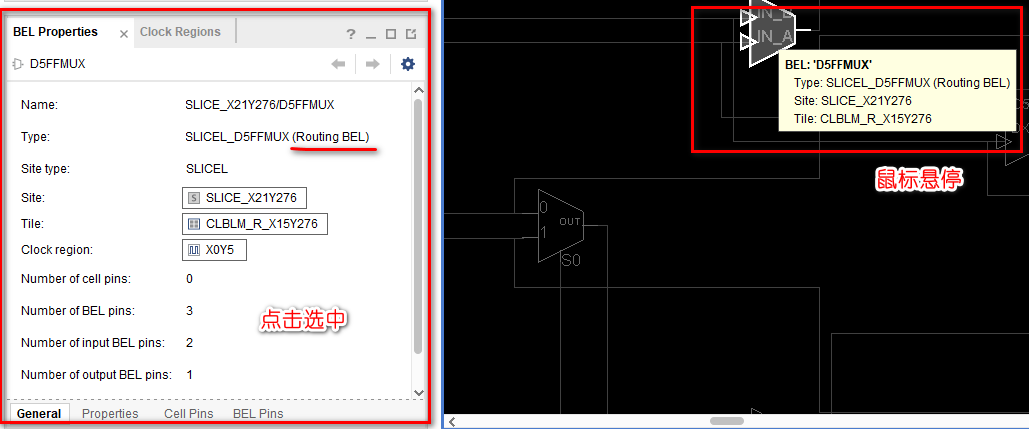

接下来随便选择一个布线BEL, 把鼠标悬停在它上面就会出现一些基本信息,如果点击选中它则会在左下角出现更详细的信息,比如它的输入/输出管脚分别连接到哪里,它属于哪个时钟区域,它是什么类型的BEL等等。

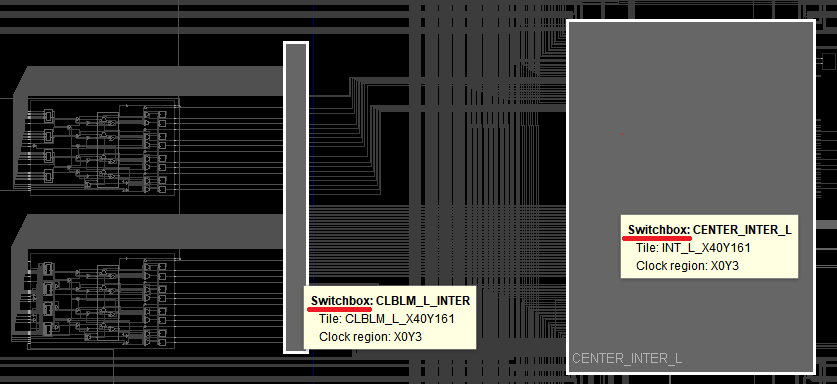

Switch Box可以理解成一个“中转站“ ,附近的各种资源的输出都到这里完成转接,所以这个布线BEL的输出可能是来自相邻的FF,也可能是来自相邻的LUT,具体都根据实际的RTL代码来决定。

布线BEL用来实现各种输入的选取,从而实现底层资源间的灵活互联!正是有了这些布线资源和布线BEL, FPGA才可以做到这么灵活。

真值表查看

综合后LUT真值表的查看。

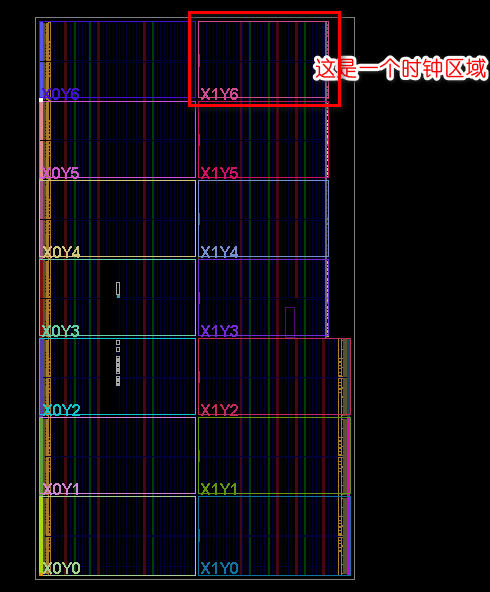

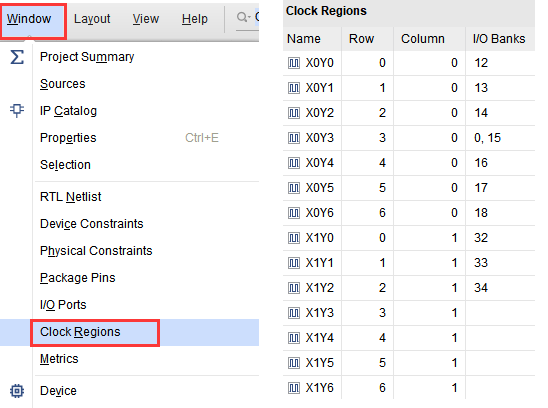

时钟区域查看

时钟区域是Xilinx FPGA对时钟的一种划分结构,它把整个芯片根据不同的IO BANK内的所有资源和连线都划定到不同的各个时钟区域下,这样对在同一时钟区域下的时钟信号就方便管理,同时也方便各种时钟资源走线和互联。

综合后打开Clock Regions可以看到时钟区域和Bank划分。IO BANK和时钟区域不是一一对应的。

参考资料

CLB部分参考:

《Vivado从此开始》第1章FPGA技术分析

从底层结构开始学习FPGA(0)----FPGA的硬件架构层次(BEL Site Tile FSR SLR Device)

从底层结构开始学习FPGA(1)----可配置逻辑块CLB(Configurable Logic Block)

FPGA基础学习(7) – 内部结构之CLB

LUT部分补充:

从底层结构开始学习FPGA(2)----LUT查找表

其他部分参考:

《FPGA深度解析》第2章 FPGA结构与片上资源

《Xilinx FPGA设计权威指南》2.2 FPGA原理及结构

官方文档:

7 Series FPGAs Configurable Logic Block User Guide (UG474)

相关文章:

FPGA结构与片上资源

文章目录 0.总览1.可配置逻辑块CLB1.1 6输入查找表(LUT6)1.2 选择器(MUX)1.3 进位链(Carry Chain)1.4 触发器(Flip-Flop) 2.可编程I/O单元2.1 I/O物理级2.2 I/O逻辑级 3.布线资源4.其…...

【分布式】——分布式事务

分布式事务 ⭐⭐⭐⭐⭐⭐ Github主页👉https://github.com/A-BigTree 笔记链接👉https://github.com/A-BigTree/tree-learning-notes ⭐⭐⭐⭐⭐⭐ Spring专栏👉https://blog.csdn.net/weixin_53580595/category_12279588.html SpringMVC专…...

第6章:“让我们思考这个”的提示

“让我们思考这个”这一提示词,是深度对话的钥匙,鼓励ChatGPT生成反思性、沉思性的文本。 对于论文写作、诗歌创作或创意任务的完成,非常实用。 当你想要深究某主题时,只需向ChatGPT提问。 它会基于提示,结合算法和…...

安卓Activity上滑关闭效果实现

最近在做一个屏保功能,需要支持如图的上滑关闭功能。 因为屏保是可以左右滑动切换的,内部是一个viewpager 做这个效果的时候,关键就是要注意外层拦截触摸事件时,需要有条件的拦截,不能影响到内部viewpager的滑动处理…...

使用conda管理python环境

为什么需要管理环境? 每个python程序依赖的库版本可能不同,因此我们需要隔离不同的环境。 创建环境: conda create --name myenv python3.8这将创建一个名为myenv的新环境,并在其中安装Python 3.8版本。 列出所有环境…...

MR混合现实情景实训教学系统在军事演练课堂中的教学应用

MR混合现实情景实训教学系统在军事演练课堂中的教学应用具有以下优势: 1. 增强现实感:通过MR技术,学生可以在军事演练中更真实地感受到战场环境,增强他们的实战经验。 2. 提高训练效率:通过MR技术,可以模…...

vant checkbox 复选框 样式改写

修改前 修改后 基于 vant: 4.8.3 unocss: 0.53.4 <van-checkbox-group v-model"query.zczb" shape"square" class"text-16 w-100% flex flex-wrap"><template v-for"item in registerCapitalOption"><v…...

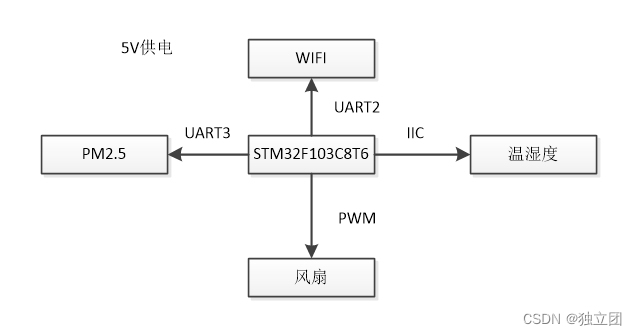

物联网实战--入门篇之(一)物联网概述

目录 一、前言 二、知识梳理 三、项目体验 四、项目分解 一、前言 近几年很多学校开设了物联网专业,但是确却地讲,物联网属于一个领域,包含了很多的专业或者说技能树,例如计算机、电子设计、传感器、单片机、网…...

将yolov5s部署到安卓上实战经验总结

最近需要在手机端实现一个目标检测的功能,于是选择了小巧又在目标检测方面表现很好的yolov5s,官网下载yolov5代码,用自己做的数据集进行了训练,然后把模型转换成torchscript格式,这些过程网上都有很多讲解,…...

)

算法日记————对顶堆(4道题)

对顶堆的作用主要在于动态维护第k大的数字,考虑使用两个优先队列,一个大9999999999根堆一个小根堆,小根堆维护大于等于第k大的数字的数,它的堆顶就是堆内最小,第k大的数字,另外一个大根堆维护小于等于k的数…...

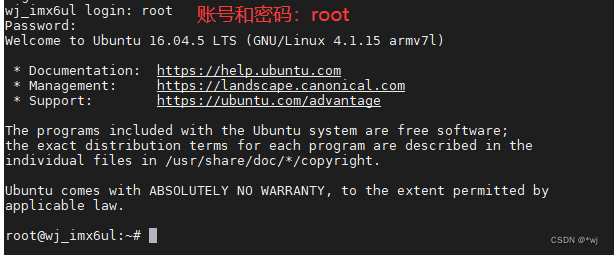

【I.MX6ULL移植】Ubuntu-base根文件系统移植

1.下载Ubuntu16.04根文件系统 http://cdimage.ubuntu.com/ 1 2 3 4 5 2.解压ubuntu base 根文件系统 为了存放 ubuntu base 根文件系统,先在 PC 的 Ubuntu 系统中的 nfs 目录下创建一个名为 ubuntu_rootfs 的目录,命令如下: 【注意&…...

unity3d for web

时光噶然 一晃好多年过去了(干了5年的u3d游戏),记得最后一次使用的版本好像是 unity 2017。 那个是 unity3d for webgl 还需要装个插件。用起来很蛋疼。 最近做一个小项目 在选择是用 Layabox 还是 cocosCreate 的时候 我想起了老战友 Uni…...

关于消费者研究的流程)

大宋咨询(深圳问卷调研)关于消费者研究的流程

消费者研究是一项至关重要的任务,它有助于企业了解目标市场的需求、偏好和行为,从而制定更加精准的营销策略。在执行消费者研究时,需要遵循一定的步骤和方法,以确保研究的准确性和有效性。开展消费者研究需要一系列的步骤和方法。…...

STM32看似无法唤醒的一种异常现象分析

1. 引言 STM32 G0 系列产品具有丰富的外设和强大的处理性能以及良好的低功耗特性,被广泛用于各类工业产品中,包括一些需要低功耗需求的应用。 2. 问题描述 用户使用 STM32G0B1 作为汽车多媒体音响控制器的控制芯片,用来作为收音机频道存贮…...

iOS - Runtime-isa详解(位域、union(共用体)、位运算)

文章目录 iOS - Runtime-isa详解(位域、union(共用体)、位运算)前言1. 位域介绍1.1 思路1.2 示例 - 结构体1.3 示例 - union(共用体)1.3.1 说明 1.4 结构体 对比 union(共用体) 2. a…...

使用VSCode搭建Vue 3开发环境

使用VSCode搭建Vue 3开发环境 Vue 3是一种流行的前端JavaScript框架,它提供了响应式的数据绑定和组合式的API。Visual Studio Code(VSCode)是一个轻量级但功能强大的源代码编辑器,支持多种语言开发。本文将引导您完成使用VSCode搭建Vue 3开发环境的步骤。 1. 下载和安装V…...

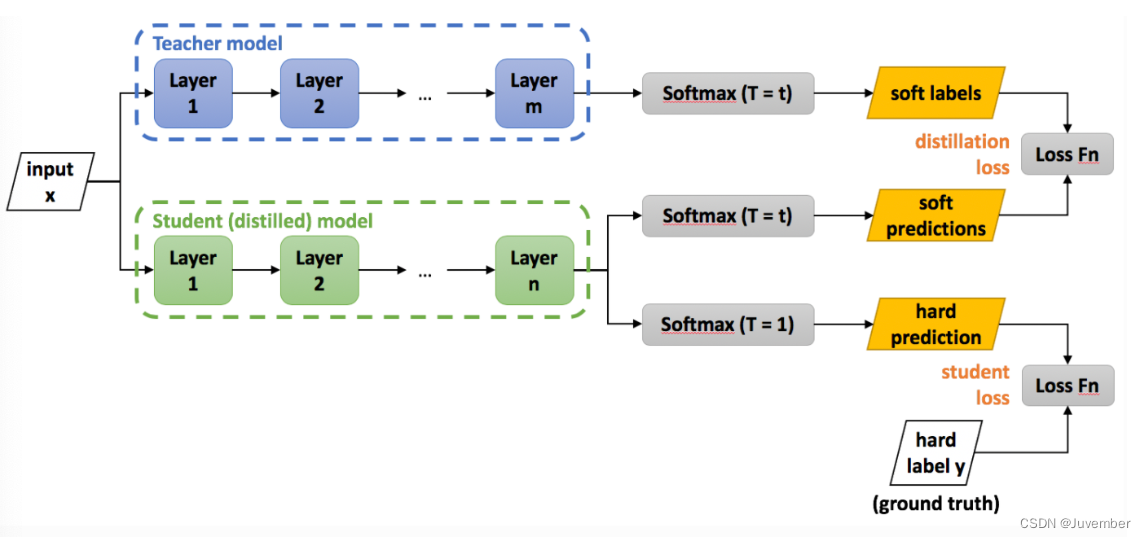

深度学习中的模型蒸馏技术:实现流程、作用及实践案例

在深度学习领域,模型压缩与部署是一项重要的研究课题,而模型蒸馏便是其中一种有效的方法。 模型蒸馏(Model Distillation)最初由Hinton等人在2015年提出,其核心思想是通过知识迁移的方式,将一个复杂的大模型…...

Java服务运行在Linux----维护常用命令

想起来哪些再添加上去 查看Java程序进程 jps -l 查出进程后根据pid 查询程序所在目录 pwdx 31313 根据端口查找PID 根据pid杀死程序 kill -p 31313 查看目录下所有包含9527的文件 grep -rn 9527 查看磁盘空间 查找文件名"nginx"文件或模糊查找"*nginx*&quo…...

夜晚水闸3D可视化:科技魔法点亮水利新纪元

在宁静的夜晚,当城市的霓虹灯逐渐暗淡,你是否曾想过,那些默默守护着城市安全的水闸,在科技的魔力下,正焕发出别样的光彩?今天,就让我们一起走进夜晚水闸3D模型,感受科技为水利带来的…...

从零开始的软件开发实战:互联网医院APP搭建详解

今天,笔者将以“从零开始的软件开发实战:互联网医院APP搭建详解”为主题,深入探讨互联网医院APP的开发过程和关键技术。 第一步:需求分析和规划 互联网医院APP的主要功能包括在线挂号、医生预约、医疗咨询、健康档案管理等。我们…...

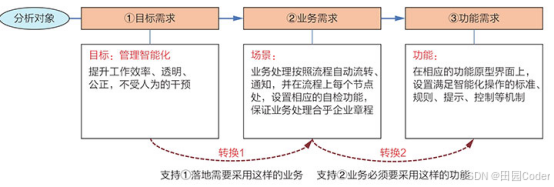

大话软工笔记—需求分析概述

需求分析,就是要对需求调研收集到的资料信息逐个地进行拆分、研究,从大量的不确定“需求”中确定出哪些需求最终要转换为确定的“功能需求”。 需求分析的作用非常重要,后续设计的依据主要来自于需求分析的成果,包括: 项目的目的…...

Golang 面试经典题:map 的 key 可以是什么类型?哪些不可以?

Golang 面试经典题:map 的 key 可以是什么类型?哪些不可以? 在 Golang 的面试中,map 类型的使用是一个常见的考点,其中对 key 类型的合法性 是一道常被提及的基础却很容易被忽视的问题。本文将带你深入理解 Golang 中…...

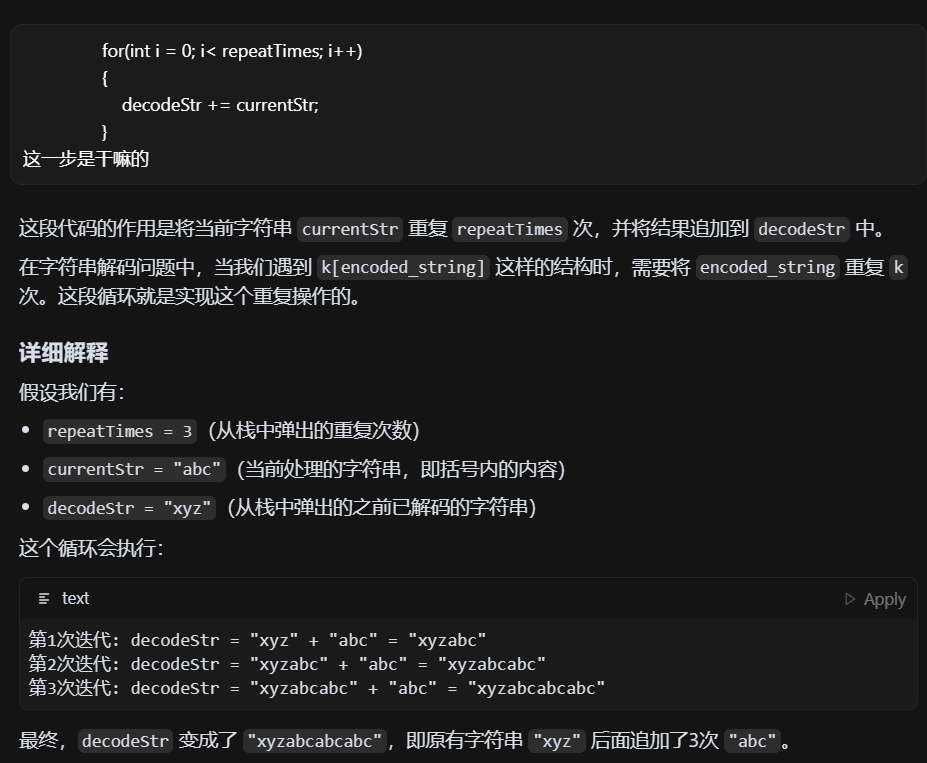

LeetCode - 394. 字符串解码

题目 394. 字符串解码 - 力扣(LeetCode) 思路 使用两个栈:一个存储重复次数,一个存储字符串 遍历输入字符串: 数字处理:遇到数字时,累积计算重复次数左括号处理:保存当前状态&a…...

服务器硬防的应用场景都有哪些?

服务器硬防是指一种通过硬件设备层面的安全措施来防御服务器系统受到网络攻击的方式,避免服务器受到各种恶意攻击和网络威胁,那么,服务器硬防通常都会应用在哪些场景当中呢? 硬防服务器中一般会配备入侵检测系统和预防系统&#x…...

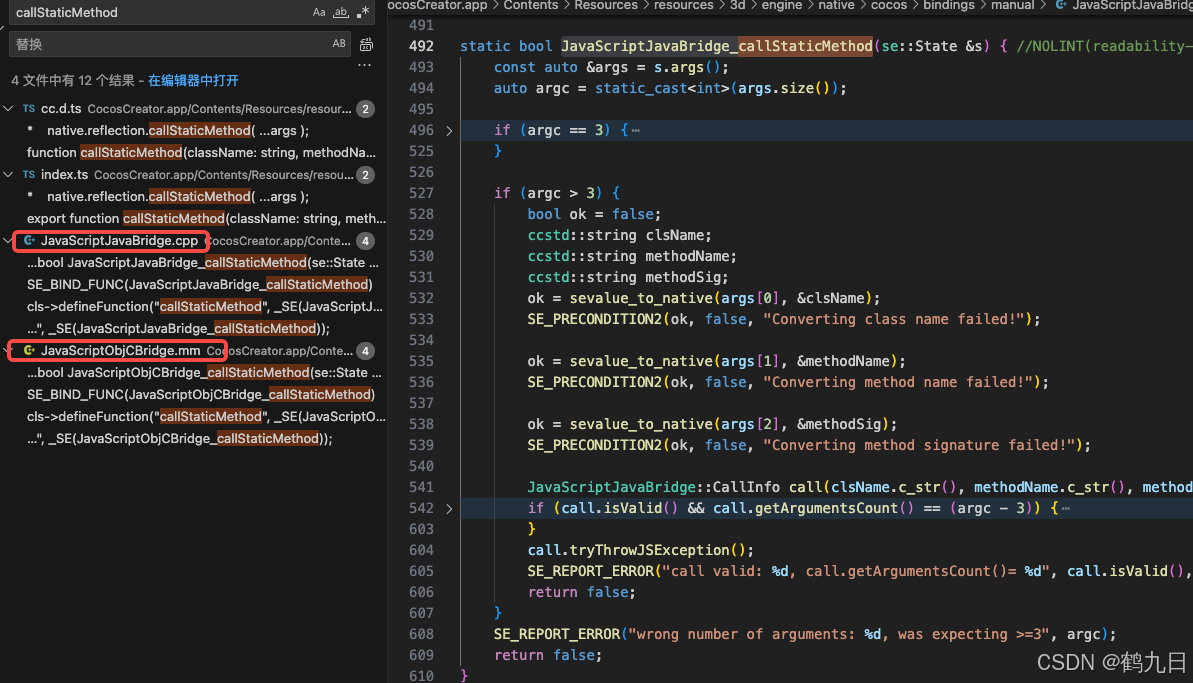

CocosCreator 之 JavaScript/TypeScript和Java的相互交互

引擎版本: 3.8.1 语言: JavaScript/TypeScript、C、Java 环境:Window 参考:Java原生反射机制 您好,我是鹤九日! 回顾 在上篇文章中:CocosCreator Android项目接入UnityAds 广告SDK。 我们简单讲…...

JDK 17 新特性

#JDK 17 新特性 /**************** 文本块 *****************/ python/scala中早就支持,不稀奇 String json “”" { “name”: “Java”, “version”: 17 } “”"; /**************** Switch 语句 -> 表达式 *****************/ 挺好的ÿ…...

ios苹果系统,js 滑动屏幕、锚定无效

现象:window.addEventListener监听touch无效,划不动屏幕,但是代码逻辑都有执行到。 scrollIntoView也无效。 原因:这是因为 iOS 的触摸事件处理机制和 touch-action: none 的设置有关。ios有太多得交互动作,从而会影响…...

Java多线程实现之Thread类深度解析

Java多线程实现之Thread类深度解析 一、多线程基础概念1.1 什么是线程1.2 多线程的优势1.3 Java多线程模型 二、Thread类的基本结构与构造函数2.1 Thread类的继承关系2.2 构造函数 三、创建和启动线程3.1 继承Thread类创建线程3.2 实现Runnable接口创建线程 四、Thread类的核心…...

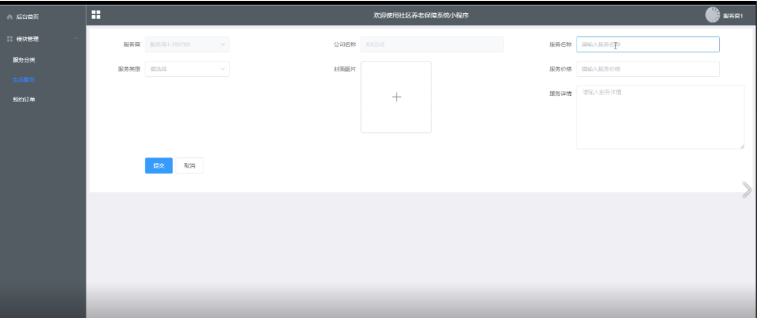

Springboot社区养老保险系统小程序

一、前言 随着我国经济迅速发展,人们对手机的需求越来越大,各种手机软件也都在被广泛应用,但是对于手机进行数据信息管理,对于手机的各种软件也是备受用户的喜爱,社区养老保险系统小程序被用户普遍使用,为方…...

MySQL 部分重点知识篇

一、数据库对象 1. 主键 定义 :主键是用于唯一标识表中每一行记录的字段或字段组合。它具有唯一性和非空性特点。 作用 :确保数据的完整性,便于数据的查询和管理。 示例 :在学生信息表中,学号可以作为主键ÿ…...