FPGA学习笔记(2)——Verilog语法及ModelSim使用

1.1 语法

1、赋值语句 = 和 <=

= 为阻塞赋值,当该语句结束时,下一个语句才开始执行,串行执行

<= 为非阻塞幅值,该语句和整个语句块同时执行,并行执行

1.2 ModelSim使用

1、修改源文件路径:File -> Source Directory/Change Directory

2、查看窗口:View -> Transcript/Project/Library

3、新建工程:File->New->Project ,添加文件夹名称

4、添加源文件和TB文件:Project 右键-> Add to Project. Existing File

5、编译:Project 右键 -> Compile All

如果出现黄色三角形的警告,查看相关文件并修改,重新编译

双击红色的警告,可以看到.v文件哪里出现问题

6、仿真:Simulate -> Start Simulate -> Design -> work

- 选择TB文件,关闭Enable optimization

7、Libraries、SDF(标准延迟文件)

8、添加信号到波形图内:sim-Default 右键添加Add Wave

某些信号看不到(no data)就重新仿真,最好先添加信号,再进行仿真。

修改Run Length 到适合的时长(例如1us),run运行设置时长

左侧Restart,重置信号。

9、命令行操作:

.main clear 清空命令行

run 1us 波形运行1us

10、ctrl+A:全选信号

ctrl+G:信号排序

1.3 Verilog

1、逻辑值:

- 0

- 1

- X(未知,可能是1/0)

- Z(高阻态,外部没有激励信号,是一个悬空状态)

2、进制:二进制(d)、八进制(o)、十进制(d)和十六进制(h)

3、数值表示:[数据位宽]'[进制][数]

例子:1’b0 8’d255 16b’1001_1010_0000_1111(下划线不影响程序读取)

4、标识符:定义模块名、端口名、信号名

任意一组字母、数字、$符号和_(下划线)

标识符第一个字符必须是字母或下划线,区分大小写。

不建议大小写混合使用,普通信号建议全部小写,信号命名最好体现信号的含义,简洁清晰易懂

例子:sum、cpu_addr、clk_50、clk_cpu

5、数据类型:寄存器、线网、参数,前两个是真正在数字电路中起作用的

(1)寄存器类型:reg,默认初始值为X

例子:

reg [31:0] delay_cnt;

reg key_reg;

注:reg类型只能在always和initial语句中被幅值。

时序逻辑:always语句带有时钟信号,则该寄存器变量对应为触发器;

组合逻辑:always语句不带有时钟信号,则该寄存器变量对应为硬件连线;

(2)线网类型:表示结构实体之间的物理连线,此变量不能存储值,它的值由驱动它的元件所决定。

驱动线网类型变量的元件有门、连续幅值语句、assign。

如果没有驱动元件连接到线网上,线网为高阻态z。

例子:

wire key_flag;

(3)参数类型:常量,用parameter定义常量。

例子:

parameter H_SYNC = 11’d41; //行同步

parameter H_BACK = 11’b2; //行显示后沿

parameter H_DISP = 11’d480; //行有效数据

parameter H_FRONT = 11’d2; //行显示前沿

parameter H_TOTAL = 11’d525; //行扫描周期

参数型数据常用于定义状态机的状态、数据的位宽和延迟大小。

标识符、参数传递

6、运算符:算数运算符(+ - * / %)、关系运算符(> < >= <= == !=)、逻辑运算符(! && ||)、

条件运算符(? : ,例子:a?b:c,a为真,选择b,否则选择c)、位运算符(~ & | ^)、

移位运算符(<< >> ,例子:8’b11110000 >>2 = 2’b00111100,0填充)、拼接运算符({})

有优先级,用括号!

7、注释方式: // 和 /* */

8、关键字

变量名不能与关键字同名

9、框架:

(1)模块block(包括接口和逻辑功能)

例子:

module block(a,b,c,d);input a,b;output c,d;assign c = a | b;assign d = a & b;

endmodule

每个verilog程序包括:端口定义、IO说明、内部信号声明、功能定义。

注意:有可以综合的语句和不可综合的语句(仿真)

(2)可综合的语句:

assign、always、例化实例元件,这三种逻辑功能是并行的。

(2-1)在always块中,逻辑是顺序执行的。

而多个always块之间是并行的。

(2-2)模块调用:信号通过模块端口在模块之间传递。

例子:

文件seg_led_static_top.v:

module seg_led_static_top(input sys_clk,input sys_rst_n,output [5:0] sel,output [7:0] seg_led

);parameter TIME_SHOW = 25'd25000_000;wire add_flag;//模块调用1:time_count #(.MAX_NUM (TIME_SHOW) //参数传递) u_time_count(.clk (sys_clk),.rst_n (sys_rst_n),.flag (add_flag));//模块调用2:必须按照模块定义顺序列写(不推荐)time_count #(.MAX_NUM (TIME_SHOW) //参数传递) u_time_count(sys_clk,sys_rst_n,add_flag);

endmodule

其他文件 time_cout.v:

module time_count(input clk,input rst_n,output reg flag

);parameter MAX_NUM = 50000_00;

reg [24:0] cnt;

10、结构语句:

(1)initial:在模块中只执行一次。常用来写测试文件,产生仿真测试信号(激励信号)和对存储器赋初始值。

例子:

initial beginsys_clk <= 1'b0;sys_rst_n <= 1'b0;touch_key <= 1'b0;#20 sys_rst_n <= 1'b0;

end

(2)always:不断重复活动,但是只有和一定的时间控制结合在一起才有作用。

例子:

always #10 sys_clk = ~sys_clk;

always的时间控制有:边沿触发,电平触发

可以是单个信号,也可以是多个信号(用or连接)

例子:

always @(posedge sys_clk or negedge sys_rst_n) begin //敏感列表if (!sys_rst_n)counter <= 24'd0;else if(counter < 24'd1000_0000)counter <= counter + 1'b1;elsecounter <= 24'd0;

end

边沿触发(posedge,negedge)的always常常描述时序逻辑行为。使用非阻塞幅值<=

电平触达的always常常描述组合逻辑行为。使用阻塞幅值=

例子:

always @(a or b or c or d or e) beginout = a ?(b+c):(d + e);

end

可以用*代表所有变量,@(*)对后面语句块所有输入变量的变化都是敏感的!

always @(*) beginout = a ?(b+c):(d + e);

end

组合逻辑没有CLK信号,时序逻辑有CLK信号,具备记忆功能。

注意:

(1)不允许在多各always块中对同一个变量进行幅值

(2)在同一个always块中不要既用非阻塞幅值又用阻塞赋值

11、条件语句:

(1)if

if (a > b)out = data_1;

(2)if else

if (a > b)out = data_1;

elseout = data_2;

(3)if else嵌套:

if (fx1)out = data_1;

else if(fx2)out = data_2;

else if(fx3)out = data_3;

elseout = data_4;

(4)使用begin和end包含多个语句:

if (a) begin语句1;语句2;

end

else begin语句1;语句2;

end

判断表达式的值:若为0,x,z,按照假进行处理,若为1,按照真处理。

(5)case语句:

casez:比较时,不考虑表达式中的高阻态z。

casex:比较时,不考虑高阻态z和不定值x

例子:

case(num)4'h0 : seg_led <= 8'b1111_0000;4'h1 : seg_led <= 8'b0000_0000;default : seg_led <= 8'b1111_1111;

endcase

注意:num和n’hx必须位宽相等。

casex(sel)8'b1100_zzzz : 语句1;8'b1100_xxzz : 语句2;

endcase

1.4 状态机

例子:利用FPGA实现电子门锁。

序列检测器

1、状态机(FSM):在有限个状态之间按一定规律转换的时序电路

2、模型:

(1)mealy状态机:输出与输入信号和当前状态有关。

组合逻辑F->状态寄存器->组合逻辑G

(2)moore状态机:输出只与当前状态有关。

3、状态机设计:

(1)步骤:状态空间定义,状态跳转,下个状态判断,各个状态下的动作。

例子:

/* part1:状态空间定义 */

//define state space

parameter SLEEP = 2'b00;

parameter STUDY = 2'b01;

parameter EAT = 2'b10;

parameter AMUSE = 2'b11;

//internal variable

reg [1:0] current_state;

reg [1:0] next_state;//独热码:每个状态只有一个寄存器置位,译码逻辑简单,生成的电路简单。

parameter SLEEP = 4'b0001;

parameter STUDY = 4'b0010;

parameter EAT = 4'b0100;

parameter AMUSE = 4'b1000;

//internal variable

reg [3:0] current_state;

reg [3:0] next_state;/* part2:状态跳转 */

//transition

always @(posedge clk or negedge rst_n) begin //敏感列表:时钟信号以及复位信号边沿的组合if(!rst_n)current_state <= SLEEP;elsecurrent_state <= next_state; //使用非阻塞赋值

end/* part3:下个状态判断(组合逻辑) */

//next state decision

always @(current_state or input_signals) begincase (current_state)SLEEP :beginif (clock_alarm)next_state = STUDY;elsenext_state = SLEEP;endSTUDY :beginif (lunch_time)next_state = EAT;elsenext_state = STUDY;endEAT :beginif (lunch_time)next_state = EAT;elsenext_state = STUDY;endAMUSE :beginif (lunch_time)next_state = EAT;elsenext_state = STUDY;enddefault:beginif (lunch_time)next_state = EAT;elsenext_state = STUDY;endendcase

end

注意:

(1)组合逻辑使用阻塞赋值

(2)if/else要配对以免产生latch(锁存器),case的状态如果没有给完全,必须要给default,否则也会生成latch

/* part4:各个状态下的动作(组合逻辑) */

//action

wire read_book;

assign read_book = (current_state == STUDY) ? 1'b1 : 1'b0;always @(current_state) beginif(current_state == STUDY)read_book = 1'b1;elseread_book = 1'b0;

end

注意:组合逻辑使用阻塞赋值

一个三段式状态机例子:divider7_fsm.v

三段式可以在组合逻辑后再增加一级寄存器(时序逻辑,有clk信号输入)来实现时序逻辑输出:

(1)可以有效滤除组合逻辑输出的毛刺;

(2)可以有效地进行时序计算和约束;

(3)对总线形式的输出信号来说,容易使总线数据对齐,从而减小总线数据间的偏移,减小接收端数据采样出错的频率。

相关文章:

——Verilog语法及ModelSim使用)

FPGA学习笔记(2)——Verilog语法及ModelSim使用

1.1 语法 1、赋值语句 和 < 为阻塞赋值,当该语句结束时,下一个语句才开始执行,串行执行 < 为非阻塞幅值,该语句和整个语句块同时执行,并行执行 1.2 ModelSim使用 1、修改源文件路径:File -> …...

2024年十大AI工具,让你的工作学习效率飞跃

在这个迅速变化的数字时代,人工智能技术正在以前所未有的速度发展和革新。AI技术不仅深入科研、医疗和教育等领域,还广泛应用于日常生活和商业活动中。本文梳理了2024年十款最好用的AI工具,它们各有特色,能极大提升工作效率和生活…...

linux之NAMP

linux之NAMP Nmap(Network Mapper)是一个开源的网络扫描和安全审计工具。它被设计用来快速地扫描大型网络,尽管它也可以对单个主机进行有效的扫描。Nmap利用原始IP数据包以多种方式探测目标网络上的主机、服务(应用程序名称和版本…...

uniapp 禁止截屏(应用内,保护隐私)插件 Ba-ScreenShot

禁止截屏(应用内,保护隐私) Ba-ScreenShot 简介(下载地址) Ba-ScreenShot 是一款uniapp禁止应用内截屏的插件,保护隐私,支持禁止截屏、放开截屏 截图展示 也可关注博客,实时更新最…...

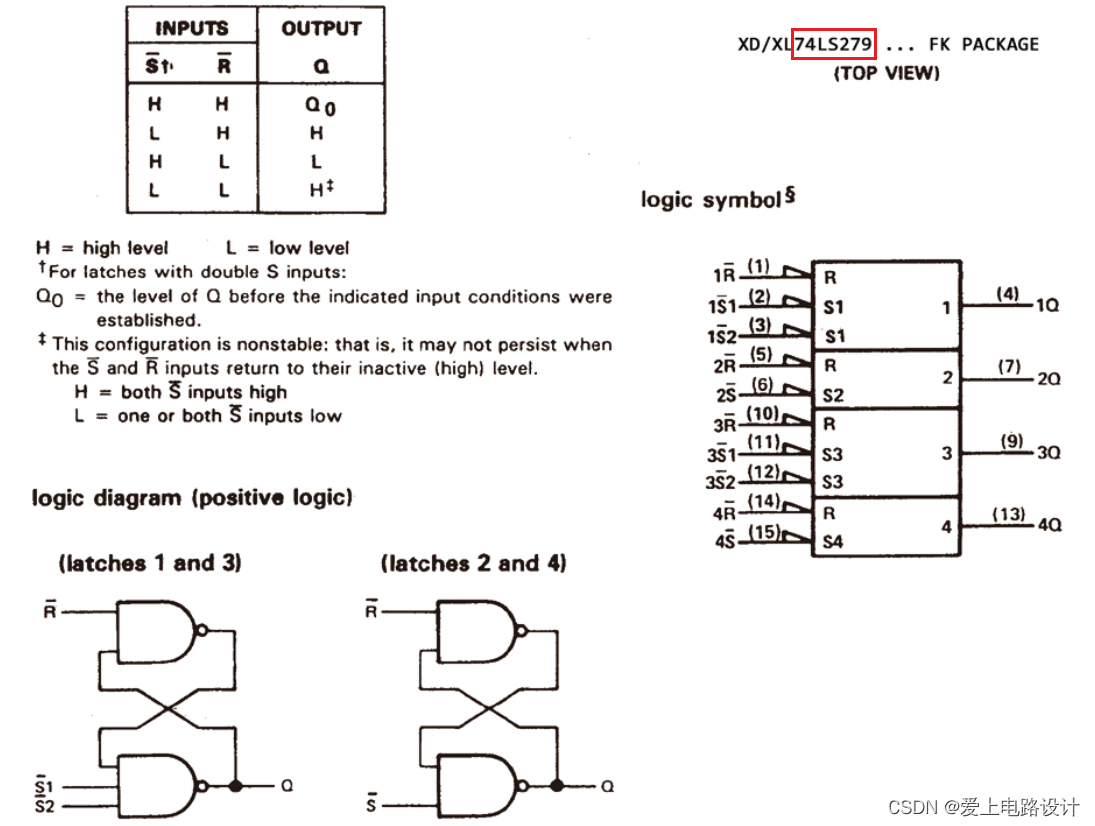

数字电路-5路呼叫显示电路和8路抢答器电路

本内容涉及两个电路,分别为5路呼叫显示电路和8路抢答器电路,包含Multisim仿真原文件,为掌握FPGA做个铺垫。紫色文字是超链接,点击自动跳转至相关博文。持续更新,原创不易! 目录: 一、5路呼叫显…...

C++中的函数签名

前言: 很多C初学者会发现函数签名这一概念在C的学习过程中经常出现,然而很多人往往不太了解函数签名包括些什么,本文章将从一个初学者的角度出发,详细解释函数签名这一概念。 在C中,函数签名用于唯一地识别函数重载。…...

Mac brew安装Redis之后更新配置文件的方法

安装命令 brew install redis 查看安装位置命令 brew list redis #查看redis安装的位置 % brew list redis /usr/local/Cellar/redis/6.2.5/.bottle/etc/ (2 files) /usr/local/Cellar/redis/6.2.5/bin/redis-benchmark /usr/local/Cellar/redis/6.2.5/bin/redis-check-ao…...

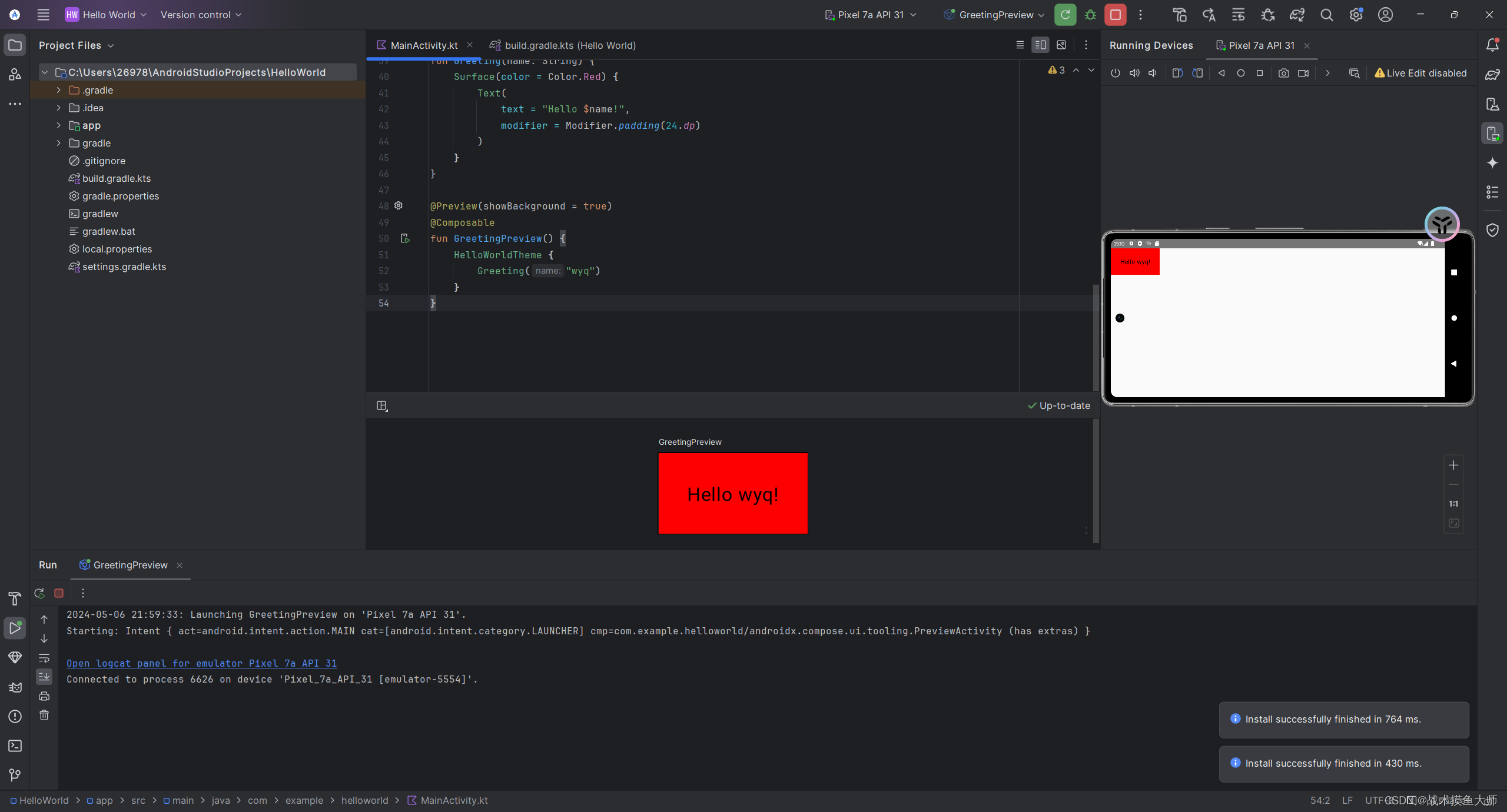

安卓应用开发(一):工具与环境

开发工具 Android Studio,用于开发 Android 应用的官方集成开发环境 (IDE)。包括以下功能: 基于Gradle的构建系统 gradle是一个项目构建工具,将源工程打包构建为apk 安卓模拟器统一环境代码编辑模拟器实时更新Github集成Lint功能࿰…...

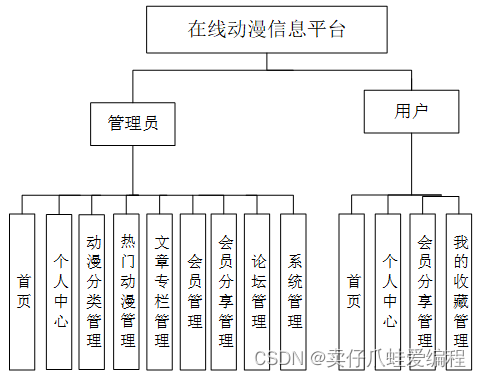

基于springboot+vue+Mysql的在线动漫信息平台

开发语言:Java框架:springbootJDK版本:JDK1.8服务器:tomcat7数据库:mysql 5.7(一定要5.7版本)数据库工具:Navicat11开发软件:eclipse/myeclipse/ideaMaven包:…...

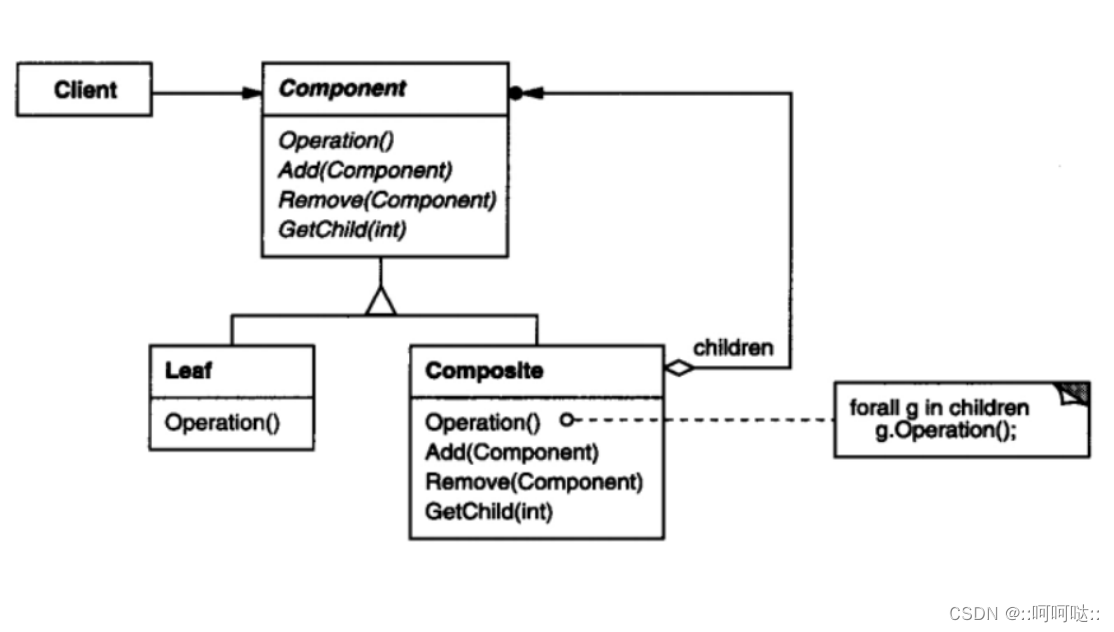

C++设计模式-结构型设计模式

写少量的代码来应对未来需求的变化。 单例模式 定义 保证一个类仅有一个实例,并提供一个该实例的全局访问点。——《设计模式》GoF 解决问题 稳定点: 类只有一个实例,提供全局的访问点(抽象) 变化点:…...

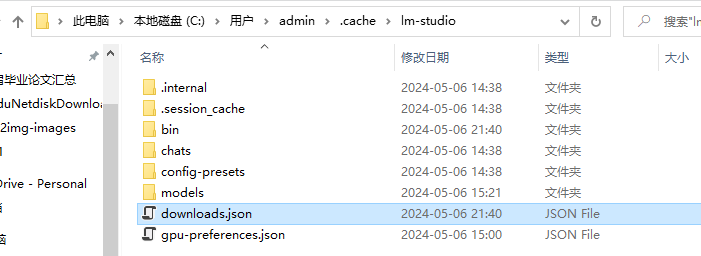

open-webui+ollama本地部署Llama3

前言 Meta Llama 3 是由 Meta 公司发布的下一代大型语言模型,拥有 80 亿和 700 亿参数两种版本,号称是最强大的开源语言模型。它在多个基准测试中超越了谷歌的 Gemma 7B 和 Mistral 7B Instruct 模型。 安装 1.gpt4all https://github.com/nomic-ai/…...

个人对行为型设计模式的理解 @by_TWJ

目录 1. 访问者模式2. 迭代器模式3. 观察者模式4. 模板模式5. 状态模式6. 备忘录模式7. 策略模式8. 解释器模式9. 责任链模式10. 命令模式11. 中介者模式 研究了一下,我为了方便理解,对它们进行了分类: 针对请求者与执行者关系方面 1对多 - 责…...

苹果挖走大量谷歌人才,建立神秘人工智能实验室;李飞飞创业成立「空间智能」公司丨 RTE 开发者日报 Vol.197

开发者朋友们大家好: 这里是 「RTE 开发者日报」 ,每天和大家一起看新闻、聊八卦。我们的社区编辑团队会整理分享 RTE(Real Time Engagement) 领域内「有话题的 新闻 」、「有态度的 观点 」、「有意思的 数据 」、「有思考的 文…...

行业唯一!易保全牵头编制的《区块链数据访问安全技术通则》发布

近日,易保全牵头参与编制的《区块链数据访问安全技术通则》经中国国际经济技术合作促进会正式发布,为中国区块链数据安全技术提供了标准参考。 易保全作为牵头起草单位、易保全CEO兼董事长刘刚担任主要起草人参与其中,在区块链技术安全风险…...

Rust Rocket创建第一个hello world的Web程序 Rust Rocket开发常用网址和Rust常用命令

一、Rust Rocket简介 Rust Rocket 是一个用 Rust 语言编写的 Web 应用框架,它结合了 Rust 的安全性和性能优势,以及 Web 开发的便利性。以下是 Rust Rocket 框架的一些优点: 安全性:Rust 是一种注重安全性的编程语言,…...

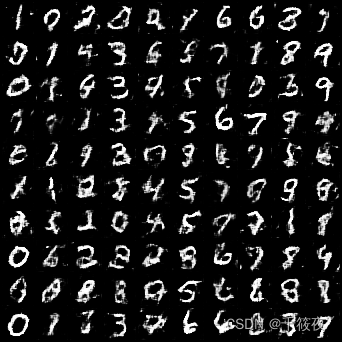

第G9周:ACGAN理论与实战

🍨 本文为🔗365天深度学习训练营 中的学习记录博客🍖 原作者:K同学啊 | 接辅导、项目定制🚀 文章来源:K同学的学习圈子 上一周已经给出代码,需要可以跳转上一周的任务 第G8周:ACGAN任…...

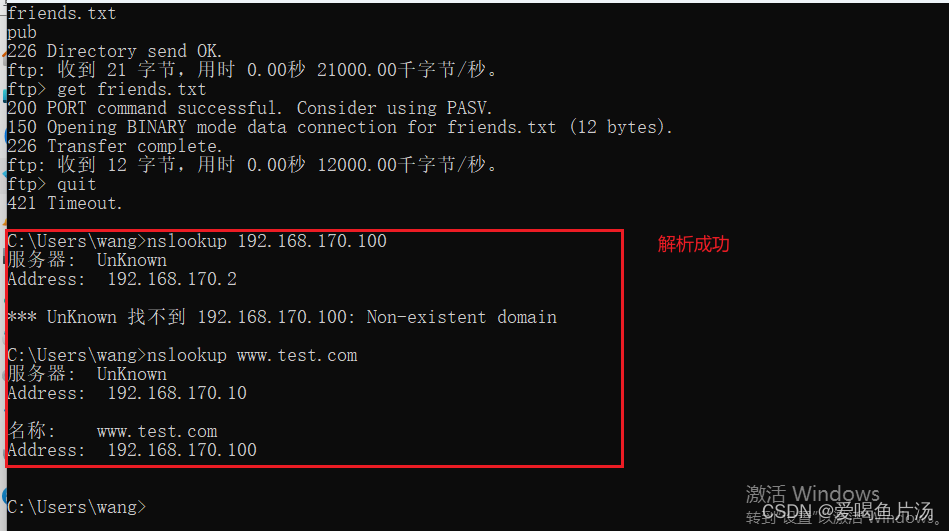

Linux网络部分——DNS域名解析服务

目录 1. 域名结构 2. 系统根据域名查找IP地址的过程 3.DNS域名解析方式 4.DNS域名解析的工作原理【☆】 5.域名解析查询方式 6.搭建主从DNS域名服务器 ①初始化操作主服务器和从服务器,安装BIND软件 ②修改主服务器的主配置文件、区域配置文件、区域数…...

预处理详解

乐观学习,乐观生活,才能不断前进啊!!! 我的主页:optimistic_chen 我的专栏:c语言 点击主页:optimistic_chen和专栏:c语言, 创作不易,大佬们点赞鼓…...

Python的创建和使用自定义模块

Python 的模块是组织代码的基本单元,它可以包含变量、函数、类等,并且可以被其他 Python 程序引用和重用。除了使用 Python 提供的标准库和第三方库外,开发者还可以创建自定义模块,用于组织和管理自己的代码。本文将详细介绍如何创…...

Python根据预设txt生成“你画我猜”题目PPT(素拓活动小工具)

Python根据预设txt生成“你画我猜”题目PPT(素拓活动小工具) 场景来源 去年单位内部的一次素拓活动,分工负责策划设置其中的“你画我猜”环节,网络上搜集到题目文字后,想着如何快速做成对应一页一页的PPT。第一时间想…...

RestClient

什么是RestClient RestClient 是 Elasticsearch 官方提供的 Java 低级 REST 客户端,它允许HTTP与Elasticsearch 集群通信,而无需处理 JSON 序列化/反序列化等底层细节。它是 Elasticsearch Java API 客户端的基础。 RestClient 主要特点 轻量级ÿ…...

未来机器人的大脑:如何用神经网络模拟器实现更智能的决策?

编辑:陈萍萍的公主一点人工一点智能 未来机器人的大脑:如何用神经网络模拟器实现更智能的决策?RWM通过双自回归机制有效解决了复合误差、部分可观测性和随机动力学等关键挑战,在不依赖领域特定归纳偏见的条件下实现了卓越的预测准…...

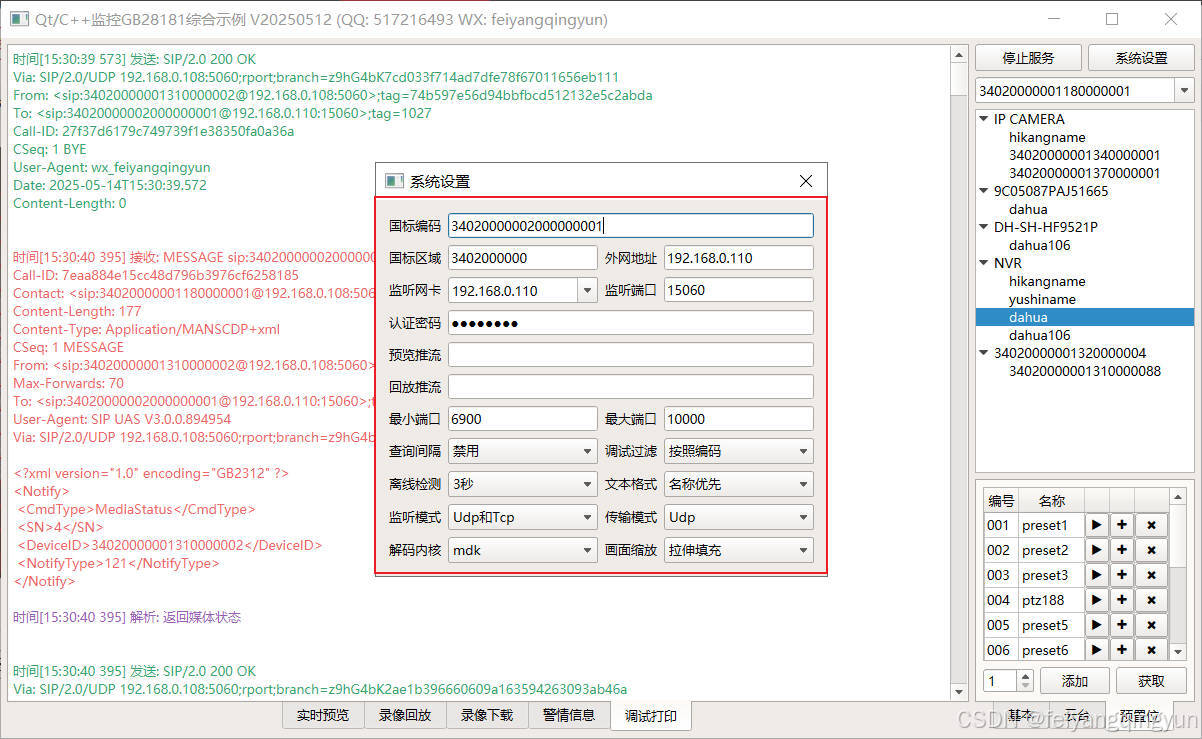

Qt/C++开发监控GB28181系统/取流协议/同时支持udp/tcp被动/tcp主动

一、前言说明 在2011版本的gb28181协议中,拉取视频流只要求udp方式,从2016开始要求新增支持tcp被动和tcp主动两种方式,udp理论上会丢包的,所以实际使用过程可能会出现画面花屏的情况,而tcp肯定不丢包,起码…...

解锁数据库简洁之道:FastAPI与SQLModel实战指南

在构建现代Web应用程序时,与数据库的交互无疑是核心环节。虽然传统的数据库操作方式(如直接编写SQL语句与psycopg2交互)赋予了我们精细的控制权,但在面对日益复杂的业务逻辑和快速迭代的需求时,这种方式的开发效率和可…...

el-switch文字内置

el-switch文字内置 效果 vue <div style"color:#ffffff;font-size:14px;float:left;margin-bottom:5px;margin-right:5px;">自动加载</div> <el-switch v-model"value" active-color"#3E99FB" inactive-color"#DCDFE6"…...

大学生职业发展与就业创业指导教学评价

这里是引用 作为软工2203/2204班的学生,我们非常感谢您在《大学生职业发展与就业创业指导》课程中的悉心教导。这门课程对我们即将面临实习和就业的工科学生来说至关重要,而您认真负责的教学态度,让课程的每一部分都充满了实用价值。 尤其让我…...

Redis数据倾斜问题解决

Redis 数据倾斜问题解析与解决方案 什么是 Redis 数据倾斜 Redis 数据倾斜指的是在 Redis 集群中,部分节点存储的数据量或访问量远高于其他节点,导致这些节点负载过高,影响整体性能。 数据倾斜的主要表现 部分节点内存使用率远高于其他节…...

)

Angular微前端架构:Module Federation + ngx-build-plus (Webpack)

以下是一个完整的 Angular 微前端示例,其中使用的是 Module Federation 和 npx-build-plus 实现了主应用(Shell)与子应用(Remote)的集成。 🛠️ 项目结构 angular-mf/ ├── shell-app/ # 主应用&…...

【Java学习笔记】BigInteger 和 BigDecimal 类

BigInteger 和 BigDecimal 类 二者共有的常见方法 方法功能add加subtract减multiply乘divide除 注意点:传参类型必须是类对象 一、BigInteger 1. 作用:适合保存比较大的整型数 2. 使用说明 创建BigInteger对象 传入字符串 3. 代码示例 import j…...

JAVA后端开发——多租户

数据隔离是多租户系统中的核心概念,确保一个租户(在这个系统中可能是一个公司或一个独立的客户)的数据对其他租户是不可见的。在 RuoYi 框架(您当前项目所使用的基础框架)中,这通常是通过在数据表中增加一个…...