ADC模-数转换原理与实现

1. 今日摸鱼计划

| 今天来学习一下ADC的原理,然后把ADC给实现 ADC芯片:ADC128S102 |

| 视频: 18A_基于SPI接口的ADC芯片功能和接口时序介绍_哔哩哔哩_bilibili 18B_使用线性序列机思路分析SPI接口的ADC芯片接口时序_哔哩哔哩_bilibili 18C_基于线性序列机的SPI接口ADC控制逻辑设计_哔哩哔哩_bilibili |

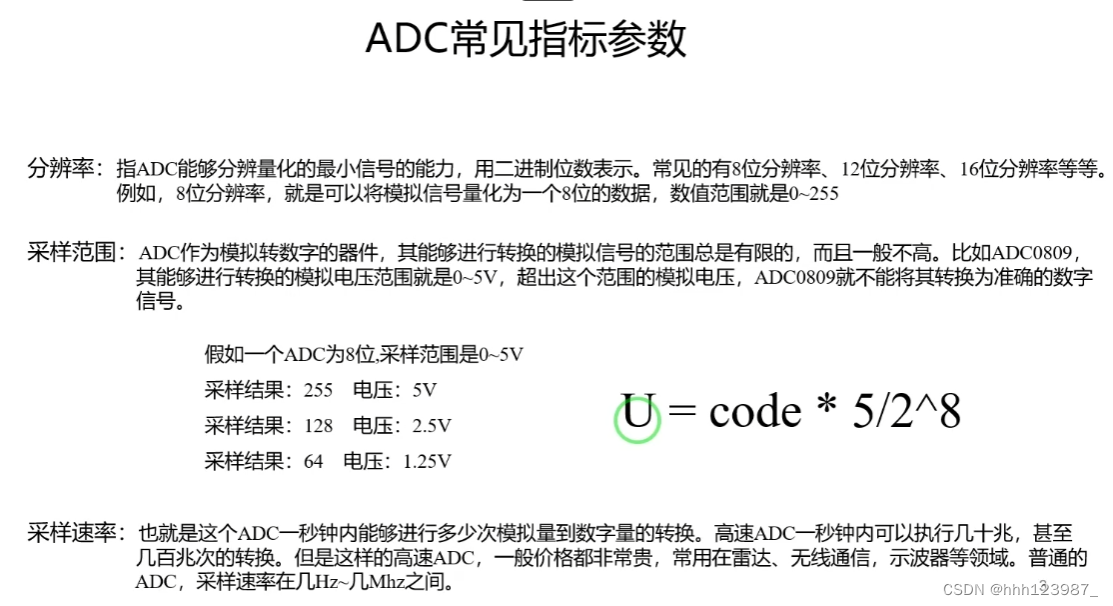

2. ADC指标参数

3. ADC128S102

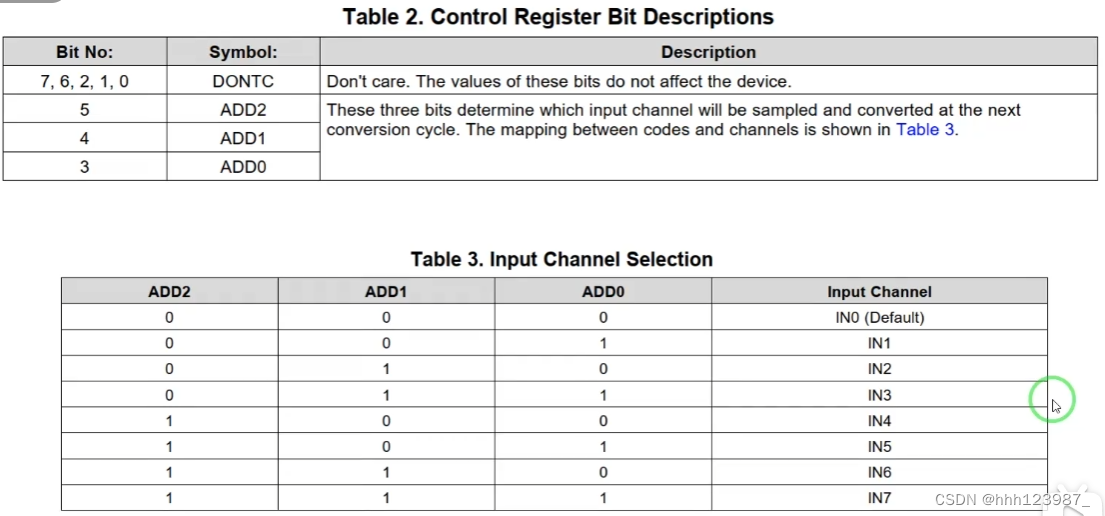

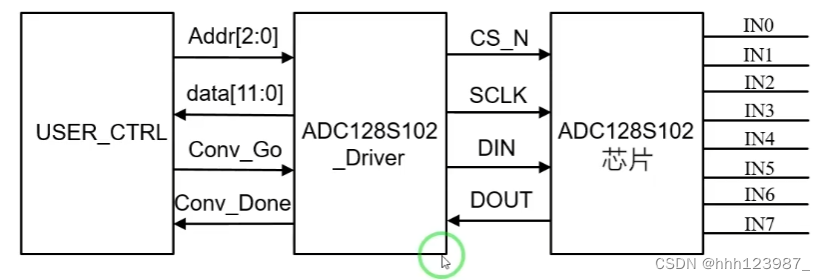

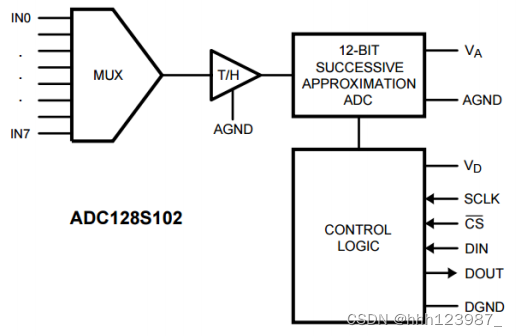

在 ACZ702 EDA 扩展板上使用的模数转换器为逐次逼近型的低功耗芯片ADC128S102,其具有 8 通道以及 12 位的分辨率。电源采用独立的模拟供电以及数字供电,其中模拟电源 VA输入范围为 2.7V~5.25V,数字电源 VD输入范围为 2.7V~VA。其与外部通信支持多种接口如:SPI、QSPI、MICROWIRE以及通用的 DSP 接口。转换速度在 500 kps~1 Mkps,典型情况下当 3V 供电时功耗为2.3mW,5V 供电时为 10.7mW,如下图为该 ADC 芯片的内部结构图。

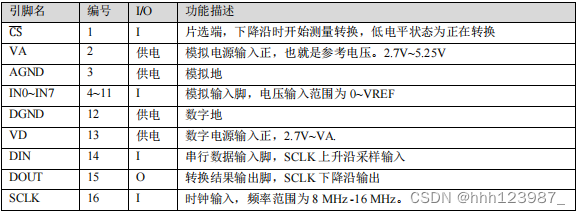

芯片引脚功能如下:

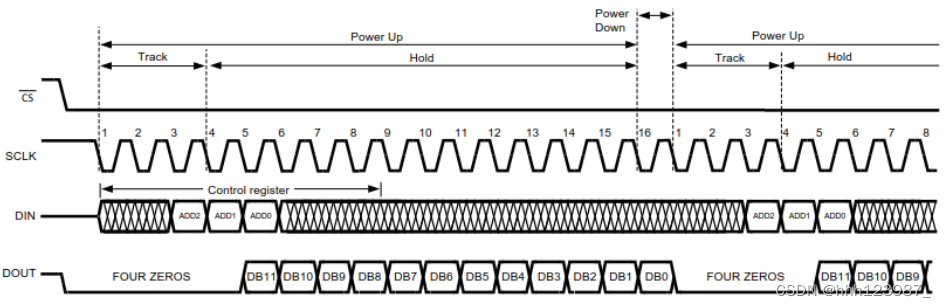

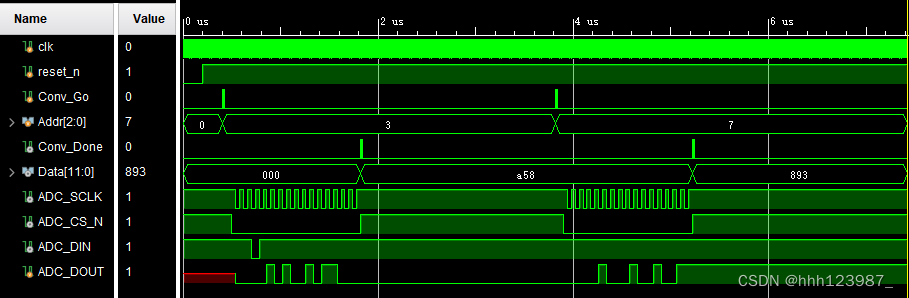

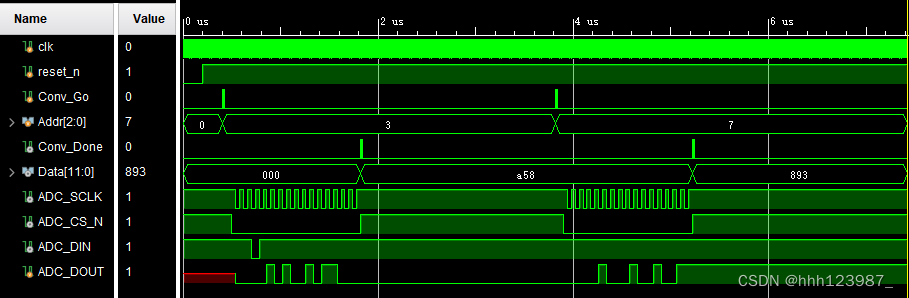

ADC128S102通过 SPI接口与控制器进行通信的时序图如下图所示:

四线SPI分析:

| CS | 片选信号(本摸鱼怪不会加横线) CS拉低,表示通信的开始,CS拉高表示通信结束 |

| SCLK | CS 为高时 SCLK 默认高 一帧包含 16 个上升沿 SCLK |

| DIN | SCLK的上升沿,DIN上的信号要保持稳定,此时ADC芯片会对DIN上的信号采样

|

| DOUT | 当CS 为高时代表空闲状态,当为低时为传输状态 |

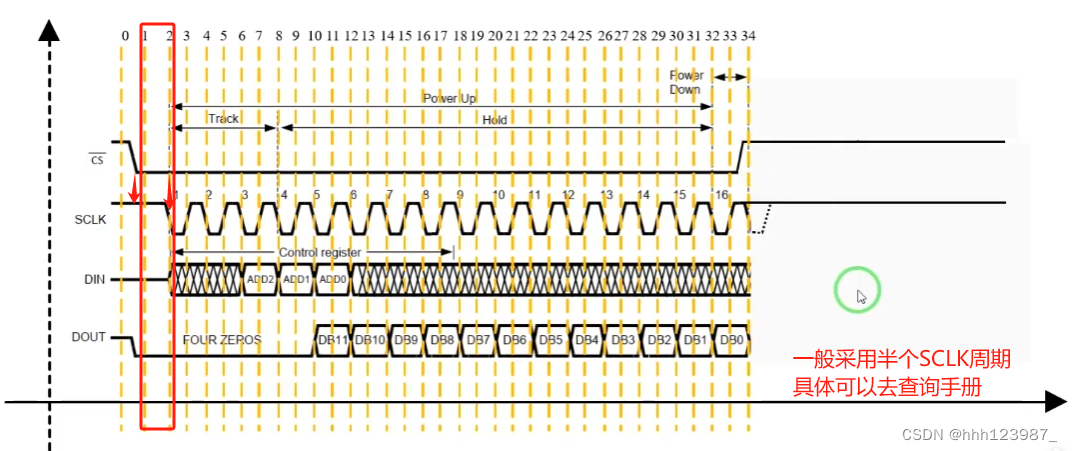

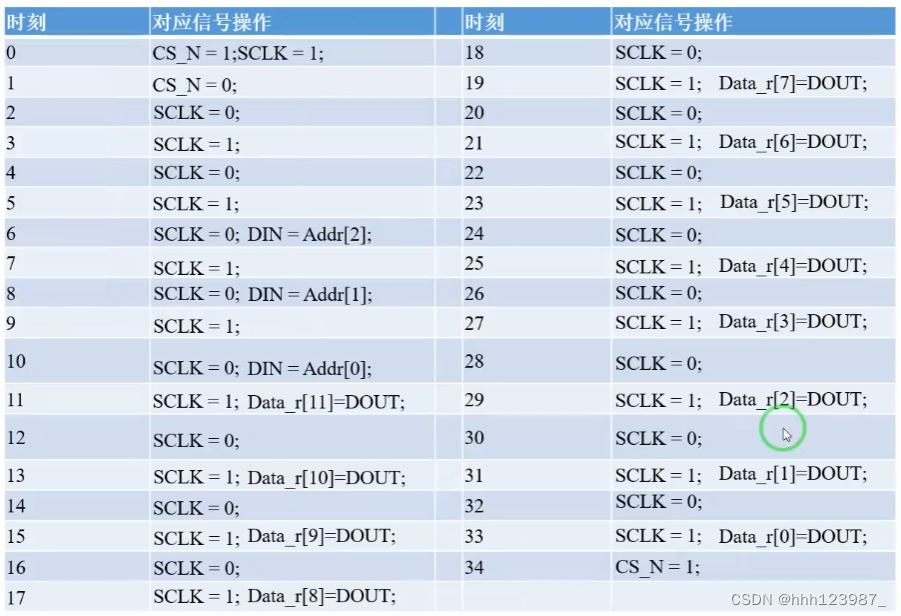

4. 线性序列机实现ADC

|

|

|

|

| module adc128s102( reg[7:0]DIV_CNT; reg [11:0]Data_r; always@(posedge Clk or negedge Reset_n)

always@(posedge Clk or negedge Reset_n ) endmodule |

5. adc128s102_tb

| `timescale 1ns/1ns module adc128s102_tb; reg clk; adc128s102 adc128s102( .Conv_Done(Conv_Done), |

相关文章:

ADC模-数转换原理与实现

1. 今日摸鱼计划 今天来学习一下ADC的原理,然后把ADC给实现 ADC芯片:ADC128S102 视频: 18A_基于SPI接口的ADC芯片功能和接口时序介绍_哔哩哔哩_bilibili 18B_使用线性序列机思路分析SPI接口的ADC芯片接口时序_哔哩哔哩_bilibili 18C_基于线性序列机的S…...

Android 文件传输

目录 device explorer 文件目录关系对应: device explorer 经常写adb命令传文件,结果发现Android studio有自带的文件管理器,可以上传下载文件。 tool windows ->device explorer 文件目录关系对应: Android java获取的程序…...

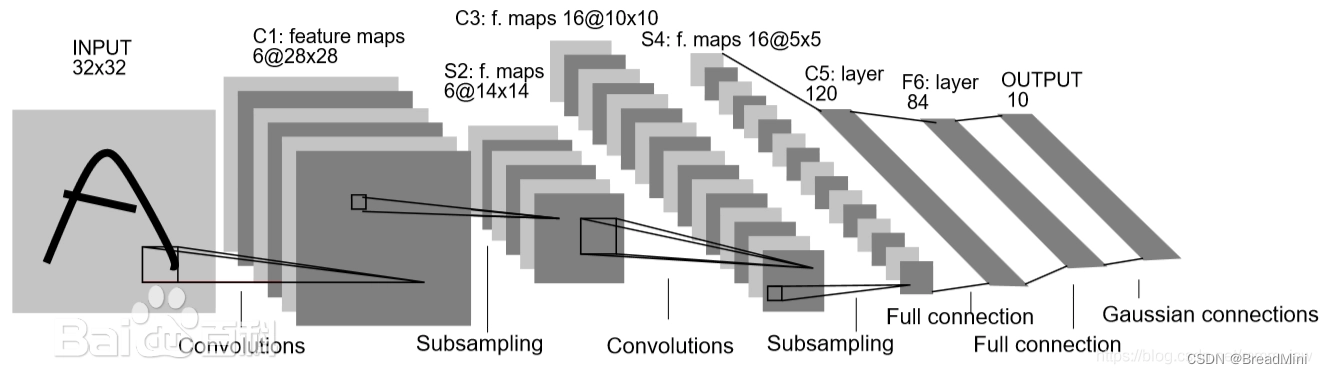

一起深度学习

CIFAR-10 卷积神经网络 下载数据集构建网络运行测试 下载数据集 batchsz 32cifar_train datasets.CIFAR10(data,trainTrue,transformtorchvision.transforms.Compose([torchvision.transforms.Resize((32,32)),torchvision.transforms.ToTensor()]),downloadTrue)cifar_train …...

servlet-会话(cookie与session)

servlet会话技术 会话技术cookie创建Cookieindex.jspCookieServlet 获取Cookieindex.jspshowCookie session创建sessionindex.jsplogin.jspLoginServlet 获取sessionRedurectServket 清除会话login.jspClearItmeServlet 会话技术 两种会话:cookie,sessi…...

windows11忘记登录密码怎么办?

STEP1:进入Win RE界面 1.按住shift不要松手,点击重新启动,进入WINRE界面 2.选择疑难解答 选择高级选项 点击命令提示符 STEP2:替换utilman 1.输入以下代码查看所在windows所在盘 diskpart list volume exit 2.根据所在盘输入命令(以C盘为…...

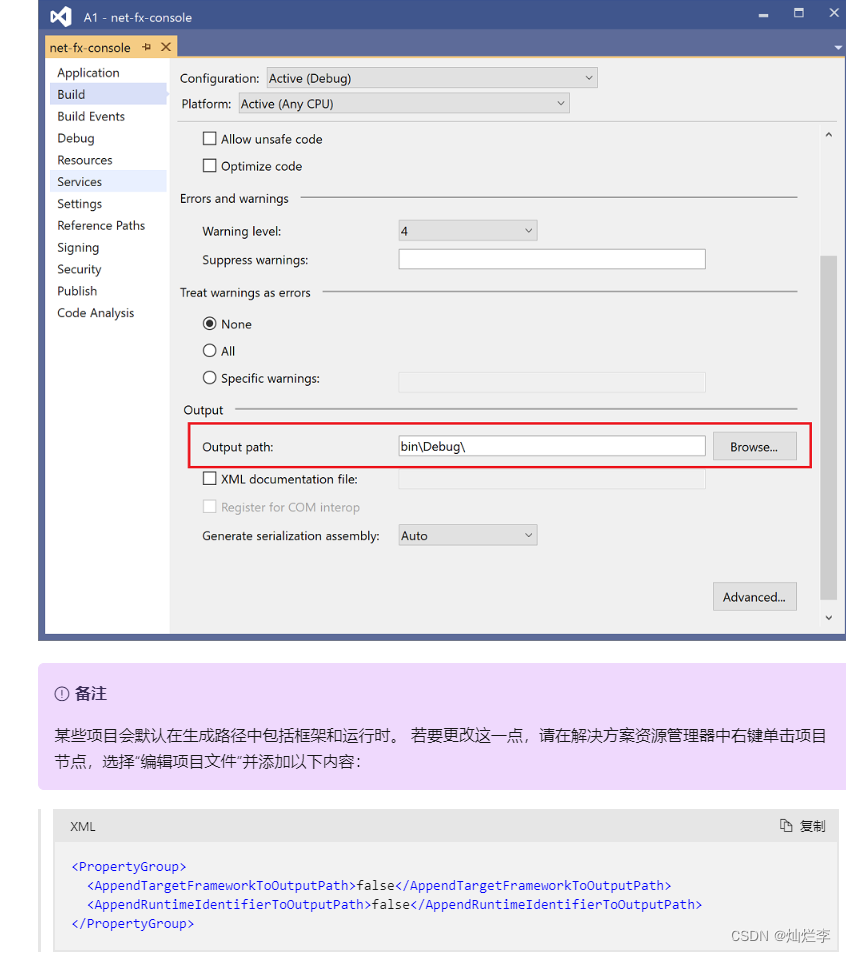

C#里如何设置输出路径,不要net7.0-windows

官网介绍: 更改生成输出目录 - Visual Studio (Windows) | Microsoft Learn <PropertyGroup> <AppendTargetFrameworkToOutputPath>false</AppendTargetFrameworkToOutputPath> <AppendRuntimeIdentifierToOutputPath>false</Appen…...

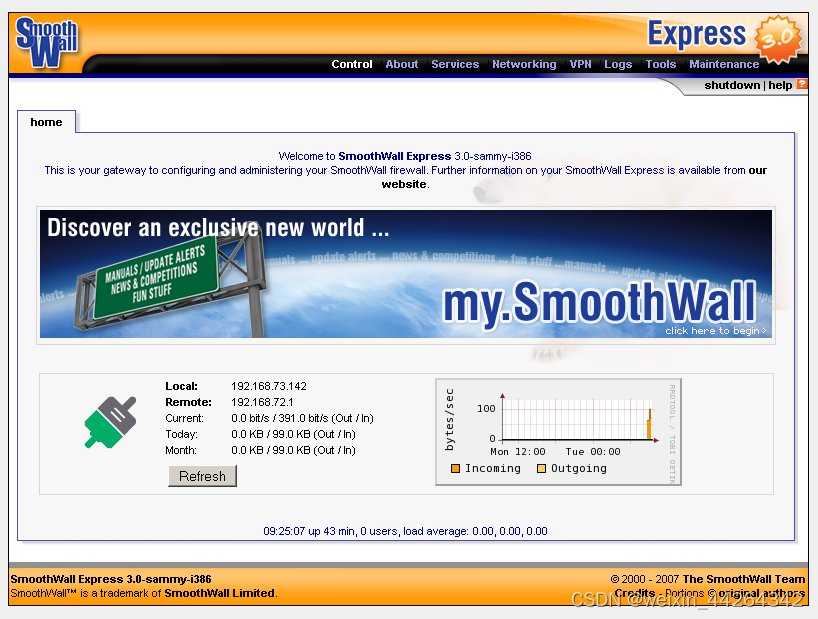

知名员工上网行为管理系统推荐榜单

上网行为管理软件旨在帮助组织监控和管理员工的网络活动,以提高工作效率、确保网络安全和合规性。以下是一些常见的上网行为管理软件: Ping32:Ping32是一款专业的员工上网行为管理系统,Ping32作为一款专业的员工上网行为管理系统&…...

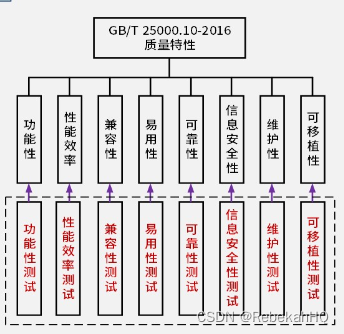

第12章 软件测试基础(第三部分)测试类型、测试工具

七、测试类型(按工程阶段划分) 单集系确收 (一)单元测试 1、单元测试/模块测试 单元就是软件中最小单位(或模块)。可以是一个函数、一个过程、一个类。主要依据是模块的详细设计文档。价值在于尽早发现…...

open-vm-tools使用虚机的拷贝/粘切

open-vm-tools 是一组用于 VMware 虚拟机中的开源工具,它们提供了一些与虚拟机操作和管理相关的功能。这些工具与 VMware 虚拟化平台集成,可以在虚拟机中提供更好的性能和功能。以下是一些 open-vm-tools 提供的功能: 1. 虚拟机增强功能: open-vm-tools 提供了与 VMware 虚…...

CKEditor编辑器的简单使用方法,取值,赋值

先从官网下载包。CKEditor 4 - Download Latest Version. 一:在项目里引用JQ基础包和CK的JS包 <script src"/JS/jquery-3.4.1.js?v1.0"></script><script src"/ckeditor/ckeditor.js"></script> 二:在表…...

创建一个线程对象需要花费多少内存空间

创建一个std::thread对象所需的内存空间大小并不是固定的,因为它取决于多种因素,包括C运行时库的实现、编译器优化、以及可能的平台和架构差异。 std::thread对象本身是一个轻量级的控制块,它主要用于管理线程的执行,包括保存线程…...

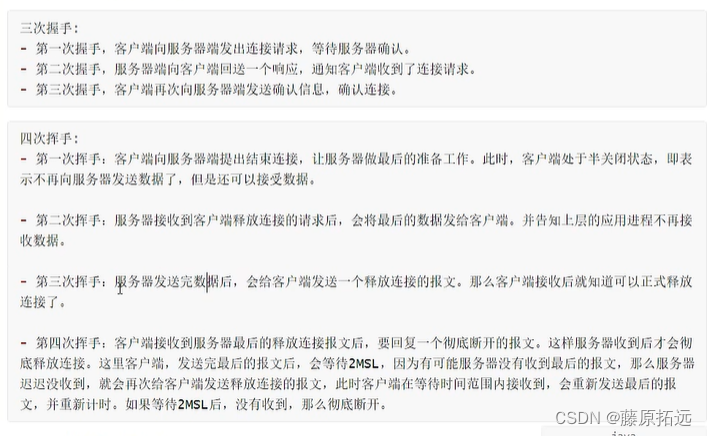

Java -- (part23)

一.网络编程 1.概述 在网络通信协议下,不同计算机上运行的程序,进行数据传输 2.软件架构 CS架构:客户端和服务端 BS架构:浏览器和服务端 3.服务器概念 安装了服务器软件的计算机 4.通信三要素 IP地址 a.概述 计算机的唯一标识,用于两台计算机之间的链接 b.特殊的IP…...

1. C++入门:命名空间及输入输出

C相比C的变化 兼容C面向对象泛型C的不足的弥补 为什么要有命名空间 在C/C中,变量、函数和后面要学到的类都是大量存在的,这些变量、函数和类的名称将都存在于全局作用域中,可能会导致很多冲突。使用命名空间的目的是对标识符的名称进行本地…...

【Kotlin】Java三目运算转成 kotlin 表达

这行代码会直接计算 array.size 1 的布尔值,并将其赋值给 result。在 Kotlin 中,不需要使用三元操作符,因为条件表达式本身就返回一个布尔值 java 中三木运算: int [] array new int[]{1, 2, 3, 4, 5}; boolean test array &g…...

如何安全可控地进行内外网跨网络传输文件?

跨网络传输文件通常指的是在不同的网络环境之间移动数据,这在现代企业运营中非常常见。随着网络技术的高速发展,为了有效地保护内部的核心数据资产,企业一般会采用内外网隔离的策略。在进行内外网跨网络传输文件时,需要考虑多种因…...

Python Json数据解析

本篇主要介绍Python 中json数据如何解析、转化、保存和加载。 目录 Json数据解析 概念 作用 Json文件组成 Json转化为Python数据类型 Python数据类型转化为json 写入本地json文件 读取本地的json文件 总结 Json数据解析 概念 一种保存数据的格式 作用 可以保存本地…...

pyinstaller打包pytorch和transformers程序

记录使用pyinstaller打包含有pytorch和transformers库的程序时遇到的问题和解决方法。 环境和版本信息 操作系统:Windows 11 Python:3.10.12 pyinstaller:5.13.0 torch:2.2.2 transformers:4.40.1 打包过程和问…...

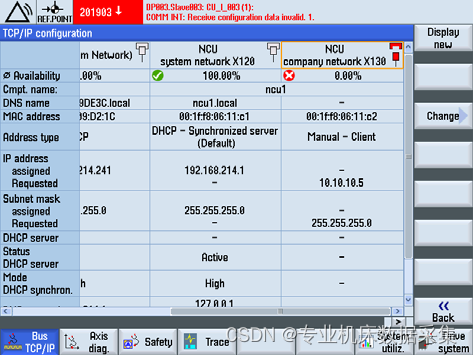

西门子数控网络IP设定配置

总结:menuselect-诊断-屏幕下方右翻页找到tcp/ip,进去选择tcp/ip诊断,进去选择x130网口,点击更改, 如果没有更改,menuselect-调试-口令,输入口令 sunrise 然后重新配置tcp/ip,配置完…...

[Unity]备份许可文件

原因:因Unity需要重新恢复出厂设置,所以需要先将许可文件本分到本地,以便重新初始化后输入许可。 1)登录管理网络web界面,在服务页面打开SSH 2)ssh到管理网络,使用service用户登录 3…...

第十五届蓝桥杯省赛大学B组(c++)

很幸运拿了辽宁赛区的省一,进入6月1号的国赛啦... 这篇文章主要对第十五届省赛大学B组(C)进行一次完整的复盘,这次省赛2道填空题6道编程题: A.握手问题 把握手情景看成矩阵: 粉色部分是7个不能互相捂手的情况 由于每个人只能和其他人捂手, 所以黑色情况是不算的 1和2握手2和…...

应用升级/灾备测试时使用guarantee 闪回点迅速回退

1.场景 应用要升级,当升级失败时,数据库回退到升级前. 要测试系统,测试完成后,数据库要回退到测试前。 相对于RMAN恢复需要很长时间, 数据库闪回只需要几分钟。 2.技术实现 数据库设置 2个db_recovery参数 创建guarantee闪回点,不需要开启数据库闪回。…...

Cesium1.95中高性能加载1500个点

一、基本方式: 图标使用.png比.svg性能要好 <template><div id"cesiumContainer"></div><div class"toolbar"><button id"resetButton">重新生成点</button><span id"countDisplay&qu…...

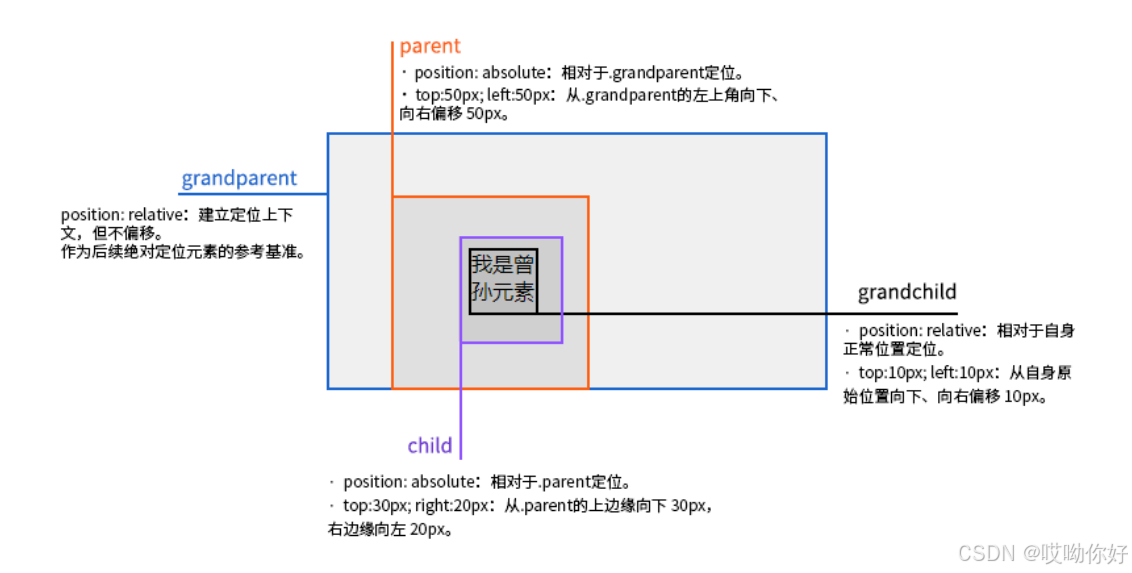

【CSS position 属性】static、relative、fixed、absolute 、sticky详细介绍,多层嵌套定位示例

文章目录 ★ position 的五种类型及基本用法 ★ 一、position 属性概述 二、position 的五种类型详解(初学者版) 1. static(默认值) 2. relative(相对定位) 3. absolute(绝对定位) 4. fixed(固定定位) 5. sticky(粘性定位) 三、定位元素的层级关系(z-i…...

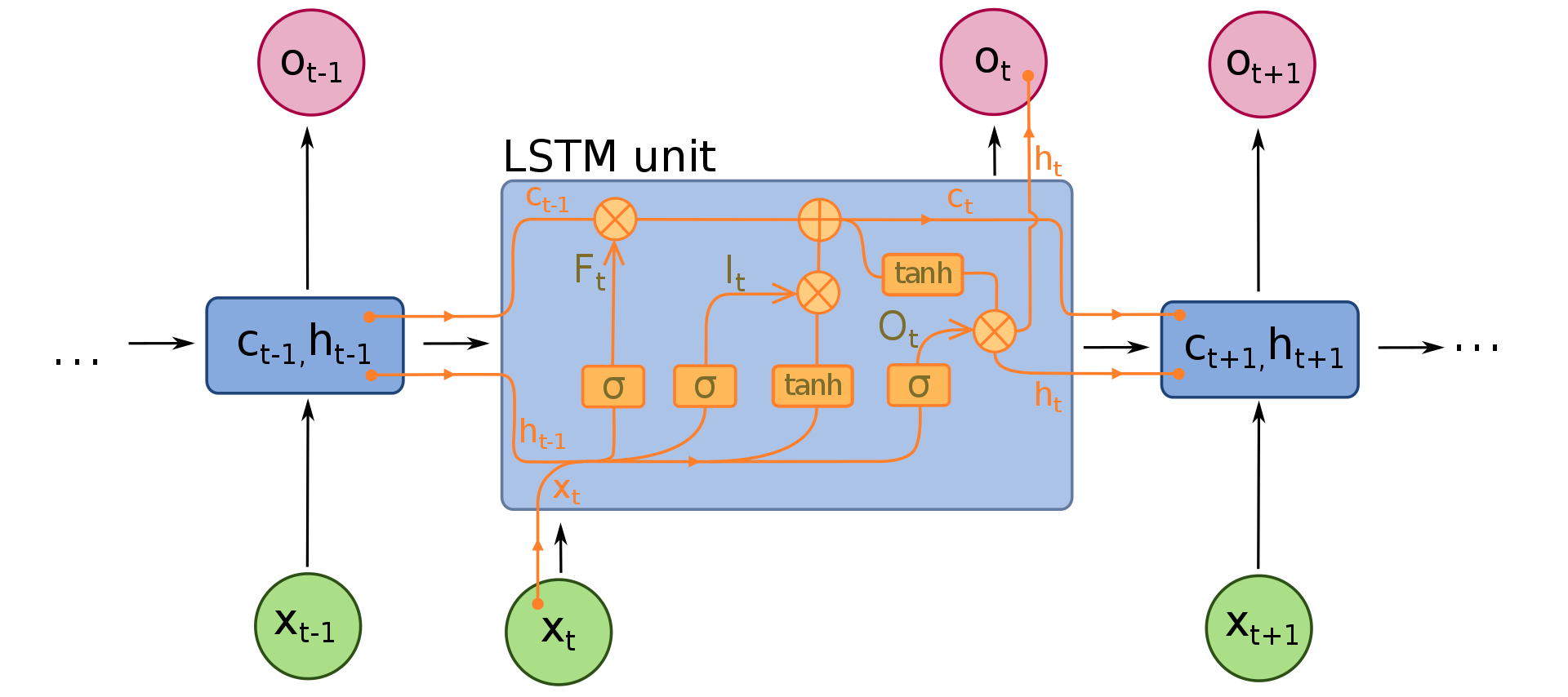

NLP学习路线图(二十三):长短期记忆网络(LSTM)

在自然语言处理(NLP)领域,我们时刻面临着处理序列数据的核心挑战。无论是理解句子的结构、分析文本的情感,还是实现语言的翻译,都需要模型能够捕捉词语之间依时序产生的复杂依赖关系。传统的神经网络结构在处理这种序列依赖时显得力不从心,而循环神经网络(RNN) 曾被视为…...

【碎碎念】宝可梦 Mesh GO : 基于MESH网络的口袋妖怪 宝可梦GO游戏自组网系统

目录 游戏说明《宝可梦 Mesh GO》 —— 局域宝可梦探索Pokmon GO 类游戏核心理念应用场景Mesh 特性 宝可梦玩法融合设计游戏构想要素1. 地图探索(基于物理空间 广播范围)2. 野生宝可梦生成与广播3. 对战系统4. 道具与通信5. 延伸玩法 安全性设计 技术选…...

return this;返回的是谁

一个审批系统的示例来演示责任链模式的实现。假设公司需要处理不同金额的采购申请,不同级别的经理有不同的审批权限: // 抽象处理者:审批者 abstract class Approver {protected Approver successor; // 下一个处理者// 设置下一个处理者pub…...

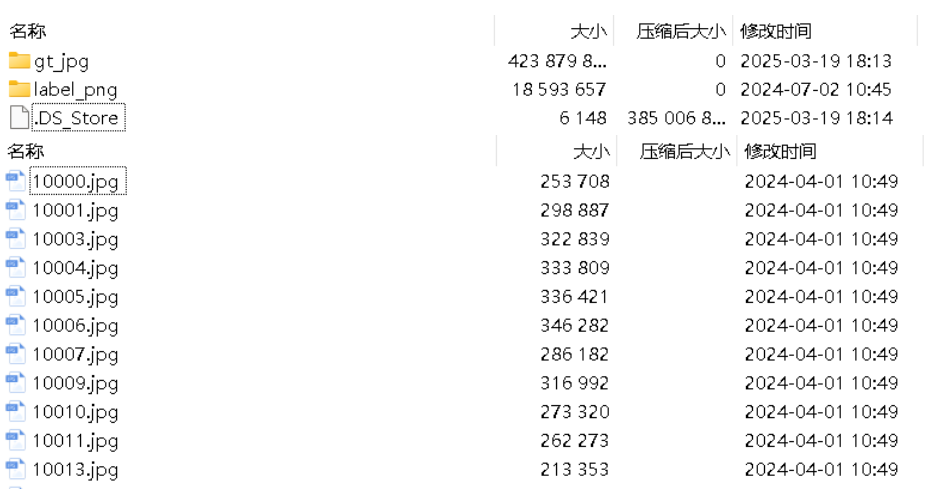

面向无人机海岸带生态系统监测的语义分割基准数据集

描述:海岸带生态系统的监测是维护生态平衡和可持续发展的重要任务。语义分割技术在遥感影像中的应用为海岸带生态系统的精准监测提供了有效手段。然而,目前该领域仍面临一个挑战,即缺乏公开的专门面向海岸带生态系统的语义分割基准数据集。受…...

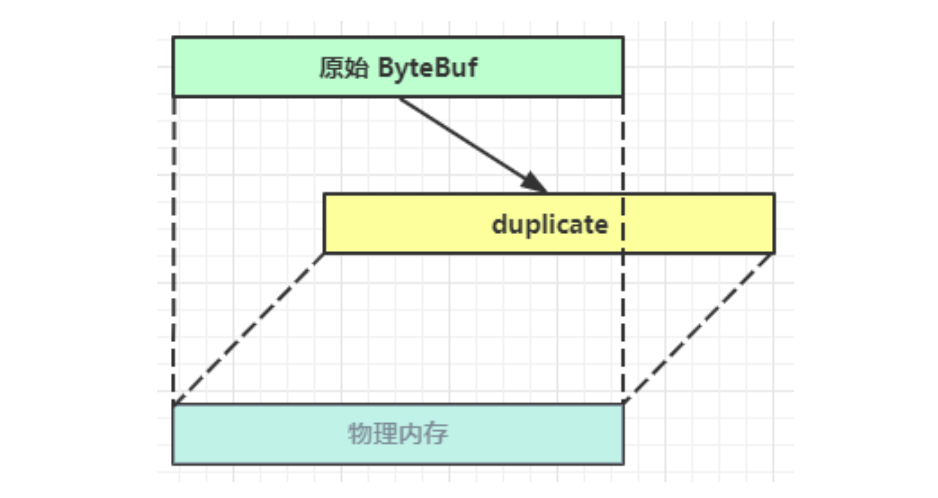

Netty从入门到进阶(二)

二、Netty入门 1. 概述 1.1 Netty是什么 Netty is an asynchronous event-driven network application framework for rapid development of maintainable high performance protocol servers & clients. Netty是一个异步的、基于事件驱动的网络应用框架,用于…...

【从零学习JVM|第三篇】类的生命周期(高频面试题)

前言: 在Java编程中,类的生命周期是指类从被加载到内存中开始,到被卸载出内存为止的整个过程。了解类的生命周期对于理解Java程序的运行机制以及性能优化非常重要。本文会深入探寻类的生命周期,让读者对此有深刻印象。 目录 …...

)

GitHub 趋势日报 (2025年06月06日)

📊 由 TrendForge 系统生成 | 🌐 https://trendforge.devlive.org/ 🌐 本日报中的项目描述已自动翻译为中文 📈 今日获星趋势图 今日获星趋势图 590 cognee 551 onlook 399 project-based-learning 348 build-your-own-x 320 ne…...