基于FPGA的AD5753(DAC数模转换器)的控制 II(SPI驱动)

基于FPGA的AD5753(DAC数模转换器)的控制 II(已上板验证)

语言 :Verilg HDL

EDA工具:Vivado

- 基于FPGA的AD5753(DAC数模转换器)的控制 II(已上板验证)

- 一、引言

- 二、基于FPGA的AD5753控制驱动实现

- 1. 顶层模块

- 2. 数据控制模块(AD5753_DATA_Ctrl模块)

- 3、gen_crc8校验模块

- 三、结尾

- 关键词: AD5753 驱动,Verilog HDL,SPI驱动,DAC数模转换器,上板已验证成功

一、引言

本次分享DAC(AD5753) SPI驱动控制器的FPGA实现,可以借鉴到大部分DAC或者ADC的SPI驱动控制,是上篇基于FPGA的AD5753(DAC数模转换器)的控制 I(SPI驱动)文章的续篇。主要包括DAC(AD5753) FPGA的工程实现,仿真以及上板调试,实现了对DAC芯片的寄存器读写控制。

二、基于FPGA的AD5753控制驱动实现

1. 顶层模块

顶层模块代码如下所示,主要包括

(1)AD5753驱动模块:AD5753_driver模块负责与AD5753 DAC通信,发送数据和触发信号。

(2)数据控制模块:AD5753_DATA_Ctrl模块生成要发送给DAC的数据,并控制数据发送。

(3)逻辑分析仪(ILA):ila实例用于监视和记录信号,以便于调试。

(4)虚拟输入输出(VIO):vio_0实例用于虚拟探针,可以观察或驱动信号。

clk_wiz_0实例用于生成50MHz的时钟信号clk_50m,并且locked信号表示时钟锁定状态。dac_reset_n输出端口被设置为locked,用于DAC的复位。

module test_ADC5753(input sys_clk,input fault_n,output sdi, // to ac5753output sclk,input sdo, // from ad5753output dac_reset_n,output sync_n, output ldac_n,output led);wire [32:0] send_data;wire send_trig;wire [32:0] spi_rx_dat;wire spi_rx_int;wire send_done ;//wire spi_clk_i2;wire spi_clk_i;wire locked;wire clk_50m;wire dat_gen_en;wire [15:0] data;clk_wiz_0 clk_wiz_inst(.clk_out2(clk_50m), .clk_out1( ), .locked (locked ), .clk_in1 (sys_clk ) //50M); assign dac_reset_n = locked;assign led = 1'b0; reg[4:0] cnt; reg clk_1M;always@(posedge clk_50m or negedge locked) beginif(!locked) begincnt = 5'b0;clk_1M = 1'b0;endelse beginif(cnt == 5'd24 ) beginclk_1M = !clk_1M;cnt = 5'd0;endelse begincnt = cnt +5'b1;endendendAD5753_driver AD5753_driver (.clk(clk_50m), .dac_reset_n(locked), .fault_n(fault_n), .send_data(send_data), .send_trig(send_trig), .send_done(send_done), .spi_clk_i(clk_1M),.spi_rx_dat(spi_rx_dat), .spi_rx_int(spi_rx_int), .ldac_n(ldac_n), .spi_clk(sclk), .sync_n(sync_n), .spi_mosi(sdi), .spi_miso(sdo)); AD5753_DATA_Ctrl AD5753_DATA_Ctrl (.clk(clk_50m), .spi_clk_i(clk_1M), .locked(locked), .data(data),.send_done(send_done), .send_trig(send_trig), .send_data(send_data), .dat_gen_en(1'b1), .spi_rx_int(spi_rx_int), .spi_rx_dat(spi_rx_dat));ila ila_inst (.clk(clk_50m), // input wire clk.probe0(send_data), // input wire [23:0] probe0 .probe1(send_trig), // input wire [0:0] probe1 .probe2(spi_rx_dat), // input wire [23:0] probe2 .probe3(spi_rx_int), // input wire [0:0] probe3 .probe4(send_done), // input wire [0:0] probe4 .probe5(locked), // input wire [0:0] probe5 .probe6(dac_reset_n), // input wire [0:0] probe6 .probe7(fault_n), // input wire [0:0] probe7 .probe8(sdi), // input wire [0:0] probe8 .probe9(sclk), // input wire [0:0] probe9 .probe10(sync_n), // input wire [0:0] probe10 .probe11(ldac_n), // input wire [0:0] probe11 .probe12(sdo) // input wire [0:0] probe12

);vio_0 vio_0 (.clk(clk_50m), // input wire clk.probe_in0( ), // input wire [0 : 0] probe_in0.probe_out0(), // output wire [0 : 0] probe_out0.probe_out1(data) // output wire [0 : 0] probe_out0

);endmodule

2. 数据控制模块(AD5753_DATA_Ctrl模块)

AD5753_DATA_Ctrl 模块,设计用于控制与AD5753数字到模拟转换器(DAC)的数据传输。通过定义一系列的输入输出端口、内部状态、计数器和标志位来实现对数据发送过程的精确控制。

模块内部实现了一个状态机,通过不同的状态(如 DATA_IDLE、DATA_FAULT、DATA_Key 等)来管理数据传输流程。状态机根据当前状态和输入信号(例如 dat_gen_en、send_done)来决定下一个状态,并通过 spi_clk_i 来同步数据的发送。

模块还包括了CRC校验逻辑,通过 gen_crc8 子模块生成数据的CRC校验码,确保数据传输的可靠性。在不同的状态下,模块会设置相应的发送触发信号 send_trig 和发送数据 send_data,以及实现特定操作的500us延时,从而完成对AD5753 DAC的命令设置和数据更新。

module AD5753_DATA_Ctrl(input clk, //50Minput spi_clk_i,input locked,input send_done,output reg send_trig,output [31:0] send_data,input dat_gen_en,input spi_rx_int,input [15:0] data,input [31:0] spi_rx_dat);// device adress localparam[2:0] DEVICE_ADRESS=3'b011; // registerlocalparam[4:0] NOP=5'h00;localparam[4:0] Key=5'h00; // STATElocalparam[4:0] DATA_IDLE = 5'd0;localparam[4:0] DATA_FAULT = 5'd1; localparam[4:0] DATA_Key = 5'd2; localparam[4:0] DATA_Key_wait = 5'd3; localparam[4:0] DATA_CLEAR = 5'd4; localparam[4:0] DATA_REQ = 5'd5; localparam[4:0] DATA_DC_SET = 5'd6; localparam[4:0] DATA_DC_SET_WAIT = 5'd7; localparam[4:0] DATA_DC_MOD = 5'd8; localparam[4:0] DATA_DC_MOD_WAIT = 5'd9; localparam[4:0] DATA_DAC_SET = 5'd10; localparam[4:0] DATA_DAC_SET_WAIT = 5'd11; localparam[4:0] DATA_DAC_MOD = 5'd12; localparam[4:0] DATA_DAC_MOD_WAIT = 5'd13; localparam[4:0] DATA_LDAC = 5'd14; localparam[4:0] DATA_OUTPUT = 5'd15;localparam[4:0] DATA_REQ_DAC = 5'd16; localparam[4:0] DATA_REQ_DAC_WAIT = 5'd17; localparam[4:0] DAC_read = 5'd18;localparam[4:0] DAC_nop = 5'd19; reg [13:0] cnt_500us;reg FLAG;reg [4:0] state;reg [4:0] next_state;reg send_trig_tem;reg [23:0] send_data_tem;reg spi_clk_dly;wire spi_clk_pos;wire spi_clk_neg; reg send_done_dly;wire send_done_pos;reg FLAG2;wire[7:0] nextCRC8_D24;wire crc_out_en;reg [15:0] data_reg;reg [15:0] data_reg2; always @ ( posedge spi_clk_i ) beginif( ~locked ) begindata_reg <= 16'b0;data_reg2 <= 16'b0;endelse begindata_reg <= data;data_reg2 <= data_reg; endend always @ ( posedge spi_clk_i ) beginif( ~locked )state <= DATA_IDLE;else state <= next_state; endalways @ (*) beginif( ~locked ) next_state = DATA_IDLE;else case ( state )DATA_IDLE: if( dat_gen_en )next_state = DATA_FAULT;else next_state = DATA_IDLE; DATA_FAULT: if( send_done ) next_state = DATA_Key;else next_state = DATA_FAULT; DATA_Key:if( send_done ) next_state = DATA_Key_wait;else next_state = DATA_Key; DATA_Key_wait:if( FLAG ) next_state = DATA_CLEAR;else next_state = DATA_Key_wait; DATA_CLEAR:if( send_done ) next_state = DATA_REQ;else next_state = DATA_CLEAR; DATA_REQ:if( send_done ) next_state = DATA_DC_SET;else next_state = DATA_REQ; DATA_DC_SET:if( send_done ) next_state = DATA_DC_SET_WAIT;else next_state = DATA_DC_SET; DATA_DC_SET_WAIT:if( FLAG ) next_state = DATA_DC_MOD;else next_state = DATA_DC_SET_WAIT; DATA_DC_MOD:if( send_done ) next_state = DATA_DC_MOD_WAIT;else next_state = DATA_DC_MOD; DATA_DC_MOD_WAIT:if( FLAG ) next_state = DATA_DAC_SET;else next_state = DATA_DC_MOD_WAIT; DATA_DAC_SET:if( send_done ) next_state = DATA_DAC_SET_WAIT;else next_state = DATA_DAC_SET; DATA_DAC_SET_WAIT:if( FLAG ) next_state = DATA_LDAC ;else next_state = DATA_DAC_SET_WAIT;

// DATA_DAC_MOD:

// if( send_done )

// next_state = DATA_DAC_MOD_WAIT ;

// else

// next_state = DATA_DAC_MOD;

// DATA_DAC_MOD_WAIT:

// if( FLAG )

// next_state = DATA_LDAC ;

// else

// next_state = DATA_DAC_MOD_WAIT; DATA_LDAC:if( send_done ) next_state = DATA_OUTPUT ;else next_state = DATA_LDAC; DATA_OUTPUT:if( send_done ) next_state = DATA_REQ_DAC ;else next_state = DATA_OUTPUT; DATA_REQ_DAC:if( send_done) next_state = DATA_REQ_DAC_WAIT ;else next_state = DATA_REQ_DAC; DATA_REQ_DAC_WAIT: if( FLAG ) next_state = DATA_LDAC ;else next_state = DATA_REQ_DAC_WAIT; DAC_read:if( send_done ) next_state = DAC_nop;else next_state = DAC_read; DAC_nop:if( send_done ) next_state = DATA_REQ_DAC;else next_state = DAC_nop; default :next_state = DATA_IDLE; endcaseendalways @ ( posedge clk ) beginif(~locked) beginspi_clk_dly <= 1'b0;send_done_dly <= 1'b0;endelse beginspi_clk_dly <=spi_clk_i;send_done_dly <= send_done; endendassign spi_clk_neg = spi_clk_dly && ~spi_clk_i;

assign spi_clk_pos = (~spi_clk_dly )&& spi_clk_i;

assign send_done_pos =( ~send_done_dly) && send_done;

reg[7:0] nextCRC8_D24_tem;

//assign send_trig =crc_out_en;

assign send_data ={send_data_tem,nextCRC8_D24_tem};always@( posedge clk) beginif( ~locked ) beginsend_trig <= 1'b0;nextCRC8_D24_tem <=8'b0;endif(crc_out_en) beginsend_trig <= 1'b1;nextCRC8_D24_tem <= nextCRC8_D24;endelse if(send_done)send_trig <= 1'b0; elsesend_trig <=send_trig;endalways @ ( posedge clk ) beginif( ~locked ) beginsend_trig_tem <= 1'b0;send_data_tem <= 24'b0;endelse beginif( state == DATA_IDLE && ~send_done ) beginsend_trig_tem <= 1'b0;send_data_tem <= 24'b0; endelse if( state == DATA_FAULT && ~send_done ) beginsend_trig_tem <= 1'b1;send_data_tem <= {DEVICE_ADRESS,5'h10,16'h005c}; // end else if( state == DATA_Key && ~send_done) beginsend_trig_tem <= 1'b1;send_data_tem <= {DEVICE_ADRESS,5'h08,16'hFCBA}; endelse if( state == DATA_CLEAR && ~send_done ) beginsend_trig_tem <= 1'b1;send_data_tem <= {DEVICE_ADRESS,5'h14,16'h2000}; // endelse if( state == DATA_REQ && ~send_done ) beginsend_trig_tem <= 1'b1;send_data_tem <= {DEVICE_ADRESS,5'h09,16'h0644}; endelse if( state == DATA_DC_SET && ~send_done ) beginsend_trig_tem <= 1'b1;send_data_tem <= {DEVICE_ADRESS,5'h0C,16'h010E}; end else if( state == DATA_DC_MOD && ~send_done ) beginsend_trig_tem <= 1'b1;send_data_tem <= {DEVICE_ADRESS,5'h0B,16'h0020}; end else if( state == DATA_DAC_SET && ~send_done ) beginsend_trig_tem <= 1'b1;send_data_tem <= {DEVICE_ADRESS,5'h06,16'h01a8}; end else if( state == DATA_DAC_MOD && ~send_done ) beginsend_trig_tem <= 1'b1;send_data_tem <= {DEVICE_ADRESS,5'h01,16'h0000}; end else if( state == DATA_LDAC && ~send_done ) beginsend_trig_tem <= 1'b1;send_data_tem <= {DEVICE_ADRESS,5'h07,16'h1DAC}; end else if( state == DATA_OUTPUT && ~send_done ) beginsend_trig_tem <= 1'b1;send_data_tem <= {DEVICE_ADRESS,5'h06,16'h01E8}; //D6 = 1end else if( state == DATA_REQ_DAC && ~send_done ) beginsend_trig_tem <= 1'b1;send_data_tem <= {DEVICE_ADRESS,5'h01,data_reg2}; end else if( state == DAC_read && ~send_done ) beginsend_trig_tem <= 1'b1;send_data_tem <= {DEVICE_ADRESS,5'h13,16'h02}; //读output寄存器 endelse if( state == DAC_nop && ~send_done ) beginsend_trig_tem <= 1'b1;send_data_tem <= {DEVICE_ADRESS,NOP,16'h00}; end else beginsend_trig_tem <= 1'b0; endendend// 延时500usalways@( posedge spi_clk_i or negedge locked)beginif( ~locked) begincnt_500us <= 14'b0;FLAG <= 1'b0;endelse beginif(state == DATA_Key_wait ) beginif(cnt_500us == 14'd1010 ) begincnt_500us <= 1'b1;FLAG <= 1'b1;endelse begincnt_500us <= cnt_500us +14'b1;FLAG <= 1'b0;endend else if(state == DATA_DC_SET_WAIT ) beginif(cnt_500us == 14'd1010 ) begincnt_500us <= 1'b0;FLAG <= 1'b1;endelse begincnt_500us <= cnt_500us +14'b1;FLAG <= 1'b0;endend else if(state == DATA_DC_MOD_WAIT ) beginif(cnt_500us == 14'd1010 ) begincnt_500us <= 1'b0;FLAG <= 1'b1;endelse begincnt_500us <= cnt_500us +14'b1;FLAG <= 1'b0;endend else if(state == DATA_REQ_DAC_WAIT ) beginif(cnt_500us == 14'd16 ) begincnt_500us <= 1'b0;FLAG <= 1'b1;endelse begincnt_500us <= cnt_500us +14'b1;FLAG <= 1'b0;endend else if(state == DATA_DAC_SET_WAIT ) beginif(cnt_500us == 14'd1010 ) begincnt_500us <= 1'b0;FLAG <= 1'b1;endelse begincnt_500us <= cnt_500us +14'b1;FLAG <= 1'b0;endend else if(state == DATA_DAC_MOD_WAIT ) beginif(cnt_500us == 14'd16 ) begincnt_500us <= 1'b0;FLAG <= 1'b1;endelse begincnt_500us <= cnt_500us +14'b1;FLAG <= 1'b0;endend else beginFLAG <= 1'b0; endend endgen_crc8 gen_crc8 (.clk(clk), .rst_n(locked), .crc_in_en(send_trig_tem), .Data(send_data_tem), .nextCRC8_D24(nextCRC8_D24), .crc_out_en(crc_out_en));endmodule

3、gen_crc8校验模块

gen_crc8 的模块用于生成8位循环冗余校验(CRC)码,模块包含时钟输入 clk,复位信号 rst_n,CRC输入使能 crc_in_en,待处理数据 Data(24位宽),以及CRC校验码输出 nextCRC8_D24 和输出使能 crc_out_en。

模块使用一个寄存器 crc_in_en_d0 来检测 crc_in_en 的边沿,即从0到1的跳变,这通常表示一个新数据块的到来。

在检测到 crc_in_en 的上升沿后,模块根据输入数据 Data 和当前的CRC寄存器值 nextCRC8_D24 来计算新的CRC校验码。CRC的计算使用了一系列异或(XOR)操作,这些操作定义了CRC的多项式。

`timescale 1ns / 1psmodule gen_crc8(input clk,

input rst_n,input crc_in_en,

input [23:0] Data,

output reg [7:0] nextCRC8_D24,

output reg crc_out_en);reg crc_in_en_d0=0;always @(posedge clk or negedge rst_n)beginif(!rst_n)crc_in_en_d0 <= 1'b0;elsecrc_in_en_d0 <= crc_in_en;

end always @(posedge clk or negedge rst_n)beginif(!rst_n)nextCRC8_D24 <= 'd0;else if(!crc_in_en_d0 && crc_in_en)begin nextCRC8_D24[0] <= Data[23] ^ Data[21] ^ Data[19] ^ Data[18] ^ Data[16] ^ Data[14] ^ Data[12] ^ Data[8] ^ Data[7] ^ Data[6] ^ Data[0] ^ nextCRC8_D24[0] ^ nextCRC8_D24[2] ^ nextCRC8_D24[3] ^ nextCRC8_D24[5] ^ nextCRC8_D24[7];nextCRC8_D24[1] <= Data[23] ^ Data[22] ^ Data[21] ^ Data[20] ^ Data[18] ^ Data[17] ^ Data[16] ^ Data[15] ^ Data[14] ^ Data[13] ^ Data[12] ^ Data[9] ^ Data[6] ^ Data[1] ^ Data[0] ^ nextCRC8_D24[0] ^ nextCRC8_D24[1] ^ nextCRC8_D24[2] ^ nextCRC8_D24[4] ^ nextCRC8_D24[5] ^ nextCRC8_D24[6] ^ nextCRC8_D24[7];nextCRC8_D24[2] <= Data[22] ^ Data[17] ^ Data[15] ^ Data[13] ^ Data[12] ^ Data[10] ^ Data[8] ^ Data[6] ^ Data[2] ^ Data[1] ^ Data[0] ^ nextCRC8_D24[1] ^ nextCRC8_D24[6];nextCRC8_D24[3] <= Data[23] ^ Data[18] ^ Data[16] ^ Data[14] ^ Data[13] ^ Data[11] ^ Data[9] ^ Data[7] ^ Data[3] ^ Data[2] ^ Data[1] ^ nextCRC8_D24[0] ^ nextCRC8_D24[2] ^ nextCRC8_D24[7];nextCRC8_D24[4] <= Data[19] ^ Data[17] ^ Data[15] ^ Data[14] ^ Data[12] ^ Data[10] ^ Data[8] ^ Data[4] ^ Data[3] ^ Data[2] ^ nextCRC8_D24[1] ^ nextCRC8_D24[3];nextCRC8_D24[5] <= Data[20] ^ Data[18] ^ Data[16] ^ Data[15] ^ Data[13] ^ Data[11] ^ Data[9] ^ Data[5] ^ Data[4] ^ Data[3] ^ nextCRC8_D24[0] ^ nextCRC8_D24[2] ^ nextCRC8_D24[4];nextCRC8_D24[6] <= Data[21] ^ Data[19] ^ Data[17] ^ Data[16] ^ Data[14] ^ Data[12] ^ Data[10] ^ Data[6] ^ Data[5] ^ Data[4] ^ nextCRC8_D24[0] ^ nextCRC8_D24[1] ^ nextCRC8_D24[3] ^ nextCRC8_D24[5];nextCRC8_D24[7] <= Data[22] ^ Data[20] ^ Data[18] ^ Data[17] ^ Data[15] ^ Data[13] ^ Data[11] ^ Data[7] ^ Data[6] ^ Data[5] ^ nextCRC8_D24[1] ^ nextCRC8_D24[2] ^ nextCRC8_D24[4] ^ nextCRC8_D24[6];end

endalways @(posedge clk)begincrc_out_en <= !crc_in_en_d0 && crc_in_en;

end endmodule

这个模块是数据传输中确保数据完整性的一个重要组件,通过CRC校验可以检测数据在传输过程中是否出现错误。如果CRC校验失败,系统可以采取相应的措施来纠正或重新发送数据。

三、结尾

本文主要描述如何使用FPGA驱动DAC芯片AD5753,已经在开发板上验证成功。使得配置完成之后,可以正常的控制dac的输出。

相关文章:

的控制 II(SPI驱动))

基于FPGA的AD5753(DAC数模转换器)的控制 II(SPI驱动)

基于FPGA的AD5753(DAC数模转换器)的控制 II(已上板验证) 语言 :Verilg HDL EDA工具:Vivado 基于FPGA的AD5753(DAC数模转换器)的控制 II(已上板验证)一、引言二…...

【全开源】Java同城服务同城信息同城任务发布平台小程序APP公众号源码

📢 连接你我,让任务触手可及 🌟 引言 在快节奏的现代生活中,我们时常需要寻找一些便捷的方式来处理生活中的琐事。同城任务发布平台系统应运而生,它为我们提供了一个高效、便捷的平台,让我们能够轻松发布…...

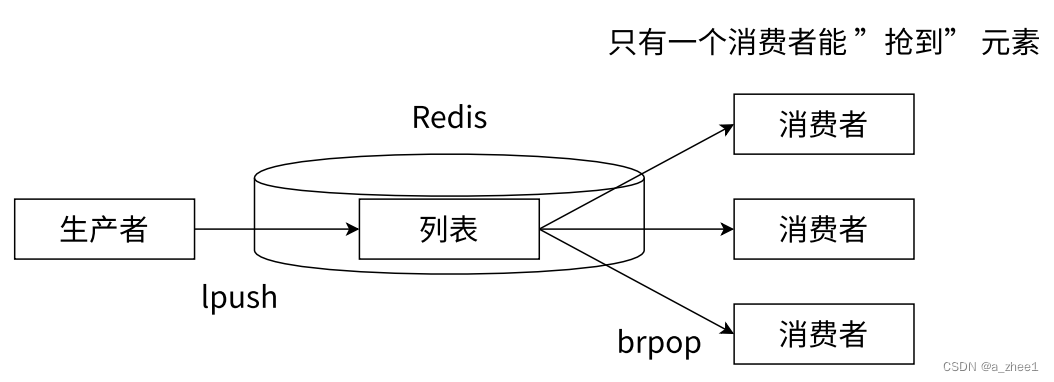

[Redis]List类型

列表类型来存储多个有序的字符串,a、b、c、d、e 五个元素从左到右组成了一个有序的列表,列表中的每个字符串称为元素,一个列表最多可以存储个元素。在 Redis 中,可以对列表两端插入(push)和弹出(…...

export 和 export default 的区别

在 JavaScript 中,export 和 export default 都是用于导出模块中的内容的关键字,但它们有一些区别: export: export 关键字用于导出多个变量、函数或对象。可以一次导出多个内容,并且在导入时需要使用对应的名称。例如:…...

29网课交单平台 epay.php SQL注入漏洞复现

0x01 产品简介 29网课交单平台是一个专注于在线教育和知识付费领域的交单平台。该平台基于PHP开发,通过全开源修复和优化,为用户提供了高效、稳定、安全的在线学习和交易环境。作为知识付费系统的重要组成部分,充分利用了互联网的优势,为用户提供了便捷的支付方式、高效的…...

推荐ChatGPT4.0——Code Copilot辅助编程、Diagrams: Show Me绘制UML图、上传PDF并阅读分析

5月14日凌晨1点、太平洋时间的上午 10 点,OpenAI的GPT-4o的横空出世,再次巩固了其作为行业颠覆者的地位。GPT-4o的发布不仅仅是一个产品的揭晓,它更像是向世界宣告AI技术已迈入了一个全新的纪元,连OpenAI的领航者萨姆奥特曼也不禁…...

rollup.js(入门篇)

前沿 Rollup 是一个用于 JavaScript 的模块打包工具,它将小的代码片段编译成更大、更复杂的代码,例如库或应用程序。它使用 JavaScript 的 ES6 版本中包含的新标准化代码模块格式,而不是以前的 CommonJS 和 AMD 等特殊解决方案。ES 模块允许…...

【Spring Cloud Alibaba】开源组件Sentinel

目录 什么是Sentinel发展历史与Hystrix的异同 Sentinel可以做什么?Sentinel的功能Sentinel的开源生态Sentinel的用户安装Sentinel控制台预备环境准备Sentinel 分为两个部分:下载地址 项目集成Sentinel创建项目修改依赖信息添加启动注解添加配置信息在控制器类中新增…...

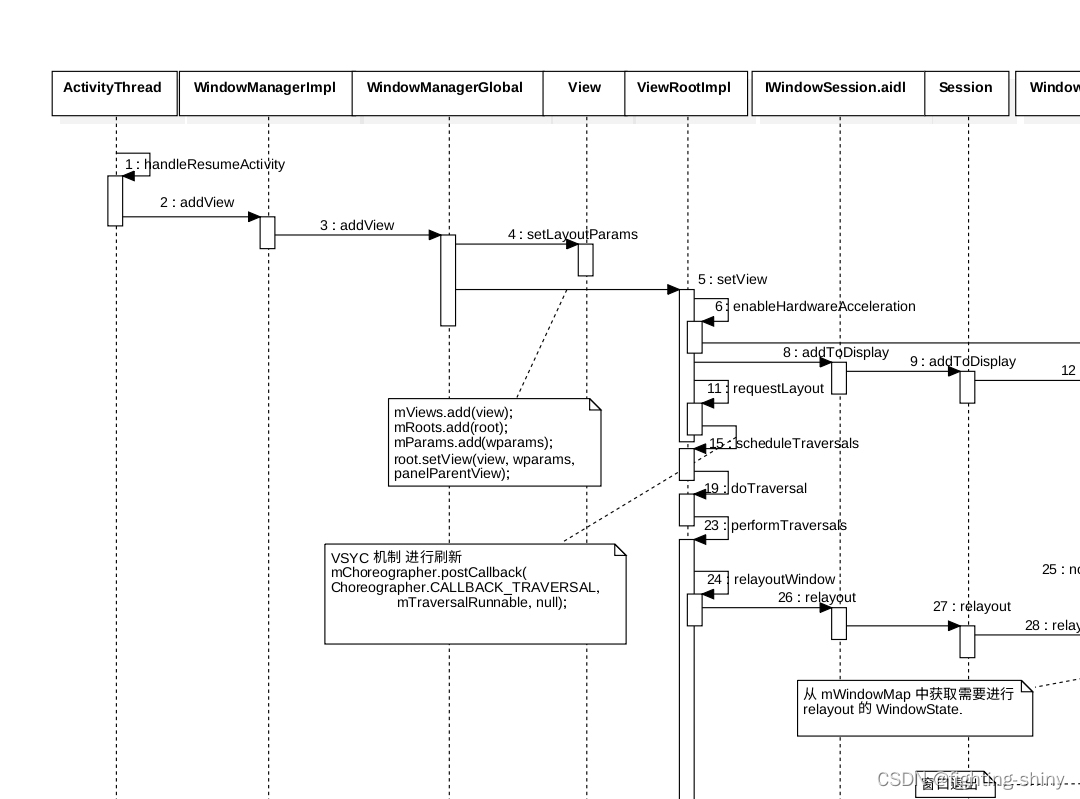

Android14 WMS-窗口绘制之relayoutWindow流程(一)-Client端

Android14 WMS-窗口添加流程(一)-Client端-CSDN博客 Android14 WMS-窗口添加流程(二)-Server端-CSDN博客 经过上述两个流程后,窗口的信息都已经传入了WMS端。 1. ViewRootImpl#setView 在窗口添加流程(一)中,有这个方法: http://aospxref…...

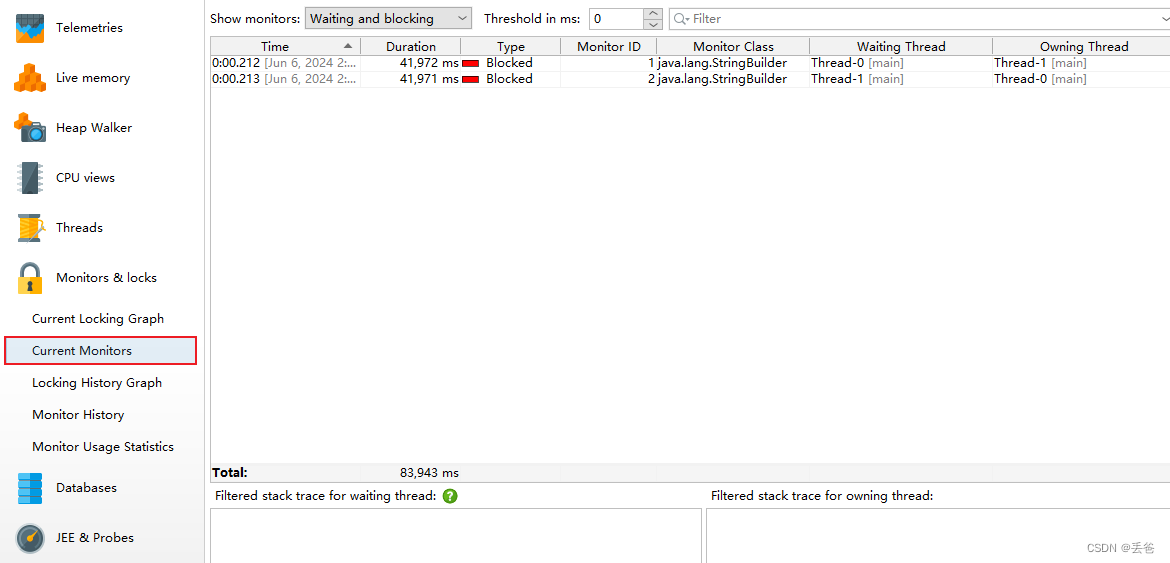

JVM学习-Jprofiler

JProfiler 基本概述 特点 使用方便,界面操作友好对被分析的应用影响小(提供模板)CPU,Tread,Memory分析功能尤其强大支持对jdbc,noSql,jsp,servlet,socket进行分析支持多种模式(离线、在线)的分析支持监控本地、远程JVM跨平台,拥…...

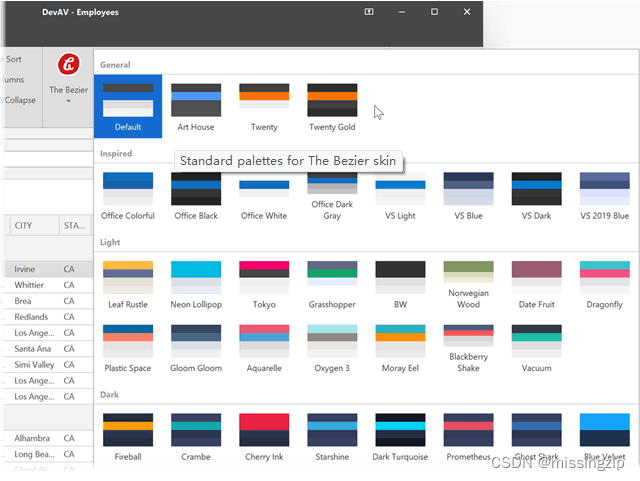

Skins

本主题解释如何将DevExpress主题/皮肤应用到应用程序中,如何允许用户在运行时在主题之间切换,如何自定义现有皮肤或创建自己的皮肤,等等。 WinForms订阅包括许多基本控件:按钮、复选框、表单、消息框、对话框、对话框等。 我们实现…...

【Meetup】探索Apache SeaTunnel的二次开发与实战案例

在数据科技快速演进的今天,业务场景的复杂化和数据量的激增,推动了大数据技术的迅速发展,在众多开源大数据处理工具中,Apache SeaTunnel以其强大的数据集成能力,成为众多企业的首选。 但随着应用深入,企业面…...

嵌入式Linux系统中RTC应用的操作详解

第一:RTC的作用以及时间简介 “RTC”的英文全称是Reul-Time Clock,翻译过来是实时时钟芯片.实时时钟芯片是日常生活中应用最为广泛的电子器件之一,它为人们或者电子系统提供精确的实时时间,实时时钟芯片通过引脚对外提供时间读写接口,通常内部带有电池,保证在外部系统关…...

Edge 工作区是什么?它都有哪些作用?

什么是工作区 Edge 工作区是什么?它是微软 Edge 浏览器中的一个功能,在帮助用户更好地组织和管理他们的浏览会话。通过工作区,用户可以创建多个独立的浏览环境,每个工作区内包含一组相关的标签页和浏览器设置。这使得用户能够根据…...

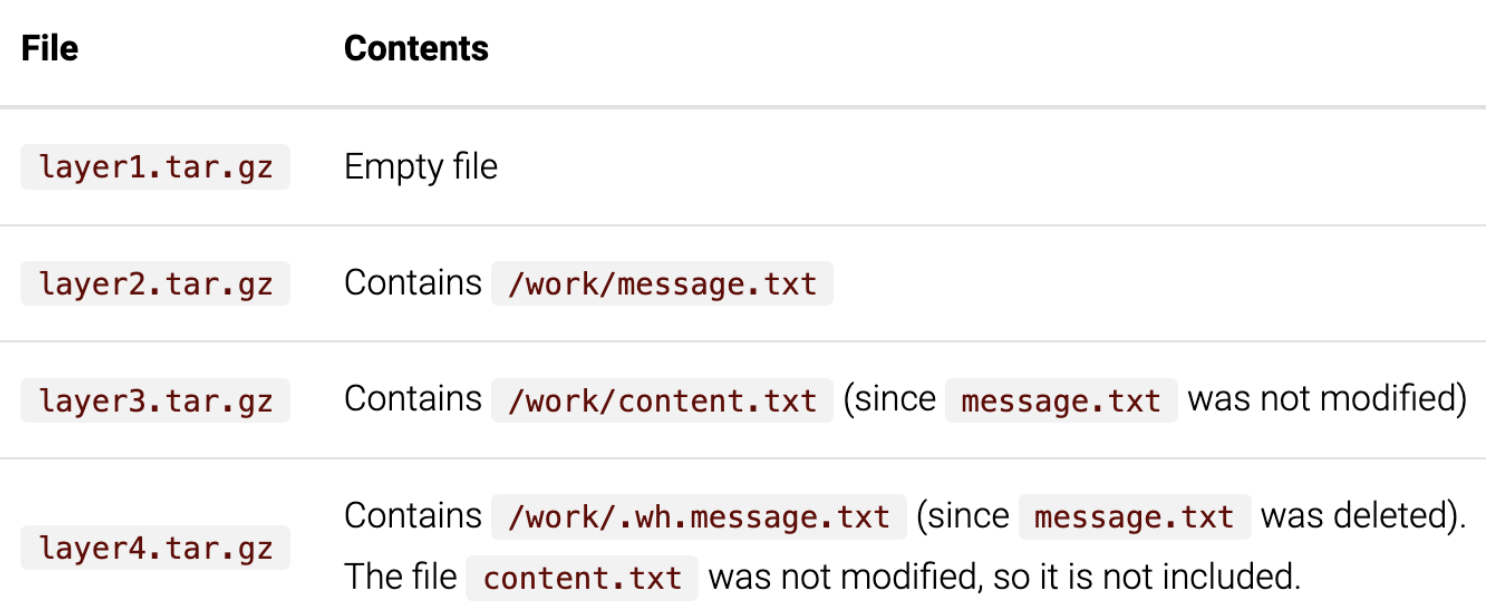

Docker|了解容器镜像层(1)

引言 容器非常神奇。它们允许简单的进程表现得像虚拟机。在这种优雅的底层是一组模式和实践,最终使一切运作起来。在设计的根本是层。层是存储和分发容器化文件系统内容的基本方式。这种设计既出人意料地简单,同时又非常强大。在今天的帖子[1]中…...

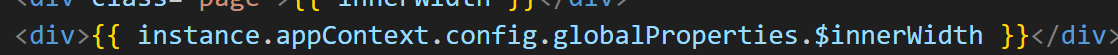

vue3设置全局变量并获取 全局响应式变量 窗口大小

设置 js文件统一管理全局变量 方法1 app provide() 全局提供变量 通过inject()使用 方法2 app实例配置全局变量 获取 通过 getCurrentInstance.appContext.config.globalProperties.$innerWidth访问到 code import { ref } from vue export const useGlobalState () > {c…...

Java——面向对象进阶(一)

前言 面向对象进阶(一):static,继承,this和super关键字 文章目录 一、static1.1 静态变量1.2 静态方法1.3 静态变量和静态方法在内存中 二、继承2.1 概念2.2 继承的特点和能继承什么2.3 继承中的重写2.4 this和super关键字 一、static 在 Jav…...

JDBC是什么?它如何工作?

一、JDBC概述 JDBC(Java Database Connectivity)是Java语言与数据库之间进行交互的API。它允许Java程序通过SQL(结构化查询语言)来执行各种数据库操作,如查询、更新、删除等。JDBC是Java应用程序访问数据库的标准方式…...

Qt:QDialogButtonBox的使用

QDialogButtonBox是Qt自带的按钮箱,通过枚举QDialogButtonBox::ButtonRole可以添加Qt定义按钮,或者通过方法QDialogButtonBox::addButton添加自定义的按钮。 // 自定义按钮。 button_box_ new QDialogButtonBox(QDialogButtonBox::Ok | QDialogButtonB…...

38页 | 工商银行大数据平台助力全行数字化转型之路(免费下载)

【1】关注本公众号,转发当前文章到微信朋友圈 【2】私信发送 工商银行大数据平台 【3】获取本方案PDF下载链接,直接下载即可。 如需下载本方案PPT/WORD原格式,请加入微信扫描以下方案驿站知识星球,获取上万份PPT/WORD解决方案&a…...

云启出海,智联未来|阿里云网络「企业出海」系列客户沙龙上海站圆满落地

借阿里云中企出海大会的东风,以**「云启出海,智联未来|打造安全可靠的出海云网络引擎」为主题的阿里云企业出海客户沙龙云网络&安全专场于5.28日下午在上海顺利举办,现场吸引了来自携程、小红书、米哈游、哔哩哔哩、波克城市、…...

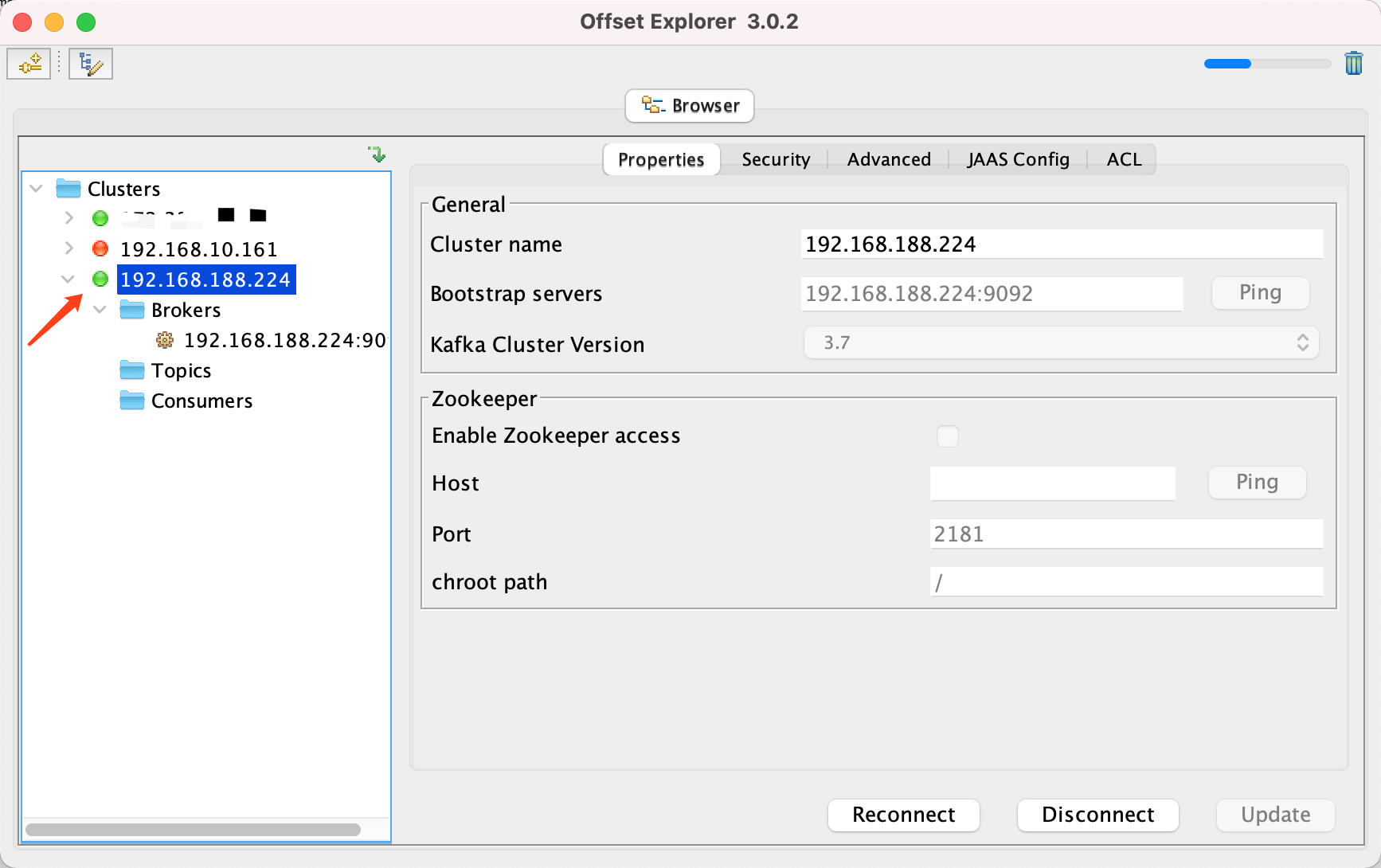

Docker 运行 Kafka 带 SASL 认证教程

Docker 运行 Kafka 带 SASL 认证教程 Docker 运行 Kafka 带 SASL 认证教程一、说明二、环境准备三、编写 Docker Compose 和 jaas文件docker-compose.yml代码说明:server_jaas.conf 四、启动服务五、验证服务六、连接kafka服务七、总结 Docker 运行 Kafka 带 SASL 认…...

测试markdown--肇兴

day1: 1、去程:7:04 --11:32高铁 高铁右转上售票大厅2楼,穿过候车厅下一楼,上大巴车 ¥10/人 **2、到达:**12点多到达寨子,买门票,美团/抖音:¥78人 3、中饭&a…...

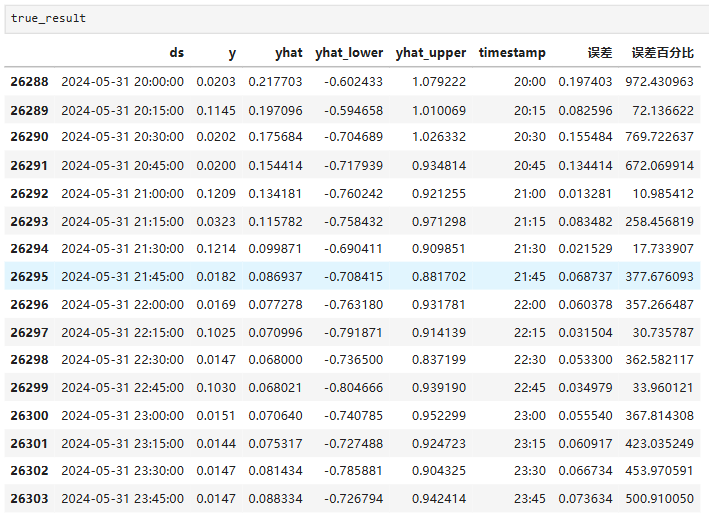

Python实现prophet 理论及参数优化

文章目录 Prophet理论及模型参数介绍Python代码完整实现prophet 添加外部数据进行模型优化 之前初步学习prophet的时候,写过一篇简单实现,后期随着对该模型的深入研究,本次记录涉及到prophet 的公式以及参数调优,从公式可以更直观…...

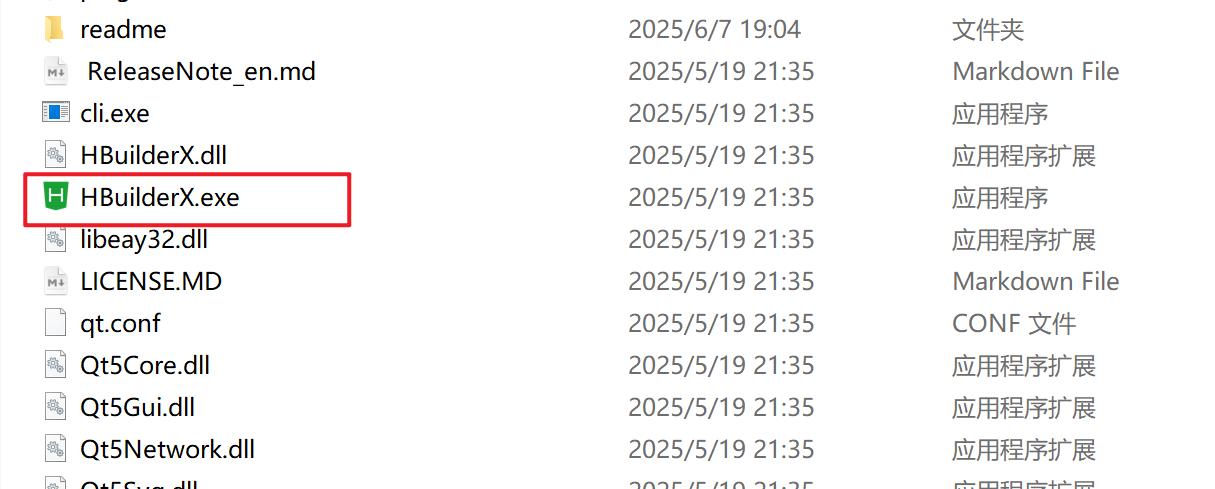

HBuilderX安装(uni-app和小程序开发)

下载HBuilderX 访问官方网站:https://www.dcloud.io/hbuilderx.html 根据您的操作系统选择合适版本: Windows版(推荐下载标准版) Windows系统安装步骤 运行安装程序: 双击下载的.exe安装文件 如果出现安全提示&…...

JDK 17 新特性

#JDK 17 新特性 /**************** 文本块 *****************/ python/scala中早就支持,不稀奇 String json “”" { “name”: “Java”, “version”: 17 } “”"; /**************** Switch 语句 -> 表达式 *****************/ 挺好的ÿ…...

JavaScript基础-API 和 Web API

在学习JavaScript的过程中,理解API(应用程序接口)和Web API的概念及其应用是非常重要的。这些工具极大地扩展了JavaScript的功能,使得开发者能够创建出功能丰富、交互性强的Web应用程序。本文将深入探讨JavaScript中的API与Web AP…...

MySQL 索引底层结构揭秘:B-Tree 与 B+Tree 的区别与应用

文章目录 一、背景知识:什么是 B-Tree 和 BTree? B-Tree(平衡多路查找树) BTree(B-Tree 的变种) 二、结构对比:一张图看懂 三、为什么 MySQL InnoDB 选择 BTree? 1. 范围查询更快 2…...

【WebSocket】SpringBoot项目中使用WebSocket

1. 导入坐标 如果springboot父工程没有加入websocket的起步依赖,添加它的坐标的时候需要带上版本号。 <dependency><groupId>org.springframework.boot</groupId><artifactId>spring-boot-starter-websocket</artifactId> </dep…...

CppCon 2015 学习:Time Programming Fundamentals

Civil Time 公历时间 特点: 共 6 个字段: Year(年)Month(月)Day(日)Hour(小时)Minute(分钟)Second(秒) 表示…...