【学习笔记】4、组合逻辑电路(下)

接前文《【学习笔记】4、组合逻辑电路(上)》

4.4.5 算术运算电路

1. 半加器和全加器

- 半加器和全加器是算术运算电路中的基本单元。

- 半加器和全加器是1位相加的组合逻辑电路。

(1)半加器

-

半加器:只考虑两个加数本身,不考虑低位进位。

-

A、B是两个加数

-

S表示和数

-

C表示进位

-

列出真值表:

| A | B | C | S |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | 1 | 0 |

- 逻辑表达式

- S = A ‾ B + A B ‾ = A ⊕ B S=\overline{A}B+A\overline{B}=A⊕B S=AB+AB=A⊕B//异或

- C = A B C=AB C=AB

- 逻辑图

(2)全加器

- 全加器:加数A,加数B,以及低位进位 C i C_i Ci。

- S表示和数

- C o C_o Co表示进位

- 列出真值表

| A加数1 | B加数2 | C i 低位进位 C_i低位进位 Ci低位进位 | C o 进位 C_o进位 Co进位 | S和 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 1 | 0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

- 列出逻辑表达式

- 不能直接给出最简形式,借助卡诺图。(先出现低位C,后出现高位A)

S = A ‾ ⋅ B ‾ ⋅ C i + A ‾ ⋅ B ⋅ C i ‾ + A ⋅ B ‾ ⋅ C i ‾ + A B C i = A ⊕ B ⊕ C i S=\overline{A}·\overline{B}·C_i+\overline{A}·B·\overline{C_i}+A·\overline{B}·\overline{C_i}+ABC_i=A⊕B⊕C_i S=A⋅B⋅Ci+A⋅B⋅Ci+A⋅B⋅Ci+ABCi=A⊕B⊕Ci//异或

C o = A ‾ ⋅ B ⋅ C i + A ⋅ B ‾ ⋅ C i + A ⋅ B = ( A ⊕ B ) ⋅ C i + A ⋅ B C_o = \overline{A}·B·C_i+A·\overline{B}·C_i+A·B=(A⊕B)·C_i+A·B Co=A⋅B⋅Ci+A⋅B⋅Ci+A⋅B=(A⊕B)⋅Ci+A⋅B

2. 多位数加法器

(1)并行相加,串行进位,加法

- 必须在低1位进行完成后,才可以进行高1位的加法。

- 先低位相加,进位,再高位相加。

- 受到进位信号的限制。

(2)集成4位超前进位加法器

-

74HC283

-

考虑到全加器组成的“并行相加,串行进位”的缺点,设计了新的多位加法逻辑电路。

-

这里的超前,指的是 各个位加法不用等低1位的进位信号,提前进行加法。

-

每位的进位,只由加数和被加数决定,与低位的进位无关。

-

前文的全加器逻辑表达式:

- S = A ⊕ B ⊕ C i S = A⊕B⊕C_i S=A⊕B⊕Ci //这里的i表示输入input

- C o = ( A ⊕ B ) ⋅ C i + A ⋅ B C_o =(A⊕B)·C_i+A·B Co=(A⊕B)⋅Ci+A⋅B//这里的i表示输入input

- S i = A i ⊕ B i ⊕ C i − 1 S_i = A_i⊕B_i⊕C_{i-1} Si=Ai⊕Bi⊕Ci−1//i表示当前全加器,i-1表示前一个全加器

- C i = ( A i ⊕ B i ) ⋅ C i − 1 + A i ⋅ B i C_{i} =(A_i⊕B_i)·C_{i-1}+A_i·B_i Ci=(Ai⊕Bi)⋅Ci−1+Ai⋅Bi//i表示当前全加器,i-1表示前一个全加器

-

为了只观察进位 C i C_i Ci,定义中间变量 G i = A i B i , P i = A i ⊕ B i G_i=A_iB_i,P_i=A_i⊕B_i Gi=AiBi,Pi=Ai⊕Bi,这两个中间变量,在计算一开始,就已经固定了。

- S i = P i ⊕ C i − 1 S_i = P_i⊕C_{i-1} Si=Pi⊕Ci−1

- C i = P i ⋅ C i − 1 + G i C_{i} =P_i·C_{i-1}+G_i Ci=Pi⋅Ci−1+Gi

-

这里重点关注 C i = P i ⋅ C i − 1 + G i C_{i} =P_i·C_{i-1}+G_i Ci=Pi⋅Ci−1+Gi,一个迭代函数。

- C 0 = G 0 + P 0 C − 1 C_0 = G_0+P_0C_{-1} C0=G0+P0C−1

- C 1 = G 1 + P 1 C 0 = G 1 + P 1 ( G 0 + P 0 C − 1 ) = G 1 + P 1 G 0 + P 1 P 0 C − 1 C_1 = G_1+P_1C_{0}=G_1+P_1(G_0+P_0C_{-1})=G_1+P_1G_0+P_1P_0C_{-1} C1=G1+P1C0=G1+P1(G0+P0C−1)=G1+P1G0+P1P0C−1

- C 2 = G 2 + P 2 C 1 = G 2 + P 2 ( G 1 + P 1 G 0 + P 1 P 0 C − 1 ) = G 2 + P 2 G 1 + P 2 P 1 G 0 + P 2 P 1 P 0 C − 1 C_2 = G_2+P_2C_{1}=G_2+P_2(G_1+P_1G_0+P_1P_0C_{-1})=G_2+P_2G_1+P_2P_1G_0+P_2P_1P_0C_{-1} C2=G2+P2C1=G2+P2(G1+P1G0+P1P0C−1)=G2+P2G1+P2P1G0+P2P1P0C−1

- C 3 = G 3 + P 3 C 2 = G 3 + P 3 ( G 2 + P 2 G 1 + P 2 P 1 G 0 + P 2 P 1 P 0 C − 1 ) = G 3 + P 3 G 2 + P 3 P 2 G 1 + P 3 P 2 P 1 G 0 + P 3 P 2 P 1 P 0 C − 1 C_3 = G_3+P_3C_2=G_3+P_3(G_2+P_2G_1+P_2P_1G_0+P_2P_1P_0C_{-1})=G_3+P_3G_2+P_3P_2G_1+P_3P_2P_1G_0+P_3P_2P_1P_0C_{-1} C3=G3+P3C2=G3+P3(G2+P2G1+P2P1G0+P2P1P0C−1)=G3+P3G2+P3P2G1+P3P2P1G0+P3P2P1P0C−1

- 根据推导,我们可以知道,当前加法器的进位信号 C i C_i Ci,只和 P i P_i Pi、 G i G_i Gi、初始进位信号 C − 1 C_{-1} C−1有关。

-

逻辑图。

-

下图是猜测的74HC283逻辑图。

-

串联进位,级联。

-

超前进位产生器(并不是一个完整的加法器)

- 74LS182

3. 减法运算

- 补码: N 补码 = 2 n − N 原码 N_{补码}=2^n-N_{原码} N补码=2n−N原码

- 补码: N 补码 = N 反码 + 1 N_{补码}=N_{反码}+1 N补码=N反码+1

- 将减法变成加法。

- A − B = A − ( 2 n − B 补 ) = A + B 补 − 2 n = A + B 反 + 1 − 2 n A-B=A-(2^n-B_补)=A+B_补-2^n=A+B_反+1-2^n A−B=A−(2n−B补)=A+B补−2n=A+B反+1−2n

- 求4位减法的结果补码: A − B = A + B 反 + 1 A-B=A+B_反+1 A−B=A+B反+1

- 结果补码 D 3 : 0 ’ = A 3 : 0 + ( B 3 : 0 ) 反码 + 1 , C o 为进位信号 结果补码D_{3:0}^’ = A_{3:0}+(B_{3:0})_{反码}+1,C_o为进位信号 结果补码D3:0’=A3:0+(B3:0)反码+1,Co为进位信号

- 求结果的原码

- 结果原码 D 3 : 0 = [ 结果补码 D 3 : 0 ’ , C o ] − 2 n = [ 结果补码 D 3 : 0 ’ , C o ] − 2 4 = [ 结果补码 D 3 : 0 ’ , C o ] − ( 10000 ) b 结果原码D_{3:0}=[结果补码D_{3:0}^’,C_o] -2^n=[结果补码D_{3:0}^’,C_o] -2^4=[结果补码D_{3:0}^’,C_o] -(10000)_b 结果原码D3:0=[结果补码D3:0’,Co]−2n=[结果补码D3:0’,Co]−24=[结果补码D3:0’,Co]−(10000)b

- 已知 结果补码 D 3 : 0 ’ 数值范围是 ( 0000 ) b 到 ( 1111 ) b 结果补码D_{3:0}^’数值范围是(0000)_b到(1111)_b 结果补码D3:0’数值范围是(0000)b到(1111)b。

- 当 C o = 1 C_o=1 Co=1时,bit4=1, 减去 2 n = ( 10000 ) b 2^n=(10000)_b 2n=(10000)b,不需要借位,异或0。

- 中间 D 0 ′ ′ = D 0 ′ ⊕ 0 = D 0 ′ 中间D_0^{''}=D_0^{'}⊕0=D_0^{'} 中间D0′′=D0′⊕0=D0′;

- 中间 D 1 ′ ′ = D 1 ′ ⊕ 0 = D 1 ′ 中间D_1^{''}=D_1^{'}⊕0=D_1^{'} 中间D1′′=D1′⊕0=D1′;

- 中间 D 2 ′ ′ = D 2 ′ ⊕ 0 = D 2 ′ 中间D_2^{''}=D_2^{'}⊕0=D_2^{'} 中间D2′′=D2′⊕0=D2′;

- 中间 D 3 ′ ′ = D 3 ′ ⊕ 0 = D 3 ′ 中间D_3^{''}=D_3^{'}⊕0=D_3^{'} 中间D3′′=D3′⊕0=D3′;

- 结果原码 D 3 : 0 = D 3 : 0 ′ ′ + A 3 : 0 ′ ′ = 结果补码 D 3 : 0 ′ = A 3 : 0 + B 3 : 0 反码 + 1 结果原码D_{3:0}=D_{3:0}^{''}+A_{3:0}^{''}=结果补码D_{3:0}^{'}=A_{3:0}+B_{3:0}{反码}+1 结果原码D3:0=D3:0′′+A3:0′′=结果补码D3:0′=A3:0+B3:0反码+1

- 举例:$A≥B,A=0101,B=0001

- 公式计算:A-B=A+B_{反码}+1-2^4=(0101)_b+(1110)_b+1-(10000)_b=(10100)_b-(10000)_b=(00100)_b$ //不需要借位,

- 电路逻辑: A − B = A 3 : 0 + B 3 : 0 反码 + 1 A-B=A_{3:0}+B_{3:0}{反码}+1 A−B=A3:0+B3:0反码+1

- 当 C o = 0 C_o=0 Co=0时,bit4=0, 减去 2 n = ( 10000 ) b 2^n=(10000)_b 2n=(10000)b,需要借位,异或1。

- 中间 D 0 ′ ′ = D 0 ′ ⊕ 1 = ( D 0 ′ ) 反 中间D_0^{''}=D_0^{'}⊕1=(D_0^{'})_{反} 中间D0′′=D0′⊕1=(D0′)反;

- 中间 D 1 ′ ′ = D 1 ′ ⊕ 1 = ( D 1 ′ ) 反 中间D_1^{''}=D_1^{'}⊕1=(D_1^{'})_{反} 中间D1′′=D1′⊕1=(D1′)反;

- 中间 D 2 ′ ′ = D 2 ′ ⊕ 1 = ( D 2 ′ ) 反 中间D_2^{''}=D_2^{'}⊕1=(D_2^{'})_{反} 中间D2′′=D2′⊕1=(D2′)反;

- 中间 D 3 ′ ′ = D 3 ′ ⊕ 1 = ( D 3 ′ ) 反 中间D_3^{''}=D_3^{'}⊕1=(D_3^{'})_{反} 中间D3′′=D3′⊕1=(D3′)反;

- 结果原码 D 3 : 0 = D 3 : 0 ′ ′ + A 3 : 0 ′ ′ + C − 1 = D 3 : 0 ′ 反码 + 1 = ( A 3 : 0 + B 3 : 0 反码 + 1 ) 反码 + 1 结果原码D_{3:0}=D_{3:0}^{''}+A_{3:0}^{''}+C_{-1}=D_{3:0}^{'}反码+1=(A_{3:0}+B_{3:0}{反码}+1)_{反码}+1 结果原码D3:0=D3:0′′+A3:0′′+C−1=D3:0′反码+1=(A3:0+B3:0反码+1)反码+1

- 举例: A < B , A = 0001 , B = 0101 A<B,A=0001,B=0101 A<B,A=0001,B=0101

- 公式计算: A − B = A + B 反码 + 1 − 2 4 = ( 0001 ) b + ( 1010 ) b + 1 − ( 10000 ) b = ( 01100 ) b − ( 10000 ) b = ( 借位 1 ⋅ 01100 ) b − ( 10000 ) b = ( 11100 ) b (直接计算得到的就是 − 4 的补码) A-B=A+B_{反码}+1-2^4=(0001)_b+(1010)_b+1-(10000)_b=(01100)_b-(10000)_b=(借位1·01100)_b-(10000)_b=(11100)_b(直接计算得到的就是-4的补码) A−B=A+B反码+1−24=(0001)b+(1010)b+1−(10000)b=(01100)b−(10000)b=(借位1⋅01100)b−(10000)b=(11100)b(直接计算得到的就是−4的补码)

- 电路逻辑: A − B = ( A 3 : 0 + B 3 : 0 反码 + 1 ) 反码 + 1 = ( ( 01100 ) b ) 反码 + 1 = ( 10011 ) b + 1 = ( 1 ⋅ 0100 ) ,也就是绝对值 = 4 ,符号 = V 借位信号 = 1 ,为负, − 4 A-B=(A_{3:0}+B_{3:0}{反码}+1)_{反码}+1=((01100)_b)_{反码}+1=(10011)_b+1=(1·0100),也就是绝对值=4,符号=V借位信号=1,为负,-4 A−B=(A3:0+B3:0反码+1)反码+1=((01100)b)反码+1=(10011)b+1=(1⋅0100),也就是绝对值=4,符号=V借位信号=1,为负,−4

4. 集成算术/逻辑单元

- 算术逻辑单元ALU(Arithmetic Logic Unit)。既支持算术运算,又支持逻辑运算。

- 74LS181是双极型ALU。

- 功能引脚M=H时,执行逻辑运算

- 功能引脚M=L时,执行算术运算

4.5 组合可编程逻辑器件

4.5.1 PLD的结构、表示方法及分类

1. PLD的结构

- PLD:可编程逻辑器件

- 基本组成:与阵列、或阵列。

2. PLD的表示方法

- 早期使用熔丝和二极管,一次性编程。

- 可擦除CMOS技术,使用浮栅技术。

3. PLD的分类

- 按照集成度划分:

- 低密度(1000以下):PROM可编程只读存储器、PLA可编程逻辑阵列、PAL可编程阵列逻辑、GAL通用阵列逻辑

- 高密度(1000以上):CPLD复杂可编程逻辑器件、FPGA现场可编程门阵列

- 按照结构体系划分:

- 简单PLD

- 复杂可编程逻辑器件CPLD

- 现场可编程逻辑器件FPGA

- 按照与或阵列是否可编程划分:

- PROM:与阵列固定,或阵列可编程

- PAL和GAL:与阵列可编程、或阵列固定。

- PLA:与阵列、或阵列都可以编程。

4.5.2 组合逻辑电路的PLD实现

- 任何组合逻辑关系都可以变换成 与或 表达式

- 通过PLD的与、或阵列,可以实现任何一个逻辑函数。

1. 可编程逻辑阵列PLA

- 缺少开发环境支持,价格贵。

- L 0 = A ‾ ⋅ B ‾ ⋅ C + A ‾ ⋅ B ⋅ C ‾ + A ⋅ B ‾ ⋅ C ‾ + A B C L_0 = \overline{A}·\overline{B}·C+\overline{A}·B·\overline{C}+A·\overline{B}·\overline{C}+ABC L0=A⋅B⋅C+A⋅B⋅C+A⋅B⋅C+ABC

- L 1 = A B + A C + B C L_1=AB+AC+BC L1=AB+AC+BC

- 列出真值表之后,可以发现该电路是“全加器”的功能。

- 全加器的逻辑表达式:

S = A ‾ ⋅ B ‾ ⋅ C i + A ‾ ⋅ B ⋅ C i ‾ + A ⋅ B ‾ ⋅ C i ‾ + A B C i = A ⊕ B ⊕ C i S=\overline{A}·\overline{B}·C_i+\overline{A}·B·\overline{C_i}+A·\overline{B}·\overline{C_i}+ABC_i=A⊕B⊕C_i S=A⋅B⋅Ci+A⋅B⋅Ci+A⋅B⋅Ci+ABCi=A⊕B⊕Ci//异或

C o = A ‾ ⋅ B ⋅ C i + A ⋅ B ‾ ⋅ C i + A ⋅ B = ( A ⊕ B ) ⋅ C i + A ⋅ B C_o = \overline{A}·B·C_i+A·\overline{B}·C_i+A·B=(A⊕B)·C_i+A·B Co=A⋅B⋅Ci+A⋅B⋅Ci+A⋅B=(A⊕B)⋅Ci+A⋅B

变形: C o = A ‾ ⋅ B ⋅ C i + A ⋅ B ‾ ⋅ C i + A ⋅ B = A ‾ ⋅ B ⋅ C i + A ⋅ B ‾ ⋅ C i + ( A ⋅ B + A B C + A B C ) 变形:C_o = \overline{A}·B·C_i+A·\overline{B}·C_i+A·B=\overline{A}·B·C_i+A·\overline{B}·C_i+(A·B+ABC+ABC) 变形:Co=A⋅B⋅Ci+A⋅B⋅Ci+A⋅B=A⋅B⋅Ci+A⋅B⋅Ci+(A⋅B+ABC+ABC)//吸收律

变形: C o = A ‾ ⋅ B ⋅ C i + A ⋅ B ‾ ⋅ C i + ( A ⋅ B + A B C + A B C ) = ( A ‾ ⋅ B ⋅ C i + A B C ) + ( A ⋅ B ‾ ⋅ C i + A B C ) + A B = B C i + A C i + A B 变形:C_o =\overline{A}·B·C_i+A·\overline{B}·C_i+(A·B+ABC+ABC)=(\overline{A}·B·C_i+ABC)+(A·\overline{B}·C_i+ABC)+AB=BC_i+AC_i+AB 变形:Co=A⋅B⋅Ci+A⋅B⋅Ci+(A⋅B+ABC+ABC)=(A⋅B⋅Ci+ABC)+(A⋅B⋅Ci+ABC)+AB=BCi+ACi+AB

变形: C o = B C i + A C i + A B 变形:C_o =BC_i+AC_i+AB 变形:Co=BCi+ACi+AB

2.可编程阵列逻辑PAL

- 与阵列可编程,或阵列固定。

- 已知 逻辑表达式,使用PAL与阵列实现该功能。

- 一个 或单元 接三个可编程 与单元。

- 没有使用到的与单元,需要全接通,简化图是“与单元中画一个大的X”,因为正反 与 在了一起,该支路逻辑值为0。

- L3有需要4个或输入,硬件受限,可以使用L0的输出作为两个输入。

4.6 用Verilog HDL描述组合逻辑电路

- HDL硬件描述语言

4.6.1 组合逻辑电路的门级建模

- verilog语言内置的12个基本门级元件。

| 分类 | 元件符号 | 功能说明 |

|---|---|---|

| 多输入门 | and | 与门 |

| 多输入门 | nand | 与非门 |

| 多输入门 | or | 或门 |

| 多输入门 | nor | 或非门 |

| 多输入门 | xor | 异或门 |

| 多输入门 | xnor | 异或非门 |

| ------------ | ---------- | ------------------------------------------ |

| 多输出门 | buf | 缓冲器 |

| 多输出门 | not | 反相器 |

| ------------ | ---------- | ------------------------------------------ |

| 三态门 | bufif1 | 三态缓冲器,if-如果,控制信号为1-高电平,输出有效 (in->out) |

| 三态门 | bufif0 | 三态缓冲器 ,if-如果,控制信号为0-低电平,输出有效(in->out) |

| 三态门 | notif1 | 三态反相器,if-如果,控制信号为1-高电平,输出有效(in->out) |

| 三态门 | notif0 | 三态反相器,if-如果,控制信号为0-低电平,输出有效 (in->out) |

1. 多输入门

-

and、nand、or、nor、xor、xnor

-

只允许一个输出,但允许有多个输入。

-

多输入门的输出端out,不可能为高阻状态z。

-

列出真值表,以2输入为例。

| and 与门 | i n 1 = 0 in_1=0 in1=0 | i n 1 = 1 in_1=1 in1=1 | i n 1 = x in_1=x in1=x | i n 1 = z ( 高阻 ) in_1=z(高阻) in1=z(高阻) |

|---|---|---|---|---|

| i n 2 = 0 in_2=0 in2=0 | 0 | 0 | 0 | 0 |

| i n 2 = 1 in_2=1 in2=1 | 0 | out=1 | x | x |

| i n 2 = x in_2=x in2=x | 0 | x | x | x |

| i n 2 = z ( 高阻 ) in_2=z(高阻) in2=z(高阻) | 0 | x | x | x |

| nand 与非门 | i n 1 = 0 in_1=0 in1=0 | i n 1 = 1 in_1=1 in1=1 | i n 1 = x in_1=x in1=x | i n 1 = z ( 高阻 ) in_1=z(高阻) in1=z(高阻) |

|---|---|---|---|---|

| i n 2 = 0 in_2=0 in2=0 | out=1 | out=1 | out=1 | out=1 |

| i n 2 = 1 in_2=1 in2=1 | out=1 | 0 | x | x |

| i n 2 = x in_2=x in2=x | out=1 | x | x | x |

| i n 2 = z ( 高阻 ) in_2=z(高阻) in2=z(高阻) | out=1 | x | x | x |

| or 或门 | i n 1 = 0 in_1=0 in1=0 | i n 1 = 1 in_1=1 in1=1 | i n 1 = x in_1=x in1=x | i n 1 = z ( 高阻 ) in_1=z(高阻) in1=z(高阻) |

|---|---|---|---|---|

| i n 2 = 0 in_2=0 in2=0 | 0 | out=1 | x | x |

| i n 2 = 1 in_2=1 in2=1 | out=1 | out=1 | out=1 | out=1 |

| i n 2 = x in_2=x in2=x | x | out=1 | x | x |

| i n 2 = z ( 高阻 ) in_2=z(高阻) in2=z(高阻) | x | out=1 | x | x |

| xor 异或门 | i n 1 = 0 in_1=0 in1=0 | i n 1 = 1 in_1=1 in1=1 | i n 1 = x in_1=x in1=x | i n 1 = z ( 高阻 ) in_1=z(高阻) in1=z(高阻) |

|---|---|---|---|---|

| i n 2 = 0 in_2=0 in2=0 | 0 | out=1 | x | x |

| i n 2 = 1 in_2=1 in2=1 | out=1 | 0 | x | x |

| i n 2 = x in_2=x in2=x | x | x | x | x |

| i n 2 = z ( 高阻 ) in_2=z(高阻) in2=z(高阻) | x | x | x | x |

2. 多输出门

-

buf缓冲器、not反相器

-

只能有一个输入,但允许多个输出。

-

列出1个输出的真值表

| buf 缓冲器 | i n = 0 in=0 in=0 | i n = 1 in=1 in=1 | i n = x in=x in=x | i n = z ( 高阻 ) in=z(高阻) in=z(高阻) |

|---|---|---|---|---|

| 输出out1 | 0 | 1 | x | x |

| not 反相器 | i n = 0 in=0 in=0 | i n = 1 in=1 in=1 | i n = x in=x in=x | i n = z ( 高阻 ) in=z(高阻) in=z(高阻) |

|---|---|---|---|---|

| 输出out1 | 1 | 0 | x | x |

3. 三态门

-

bufif1、bufif0、notif1、notif0

-

有一个输出,一个输入,一个控制。

-

当控制信号为无效时,三态门输出高阻状态z。

-

if1表示,高电平时允许输出(in->out),低电平时,输出高阻状态。

-

if0表示,低电平时允许输出(in->out),高电平时,输出高阻状态。

-

列出真值表

| bufif1 缓冲器 | 控制信号 c t r l = 0 控制信号ctrl=0 控制信号ctrl=0 | 控制信号 c t r l = 1 控制信号ctrl=1 控制信号ctrl=1 | 控制信号 c t r l = x 控制信号ctrl=x 控制信号ctrl=x | 控制信号 c t r l = z ( 高阻 ) 控制信号ctrl=z(高阻) 控制信号ctrl=z(高阻) |

|---|---|---|---|---|

| 数据输入 i n = 0 数据输入in=0 数据输入in=0 | out=z(高阻) | out=0 | out=0或者z | out=0或者z |

| 数据输入 i n = 1 数据输入in=1 数据输入in=1 | out=z(高阻) | out=1 | out=1或者z | out=1或者z |

| 数据输入 i n = x 数据输入in=x 数据输入in=x | out=z(高阻) | x | x | x |

| 数据输入 i n = z ( 高阻 ) 数据输入in=z(高阻) 数据输入in=z(高阻) | out=z(高阻) | x | x | x |

| notif1 缓冲器 | 控制信号 c t r l = 0 控制信号ctrl=0 控制信号ctrl=0 | 控制信号 c t r l = 1 控制信号ctrl=1 控制信号ctrl=1 | 控制信号 c t r l = x 控制信号ctrl=x 控制信号ctrl=x | 控制信号 c t r l = z ( 高阻 ) 控制信号ctrl=z(高阻) 控制信号ctrl=z(高阻) |

|---|---|---|---|---|

| 数据输入 i n = 0 数据输入in=0 数据输入in=0 | out=z(高阻) | out=1 | out=1或者z | out=1或者z |

| 数据输入 i n = 1 数据输入in=1 数据输入in=1 | out=z(高阻) | out=0 | out=0或者z | out=0或者z |

| 数据输入 i n = x 数据输入in=x 数据输入in=x | out=z(高阻) | x | x | x |

| 数据输入 i n = z ( 高阻 ) 数据输入in=z(高阻) 数据输入in=z(高阻) | out=z(高阻) | x | x | x |

4. 举例

(1) Verilog实现2线-4线译码器

- 2线-4线译码器,使用Verilog语言的门级元件进行描述。

- 2个数据输入A1和A0

- 1个使能输入E

- 4个输出Y

- 3个内部节点,使用wire定义。

- 关键字定义多个元件时,调用名不能省略,多个调用名元件之间必须使用逗号分隔。

//门级Gate-Level

//2线-4线译码器 2-to-4 line decodermodule _2to4decoder(A1,A0,E,Y);input A,B,E; //定义输入信号output [3:0]Y;//定义输出信号wire A1not,A0not,Enot;//内部节点信号//非门not n1(A1not,A1),n2(A0not,A0),n3(Enot,E);//与非门nand n4(Y[0],A1not,A0not,Enot),n5(Y[1],A1not,A0 ,Enot),n6(Y[2],A1 ,A0not,Enot),n7(Y[3],A1 ,A0 ,Enot);endmodule(2) Verilog实现2选1数据选择器

-

使用了三态门缓冲器bufif0,bufif1。

-

重点:L同时受两路信号驱动。在多驱动元的情况下逻辑值会发生冲突,从而产生不确定值。类似于竞争冒险。

-

在Verilog中:

- 线网 wire:用于表示单个门驱动或连续赋值语句驱动的网络数据类型,

- 三态线网 tri:用来表示多驱动器驱动的网络型数据。

- 当没有定义wire和tri的逻辑强度时,在多驱动元的情况下逻辑值会发生冲突,从而产生不确定值。

//门级Gate-Level

//2线-1线数据选择器 2-to-1-line multiplexer

module _2to1muxtri(A,B,SEL,L)input A,B,SEL;output L; //定义输出信号tri L;//tri数据类型(三态线网),多驱动网络类型。bufif1(L,B,SEL);bufif0(L,A,SEL);

endmodule5. 分层次的电路设计方法简介

-

自顶而下(top-down):先定义顶层模块,再定义顶层模块用到的子模块。

-

自底向上(bottom-up):先定义底层的各个子模块,再将子模块组合起来,构成顶层模块。

- (1)使用门级元件定义底层的半加器。

- (2)调用2个半加器+一个或门,定义一个全加器。

- (3)调用4个1位全加器,构成顶层的4位全加器。

-

上层模块调用下层模块时,通过模块名完成调用过程,调用名不能省略。

- 调用模块时,按照原来端口的排列顺序,可以使用一套新的端口,也可以使用同名的旧端口。

- 调用模块时,按照端口名称,对应下层模块端口名称。顺序任意。 " . 下层端口 ( 上层端口 ) − > . S ( S 1 ) " ".下层端口(上层端口)->.S(S1)" ".下层端口(上层端口)−>.S(S1)"

verilog实现4位全加器

- 非超前进位加法器。

- 底层半加器

//半加器

module halfadder(S,C,A,B)input A,B;output S,C;//和xor(S,A,B);//S=A⊕B//进位and(C,A,B);//C=AB

endmodule

- 2个半加器+1个或门=1个1位全加器

//全加器

module fulladder(S,CO,A,B,CI)input A,B,CI;output S,CO;wire S1,D1,D2;//计算中间值S1,D1halfadder HA1(S1,D1,A,B);//和halfadder HA2(S,D2,S1,CI);//进位or g1(CO,D2,D1);

endmodule

- 4个1位全加器=1个4位全加器

module _4bit_adder(S,C3,A,B,C_1)input [3:0]A,B;input C_1;output [3:0]S;output C3;wire C0,C1,C2;//内部进位信号fulladder FA0(S[0],C0,A[0],B[0],C_1),FA1(S[1],C1,A[1],B[1],C0),FA2(S[2],C2,A[2],B[2],C1),FA3(S[3],C3,A[3],B[3],C2);

endmodule

4.6.2 组合逻辑电路的数据流建模

- 门级建模太费事,工作效率低。

- 使用数据流建模,较高的抽象级别,描述电路。

- 通过“综合软件”,能够自动转换成门级电路。

1. 运算符

- 大约30个运算符。

| 类型 | 分类 | 符号 | 功能说明 |

|---|---|---|---|

| 算术运算符 | 双目运算符 | + | 二进制加 |

| 算术运算符 | 双目运算符 | - | 二进制减 |

| 算术运算符 | 双目运算符 | * | 二进制乘 |

| 算术运算符 | 双目运算符 | / | 二进制除 |

| 算术运算符 | 双目运算符 | % | 求模 |

| ------------ | ---------- | ----------------- | ----------------- |

| 关系运算符 | 双目运算符 | > | 大于 |

| 关系运算符 | 双目运算符 | < | 小于 |

| 关系运算符 | 双目运算符 | >= | 大于等于 |

| 关系运算符 | 双目运算符 | <= | 小于等于 |

| 关系运算符 | 双目运算符 | == | 等于 |

| 关系运算符 | 双目运算符 | != | 不等于 |

| 关系运算符 | 双目运算符 | === | 全等于 |

| 关系运算符 | 双目运算符 | !== | 不全等于 |

| ------------ | ---------- | ----------------- | ----------------- |

| 位运算符 | 双目运算符 | ~ | 按位取反 |

| 位运算符 | 双目运算符 | & | 按位与 |

| 位运算符 | 双目运算符 | | | 按位或 |

| 位运算符 | 双目运算符 | ^ | 按位异或 |

| 位运算符 | 双目运算符 | ^~ 或 ~^ | 按位同或 |

| ------------ | ---------- | ----------------- | ----------------- |

| 缩位运算符 | 单目运算符 | & | 缩位与 |

| 缩位运算符 | 单目运算符 | ~& | 缩位与非 |

| 缩位运算符 | 单目运算符 | | | 缩位或 |

| 缩位运算符 | 单目运算符 | ~| | 缩位或非 |

| 缩位运算符 | 单目运算符 | ^ | 缩位异或 |

| 缩位运算符 | 单目运算符 | ^~ 或 ~^ | 缩位同或 |

| ------------ | ---------- | ----------------- | ----------------- |

| 逻辑运算符 | - | ! | 逻辑非 |

| 逻辑运算符 | - | && | 逻辑与 |

| 逻辑运算符 | - | || | 逻辑或 |

| ------------ | ---------- | ----------------- | ----------------- |

| 移位运算符 | 双目运算符 | >> | 右移 |

| 移位运算符 | 双目运算符 | << | 左移 |

| ------------ | ---------- | ----------------- | ----------------- |

| 位拼接运算符 | - | { , } { { } } | 将多个操作数拼接成一个操作数 |

| ------------ | ---------- | ----------------- | ----------------- |

| 条件运算符 | 三目运算符 | ?: | 如果真,则,否,则 |

2.举例

(1)连续赋值语句 assign

- verilog语言中,基本语句是“连续赋值语句”。

- 针对wire型变量进行赋值。

- 这里的“连续”,表示持续性赋值,而不是一次性。

- 如下所示,只要等式右边逻辑值发生变化,会立即被计算出,并赋值给左边的变量

wire A,B,SEL,L;//4个连线型变量assign L = (A&~SEL)|(B&SEL);//连续赋值- 例如1:前文门级实现的2-4译码器,重新描述如下:

module decoder_df(A1,A0,E,Y);input A1,A0,E;output [3:0]Y;assign Y[0] = ~(~A1 & ~A0 & ~E);//000assign Y[1] = ~(~A1 & A0 & ~E);//010assign Y[2] = ~( A1 & ~A0 & ~E);//100assign Y[3] = ~( A1 & A0 & ~E);//110

endmodule

- 数据流与门级建模对比

- 例如2,4位全加器,重新实现:

- 被加数、加数都是4位的,如果发生进位,结果可能是5位。

- 用{Cout,SUM}拼接起来,Cout接收bit4,SUM接收bit[3:0]。

module binary_adder(A,B,Cin,SUM,Cout);input [3:0]A,B;input Cin;output [3:0]SUM;output Cout;assign {Cout,SUM} = A+B+Cin;

endmodule

-

数据流与门级建模对比

-

例如3,2选1数据选择器

-

使用连续赋值语句

module mux2x1_df(A,B,SEL,L);input A,B,SEL;output L;assign L=SEL?A:B;

endmodule

- 数据流与门级建模对比

4.6.3 组合逻辑电路的行为级建模

-

描述数字逻辑电路的功能和算法。

-

always是一个循环执行语句,后面跟着循环执行条件。

-

在always结构中,逻辑表达式就是一种过程赋值语句。

always @( 循环执行的条件 ) //不加分号“;”

//括号里的任何一个变量发生变化时,都会触发执行后面的过程赋值语句。

//执行完最后一句后,执行挂起,always语句再次等待变量发生变化。

//因此,循环执行条件被称为,“敏感变量”。

always @( 敏感变量 )

//敏感变量之间,使用关键词or,代替逻辑或运算“|”

-

always结构,过程赋值语句,只能给reg类型的变量赋值。

-

条件语句(if-else)

-

多路分支语句(case-endcase)

1. 条件语句

- condition_expr 一般是 逻辑表达式或者关系表达式

- condition_expr = 0,x,z时,按照“假”处理。

- condition_expr = 1,按照“真”处理,并执行相应的语句。

if(condition_expr) true_statement; if(condition_expr) true_statement;

else fale_statement;if(condition_expr1) true_statement1;

else if(condition_expr2)true_statement2;

else if(condition_expr3)true_statement3;

......

else default_statement;

2. 多路分支语句

- 先计算case_expr的值。

- 每个分支可以是单条语句,也可以是多条语句。

- 多条语句时,需要用begin和end包围着,构成一个整体(顺序语句块)。

- 每个分支的表达式的值,必须不同。执行完某一个分支后,case语句结束。(不需要break)

- 连续几个分支,都执行同样的表达式,可以用逗号分隔各个分支表达式,将执行语句放在其中最后一个表达式的后面。

case(case_expr)

item_expr1: statement1;

item_expr2: statement2;

......

default: default_statement;//可以省略

endcase

3. 举例

- 2选1数据选择器。

- 因为过程赋值语句,只能给reg数据赋值,所以需要把输出L定义成reg类型。

module mux2to1_bh(A,B,SEL,L)input A,B,SEL;output L;reg L; //always @(SEL or A or B) //敏感变量,任何一个变化,都会触发执行if(SEL == 1)L=B; //if(SEL) L=B;else L=A;

endmodule

- 4选1数据选择器

module mux4to1_bh(A,SEL,E,L)input [3:0]A;input [1:0]SEL;input E;output L;reg L; always @( A or SEL or E) //敏感变量,任何一个变化,都会触发执行begin if(E==1) L=0; else case(SEL)2'd0: L=A[0];2'd1: L=A[1];2'd2: L=A[2];2'd3: L=A[3];endcaseend

endmodule

相关文章:

【学习笔记】4、组合逻辑电路(下)

接前文《【学习笔记】4、组合逻辑电路(上)》 4.4.5 算术运算电路 1. 半加器和全加器 半加器和全加器是算术运算电路中的基本单元。半加器和全加器是1位相加的组合逻辑电路。 (1)半加器 半加器:只考虑两个加数本身,不考虑低位进…...

使机器人在执行任务倒快递

这段代码是用来控制机器人在不同模式下的行为,具体是处理 residenceright 和 residenceleft 两种模式下的过渡过程。代码中使用了一个 mythread 结构体,该结构体包含了机器人的当前模式 (mode) 和过渡过程的阶段 (residenceTransientProcess)。以下是对这…...

谈谈软件交互设计

谈谈软件交互设计 交互设计的由来 交互设计(Interaction Design)这一概念,最初是由IDEO创始人之一Bill.Moggridge(莫格里奇)1984年在一次会议上提出。他设计了世界上第一台笔记本电脑Compass,并写作出版了在交互设计领域影响深远的《Designing Interactions》一书,被称…...

npm install报错:淘宝镜像证书过期

npm install报错:淘宝镜像证书过期 近期使用npm淘宝镜像新建项目或依赖时出现报错: npm ERR! request to https://registry.npm.taobao.org/xxx failed, reason: certificate has expired 错误原因: 早在 2021 年,淘宝就发文称…...

各种Attention|即插即用|适用于YoloV5、V7、V8、V9、V10(一)

摘要 本文总结了各种注意力,即插即用,方便大家将注意力加到自己的论文中。 SE import torch from torch import nn class SEAttention(nn.Module): """ SENet(Squeeze-and-Excitation Networks)中的注意力…...

语言模型演进:从NLP到LLM的跨越之旅

在人工智能的浩瀚宇宙中,自然语言处理(NLP)一直是一个充满挑战和机遇的领域。随着技术的发展,我们见证了从传统规则到统计机器学习,再到深度学习和预训练模型的演进。如今,我们站在了大型语言模型ÿ…...

自动驾驶中的人机互相接管问题讨论

一、背景 人机接管(human takeover)是指在自动驾驶过程中,当系统遇到超出其处理能力或预设安全阈值的情况时,将控制权交还给驾驶员的过程。这一环节的设计直接关系到自动驾驶技术的实用性与安全性,是目前研究和实践中…...

语音识别HResults统计工具以及字根据关键词进行合并

#主要想说一下关键词合并 1.HResults统计工具可以参考其他博主的:https://blog.csdn.net/weixin_30348519/article/details/98426654?ops_request_misc%257B%2522request%255Fid%2522%253A%2522172088587416800215066191%2522%252C%2522scm%2522%253A%25222014071…...

lvs集群、NAT模式和DR模式、keepalive

目录 lvs集群概念 集群的类型:三种类型 系统可靠性指标 lvs集群中的术语 lvs的工作方式 NAT模式 lvs的工具 算法 实验 数据流向 步骤 一 、调度器配置(test1 192.168.233.10) 二、RS配置(nginx1和nginx2)…...

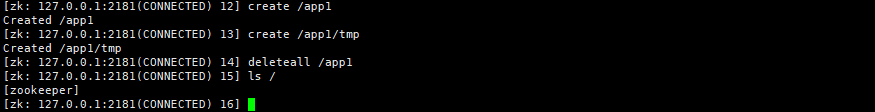

zookeeper在哪里能用到

zookeeper是什么 ZooKeeper 顾名思义 动物园管理员,他是拿来管大象(Hadoop) 、 蜜蜂(Hive) 、 小猪(Pig) 的管理员, Apache Hbase和 Apache Solr 以及LinkedIn sensei 等项目中都采用到了 Zookeeper。 ZooKeeper是一个分布式的,开放源码的分…...

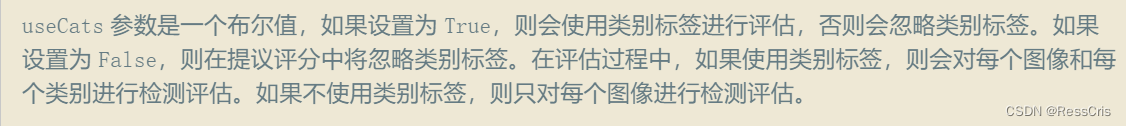

coco_eval 使用

参考 coco eval 解析 COCO目标检测比赛中的模型评价指标介绍! coco 的评估函数对应的是 pycocotools 中的 cocoeval.py 文件。 从整体上来看,整个 COCOeval 类的框架如图: 基础的用法为 # The usage for CocoEval is as follows: cocoGt…...

国产精品ORM框架-SqlSugar详解 进阶功能 集成整合 脚手架应用 专题二

国产精品ORM框架-SqlSugar详解 SqlSugar初识 专题一-CSDN博客 sqlsugar 官网-CSDN博客 4、进阶功能 5、集成整合 6、脚手架应用 4、进阶功能 4.1、生命周期 Queryable 什么时候操作库 Queryable是一个引用类型 Queryable拷贝机制 4.2、执行Sql 方法列表 方法名 描述 返…...

el-table 动态添加删除 -- 鼠标移入移出显隐删除图标

<el-table class"list-box" :data"replaceDataList" border><el-table-column label"原始值" prop"original" align"center" ><template slot-scope"scope"><div mouseenter"showClick…...

Kafka接收消息

文章目录 Acknowledgment读消息指定分区批量消费消息拦截 // 采用监听得方式接收 Payload标记消息体内容. KafkaListener(topics {"test"},groupId "hello") public void onEvent(Payload String event,Header(value KafkaHeaders.RECEIVED_TOPIC) Stri…...

C语言 | Leetcode C语言题解之第233题数字1的个数

题目: 题解: int countDigitOne(int n) {// mulk 表示 10^k// 在下面的代码中,可以发现 k 并没有被直接使用到(都是使用 10^k)// 但为了让代码看起来更加直观,这里保留了 klong long mulk 1;int ans 0;f…...

简谈设计模式之原型模式

原型模式是一种创建型设计模式, 用于创建对象, 而不必指定它们所属的具体类. 它通过复制现有对象 (即原型) 来创建新对象. 原型模式适用于当创建新对象的过程代价较高或复杂时, 通过克隆现有对象来提高性能 原型模式结构 原型接口. 声明一个克隆自身的接口具体原型. 实现克隆…...

CentOS7.X系统部署Zabbix6.0版本(可跟做)

文章目录 一、部署环境说明二、基本环境部署步骤1、环境初始化操作2、部署并配置Nginx3、部署并配置PHP4、测试NginxPHP环境5、部署并配置MariaDB 三、Zabbix-Server部署步骤1、编译安装Zabbix-Server2、导入Zabbix初始化库3、配置Zabbix前端UI4、启动Zabbix-Server5、WEB页面配…...

QT文件生成可执行的exe程序

将qt项目生成可执行的exe程序可按照以下步骤进行: 1、在qt中构建运行生成.exe文件; 2、从自定义的路径中取出exe文件放在一个单独的空文件夹中(exe文件在该文件夹中的release文件夹中); 3、从开始程序中搜索qt…...

【ZooKeeper学习笔记】

1. ZooKeeper基本概念 Zookeeper官网:https://zookeeper.apache.org/index.html Zookeeper是Apache Hadoop项目中的一个子项目,是一个树形目录服务Zookeeper翻译过来就是动物园管理员,用来管理Hadoop(大象)、Hive&…...

220V降5V芯片输出电压电流封装选型WT

220V降5V芯片输出电压电流封装选型WT 220V降5V恒压推荐:非隔离芯片选型及其应用方案 在考虑220V转低压应用方案时,以下非隔离芯片型号及其封装形式提供了不同的电压电流输出能力: 1. WT5101A(SOT23-3封装)适用于将2…...

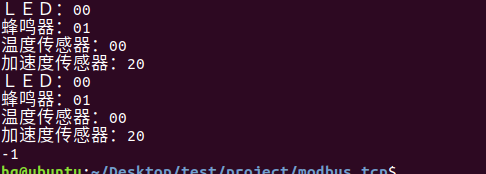

网络编程(Modbus进阶)

思维导图 Modbus RTU(先学一点理论) 概念 Modbus RTU 是工业自动化领域 最广泛应用的串行通信协议,由 Modicon 公司(现施耐德电气)于 1979 年推出。它以 高效率、强健性、易实现的特点成为工业控制系统的通信标准。 包…...

测试微信模版消息推送

进入“开发接口管理”--“公众平台测试账号”,无需申请公众账号、可在测试账号中体验并测试微信公众平台所有高级接口。 获取access_token: 自定义模版消息: 关注测试号:扫二维码关注测试号。 发送模版消息: import requests da…...

SkyWalking 10.2.0 SWCK 配置过程

SkyWalking 10.2.0 & SWCK 配置过程 skywalking oap-server & ui 使用Docker安装在K8S集群以外,K8S集群中的微服务使用initContainer按命名空间将skywalking-java-agent注入到业务容器中。 SWCK有整套的解决方案,全安装在K8S群集中。 具体可参…...

【杂谈】-递归进化:人工智能的自我改进与监管挑战

递归进化:人工智能的自我改进与监管挑战 文章目录 递归进化:人工智能的自我改进与监管挑战1、自我改进型人工智能的崛起2、人工智能如何挑战人类监管?3、确保人工智能受控的策略4、人类在人工智能发展中的角色5、平衡自主性与控制力6、总结与…...

转转集团旗下首家二手多品类循环仓店“超级转转”开业

6月9日,国内领先的循环经济企业转转集团旗下首家二手多品类循环仓店“超级转转”正式开业。 转转集团创始人兼CEO黄炜、转转循环时尚发起人朱珠、转转集团COO兼红布林CEO胡伟琨、王府井集团副总裁祝捷等出席了开业剪彩仪式。 据「TMT星球」了解,“超级…...

使用van-uploader 的UI组件,结合vue2如何实现图片上传组件的封装

以下是基于 vant-ui(适配 Vue2 版本 )实现截图中照片上传预览、删除功能,并封装成可复用组件的完整代码,包含样式和逻辑实现,可直接在 Vue2 项目中使用: 1. 封装的图片上传组件 ImageUploader.vue <te…...

拉力测试cuda pytorch 把 4070显卡拉满

import torch import timedef stress_test_gpu(matrix_size16384, duration300):"""对GPU进行压力测试,通过持续的矩阵乘法来最大化GPU利用率参数:matrix_size: 矩阵维度大小,增大可提高计算复杂度duration: 测试持续时间(秒&…...

自然语言处理——Transformer

自然语言处理——Transformer 自注意力机制多头注意力机制Transformer 虽然循环神经网络可以对具有序列特性的数据非常有效,它能挖掘数据中的时序信息以及语义信息,但是它有一个很大的缺陷——很难并行化。 我们可以考虑用CNN来替代RNN,但是…...

十九、【用户管理与权限 - 篇一】后端基础:用户列表与角色模型的初步构建

【用户管理与权限 - 篇一】后端基础:用户列表与角色模型的初步构建 前言准备工作第一部分:回顾 Django 内置的 `User` 模型第二部分:设计并创建 `Role` 和 `UserProfile` 模型第三部分:创建 Serializers第四部分:创建 ViewSets第五部分:注册 API 路由第六部分:后端初步测…...

的打车小程序)

基于鸿蒙(HarmonyOS5)的打车小程序

1. 开发环境准备 安装DevEco Studio (鸿蒙官方IDE)配置HarmonyOS SDK申请开发者账号和必要的API密钥 2. 项目结构设计 ├── entry │ ├── src │ │ ├── main │ │ │ ├── ets │ │ │ │ ├── pages │ │ │ │ │ ├── H…...