63.HDMI显示器驱动设计与验证-彩条实验

(1)常见的视频传输接口有三种: VGA 接口、 DVI 接口和 HDMI 接口,目前的显示设备都配有这三种视频传输接口。三类视频接口的发展历程为 VGA→DVI→HDMI。其中 VGA 接口出现最早,只能传输模拟图像信号; 随后出现的 DVI 接口又分为三类: DVI-A、 DVI-D、 DVI-I,分别可传输纯模拟图像信号、纯数字图像信号和兼容模拟、数字图像信号;最后的HDMI 在传输数字图像信号的基础上又可以传输音频信号。

(2)HDMI 全称“High Definition Multimedia Interface 高清多媒体接口”,HDMI 标准的制定,并没有抛弃 DVI 标准中相对成熟且较易实现的部分技术标准,整个传输原理依然是基于 TMDS 编码技术。针对 DVI 的诸多问题,HDMI 做了大幅改进。HDMI 接口体积更小,各种设备都能轻松安装可用于机顶盒、DVD 播放机、个人计算机、电视、游戏主机、综合扩大机、数字音响与电视机等设备;抗干扰能力更强,能实现最长20 米的无增益传输;针对大尺寸数字平板电视分辨率进行优化,兼容性好;拥有强大的版权保护机制(HDCP),有效防止盗版现象;支持 24bit 色深处理,(RGB、YCbCr4-4-4、YCbCr4-2-2);一根线缆实现数字音频、视频信号同步传输,有效降低使用成本和繁杂程度。

(3)HDMI type-a 引脚

TMDS:最小化传输差分信号

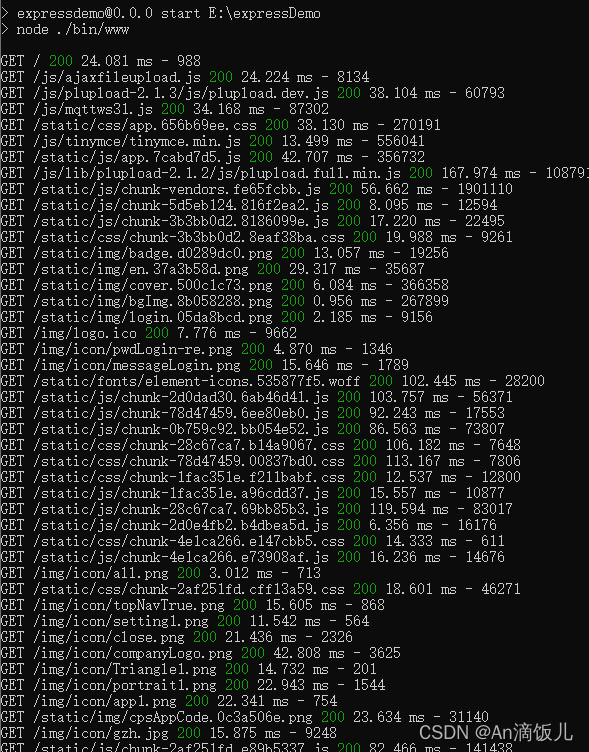

升腾A7板块采用了SII9134芯片,能实现VGA转HDMI的编码,因此不需要自己编写HDMI的编码

(4)如果要编写HDMI编码,对应Visio视图:

(5)TMDS编码(8bit转10bit)具体代码:

module encode

(input wire hdmi_clk , input wire reset_n , //复位信号,低电平有效input wire hsync , //行同步信号input wire vsync , //列同步信号input wire de , input wire [7:0] data_in , output reg [9:0] data_out

);//变量定义

wire condition_1 ;

wire condition_2 ;

wire condition_3 ;

wire [8:0] q_m ;reg [3:0] q_m_n1 ;

reg [3:0] q_m_n0 ;

reg [3:0] data_in_n1 ; //最多8个1 ,即1000 四位

reg [7:0] data_in_reg ;

reg [4:0] cnt ;

reg [8:0] q_m_reg ;

reg de_reg0 ;

reg de_reg1 ;

reg hsync_reg0 ;

reg hsync_reg1 ;

reg vsync_reg0 ;

reg vsync_reg1 ;//条件定义

always@(posedge hdmi_clk or negedge reset_n)if(!reset_n)data_in_n1 <= 4'd0;else data_in_n1 <= data_in[0] + data_in[1] + data_in[2] + data_in[3]+data_in[4] + data_in[5] + data_in[6] + data_in[7];assign condition_1 = (data_in_n1 > 4'd4) || ((data_in_n1 == 4'd4) && (data_in_reg[0] == 1'd0));always@(posedge hdmi_clk or negedge reset_n)if(!reset_n)beginq_m_n1 <= 4'd0;q_m_n0 <= 4'd0;endelse beginq_m_n1 = q_m[0] + q_m[1] + q_m[2] + q_m[3]+ q_m[4] + q_m[5] + q_m[6] + q_m[7];q_m_n0 = 4'd8 - (q_m[0] + q_m[1] + q_m[2] + q_m[3]+ q_m[4] + q_m[5] + q_m[6] + q_m[7]);endassign condition_2 = (cnt == 5'd0) || (q_m_n1 == q_m_n0);

assign condition_3 = ((cnt[4] == 1'd0) && (q_m_n1 > q_m_n0)) || ((cnt[4] == 1'd1) && (q_m_n1 < q_m_n0)); //打拍变量定义

always@(posedge hdmi_clk or negedge reset_n)if(!reset_n)begindata_in_reg <= 8'd0;q_m_reg <= 9'd0;de_reg0 <= 1'd0;de_reg1 <= 1'd0;hsync_reg0 <= 1'd0;hsync_reg1 <= 1'd0;vsync_reg0 <= 1'd0;vsync_reg1 <= 1'd0; endelse begin data_in_reg <= data_in;q_m_reg <= q_m ;de_reg0 <= de;de_reg1 <= de_reg0;hsync_reg0 <= hsync;hsync_reg1 <= hsync_reg0;vsync_reg0 <= vsync;vsync_reg1 <= vsync_reg0; end//q_m信号变量

assign q_m[0] = data_in_reg[0] ;

assign q_m[1] = condition_1 ? (q_m[0] == data_in_reg[1]) : (q_m[0] ^ data_in_reg[1]);

assign q_m[2] = condition_1 ? (q_m[1] == data_in_reg[2]) : (q_m[1] ^ data_in_reg[2]);

assign q_m[3] = condition_1 ? (q_m[2] == data_in_reg[3]) : (q_m[2] ^ data_in_reg[3]);

assign q_m[4] = condition_1 ? (q_m[3] == data_in_reg[4]) : (q_m[3] ^ data_in_reg[4]);

assign q_m[5] = condition_1 ? (q_m[4] == data_in_reg[5]) : (q_m[4] ^ data_in_reg[5]);

assign q_m[6] = condition_1 ? (q_m[5] == data_in_reg[6]) : (q_m[5] ^ data_in_reg[6]);

assign q_m[7] = condition_1 ? (q_m[6] == data_in_reg[7]) : (q_m[6] ^ data_in_reg[7]);

assign q_m[8] = condition_1 ? 1'd0 : 1'd1;always@(posedge hdmi_clk or negedge reset_n)if(!reset_n)begindata_out <= 10'd0;cnt <= 5'd0;endelse beginif(de_reg1)beginif(condition_2)begindata_out[9] <= ~q_m_reg[8];data_out[8] <= q_m_reg[8];data_out[7:0] <= (q_m_reg[8]? q_m_reg[7:0]: ~q_m_reg[7:0]);if(q_m_reg[8] == 1'd0)cnt <= cnt + q_m_n0 - q_m_n1;else cnt <= cnt + q_m_n1 - q_m_n0;endelse beginif(condition_3)begindata_out[9] <= 1'd1;data_out[8] <= q_m_reg[8];data_out[7:0] <= ~q_m_reg[7:0];cnt <= cnt + {q_m_reg[8],1'd0} + q_m_n0 - q_m_n1;endelse begindata_out[9] <= 1'd0;data_out[8] <= q_m_reg[8];data_out[7:0] <= q_m_reg[7:0];cnt <= cnt - {~q_m_reg[8],1'd0} + q_m_n1 - q_m_n0; endendendelse begincnt <= 5'd0;case({vsync_reg1,hsync_reg0})2'b00: data_out <= 10'b11_0101_0100;2'b01: data_out <= 10'b00_1010_1011;2'b10: data_out <= 10'b01_0101_0100;2'b11: data_out <= 10'b10_1010_1011;default:;endcaseendendendmodule

(6)原语:英文全称“Primitive”,是Xilinx针对其器件特征开发的一系列常用模块的名字,用户可以将其视为Xilinx公司为用户提供的库函数。原语按照功能可以分为10类,包括:计算组件、IO端口组件、寄存器和锁存器、时钟组件、处理器组件、移位寄存器组件、配置和检测组件、RAM/ROM组件、Slice/CLB组件以及G比特收发器组件。

(7)ODDR是Xilinx提供的双数据速率原语,双数据速率原语ODDR可以用于在逻辑资源中实现DDR寄存器,可以把单沿传输的数据转换为双沿传输的数据。

OBUFDA是Xilinx提供的将单端信号转换为差分信号的原语。

(8)升腾Pro对应Viso视图(驱动SII934芯片):

(9)对应代码:

- IIC控制器

module IIC_ctrl(input wire clk ,input wire reset_n ,input wire IIC_start ,input wire wr_en ,input wire rd_en ,input wire [7:0] device_addr ,input wire [15:0] byte_addr ,input wire [7:0] wr_data ,input wire addr_num ,output reg IIC_SCL ,inout wire IIC_SDA ,output reg IIC_clk ,output reg IIC_end ,output reg [7:0] rd_data );reg [4:0] cnt_1M ; //计数最大值是25 一个五位宽的寄存器足以胜任计数任务reg [15:0] state ;reg [1:0] IIC_clk_cnt ;reg EN_IIC_clk_cnt ;reg [2:0] bit_cnt ;reg ack ;reg sda_out ;reg [7:0] rd_data_reg ;wire sda_in ;wire EN_IIC_SDA ;wire [6:0] device_add_i ; assign device_add_i = device_addr[7:1];parameter IDLE = 16'b0000_0000_0000_0001 ; //空闲状态parameter START = 16'b0000_0000_0000_0010 ; //发送开始信号parameter SEND_D_A = 16'b0000_0000_0000_0100 ; //发送控制命令(器件地址+写操作) {7'b1010_011,1'b0}parameter ACK_1 = 16'b0000_0000_0000_1000 ; //等待响应 parameter SEND_B_H = 16'b0000_0000_0001_0000 ; //发送存储地址高8位 parameter ACK_2 = 16'b0000_0000_0010_0000 ; //等待响应parameter SEND_B_L = 16'b0000_0000_0100_0000 ; //发送存储地址低8位parameter ACK_3 = 16'b0000_0000_1000_0000 ; //等待响应parameter WR_DATA = 16'b0000_0001_0000_0000 ; //写入单比特数据 parameter ACK_4 = 16'b0000_0010_0000_0000 ; //等待响应parameter START_2 = 16'b0000_0100_0000_0000 ; //发送开始信号parameter SEND_RD_A = 16'b0000_1000_0000_0000 ; //发送控制命令(器件地址+读操作) {7'b0101_011,1'b1} parameter ACK_5 = 16'b0001_0000_0000_0000 ; //等待响应parameter RD_DATA = 16'b0010_0000_0000_0000 ; //读出单比特数据parameter NO_ACK = 16'b0100_0000_0000_0000 ; //等待无响应信号parameter END = 16'b1000_0000_0000_0000 ; //结束单比特传输// parameter DEVICE_ADD = 7'b1010_011 ; //EEPROM器件地址设定/*-----------IIC_clk生成模块--------------------*/

//IIC_clk 频率要求1MHz,而系统时钟clk频率为50MHz,半个周期需要计数25次(5位寄存器)always@(posedge clk or negedge reset_n)if(!reset_n)cnt_1M <= 5'd0;else if(cnt_1M == 5'd24)cnt_1M <= 5'd0;else cnt_1M <= cnt_1M + 5'd1;always@(posedge clk or negedge reset_n)if(!reset_n)IIC_clk <= 1'd0;else if(cnt_1M == 5'd24)IIC_clk <= ~IIC_clk;else IIC_clk <= IIC_clk;/*----------------状态机设计-----------------------*/ always@(posedge IIC_clk or negedge reset_n)if(!reset_n)state <= IDLE;else begincase(state)IDLE :if(IIC_start)state <= START;else state <= state;START : if(IIC_clk_cnt == 2'd3)state <= SEND_D_A;else state <= state; SEND_D_A : if((bit_cnt == 3'd7) && (IIC_clk_cnt == 2'd3))state <= ACK_1;else state <= state;ACK_1 : if((IIC_clk_cnt == 2'd3) && (ack == 1'd0) && (addr_num == 1'd1))state <= SEND_B_H;else if((IIC_clk_cnt == 2'd3) && (ack == 1'd0) && (addr_num == 1'd0))state <= SEND_B_L;else state <= state; SEND_B_H : if((bit_cnt == 3'd7) && (IIC_clk_cnt == 2'd3))state <= ACK_2;else state <= state;ACK_2 : if((IIC_clk_cnt == 2'd3) && (ack == 1'd0))state <= SEND_B_L;else state <= state; SEND_B_L : if((bit_cnt == 3'd7) && (IIC_clk_cnt == 2'd3))state <= ACK_3;else state <= state;ACK_3 : if((IIC_clk_cnt == 2'd3) && (ack == 1'd0) && (wr_en == 1'd1))state <= WR_DATA;else if((IIC_clk_cnt == 2'd3) && (ack == 1'd0) && (rd_en == 1'd1))state <= START_2;else state <= state;WR_DATA : if((bit_cnt == 3'd7) && (IIC_clk_cnt == 2'd3))state <= ACK_4;else state <= state;ACK_4 : if((IIC_clk_cnt == 2'd3) && (ack == 1'd0))state <= END;else state <= state; START_2 : if(IIC_clk_cnt == 2'd3)state <= SEND_RD_A;else state <= state; SEND_RD_A : if((bit_cnt == 3'd7) && (IIC_clk_cnt == 2'd3))state <= ACK_5;else state <= state;ACK_5 : if((IIC_clk_cnt == 2'd3) && (ack == 1'd0))state <= RD_DATA;else state <= state; RD_DATA : if((bit_cnt == 3'd7) && (IIC_clk_cnt == 2'd3))state <= NO_ACK;else state <= state;NO_ACK : if(IIC_clk_cnt == 2'd3)state <= END;else state <= state; END : if((bit_cnt == 3'd3) && (IIC_clk_cnt == 2'd3))state <= IDLE;else state <= state;default : state <= IDLE;endcase end/*----------------IIC_clk_cnt 、 EN_IIC_clk_cnt设计-----------------------*/

always@(posedge IIC_clk or negedge reset_n)if(!reset_n)IIC_clk_cnt <= 2'd0;else if(!EN_IIC_clk_cnt) IIC_clk_cnt <= 2'd0;else IIC_clk_cnt <= IIC_clk_cnt + 2'd1;always@(posedge IIC_clk or negedge reset_n)if(!reset_n)EN_IIC_clk_cnt <= 1'd0;else if((state == END) && (bit_cnt == 3'd3) && (IIC_clk_cnt == 2'd3))EN_IIC_clk_cnt <= 1'd0;else if(IIC_start)EN_IIC_clk_cnt <= 1'd1;else EN_IIC_clk_cnt <= EN_IIC_clk_cnt;/*--------------------bit_cnt设计-----------------------*/

always@(posedge IIC_clk or negedge reset_n)if(!reset_n)bit_cnt <= 3'd0;else if((state == IDLE)||(state == START)||(state == ACK_1)||(state == ACK_2)||(state == ACK_3)||(state == ACK_4) ||(state == START_2)||(state == ACK_5)||(state == NO_ACK))bit_cnt <= 3'd0;else if((state == END) && (bit_cnt == 3'd3) && (IIC_clk_cnt == 2'd3))bit_cnt <= 3'd0;else if(IIC_clk_cnt == 2'd3)bit_cnt <= bit_cnt + 3'd1;else bit_cnt <= bit_cnt;/*--------------------ack 、 sda_in信号设计---------------------------*/

always@(*)begincase(state)ACK_1,ACK_2,ACK_3,ACK_4,ACK_5 : if(IIC_clk_cnt == 2'd0)ack <= sda_in ;else ack <= ack ;default : ack = 1'd1;endcaseendassign sda_in = IIC_SDA ;/*--------------------IIC_SCL设计-----------------------*/

always@(*)begincase(state)IDLE:IIC_SCL <= 1'd1;START:if(IIC_clk_cnt == 2'd3)IIC_SCL <= 1'd0;else IIC_SCL <= 1'd1;SEND_D_A,ACK_1,SEND_B_H,ACK_2,SEND_B_L,ACK_3,WR_DATA,ACK_4,START_2,SEND_RD_A,ACK_5,RD_DATA,NO_ACK:if((IIC_clk_cnt == 2'd1) || (IIC_clk_cnt == 2'd2))IIC_SCL <= 1'd1;else IIC_SCL <= 1'd0;END:if((bit_cnt == 3'd0) && (IIC_clk_cnt == 2'd0))IIC_SCL <= 1'd0;else IIC_SCL <= 1'd1;default:IIC_SCL <= 1'd1;endcaseend/*--------------------sda_out 、 rd_data_reg设计-----------------------*/

always@(*)begincase(state)IDLE :beginsda_out <= 1'd1; rd_data_reg <= 8'd0;endSTART :if(IIC_clk_cnt >= 2'd1)sda_out <= 1'd0; else sda_out <= 1'd1;SEND_D_A :if(bit_cnt <= 3'd6)sda_out <= device_add_i[6 - bit_cnt];else sda_out <= 1'd0;ACK_1,ACK_2,ACK_3,ACK_4,ACK_5 :sda_out <= 1'd1;SEND_B_H : sda_out <= byte_addr[15-bit_cnt]; SEND_B_L : sda_out <= byte_addr[7-bit_cnt]; WR_DATA :sda_out <= wr_data[7-bit_cnt]; START_2 :if(IIC_clk_cnt >= 2'd2)sda_out <= 1'd0; else sda_out <= 1'd1; SEND_RD_A :if(bit_cnt <= 3'd6)sda_out <= device_add_i[6 - bit_cnt];else sda_out <= 1'd1; RD_DATA :beginsda_out <= 1'd1;if(IIC_clk_cnt == 2'd2)rd_data_reg[7 - bit_cnt] <= sda_in;else rd_data_reg <= rd_data_reg;endNO_ACK :sda_out <= 1'd1;END :if((bit_cnt == 3'd0) && (IIC_clk_cnt <= 2'd2))sda_out <= 1'd0;else sda_out <= 1'd1;default :beginsda_out <= 1'd1;rd_data_reg <= rd_data_reg;endendcaseend/*--------------------rd_data设计-----------------------*/

always@(posedge IIC_clk or negedge reset_n)if(!reset_n)rd_data <= 8'd0;else if((state == RD_DATA) && (bit_cnt == 3'd7) && (IIC_clk_cnt == 2'd3))rd_data <= rd_data_reg;else rd_data <= rd_data;/*--------------------EN_IIC_SDA设计-----------------------*/

//EN_IIC_SDA信号为1,表示IIC_SDA输出;反之,EN_IIC_SDA信号为0,表示IIC_SDA作为输入.assign EN_IIC_SDA = ((state == IDLE) || (state == START) || (state == SEND_D_A) || (state == SEND_B_H) || (state == SEND_B_L) || (state == WR_DATA)|| (state == START_2) || (state == SEND_RD_A) || (state == NO_ACK)|| (state == END));/*--------------------IIC_SDA设计-----------------------*/

assign IIC_SDA = EN_IIC_SDA ? sda_out : 1'dz;/*--------------------IIC_end设计-----------------------*/

always@(posedge IIC_clk or negedge reset_n)if(!reset_n)IIC_end <= 1'd0;else if((state == END) && (bit_cnt == 3'd3) && (IIC_clk_cnt == 2'd3))IIC_end <= 1'd1;else IIC_end <= 1'd0;endmodule

- 给SII9134寄存器配置的模块

module hdmi_cfg (input wire cfg_clk ,input wire reset_n ,input wire cfg_end ,output reg cfg_start ,output wire [31:0] cfg_data ,output reg cfg_done);parameter NUM_REG = 10'd4 ; parameter CNT_WAIT_MAX = 10'd1023 ;reg [9:0] cnt_wait ; reg [9:0] cnt_num ;wire [31:0] cfg_data_reg[NUM_REG - 1'd1 : 0];assign cfg_data_reg[0] = {8'h72,16'h08,8'h35}; assign cfg_data_reg[1] = {8'h72,16'h49,8'h00}; assign cfg_data_reg[2] = {8'h72,16'h4a,8'h00}; assign cfg_data_reg[3] = {8'h72,16'h2f,8'h00};always@(posedge cfg_clk or negedge reset_n)if(!reset_n)cnt_wait <= 10'd0;else if(cnt_wait == CNT_WAIT_MAX)cnt_wait <= cnt_wait;else cnt_wait <= cnt_wait + 10'd1;always@(posedge cfg_clk or negedge reset_n)if(!reset_n)cnt_num <= 10'd0;else if(cfg_end)cnt_num <= cnt_num + 10'd1;else cnt_num <= cnt_num ;always@(posedge cfg_clk or negedge reset_n)if(!reset_n)cfg_start <= 1'd0;else if(cnt_wait == CNT_WAIT_MAX - 1'd1)cfg_start <= 1'd1;else if(cfg_end == 1'd1 && cnt_num < NUM_REG)cfg_start <= 1'd1;else cfg_start <= 1'd0;assign cfg_data = cfg_done ? 32'd0 : cfg_data_reg[cnt_num];always@(posedge cfg_clk or negedge reset_n)if(!reset_n)cfg_done <= 1'd0;else if(cfg_end == 1'd1 && cnt_num == NUM_REG)cfg_done <= 1'd1;else cfg_done <= cfg_done; endmodule - IIC顶层模块

module hdmi_iic (input wire hdmi_clk ,input wire reset_n ,output wire hdmi_scl ,inout wire hdmi_sda );wire IIC_start; wire IIC_end; wire [31:0] cfg_data; wire cfg_clk;IIC_ctrl IIC_ctrl_inst (.clk (hdmi_clk ),.reset_n (reset_n ),.IIC_start (IIC_start ),.wr_en (1'd1 ),.rd_en (),.device_addr (cfg_data[31:24] ),.byte_addr (cfg_data[23:8] ),.wr_data (cfg_data[7:0] ),.addr_num (1'd0 ),.IIC_SCL (hdmi_scl ),.IIC_SDA (hdmi_sda ),.IIC_clk (cfg_clk ),.IIC_end (IIC_end ),.rd_data () );hdmi_cfg hdmi_cfg_inst (.cfg_clk (cfg_clk ),.reset_n (reset_n ),.cfg_end (IIC_end ),.cfg_start (IIC_start ),.cfg_data (cfg_data ),.cfg_done ());endmodule - 彩条数据生成模块

module data_gen(input [9:0] hang ,input [9:0] lie ,input hdmi_clk ,input reset_n ,output reg [23:0] data

);

//定义最大行、列parameter HANG_MAX = 640 ;parameter LIE_MAX = 480 ;//定义颜色parameter RED = 24'hff0000;parameter ORANGE = 24'hffcc66;parameter YELLOW = 24'hffff00;parameter GREEN = 24'h33cc33;parameter CYAN = 24'h00ffcc;parameter BLUE = 24'h3333ff;parameter PUPPLE = 24'hcc00cc;parameter BLACK = 24'h000000;parameter WHITE = 24'hffffff;parameter GRAY = 24'hb2b2b2;//数据生成设计always@(posedge hdmi_clk or negedge reset_n)if(!reset_n)data <= BLACK ;else if((hang >= 1) && (hang <= HANG_MAX/10))data <= RED ;else if((hang > HANG_MAX/10) && (hang <= (HANG_MAX/10) * 2))data <= ORANGE ;else if((hang > (HANG_MAX/10) * 2) && (hang <= (HANG_MAX/10) * 3))data <= YELLOW ;else if((hang > (HANG_MAX/10) * 3) && (hang <= (HANG_MAX/10) * 4))data <= GREEN ;else if((hang > (HANG_MAX/10) * 4) && (hang <= (HANG_MAX/10) * 5))data <= CYAN ;else if((hang > (HANG_MAX/10) * 5) && (hang <= (HANG_MAX/10) * 6))data <= BLUE ;else if((hang > (HANG_MAX/10) * 6) && (hang <= (HANG_MAX/10) * 7))data <= PUPPLE ;else if((hang > (HANG_MAX/10) * 7) && (hang <= (HANG_MAX/10) * 8))data <= BLACK ;else if((hang > (HANG_MAX/10) * 8) && (hang <= (HANG_MAX/10) * 9))data <= WHITE ;else if((hang > (HANG_MAX/10) * 9) && (hang <= HANG_MAX))data <= GRAY ;elsedata <= BLACK ;endmodule

- 顶层模块:

module hdmi_colorbar (input wire clk ,input wire reset_n ,output wire hdmi_clk ,output wire hdmi_reset_n ,output wire hdmi_scl ,inout wire hdmi_sda ,output wire [23:0] rgb_tft ,output wire hsync ,output wire vsync ,output wire tft_DE );wire clk_25M ; wire rst_n ; wire locked ; wire [9:0] hang ; wire [9:0] lie ; wire [23:0] data ;assign rst_n = reset_n & locked ; assign hdmi_reset_n = rst_n ;clk_gen clk_gen_inst (.clk_25M (clk_25M ), // output clk_25M.clk_125M (), .reset (~reset_n ), .locked (locked ), .clk_in1 (clk ) ); assign hdmi_clk = clk_25M; data_gen data_gen_inst (.hang (hang ),.lie (lie ),.hdmi_clk (clk_25M ),.reset_n (rst_n ),.data (data ) );tft_ctrl tft_ctrl_inst (.hdmi_clk (clk_25M ),.reset_n (rst_n ),.data_in (data ),.hang (hang ),.lie (lie ),.hsync (hsync ),.vsync (vsync ),.rgb_tft (rgb_tft ),.tft_DE (tft_DE ) );hdmi_iic hdmi_iic_inst (.hdmi_clk (clk_25M ),.reset_n (rst_n ),.hdmi_scl (hdmi_scl ),.hdmi_sda (hdmi_sda ));endmodule

(10)实验现象:

相关文章:

63.HDMI显示器驱动设计与验证-彩条实验

(1)常见的视频传输接口有三种: VGA 接口、 DVI 接口和 HDMI 接口,目前的显示设备都配有这三种视频传输接口。三类视频接口的发展历程为 VGA→DVI→HDMI。其中 VGA 接口出现最早,只能传输模拟图像信号; 随后…...

安卓13设置删除网络和互联网选项 android13隐藏设置删除网络和互联网选项

总纲 android13 rom 开发总纲说明 文章目录 1.前言2.问题分析3.代码分析4.代码修改4.1修改方法14.2修改方法25.编译6.彩蛋1.前言 有些客户不想让用户修改默认的网络配置,禁止用户进入里面调整网络相关的配置。 2.问题分析 像这个问题,我们有好几种方法去处理,这种需求一般…...

C++的6种构造函数

在 C 中,构造函数是一种特殊的成员函数,用于初始化类对象。在对象创建时自动调用,构造函数的主要作用是分配资源、初始化数据成员等。根据不同的功能和使用场景,C 提供了多种类型的构造函数: 1. 默认构造函数 (Defaul…...

【FE】NPM——概述

NPM基本使用 下载Node 老生常谈,选择LTS版本官网放这里:https://nodejs.cn/download/ 1.镜像配置:镜像源 镜像配置 依赖仓库:版本查看 //不确定仓库有哪些版本,列出指定包的所有版本 npm view <package-name&…...

Clipboard.js实现复制文本到剪贴板功能

一、Clipboard.js简介 Clipboard.js是一个轻量级的实现复制文本到剪贴板功能的JavaScript插件,该插件可以将输入框,文本域,DOM节点元素中的文本内容复制到剪贴板中。 官网地址:Clipboard.js 浏览器兼容性:兼容Chrome、…...

Harbor安装笔记

下载离线安装包 wget https://github.com/goharbor/harbor/releases/download/v2.11.1/harbor-offline-installer-v2.11.1.tgz 解压 tar -zxvf harbor-offline-installer-v2.11.1.tgz 复制一份配置文件出来,修改配置 cp harbor.yml.tmpl harbor.yml vim harbor…...

HTTP 1.0 2.0 3.0详解

HTTP HTTP全称超文本传输协议,是一种属于应用层的通信协议。它允许将超文本标记语言文档(HTML)从Web服务器传输到客户端的浏览器。 HTTP报文结构 请求报文结构 请求方法: GET:一般用来请求已被URI识别的资源&#x…...

Python操作TXT文本:从入门到精通

在数字化时代,文本处理成为了许多工作和项目的基础。Python作为一种强大且易学的编程语言,在文本处理方面展现出了无与伦比的优势。本文将通过举例的方式,向读者介绍如何使用Python来操作TXT文本,让您轻松掌握文本处理的精髓。 一、读取TXT文本内容 首先,我们需要学会如…...

开源 AI 智能名片 2+1 链动模式 S2B2C 商城小程序的数据运营策略与价值创造

一、引言 1.1 研究背景 在当今数字化时代,数据运营已成为企业发展的核心驱动力。开源 AI 智能名片 21 链动模式 S2B2C 商城小程序作为一种创新的营销工具,与数据运营紧密相连。该小程序通过集成人工智能、大数据分析等先进技术,能够实时收集…...

ip 地址查看cmd命令

ip 地址查看cmd命令 在不同的操作系统中,查看IP地址的命令可能会有所不同。以下是一些常见操作系统中查看IP地址的命令: Windows: 打开命令提示符(CMD),然后输入 ipconfig 命令。 Linux/Unix: 打开终端࿰…...

力扣9.26

931. 下降路径最小和 给你一个 n x n 的 方形 整数数组 matrix ,请你找出并返回通过matrix 的下降路径 的 最小和 。 下降路径 可以从第一行中的任何元素开始,并从每一行中选择一个元素。在下一行选择的元素和当前行所选元素最多相隔一列(即…...

HT8731 内置自适应H类升压和防破音功能的10W D类及AB类音频功率放大器

1、特点 防削顶失真功能(防破音,Anti-Clipping Function, ACF) 免滤波器数字调制,直接驱动扬声器 输出功率 10W(VBAT4.2V,RL3Ω,THDN10%, fiN 1kHz) 6W(VBAT3.3~4.2V,RL4Ω,THDN<1%,20-20kHz 全频段) 3W (VBAT3.3~4.2V,RL8Ω, THDN<1%, 20- 20kHz 全频段 VB…...

webpack使用

一、简介 概述 本次使用webpack4进行构建打包 二、webpack 安装webpack、webpack-cli npm install webpack4.2.0 webpack-cli4.2.0 -D 三、loader 加载器概述 raw-loader:加载文件原始内容(utf-8) file-loader:把文件输出…...

高通Android 12 音量API设置相关代码

// 获取当前音量大小public static int getCurrentVolume(Context context) {AudioManager audioManager (AudioManager) context.getSystemService(Context.AUDIO_SERVICE);return audioManager.getStreamVolume(AudioManager.STREAM_MUSIC); // 使用 STREAM_MUSIC 作为示例…...

Qt开发第一讲

一、Qt项目里面有什么? 对各个文件的解释: Empty.pro文件 QT core gui # 要引入的Qt模块,后面学习到一些内容的时候可能会修改这里 #这个文件相当于Linux里面的makefile文件。makefile其实是一个非常古老的技术了。 #qmake搭配.pr…...

详细指南:如何有效解决Windows系统中msvcp140.dll丢失的解决方法

如果你在使用Windows系统时遇到“msvcp140.dll丢失”的错误提示,通常是因为你的计算机上缺少或损坏了msvcp140.dll文件。msvcp140.dll是Microsoft Visual C Redistributable包的一部分,许多应用程序和游戏需要它来正常运行。以下是几种解决msvcp140.dll丢…...

【RabbitMQ】幂等性、顺序性

幂等性 概述 幂等性是数学和计算机科学中某些运算的性质,他们可以被多次应用,而不会改变初始应用的结果。RabbitMQ的幂等性则是指同一条消息,多次消费,对系统的影响是相同的。 一般消息中间件的消息传输保障分为三个层级&#…...

FFmpeg源码:avio_skip函数分析

AVIOContext结构体和其相关的函数分析: FFmpeg源码:avio_r8、avio_rl16、avio_rl24、avio_rl32、avio_rl64函数分析 FFmpeg源码:read_packet_wrapper、fill_buffer函数分析 FFmpeg源码:avio_read函数分析 FFmpeg源码ÿ…...

Llama 3.1 技术研究报告-6

6 推理 我们研究了两种主要技术,以使 Llama 3 405B 模型的推理⾼效:(1) 流⽔线并⾏和 (2) FP8 量化。我们已经公开发布了我们的 FP8 量化实现。 6.1 流⽔线并⾏ 当使⽤ BF16 数字表⽰模型参数时,Llama 3 405B 不适合在装有 8 个 Nvidia H1…...

更新日志-Python OS

这么久没更新全是因为这段时间的事情很多,只能一点一点的更新代码,不过好在,也是成功更新出来啦! 更新日志(2024/9/29) 代码全文更新,将所有的绝对路径替换为相对路径,这样在各位大…...

Phi-3-mini-128k-instruct部署避坑指南:vLLM加载失败、Chainlit连接超时解决方案

Phi-3-mini-128k-instruct部署避坑指南:vLLM加载失败、Chainlit连接超时解决方案 你是不是也遇到过这种情况:兴致勃勃地部署一个最新的AI模型,结果卡在模型加载或者前端连接上,折腾半天也没搞定?今天咱们就来聊聊Phi-…...

Python从入门到精通day51

前后端分离开发入门:DjangoVue.js 实战 前后端分离是现代 Web 开发的主流模式,核心是将页面渲染、交互逻辑(前端)与数据处理、业务逻辑(后端)解耦,通过标准化的 API 接口实现数据交互。本文以 …...

JUC系列之《CompletableFuture:Java异步编程的终极武器》)

(转)JUC系列之《CompletableFuture:Java异步编程的终极武器》

转自: https://developer.aliyun.com/article/1684158 引言一、为什么需要CompletableFuture?二、核心概念:Promise与异步任务三、创建CompletableFuture四、任务链式编排:thenApply、thenAccept、thenRun五、组合多个Future&…...

建立保持时间详解

建立时间与保持时间保障的详细解释 1. 基本概念与物理本质 建立时间(Setup Time)和保持时间(Hold Time)是数字电路中确保数据正确采样的两个关键时序参数,它们共同构成了寄存器可靠工作的时序窗口。 1.1 定义解析 时序参数 定义 作用 建立时间 (tsu) 时钟有效边沿到达之…...

Token不用就过期了!我花 1 小时开源了个“类纸风” AI 专属 UI——papyrai-ui

一、想法 Token不用就过期了,放着不用简直就是暴殄天物!但每次想随便搭个 AI 小应用跑跑看,都要从头写一遍对话气泡、流式输出、状态指示器……不仅繁琐,还非常劝退。 我就在想:前端五花八门且框架繁多,能…...

CefFlashBrowser技术解析:Flash兼容解决方案深度指南

CefFlashBrowser技术解析:Flash兼容解决方案深度指南 【免费下载链接】CefFlashBrowser Flash浏览器 / Flash Browser 项目地址: https://gitcode.com/gh_mirrors/ce/CefFlashBrowser 问题:Flash技术的现代困境与挑战 随着主流浏览器逐步终止对A…...

Flowise架构剖析:前后端分离设计与微服务集成

Flowise架构剖析:前后端分离设计与微服务集成 1. 开篇:重新认识Flowise的价值 你可能听说过Flowise,也知道它能用拖拽的方式搭建AI工作流。但今天我们要聊点不一样的——不是怎么用,而是为什么它能这么好用。 想象一下…...

从选题到成稿零焦虑:Paperzz 毕业论文初稿写作,让学术创作告别 “卡壳式内耗”

Paperzz-AI官网免费论文查重复率AIGC检测/开题报告/文献综述/论文初稿paperzz - 毕业论文-AIGC论文检测-AI智能降重-ai智能写作https://www.paperzz.cc/dissertation 在毕业论文的漫长写作路上,你是否也陷入过这样的循环:对着空白文档发呆半天写不出开头…...

Uniapp中renderjs解决three.js在APP中的通信阻塞问题

1. 为什么你的Uniapp APP里,three.js动画卡成了PPT? 如果你正在用Uniapp开发APP,并且想在里边搞点酷炫的3D效果,比如展示个产品模型、做个AR预览,那你大概率会想到用three.js。但当你兴冲冲地把Web端跑得飞起的three.j…...

新手零基础入门:借助快马ai编程动手实现第一个待办事项应用

作为一名刚接触编程不久的新手,我最近一直在寻找一种既能动手实践,又不会因为复杂的语法和环境配置而劝退的学习方法。传统的教程要么是枯燥的理论,要么是直接扔给你一堆看不懂的代码,让人望而却步。直到我尝试了用AI来辅助编程&a…...