FPGA 16 ,Verilog中的位宽:深入理解与应用

目录

前言

一. 位宽的基本概念

二. 位宽的定义方法

1. 使用向量变量定义位宽

① 向量类型及位宽指定

② 位宽范围及位索引含义

③ 存储数据与字节数据

2. 使用常量参数定义位宽

3. 使用宏定义位宽

4. 使用[+:][-:]操作符定义位宽

1. 详细解释

+: 操作符

-: 操作符

2. 关键总结

三. 位宽在不同数据类型中的应用

1. reg型数据的位宽

2. wire型数据的位宽

3. integer型数据的位宽

四. 位宽不一致时的处理

五. 位宽相关的注意事项

六. 文章关键字提取解析

1. wire

2. reg

3. parameter

4. `define

5. integer

6. [+:][-:] 操作符

7. module

七. 更多操作

前言

在 Verilog 编程中,位宽是一个非常重要的概念,它直接关系到数据的存储、传输以及电路的功能实现。这里将深入探讨 Verilog 中位宽的相关知识,包括位宽的定义方法、在不同数据类型中的应用、位宽不一致时的处理以及相关的注意事项等等。

一. 位宽的基本概念

在Verilog这一硬件描述语言(HDL)中,位宽指的是数据在Verilog中的表示宽度,以比特(bit)为单位。它决定了一个信号或者变量能够存储的信息量。例如,一个位宽为8的信号可以表示 2⁸ = 256 种不同的状态。

二. 位宽的定义方法

1. 使用向量变量定义位宽

对于向量类型(如 wire 或 reg),可以直接指定位宽的大小。例如:

wire [7:0] data; // 定义一个8位宽的信号,位宽范围是从7到0

// 这里的7是最高有效位(MSB - Most Significant Bit),

// 0是最低有效位(LSB - Least Significant Bit)在这个例子中:

- wire 是数据类型,用于表示模块之间的连线或信号路径。

- [7:0] 是位宽说明符,它指定了该信号由8个连续的二进制位组成,从最高有效位(MSB, bit 7)到最低有效位(LSB, bit 0)。

- data 是变量名,标识了这个8位宽的 wire 类型向量。

因此,data 变量信号可以用来存储8位的数据,比如一个字节的数据。

关键点的总结:

- wire 既是一种数据类型,可以通过指定位宽来表示单个位或向量(多位信号)。当你给 wire 指定位宽时,它就成为一个能够表示多个比特信息的向量。

- [7:0] 是位宽说明符,指定了信号的宽度,表明这个信号有多少个二进制位。

- data 是变量名,标识了一个特定的信号或寄存器,在这个例子中是一个8位宽的 wire 线网型向量。

① 向量类型及位宽指定

Wire 类型

- 概念:

wire类型用于表示模块之间的连线或信号路径,这些信号线用来传输数据。在实际硬件中,可以将wire想象成连接不同组件(如门、触发器等)的物理导线。- 向量定义:当需要传输多位数据时,可以通过定义一个向量来表示一组相关的信号。例如,

wire [7:0] data;定义了一个8位宽的data向量,意味着它能够承载从最低位(bit 0)到最高位(bit 7)共8个二进制位的信息。- 赋值方式:

wire类型的赋值通常通过assign语句或者通过实例化底层元件(如门级原语)来完成。wire必须被驱动,即它的值由其驱动源决定,不能直接在过程块外部进行赋值操作。

Reg 类型

- 概念:

reg类型则更多地用于表示具有存储能力的元素,比如寄存器。它可以保存数据,并且可以在特定的过程中(如always块内)根据一定的逻辑条件更新其值。需要注意的是,reg并不一定代表实际的寄存器;它也可以代表组合逻辑的结果,这取决于它是在时序逻辑还是组合逻辑上下文中被使用。- 向量定义:与

wire类似,reg也支持向量定义,如reg [7:0] counter;表示一个8位宽的寄存器,可以用来保存8位的数据。- 赋值方式:

reg类型的变量只能在过程块(如always块)中进行赋值。在组合逻辑过程中,它会模拟组合逻辑的行为;而在时序逻辑过程中,它会表现出存储特性,通常是在时钟沿或特定事件发生时更新其值。

当我们要表示更复杂、能承载多位数据的信号时,就会将它们定义成向量类型,通过指定 [位宽范围] 的方式来明确其可以容纳的二进制位数。以 wire[7:0] data; 为例,这里 [7:0] 就是在指定位宽,表明 data 信号是一个位宽为 8 位的向量。

② 位宽范围及位索引含义

位宽范围的表示方式:在 wire[7:0] data; 里,7:0 这种写法定义了位宽范围,其中 7 代表最高有效位(MSB - Most Significant Bit),而 0 代表最低有效位(LSB - Least Significant Bit)。位宽范围的表示是从高位到低位依次递减排列的,这样的规定符合我们在数字电路以及计算机存储中对二进制数据表示的习惯。

位索引的作用:每个位都有对应的索引,用于精准地访问和操作向量信号中的某一位或者某几位。比如,data[7] 就专门用于访问 data 信号的最高有效位(也就是第 7 位),data[0] 则是用于访问其最低有效位。这种通过位索引来操作具体位的方式,在进行各种逻辑设计时非常有用,比如在进行数据的位操作、掩码处理、条件判断等情况中都会频繁用到。

例如,若想判断 data 信号的最高有效位是否为 1,可以写成如下的条件判断语句:

if (data[7] == 1)

// 执行相应的操作,比如进行一些后续的逻辑处理等

③ 存储数据与字节数据

存储数据的范围:由于

data信号被定义为 8 位宽,根据二进制数的表示原理,它一共可以表示 2⁸ = 256 种不同的状态,对应的十进制数值范围是从 0(即二进制表示为00000000)到 255(即二进制表示为11111111)。这意味着这个信号能够存储和传递处于这个范围内的任何数值,这体现了它作为一个具有特定位宽的向量信号所具备的存储能力。与字节数据的联系:在计算机领域中,一个字节(Byte)的标准定义就是由 8 个二进制位组成的基本存储单元。所以,像

data这样位宽为 8 位的信号,正好可以完整地存储一个字节的数据。这种对应关系在实际的数字电路设计以及计算机系统的数据交互等诸多场景中都有着广泛的应用。

例如,在一个简单的微处理器与外部存储器的数据传输过程中,如果每次传输是以字节为单位进行的,那么就可以利用像 data 这样的 8 位宽信号作为数据总线,来承载每一次传输的字节数据,实现数据在不同组件之间的有效传递。再比如,在一些简单的数字信号处理模块中,输入的数据如果是以字节格式进行编码的,同样可以用 data 信号接收并暂存这些字节数据,进而进行后续的诸如解码、运算等处理操作。

总之,通过 wire[7:0] data; 这样简洁的语句定义一个具有特定位宽且明确位索引的向量信号,我们可以在 Verilog 语言环境下方便灵活地进行与 8 位数据(即字节数据)相关的各种存储、传输以及逻辑处理操作,这为构建更为复杂的数字电路系统和逻辑功能模块奠定了坚实的基础。

2. 使用常量参数定义位宽

通过定义参数(parameter模块级常量 或 localparam局部常量)来灵活地设置位宽是一种推荐的做法。这种方法不仅提高了代码的可维护性,而且使得设计更加模块化和易于调试。当需要修改位宽时,只需要更改参数的值,而无需在代码中每个使用该位宽的地方进行修改。

// 定义一个参数 WIDTH,默认为8

parameter WIDTH = 8;// 使用参数来定义位宽

wire [WIDTH-1:0] data; // 定义了一个 WIDTH 位宽的 wire 向量如果之后需要将位宽修改为16,只需要修改 parameter WIDTH = 16; 即可,所有依赖于 WIDTH 的定义会自动更新,而不需要在所有使用到 data 位宽的地方进行手动修改。

进一步的优化:

如果你希望在整个项目中保持一致的命名规范,并且可能需要在多个模块中使用相同的位宽定义,可以考虑将这些参数集中定义在一个单独的文件中,然后通过 include 指令引入。

// 在 parameters.v 文件中定义公共参数

parameter DATA_WIDTH = 8;

parameter ADDR_WIDTH = 32;// 在其他 Verilog 文件中引入参数

`include "parameters.v"

// 下面使用上面提到的,parameter 和 localparam 都用于定义常量,但它们之间有一些重要的区别。理解这些差异可以帮助我们更有效地使用它们,并根据具体需求选择合适的类型。

parameter:模块级常量

定义:parameter 是模块级的常量,可以在模块内部或外部(其他模块)引用。

作用域:在模块内部定义时,parameter 的作用域是整个模块。

localparam:局部常量

定义:localparam 类似于 parameter,但它只能在定义它的模块内部使用,不能被外部模块实例化时覆盖。

作用域:localparam 的作用域严格限制在定义它的模块内部。

3. 使用宏定义位宽

在Verilog中,宏定义(通过反引号 ` 和 define 指令)可以用于定义常量值,如位宽。这提供了一种简单的方法来在整个设计中一致地应用某个特定值。例如:

`define WIDTH 8 // 定义一个宏

wire[`WIDTH - 1:0] data; // 使用宏来定义位宽在这个例子中,WIDTH 是一个宏,其值为8。宏定义在预处理阶段进行简单的文本替换,因此 wire [WIDTH-1:0] data;实际上会被替换为wire [8-1:0] data;,即 wire [7:0] data;`。

但是需要注意的是,在 Verilog 中宏定义在预处理时进行简单的文本替换,可能会带来一些潜在的问题,特别是在涉及到复杂的位宽计算或者嵌套使用宏时。例如,当定义位宽为1时可能导致的错误,在模块中使用 define定义相关参数时,预处理时宏展开可能导致意外行为,所以在使用 define时要谨慎处理位宽计算,以避免设计错误url。

为了避免上述问题,建议遵循以下最佳实践:使用参数代替宏,对于位宽等常量值,推荐使用 parameter 或 localparam 来代替宏定义。这些关键字允许你在模块内部定义常量,并且可以在仿真和综合工具中更好地进行优化和调试。也就是,我们上面第二项记录的,2. 使用常量参数定义位宽。

4. 使用[+:][-:]操作符定义位宽

在Verilog语法中,+: 和 -: 操作符主要用于进行位宽度选择(bit-width selection)。这些操作符允许你以一种更灵活的方式,从向量中提取子集,特别是在处理动态或参数化位宽时非常有用。语法如下:

value[base_expression +: width_expression];

value[base_expression -: width_expression];

// base_expression:表示起始的比特位置。

// width_expression:表示要选择的位宽。1. 详细解释

+: 操作符

+: 操作符从 base_expression 开始,向高位方向选择指定宽度的比特。具体来说:

- value[base_expression +: width_expression] 表示从 base_expression 开始,向高位选择 width_expression 个比特。

- 这种选择是连续的,并且总是从低位到高位进行。

代码示例

reg [15:0] big_value;// 从第0位开始,选择8个比特,等价于 big_value[7:0]

big_value[0 +: 8];// 从第8位开始,选择8个比特,等价于 big_value[15:8]

big_value[8 +: 8];-: 操作符

-: 操作符从 base_expression 开始,向低位方向选择指定宽度的比特。具体来说:

- value[base_expression -: width_expression] 表示从 base_expression 开始,向低位选择 width_expression 个比特。

- 这种选择也是连续的,并且总是从高位到低位进行。

代码示例

reg [15:0] big_value;// 从第7位开始,选择8个比特,等价于 big_value[7:0]

big_value[7 -: 8];// 从第15位开始,选择8个比特,等价于 big_value[15:8]

big_value[15 -: 8];2. 关键总结

+:操作符:向高位选择比特。适用于从低地址到高地址的选择。-:操作符:向低位选择比特。适用于从高地址到低地址的选择。

这些操作符 +: 和 -: 操作符的一个重要特性是它们允许动态地选择位宽。这意味着你可以根据变量或参数来决定选择哪些比特,这在某些设计中非常有用。

三. 位宽在不同数据类型中的应用

1. reg型数据的位宽

reg类型用于表示寄存器类型的数据,可以存储一个值,直到被新的值覆盖。位宽的定义方式和前面提到的一样。例如:

reg[3:0] counter; // 定义一个4位宽的寄存器,可用于计数,范围是0到15在这个例子中,counter可以用来实现一个简单的4位计数器。

2. wire型数据的位宽

wire类型用于表示连线,它的值由驱动它的信号决定。同样可以定义位宽,例如:

wire[15:0] address; // 定义一个15位宽的地址线这里的address可以用于表示一个16位的地址信号,用于在电路中进行地址传输。

3. integer型数据的位宽

在Verilog中,integer 默认是32位的有符号数。虽然不能像 reg 和 wire 那样直接指定自定义的位宽,但在进行运算时需要考虑其32位的位宽特性。例如:

integer num;

// num在参与运算时,是按照32位有符号数进行处理的四. 位宽不一致时的处理

- 在Verilog和SystemVerilog中,当不同位宽信号进行运算时可能导致预期结果错误。例如,一个8位的信号和一个16位的信号相加。

- 可以通过扩展位宽的方式来解决。例如,将8位信号扩展为16位后再进行相加操作。

- 也可以通过类型转换等方式确保运算的正确性。在实际编程中,需要根据具体的设计需求和电路功能来选择合适的处理方法。

五. 位宽相关的注意事项

- 在定义位宽时,要确保位宽的范围定义正确,特别是在使用[MSB:LSB]这种方式时,MSB和LSB都需要是常数而不能是变量(除了使用[+:][-:]操作符的情况)。

- 当使用参数或者宏定义位宽时,要注意它们的作用范围和可能带来的副作用。例如宏定义的文本替换特性可能导致意外的结果,而参数在模块实例化时的传递也需要正确处理。

- 在进行位宽相关的调试时,如果发现结果不符合预期,首先要检查位宽的定义和运算中涉及到的位宽处理是否正确。例如,是否存在位宽不匹配导致的数据截断或者错误的扩展。

六. 文章关键字提取解析

我们都知道,在Verilog中,关键字是该语言的重要组成部分,用于定义数据类型、控制结构和其它语言特性。虽然,上面和之前都有一些关键字的解析和应用,这里再来记录一下,多多益善。以下是以上博客文章中提取到的一些Verilog关键字,解析和小结,并附有示例代码和注释。

1. wire

wire关键字用来声明连线(net)类型的信号,它表示一个物理连接或逻辑门之间的信号线。wire的值由驱动它的源来决定,不能直接赋值。

// 定义一个8位宽的wire型变量data,它可以代表一个8位的数据总线

wire [7:0] data;2. reg

reg关键字用于声明寄存器类型的变量,可以保存值直到被新的值覆盖。reg类型常用于存储状态信息,如计数器、寄存器文件等。

// 定义一个4位宽的reg型变量counter,可用于实现计数功能

reg [3:0] counter;3. parameter

parameter关键字用于定义参数,即常量。参数可以在模块内部或跨多个模块共享,提供了一种灵活的方式去改变设计中的数值。

// 定义一个名为WIDTH的参数,默认值为8

parameter WIDTH = 8;// 使用参数WIDTH来定义一个宽度可变的wire型变量data

wire [WIDTH-1:0] data;4. `define

`define 是一种预处理指令,用来创建宏定义。它会在编译前进行简单的文本替换。由于它是基于文本替换的,因此需要小心使用以避免潜在的问题。

// 定义一个名为WIDTH的宏,默认值为8

`define WIDTH 8// 使用宏定义WIDTH来定义一个宽度可变的wire型变量data

wire [`WIDTH-1:0] data;5. integer

integer关键字用于声明整数类型的变量。默认情况下,integer是32位宽的有符号数。

// 声明一个integer类型的变量num,它默认是32位宽的有符号整数

integer num;6. [+:][-:] 操作符

[+:][-:]操作符允许动态选择位段,其中+:是从低位开始向上取指定数量的位,而-:则是从高位向下取指定数量的位。

reg [15:0] big_value; // 定义一个16位宽的寄存器big_value// 使用+:操作符选取big_value的低8位

assign low_byte = big_value[0 +: 8]; // 等价于big_value[7:0]// 使用-:操作符选取big_value的高8位

assign high_byte = big_value[15 -: 8]; // 等价于big_value[15:8]7. module

module关键字用于定义一个模块,它是Verilog设计的基本单元,包含了输入输出端口和内部逻辑。endmodule结束模块。

module example (input wire clk, // 时钟信号输入input wire rst_n, // 异步复位信号输入input wire [7:0] din,// 8位数据输入output reg [7:0] dout// 8位数据输出

);// 模块内部逻辑...

endmodule以上是对博客文章中涉及的关键Verilog关键字的解析。每个关键字都有其特定的作用范围和用法,在实际编程中正确运用这些关键字对于编写高效且无误的Verilog代码至关重要。

七. 更多操作

之前文章中,有提到过关于 Verilog 中的关键字解析,请看

FPGA 9 ,Verilog 中的关键字和基数![]() https://blog.csdn.net/weixin_65793170/article/details/141625021

https://blog.csdn.net/weixin_65793170/article/details/141625021

完整FPGA系列,请看

FPGA系列,文章目录![]() https://blog.csdn.net/weixin_65793170/article/details/144185217?spm=1001.2014.3001.5501

https://blog.csdn.net/weixin_65793170/article/details/144185217?spm=1001.2014.3001.5501

相关文章:

FPGA 16 ,Verilog中的位宽:深入理解与应用

目录 前言 一. 位宽的基本概念 二. 位宽的定义方法 1. 使用向量变量定义位宽 ① 向量类型及位宽指定 ② 位宽范围及位索引含义 ③ 存储数据与字节数据 2. 使用常量参数定义位宽 3. 使用宏定义位宽 4. 使用[:][-:]操作符定义位宽 1. 详细解释 : 操作符 -: 操作符 …...

vue-生命周期

Vue 的生命周期是指 Vue 实例从创建到销毁期间经历的一系列阶段。每个阶段都有相应的钩子函数(Lifecycle Hooks),允许开发者在这些关键时刻执行自定义逻辑。 一、钩子函数 1. 创建阶段 beforeCreate 在实例初始化之后,数据观测 …...

浅谈Kubernetes(K8s)之RC控制器与RS控制器

1.RC控制器 1.1RC概述 Replication Controller 控制器会持续监控正在运行的Pod列表,并保证相应类型的Pod的数量与期望相符合,如果Pod数量过少,它会根据Pod模板创建新的副本,反之则会删除多余副本。通过RC可实现了应用服务的高可用…...

本题要求采用选择法排序,将给定的n个整数从大到小排序后输出。

#include <stdio.h> #define MAXN 10 int main() { int i, index, k, n, temp; int a[MAXN]; scanf("%d", &n); for (i 0; i < n; i) { scanf("%d", &a[i]); } // 外层循环控制排序轮数,一共需要n-1轮 for (k 0; k < n…...

Linux: glibc: 频繁调用new/delete会不会导致内存的碎片

最近同事问了一个问题:频繁调用new/delete会不会导致内存的碎片。 下面是我想到的一些回答, glibc的内存处理机制,是在释放的时候会自动将小块内存整合成大块内存,为接下来满足大块的需求的可能。而且程序也不是一直占着内存不释放(如果是一直不释放,要考虑是不是内存泄漏…...

量子变分算法---损失函数

引子 关于损失函数,我们知道在强化学习中,会有一个函数,用来表示模型每一次行为的分数,通过最大化得分,建立一个正反馈机制,若模型为最优则加分最多,若决策不佳则加很少分或者扣分。而在神经网络…...

计算机的性能评估

目录 计算机的性能评估 确定性能指标 考虑通讯因素 考虑机器过热因素 综合评估模型 动态评估与调整 计算机的性能评估 在分布式计算机系统中,综合考虑各种因素来评估性能是一个复杂但重要的问题。以下是一种可能的方法来综合考虑评估分布式计算机性能,动态地考虑实际情…...

大数据之国产数据库_OceanBase数据库002_在centos7.9上_安装部署OceanBase001_踩坑指南_亲测可用

部署前最好看一下,部署前的要求, 主要是系统 以及系统内核版本,还有比如清理一下缓存等,按照做一做. 这些都是前置条件. 清一下缓存. 也就是说官网给的前置的条件,都要根据说明去执行一遍,如果不执行可能后面安装会报错. 然后用户最好也去创建一个用户. 注意前置...

【ETCD】【源码阅读】深入解析 EtcdServer.run 函数

EtcdServer.run 是 etcd 的核心运行逻辑之一,负责管理 Raft 状态机的应用、事件调度以及集群的核心操作。本文将逐步从源码层面分析 run 函数的逻辑,帮助读者理解其内部机制和设计思想。 函数签名与关键职责 func (s *EtcdServer) run() {... }关键职责…...

springboot/ssm校内订餐系统Java代码web项目美食外卖点餐配送源码

springboot/ssm校内订餐系统Java代码web项目美食外卖点餐配送源码 基于springboot(可改ssm)vue项目 开发语言:Java 框架:springboot/可改ssm vue JDK版本:JDK1.8(或11) 服务器:tomcat 数据库ÿ…...

floodfill算法

目录 什么是floodfill算法 题目一——733. 图像渲染 - 力扣(LeetCode) 题目二——200. 岛屿数量 - 力扣(LeetCode) 题目三——695. 岛屿的最大面积 - 力扣(LeetCode) 题目四—— 130. 被围绕的区域 …...

【JAVA】六亮增加贴

James Gosling(詹姆斯.高斯林) Java 语言源于 1991 年 4 月,Sun 公司 James Gosling博士 领导的绿色计划(Green Project) 开始启动,此计划最初的目标是开发一种能够在各种消费性电子产品(如机顶盒、冰箱、收音机等)上运行的程序…...

git提交时出现merge branch main of xxx

git提交时出现merge branch main of xxx 原因: 1、同事commit了一个修改A,push到remote 2、我把这个修改直接pull了下来(pull是fetchmerge的操作,自动合并到本地workspace) 3、同事因为后续的commit有冲突,…...

lstm 输入数据的形状是怎么样的,他有两种输入方式,通过参数 batch_first来设置 默认是False

lstm 输入数据的形状是怎么样的,他有两种输入方式,通过参数 batch_first来设置 默认是False 当batch_firstFalse时,LSTM输入的数据形状通常是一个三维张量,其维度顺序为[sequence_length, batch_size, input_size]。下面是对这些维…...

Apache Doris 数据类型

Apache Doris 已支持的数据类型列表如下: 数值类型 类型名存储空间(字节)描述BOOLEAN1布尔值,0 代表 false,1 代表 true。TINYINT1有符号整数,范围 [-128, 127]。SMALLINT2有符号整数,范围 …...

编译问题 fatal error: rpc/rpc.h: No such file or directory

在编译一些第三方软件的时候,会经常遇到一些文件识别不到的问题,这里整理下做个归总。 目前可能的原因有(排序分先后): 文件不存在;文件存在但路径识别不了;…… 这次以常见的编译lmbench测试…...

linux 安装composer

下载composer curl -sS https://getcomposer.org/installer | php下载后设置环境变量,直接通过命令composer -v mv composer.phar /usr/local/bin/composer查看版本看是否安装成功 composer -v...

数据库公共字段自动填充的三种实现方案

背景介绍 在实际项目开发中,我们经常需要处理一些公共字段的自动填充,比如: createTime (创建时间)updateTime (更新时间)createUser (创建人)updateUser (更新人) 这些字段在每个表中都存在,如果每次都手动设置会很麻烦。下面介绍三种常用的解决方案。 方案一:M…...

《MySQL 入门:数据库世界的第一扇门》

一、MySQL 简介 MySQL 是一种开源的关系型数据库管理系统,在数据库领域占据着重要地位。它以其高效查询、高安全性、低成本和扩展性著称,广泛应用于网站、企业级应用、数据分析等领域。 MySQL 具有诸多优点。首先,它成本低,作为…...

Qt之第三方库QCustomPlot使用(二)

Qt开发 系列文章 - qcustomplot(二) 目录 前言 一、Qt开源库 二、QCustomPlot 1.qcustomplot介绍 2.qcustomplot下载 3.qcustomplot移植 4.修改项目文件.pro 5.提升QWidget类 三、技巧讲解 1.拖动缩放功能 2.等待更新 总结 前言 Qt第三方…...

Python爬虫实战:研究MechanicalSoup库相关技术

一、MechanicalSoup 库概述 1.1 库简介 MechanicalSoup 是一个 Python 库,专为自动化交互网站而设计。它结合了 requests 的 HTTP 请求能力和 BeautifulSoup 的 HTML 解析能力,提供了直观的 API,让我们可以像人类用户一样浏览网页、填写表单和提交请求。 1.2 主要功能特点…...

AI-调查研究-01-正念冥想有用吗?对健康的影响及科学指南

点一下关注吧!!!非常感谢!!持续更新!!! 🚀 AI篇持续更新中!(长期更新) 目前2025年06月05日更新到: AI炼丹日志-28 - Aud…...

使用VSCode开发Django指南

使用VSCode开发Django指南 一、概述 Django 是一个高级 Python 框架,专为快速、安全和可扩展的 Web 开发而设计。Django 包含对 URL 路由、页面模板和数据处理的丰富支持。 本文将创建一个简单的 Django 应用,其中包含三个使用通用基本模板的页面。在此…...

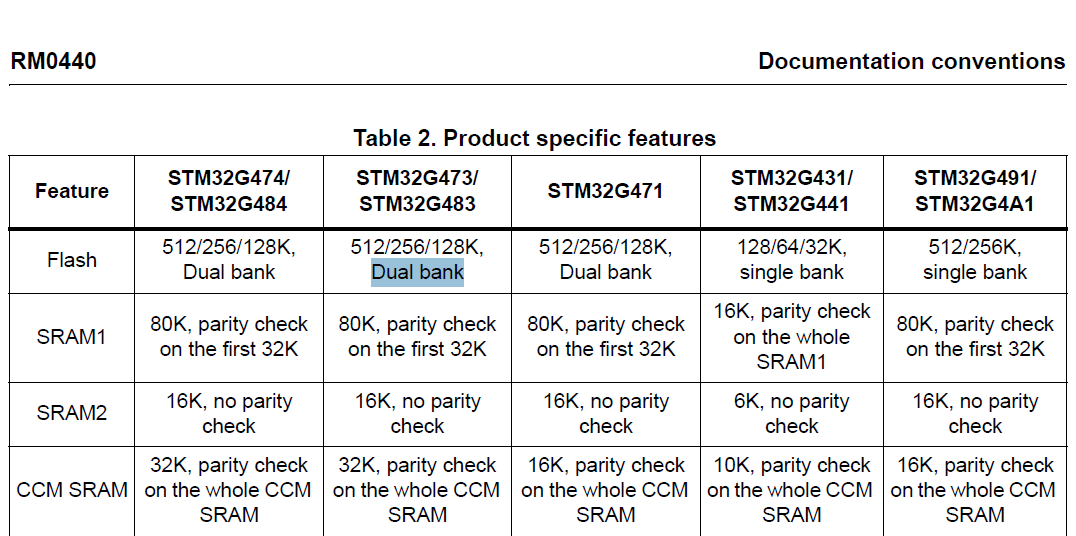

stm32G473的flash模式是单bank还是双bank?

今天突然有人stm32G473的flash模式是单bank还是双bank?由于时间太久,我真忘记了。搜搜发现,还真有人和我一样。见下面的链接:https://shequ.stmicroelectronics.cn/forum.php?modviewthread&tid644563 根据STM32G4系列参考手…...

简易版抽奖活动的设计技术方案

1.前言 本技术方案旨在设计一套完整且可靠的抽奖活动逻辑,确保抽奖活动能够公平、公正、公开地进行,同时满足高并发访问、数据安全存储与高效处理等需求,为用户提供流畅的抽奖体验,助力业务顺利开展。本方案将涵盖抽奖活动的整体架构设计、核心流程逻辑、关键功能实现以及…...

Oracle查询表空间大小

1 查询数据库中所有的表空间以及表空间所占空间的大小 SELECTtablespace_name,sum( bytes ) / 1024 / 1024 FROMdba_data_files GROUP BYtablespace_name; 2 Oracle查询表空间大小及每个表所占空间的大小 SELECTtablespace_name,file_id,file_name,round( bytes / ( 1024 …...

QMC5883L的驱动

简介 本篇文章的代码已经上传到了github上面,开源代码 作为一个电子罗盘模块,我们可以通过I2C从中获取偏航角yaw,相对于六轴陀螺仪的yaw,qmc5883l几乎不会零飘并且成本较低。 参考资料 QMC5883L磁场传感器驱动 QMC5883L磁力计…...

linux 错误码总结

1,错误码的概念与作用 在Linux系统中,错误码是系统调用或库函数在执行失败时返回的特定数值,用于指示具体的错误类型。这些错误码通过全局变量errno来存储和传递,errno由操作系统维护,保存最近一次发生的错误信息。值得注意的是,errno的值在每次系统调用或函数调用失败时…...

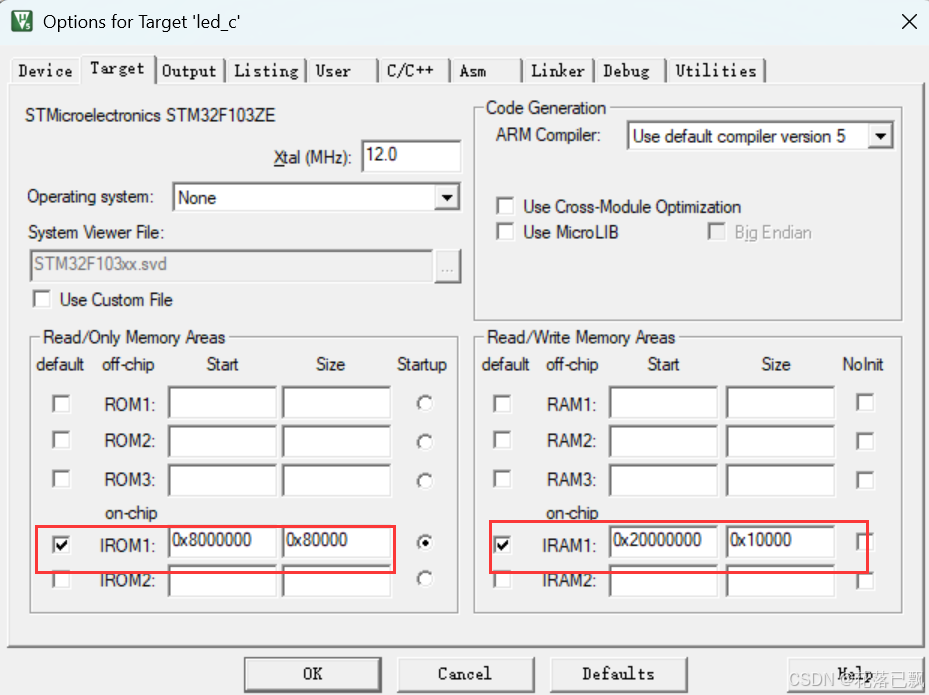

Keil 中设置 STM32 Flash 和 RAM 地址详解

文章目录 Keil 中设置 STM32 Flash 和 RAM 地址详解一、Flash 和 RAM 配置界面(Target 选项卡)1. IROM1(用于配置 Flash)2. IRAM1(用于配置 RAM)二、链接器设置界面(Linker 选项卡)1. 勾选“Use Memory Layout from Target Dialog”2. 查看链接器参数(如果没有勾选上面…...

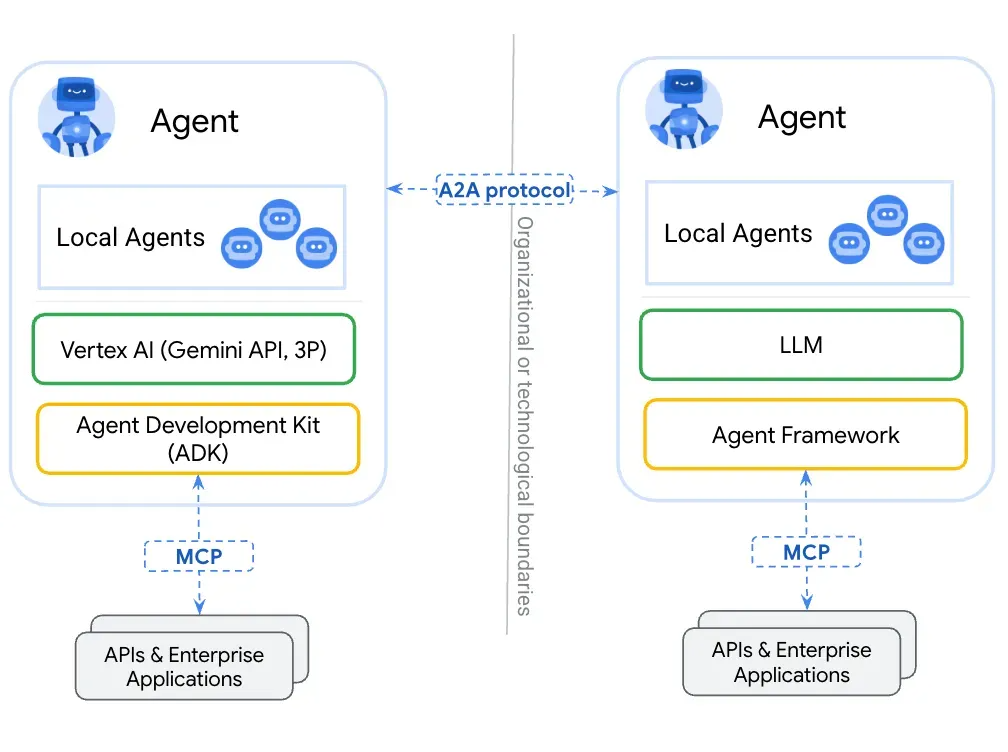

第一篇:Agent2Agent (A2A) 协议——协作式人工智能的黎明

AI 领域的快速发展正在催生一个新时代,智能代理(agents)不再是孤立的个体,而是能够像一个数字团队一样协作。然而,当前 AI 生态系统的碎片化阻碍了这一愿景的实现,导致了“AI 巴别塔问题”——不同代理之间…...