实验六 项目二 简易信号发生器的设计与实现 (HEU)

声明:代码部分使用了AI工具

实验六 综合考核

Quartus 18.0

FPGA 5CSXFC6D6F31C6N

1. 实验项目

要求利用硬件描述语言Verilog(或VHDL)、图形描述方式、IP核,结合数字系统设计方法,在Quartus开发环境下,2人1组本班内自由组队,从下列3个实验项目中任选1项(3选1)进行实现。因材料限制,每个项目每个班级最多6组选择,第一次实验时填表选定,不得变更。

实验分为2部分内容,基础实验12学时,使用FPGA开发板实现。拓展实验需要搭建外围电路与开发板连接实现相关功能,可利用课余时间进行开放实验,第二次实验时进行集中实验验收(4学时)。

注意事项:需自带计算机(安装有Quartus、multisim等软件);还需带烙铁、焊锡焊接工具和万用表等,实验室提供相关元器件。

| 实验项目名称 | 基础实验内容(12学时) | 拓展实验内容 (开放实验+4学时验收实验) |

| 项目1:简易频率计的设计与实现 | 利用硬件描述语言或图形描述方式,结合数字电路设计方法,实现以下功能: 1.对1kHz-1MHz方波信号的频率测量功能,进行quartus/modelsim仿真验证;(60分) 2.使用实验室提供开发板完成对1kHz-1MHz方波信号的频率测量功能,控制数码管实时显示测量结果。(20分) 3.可通过开发板上的USB-Uart接口,将测量频率结果传送至计算机上的串口调试助手显示。(20分) | 在基础实验内容的基础上,使用元器件搭建外围电路,经multisim/proteus仿真验证后,制作实物电路与开发板连接,实现以下功能: 1.可对幅度0.1V-4V,频率1kHz-10kHz范围的正弦信号进行频率测量;(60分) 2.对输入正弦信号同时进行幅度和频率测量,并将测量结果实时显示并发送至计算机。(40分) |

| 项目2:简易信号发生器的设计与实现 | 利用硬件描述语言或图形描述方式,结合数字电路设计方法,实现以下功能: 1.产生1kHz-1MHz范围内的方波信号,信号频率可由按键调节,步进间隔1kHz,进行quartus/modelsim仿真验证;(60分) 2.使用实验室提供开发板输出1kHz-1MHz方波信号,信号频率可由按键调节,控制数码管实时显示当前频率值。(20分) 3.实现用计算机调节开发板输出方波信号频率的功能。(20分) | 在基础实验内容的基础上,使用元器件搭建外围电路,经multisim/proteus仿真验证后,制作实物电路与开发板连接,实现以下功能: 1.产生1kHz-10kHz范围内的三角波信号,频率可由按键和计算机进行调节;(60分) 2.产生7kHz-10kHz范围内的正弦波信号,频率可由按键和计算机进行调节。(40分) |

| 项目3:电压电流表的设计与实现 | 利用硬件描述语言或图形描述方式,结合数字电路设计方法,实现以下功能: 1.使用实验室提供开发板对介于0-4V之间的直流电压值进行测量,分辨率1mV,测量结果在数码管上显示,每秒至少刷新1次;(60分) 2.对两路0-4V之间的直流电压值同时进行测量,测量结果交替显示。(20分) 3.可通过开发板上的USB-Uart接口,将测量电压结果传送至计算机上的串口调试助手显示。(20分) | 在基础实验内容的基础上,使用元器件搭建外围电路,经multisim/proteus仿真验证后,制作实物电路与开发板连接,实现以下功能: 1.对直流电源输出到负载上的电压和电流进行测量,并将测量结果实时显示并发送至计算机;(60分) 2.使用电压电流测量结果计算负载实时功率和耗电量,将计算结果发送至计算机。(40分) |

2. 实验要求

(1)每人对于所选择完成的实验项目,通过查阅资料理解实验原理,设计实验方案,并将实验原理和方案写于实验报告中。

(2)按照实验要求,完成电路设计、通过编译无误后,完成测试代码编写,实现功能仿真,记录仿真波形并写于实验报告。

(3)编译的输出文件下载到FPGA电路板,完成指定功能,进行拍照和结果分析,写入实验报告。

(4)基础实验内容完成后由老师验收并记录实验成绩。

(5)设计外围电路完成相关功能,使用Multisim、Proteus对外围电路功能进行验证,截图写入实验报告。

(6)利用开放实验时间搭建外围电路实物,进行测试验证,对测试结果进行拍照和分析,写入实验报告。

(7)集中验收实验时经老师检查电路无误后,将搭建电路与FPGA开发板连接,进行测试。测试完成后由老师验收并记录实验成绩,认真撰写实验报告,按时上交实验报告。

(8)实验六实验报告使用智慧树平台网上填写提交,每组仅需提交1份,按自己选择题目提交相应作业,截止时间为第二次实验当晚23:59前。建议边做实验边拍照记录,减少实验报告撰写时间。

3. 实验器材清单

(1)FPGA开发板,有DE1SOC和DE10-Standard这2种,随机领用,看准自己开发板型号,查找相关资料。

(2)直流电源、信号源、示波器、万用表(需自备)。

(3)直插1/4W电阻

阻值:10Ω, 22Ω, 47Ω, 100Ω , 150Ω , 200Ω , 220Ω , 270Ω , 330Ω, 470Ω, 510Ω, 680Ω, 1kΩ, 2kΩ, 2.2kΩ, 3.3kΩ, 4.7kΩ, 5.1kΩ, 6.8kΩ, 10kΩ, 20kΩ, 47kΩ, 51kΩ, 68kΩ, 100kΩ, 220kΩ, 300kΩ, 470kΩ, 680kΩ, 1MΩ

(4)瓷片电容

容值:2pF, 3pF, 5pF, 10pF, 15pF, 22pF, 30pF, 47pF, 68pF, 75pF, 82pF, 100pF, 150pF, 220pF, 330pF, 470pF, 680pF, 1npF, 1.5nF, 2.2nF, 3.3nF, 4.7nF, 6.8nF, 10nF, 15nF, 22nF, 47nF, 68nF, 100nF

3. 实验器材清单

(5)电解电容(焊接务必注意正负极)

50V0.22uF, 50V0.47uF, 50V1uF, 50V2.2uF, 50V4.7uF, 25V10uF, 25V22uF, 16V33uF, 16V47uF, 16V100uF, 10V220uF, 10V470uF

(6)二极管

1N4148, 1N4007, 1N5819, 1N5399, FR107, FR207, 1N5408, 1N5822

(7)运算放大器LM324及芯片座

(8)比较器LM393及芯片座

(9)USB转TTL转换器(计算机和开发板通信用,用后需归还)

驱动及安装说明: https://zhuanlan.zhihu.com/p/370245114

(10)万用板5*7cm单面(每组一块), 杜邦线。

声明:我们选择的是项目二;隔得时间太久,有的照片找不着了;分频器部分,由于采用了除法,受限于有限字长,得到的实际频率有一定误差,虽然人为进行了修正,但在高频时仍比较明显,可以考虑其他算法改进;正弦波部分的带通滤波器没有问题;但三角波部分的积分器需要改进,现在的问题是频率较高时幅值衰减较明显。

考核内容

1.1.【问答题】(10分)

产生1kHz-1MHz范围内的方波信号,信号频率可由按键调节,步进间隔1kHz,进行

quartus,/modelsim仿真验证;简述该设计的主要功能和原理?

主要功能:

可以通过按钮调节输出1kHz-1MHz的方波、7kHz-10kHz正弦波、1kHz-10kHz三角波(步进均为1kHz);可以通过串口从电脑上控制输出1kHz-1MHz的方波、7kHz-10kHz正弦波、1kHz-10kHz三角波(步进均为1kHz)。

不过,串口控制功能只能输入十六进制数,所以在测试时需要先把想输入的十进制数转换为十六进制,允许输入范围为0x0001~0x03E8(注意,1MHz即为1000kHz,我们这里使用三位数码管,故显示为000)。比如,我想通过串口控制输出726kHz方波,只需在电脑串口助手上输入02D6再发送即可。

原理:时钟脉冲信号经过可调分频器后得到可控频率的矩形脉冲信号,矩形脉冲信号分别经过滤波器和积分器后可得到正弦波和三角波。编写一个调节模块用以传递输入的指令,并联系输入部分和输出部分。

1.2.【问答题】(5分)

上传设计框图、源程序等截图:

1.3.【问答题】(5分)

上传仿真结果截图,描述图中结果:

引脚分配:

quartus/modelsim联合仿真:

1.4.【问答题】(5分)

使用实验室提供开发板输出1kHz-1MHz方波信号,信号频率可由按键调节,控制数码管实时显示

当前频率值。上传输出最低频率方波的照片,照片中需包含设置频率和示波器测量波形。

实验六项目二按钮演示

实验六项目二串口演示

1.5.【问答题】(5分)

上传输出最高频率方波的照片,照片中需包含设置频率和示波器测量波形。

找不着照片了

1.6.【问答题】(5分)

你最终实现了多少范围内的频率输出功能?误差是多少?

范围达到了题目要求,这里误差不是我算的,不知道。

1.7.【问答题】(10分)

在基础实验内容的基础上,使用元器件搭建外围电路,简述外围电路原理?

带通滤波器设计:

1.8.【问答题】(10分)

上传外围电路图及仿真测试结果,并说明仿真情况

带通滤波器:

积分器:

1.9.【问答题】(10分)

制作实物电路与开发板连接,实现以下功能:

产生1kHz-10kHz范围内的三角波信号,频率可由按键和计算机进行调节;上传最低频率和最高频

率时输出三角波的测量结果照片。

1.10.【问答题】(10分)

产生7kHz-10kHz范围内的正弦波信号,频率可由按键和计算机进行调节。上传最低频率和最高频

率时输出正弦波的测量结果照片。

2.【问答题】(10分)

上传搭建的外围电路与开发板连接的实物照片。

3.【问答题】(10分)

你在实验调试过程中出现了哪些问题?如何解决的?有何实验心得体会?

(1)有时会出现不明原因的报错,报错中会出现“License”相关字眼,这是在程序运行途中发生了破解失效,需要妥善保存工程后再一次进行破解。

(2)在仿真过程中,程序选择的文件保存路径经常会出现问题,“.vwf”文件与“.vt"文件可能会被写入不同路径,这会导致报错并且仿真错误。摸索出来的解决方法是在可能的路径中分别复制一份对应文件。

(3)可以通过给FPGA断电后再上电来清除上一次下载到FPGA中的程序。

(4)遇到报错,可将报错信息输送给一些大语言模型,往往会得到不错的改进建议,适时适量使用AI工具并非坏事。

附录(代码及资源)

代码

dds.v

//主程序

module dds(input wire clk, // FPGA主时钟input wire rst_n, // 复位信号input wire button_up, // 增加频率按钮input wire button_down, // 减少频率按钮input wire uart_rx, // 计算机控制的UART输入input wire select_control,// 选择控制信号:0为按键控制,1为UART控制output wire wave_out, // 输出方波信号output wire [6:0] hex0, // 数码管显示output wire [6:0] hex1,output wire [6:0] hex2

);wire [19:0] freq_from_button; // 来自按键控制的频率选择wire [19:0] freq_from_uart; // 来自UART控制的频率选择reg [19:0] freq_sel; // 实际选择的频率// 按键控制模块button_control btn_ctrl (.clk(clk),.rst_n(rst_n),.button_up(button_up),.button_down(button_down),.freq_sel(freq_from_button));// 方波信号生成模块clock_divider clk_div (.clk(clk),.rst_n(rst_n),.freq_sel(freq_sel),.wave_out(wave_out));// 数码管显示模块seven_segment_display display (.clk(clk),.rst_n(rst_n),.freq_sel(freq_sel),.hex0(hex0),.hex1(hex1),.hex2(hex2));// 计算机调节模块uart_control uart_ctrl (.clk(clk),.rst_n(rst_n),.uart_rx(uart_rx),.freq_sel(freq_from_uart));// 多路选择器always @(*) beginif (select_control) freq_sel = freq_from_uart; // 如果select_control为1,用UART控制频率else freq_sel = freq_from_button; // 否则用按键控制频率endendmodule

clock_divider.v

// 时钟分频器模块

module clock_divider(input wire clk, // FPGA主时钟,例如50MHzinput wire rst_n, // 复位信号input wire [31:0] freq_sel, // 选择的频率(步进为1kHz)output reg wave_out // 输出方波信号

);reg [31:0] counter;reg [31:0] threshold;always @(posedge clk or negedge rst_n) beginthreshold = 85899*freq_sel;if(!rst_n) counter <= 0; else counter <= counter + threshold; end always@(posedge clk or negedge rst_n) begin if(!rst_n) wave_out <= 0; else if(counter < 32'h7FFF_FFFF) wave_out <= 0; else wave_out <= 1; end endmodule button_control.v

module button_control(input wire clk,input wire rst_n,input wire button_up, // 增加频率按钮input wire button_down, // 减少频率按钮output reg [19:0] freq_sel // 输出选择的频率

);reg [19:0] freq_max = 20'd1000; // 最大频率 1 MHz (1000 kHz)reg [19:0] freq_min = 20'd1; // 最小频率 1 kHzreg button_up_last;reg button_down_last;// 检测下降沿wire button_up_fall = (button_up_last == 1) && (button_up == 0);wire button_down_fall = (button_down_last == 1) && (button_down == 0);always @(posedge clk) beginif (!rst_n) beginfreq_sel <= 20'd1;button_up_last <= 1'b1; button_down_last <= 1'b1; // 默认频率1 kHzend else begin// 更新按键的上一个状态button_up_last <= button_up;button_down_last <= button_down;// 处理按键下降沿if (button_up_fall && freq_sel < freq_max)freq_sel <= freq_sel + 1;else if (button_down_fall && freq_sel > freq_min)freq_sel <= freq_sel - 1;end

endendmoduleseven_segment_display.v

// 数码管显示模块

module seven_segment_display(input wire clk,input wire rst_n,input wire [19:0] freq_sel, // 当前选择的频率值(单位kHz)output reg [6:0] hex0, // 数码管显示频率的最低位output reg [6:0] hex1, // 数码管显示频率的中间位output reg [6:0] hex2 // 数码管显示频率的最高位

);wire [3:0] digit0 = freq_sel % 10; // 频率个位wire [3:0] digit1 = (freq_sel / 10) % 10; // 频率十位wire [3:0] digit2 = (freq_sel / 100) % 10; // 频率百位always @(*) beginhex0 = digit_to_segment(digit0);hex1 = digit_to_segment(digit1);hex2 = digit_to_segment(digit2);endfunction [6:0] digit_to_segment;input [3:0] digit;case (digit)4'd0: digit_to_segment = 7'b1000000; // 显示04'd1: digit_to_segment = 7'b1111001; // 显示14'd2: digit_to_segment = 7'b0100100; // 显示24'd3: digit_to_segment = 7'b0110000; // 显示34'd4: digit_to_segment = 7'b0011001; // 显示44'd5: digit_to_segment = 7'b0010010; // 显示54'd6: digit_to_segment = 7'b0000010; // 显示64'd7: digit_to_segment = 7'b1111000; // 显示74'd8: digit_to_segment = 7'b0000000; // 显示84'd9: digit_to_segment = 7'b0010000; // 显示9default: digit_to_segment = 7'b1111111; // 默认不显示endcaseendfunction

endmoduleuart_control.v

module uart_control(input wire clk, // FPGA主时钟input wire rst_n, // 复位信号input wire uart_rx, // 接收来自计算机的UART信号output reg [19:0] freq_sel // 输出设置的频率值

);wire [7:0] uart_data; // 单字节UART数据wire uart_data_ready; // 数据是否接收完成的标志reg [15:0] received_data; // 两字节拼接后的数据reg [1:0] byte_counter; // 字节计数器,跟踪接收的字节数reg data_processed; // 数据是否已处理标志// 实例化UART接收器uart_receiver uart_rx_inst (.clk(clk),.rst_n(rst_n),.rx(uart_rx),.data(uart_data),.data_ready(uart_data_ready));always @(posedge clk or negedge rst_n) beginif (!rst_n) beginfreq_sel <= 20'd1; // 默认频率1 kHzreceived_data <= 16'd0;byte_counter <= 2'd0;data_processed <= 1'b0;end else begin// 当UART数据接收完成且尚未处理时if (uart_data_ready && !data_processed) begin// 处理接收到的第一个或第二个字节if (byte_counter == 2'd0) beginreceived_data[7:0] <= uart_data; // 保存第一个字节byte_counter <= byte_counter + 1;end else if (byte_counter == 2'd1) beginreceived_data[15:8] <= uart_data; // 保存第二个字节byte_counter <= 2'd0; // 重置字节计数器// 检查拼接后的频率是否在有效范围内if (received_data >= 16'd1 && received_data <= 16'd1000) beginfreq_sel <= {4'd0, received_data}; // 将16位数据扩展为20位enddata_processed <= 1'b1; // 标记数据已处理endend// 当数据未准备好时,重置标志以等待下一个数据if (!uart_data_ready) begindata_processed <= 1'b0;endendend

endmodule

uart_receiver.v

module uart_receiver (input wire clk, // FPGA主时钟input wire rst_n, // 复位信号input wire rx, // UART接收信号output reg [7:0] data, // 接收到的数据output reg data_ready // 数据接收完成标志

);parameter CLK_FREQ = 50000000; // FPGA主时钟频率(例如50MHz)parameter BAUD_RATE = 9600; // UART波特率(例如9600)localparam BIT_PERIOD = CLK_FREQ / BAUD_RATE; // 每个位的时钟周期数reg [15:0] clk_counter; // 时钟计数器reg [3:0] bit_index; // 当前位索引reg [7:0] rx_shift_reg; // 接收移位寄存器reg receiving; // 接收状态标志always @(posedge clk or negedge rst_n) beginif (!rst_n) beginclk_counter <= 16'd0;bit_index <= 4'd0;rx_shift_reg <= 8'd0;data_ready <= 1'b0;receiving <= 1'b0;end else begin// 开始接收:检测到起始位(rx == 0)if (!receiving && rx == 1'b0) beginreceiving <= 1'b1;clk_counter <= 16'd0;bit_index <= 4'd0;data_ready <= 1'b0;end// 接收状态:按波特率接收位if (receiving) beginif (clk_counter == BIT_PERIOD - 1) beginclk_counter <= 16'd0;if (bit_index == 4'd8) begin// 停止位接收完成,数据完整receiving <= 1'b0;data <= rx_shift_reg; // 将移位寄存器中的数据存入datadata_ready <= 1'b1; // 设置数据接收完成标志end else begin// 继续接收数据位,移位存储rx_shift_reg <= {rx, rx_shift_reg[7:1]};bit_index <= bit_index + 1;endend else beginclk_counter <= clk_counter + 1;endend else begindata_ready <= 1'b0; // 重置data_ready标志endendendendmodule

资源

1.Quartus搭配Modelsim仿真全流程/Bug解决文章浏览阅读1.6w次,点赞20次,收藏178次。Quartus搭配Modelsim仿真全流程教学,可能遇到的问题以及解决方法_quartus仿真https://blog.csdn.net/weixin_43680772/article/details/117791151?fromshare=blogdetail&sharetype=blogdetail&sharerId=117791151&sharerefer=PC&sharesource=AhandsomeA&sharefrom=from_link![]() https://blog.csdn.net/weixin_43680772/article/details/117791151?fromshare=blogdetail&sharetype=blogdetail&sharerId=117791151&sharerefer=PC&sharesource=AhandsomeA&sharefrom=from_link

https://blog.csdn.net/weixin_43680772/article/details/117791151?fromshare=blogdetail&sharetype=blogdetail&sharerId=117791151&sharerefer=PC&sharesource=AhandsomeA&sharefrom=from_link

Quartus使用步骤及联合Modelsim仿真教程文章浏览阅读2.1w次,点赞52次,收藏300次。Quartus使用记录及与modelsim联合仿真_quartus仿真https://blog.csdn.net/m0_64605336/article/details/134355651?fromshare=blogdetail&sharetype=blogdetail&sharerId=134355651&sharerefer=PC&sharesource=AhandsomeA&sharefrom=from_link![]() https://blog.csdn.net/m0_64605336/article/details/134355651?fromshare=blogdetail&sharetype=blogdetail&sharerId=134355651&sharerefer=PC&sharesource=AhandsomeA&sharefrom=from_link

https://blog.csdn.net/m0_64605336/article/details/134355651?fromshare=blogdetail&sharetype=blogdetail&sharerId=134355651&sharerefer=PC&sharesource=AhandsomeA&sharefrom=from_link

2.Quartus串口驱动及USB-Blaster驱动下载指南https://blog.csdn.net/gitblog_09700/article/details/143154139![]() https://blog.csdn.net/gitblog_09700/article/details/143154139

https://blog.csdn.net/gitblog_09700/article/details/143154139

3.AI工具ChatGPThttps://chat.openai.com/![]() https://chat.openai.com/

https://chat.openai.com/

豆包https://www.doubao.com/chat/2377401![]() https://www.doubao.com/chat/2377401

https://www.doubao.com/chat/2377401

DeepSeekhttps://chat.deepseek.com/![]() https://chat.deepseek.com/

https://chat.deepseek.com/

4.使用手册:Terasic - All FPGA Boards - Cyclone V - DE1-SoC Boardhttps://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=167&No=836&PartNo=4![]() https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=167&No=836&PartNo=4

https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=167&No=836&PartNo=4

Terasic - SoC Platform - Cyclone - DE10-Standardhttps://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=205&No=1081&PartNo=4![]() https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=205&No=1081&PartNo=4

https://www.terasic.com.tw/cgi-bin/page/archive.pl?Language=English&CategoryNo=205&No=1081&PartNo=4

相关文章:

实验六 项目二 简易信号发生器的设计与实现 (HEU)

声明:代码部分使用了AI工具 实验六 综合考核 Quartus 18.0 FPGA 5CSXFC6D6F31C6N 1. 实验项目 要求利用硬件描述语言Verilog(或VHDL)、图形描述方式、IP核,结合数字系统设计方法,在Quartus开发环境下ÿ…...

如何用微信小程序写春联

生活没有模板,只需心灯一盏。 如果笑能让你释然,那就开怀一笑;如果哭能让你减压,那就让泪水流下来。如果沉默是金,那就不用解释;如果放下能更好地前行,就别再扛着。 一、引入 Vant UI 1、通过 npm 安装 npm i @vant/weapp -S --production 2、修改 app.json …...

LabVIEW无人机航线控制系统

介绍了一种无人机航线控制系统,该系统利用LabVIEW软件与MPU6050九轴传感器相结合,实现无人机飞行高度、速度、俯仰角和滚动角的实时监控。系统通过虚拟仪器技术,有效实现了数据的采集、处理及回放,极大提高了无人机航线的控制精度…...

C++哈希表深度解析:从原理到实现,全面掌握高效键值对存储

目录 一、核心组件与原理 1. 哈希函数(Hash Function) 2. 冲突解决(Collision Resolution) 3. 负载因子(Load Factor)与扩容 二、C实现:std::unordered_map 1. 模板参数 2. 关键操作与复…...

Vue.js组件开发-实现字母向上浮动

使用Vue实现字母向上浮动的效果 实现步骤 创建Vue项目:使用Vue CLI来创建一个新的Vue项目。定义组件结构:在组件的模板中,定义包含字母的元素。添加样式:使用CSS动画来实现字母向上浮动的效果。绑定动画类:在Vue组件…...

自研有限元软件与ANSYS精度对比-Bar2D2Node二维杆单元模型-四连杆实例

目录 1、四连杆工程实例以及手算求解 2、四连杆的自研有限元软件求解 2.1、选择单元类型 2.2、导入四连杆工程 2.3、节点坐标定义 2.4、单元连接关系、材料定义 2.5、约束定义 2.6、外载定义 2.7、矩阵求解 2.8、变形云图展示 2.9、节点位移 2.10、单元应力 2.11、…...

04树 + 堆 + 优先队列 + 图(D1_树(D11_伸展树))

目录 一、基本介绍 二、伸展操作 1. 左右情况的伸展 2. 左左情况的伸展 3. 右左情况的伸展 4. 右右情况的伸展 三、其它操作 1. 插入 2. 删除 四、代码实现 一、基本介绍 伸展树是一种二叉搜索树,伸展树也是一种平衡树,不过伸展树并不像AVL树那…...

c语言练习题【数据类型、递归、双向链表快速排序】

练习1:数据类型 请写出以下几个数据的数据类型 整数 a a 的地址 存放a的数组 b 存放a的地址的数组 b的地址 c的地址 指向 printf 函数的指针 d 存放 d的数组 整数 a 的类型 数据类型是 int a 的地址 数据类型是 int*(指向 int 类型的指针) …...

SliverAppBar的功能和用法

文章目录 1 概念介绍2 使用方法3 示例代码 我们在上一章回中介绍了SliverGrid组件相关的内容,本章回中将介绍SliverAppBar组件.闲话休提,让我们一起Talk Flutter吧。 1 概念介绍 我们在本章回中介绍的SliverAppBar和普通的AppBar类似,它们的…...

五、定时器实现呼吸灯

5.1 定时器与计数器简介 定时器是一种通过对内部时钟脉冲计数来测量时间间隔的模块。它的核心是一个递增或递减的寄存器(计数器值)。如果系统时钟为 1 MHz,定时器每 1 μs 计数一次。 计数器是一种对外部事件(如脉冲信号ÿ…...

Elasticsearch的索引生命周期管理

目录 说明零、参考一、ILM的基本概念二、ILM的实践步骤Elasticsearch ILM策略中的“最小年龄”是如何计算的?如何监控和调整Elasticsearch ILM策略的性能? 1. **监控性能**使用/_cat/thread_pool API基本请求格式请求特定线程池的信息响应内容 2. **调整…...

【大模型理论篇】最近大火的DeepSeek-R1初探系列1

1. 背景介绍 这一整个春节,被DeepSeek-R1刷屏。各种铺天盖地的新闻以及老板发的相关信息,着实感受到DeepSeek-R1在国外出圈的震撼。 DeepSeek推出了新的推理模型:DeepSeek-R1-Zero 和 DeepSeek-R1。DeepSeek-R1-Zero 是一个在没有经过监督微调…...

【数据结构】(4) 线性表 List

一、什么是线性表 线性表就是 n 个相同类型元素的有限序列,每一个元素只有一个前驱和后继(除了第一个和最后一个元素)。 数据结构中,常见的线性表有:顺序表、链表、栈、队列。 二、什么是 List List 是 Java 中的线性…...

【C++ STL】vector容器详解:从入门到精通

【C STL】vector容器详解:从入门到精通 摘要:本文深入讲解C STL中vector容器的使用方法,涵盖常用函数、代码示例及注意事项,助你快速掌握动态数组的核心操作! 一、vector概述 vector是C标准模板库(STL&am…...

OpenAI推出Deep Research带给我们怎样的启示

OpenAI 又发新产品了,这次是面向深度研究领域的智能体产品 ——「Deep Research」,貌似被逼无奈的节奏… 在技术方面,Deep Research搭载了优化后o3模型并通过端到端强化学习在多个领域的复杂浏览和推理任务上进行了训练。因没有更多的技术暴露…...

洛谷[USACO08DEC] Patting Heads S

题目传送门 题目难度:普及/提高一 题面翻译 今天是贝茜的生日,为了庆祝自己的生日,贝茜邀你来玩一个游戏。 贝茜让 N N N ( 1 ≤ N ≤ 1 0 5 1\leq N\leq 10^5 1≤N≤105) 头奶牛坐成一个圈。除了 1 1 1 号与 N N N 号奶牛外࿰…...

CSS 溢出内容处理:从基础到实战

CSS 溢出内容处理:从基础到实战 1. 什么是溢出?示例代码:默认溢出行为 2. 使用 overflow 属性控制溢出2.1 使用 overflow: hidden 裁剪内容示例代码:裁剪溢出内容 2.2 使用 overflow: scroll 显示滚动条示例代码:显示滚…...

Spring Boot项目如何使用MyBatis实现分页查询

写在前面:大家好!我是晴空๓。如果博客中有不足或者的错误的地方欢迎在评论区或者私信我指正,感谢大家的不吝赐教。我的唯一博客更新地址是:https://ac-fun.blog.csdn.net/。非常感谢大家的支持。一起加油,冲鸭&#x…...

飞行汽车中的无刷外转子电机、人形机器人中的无框力矩电机技术解析与应用

重点:无刷外转子电机与无框力矩电机:技术解析与应用对比 在现代工业自动化和精密机械领域,无刷电机因其高效、低噪音和高可靠性而备受青睐。其中,无刷外转子电机和无框力矩电机更是以其独特的结构和性能特点,成为众多应用场景中的…...

FreeRTOS学习 --- 队列集

队列集简介 一个队列只允许任务间传递的消息为同一种数据类型,如果需要在任务间传递不同数据类型的消息时,那么就可以使用队列集 ! 作用:用于对多个队列或信号量进行“监听”,其中不管哪一个消息到来,都可让…...

在软件开发中正确使用MySQL日期时间类型的深度解析

在日常软件开发场景中,时间信息的存储是底层且核心的需求。从金融交易的精确记账时间、用户操作的行为日志,到供应链系统的物流节点时间戳,时间数据的准确性直接决定业务逻辑的可靠性。MySQL作为主流关系型数据库,其日期时间类型的…...

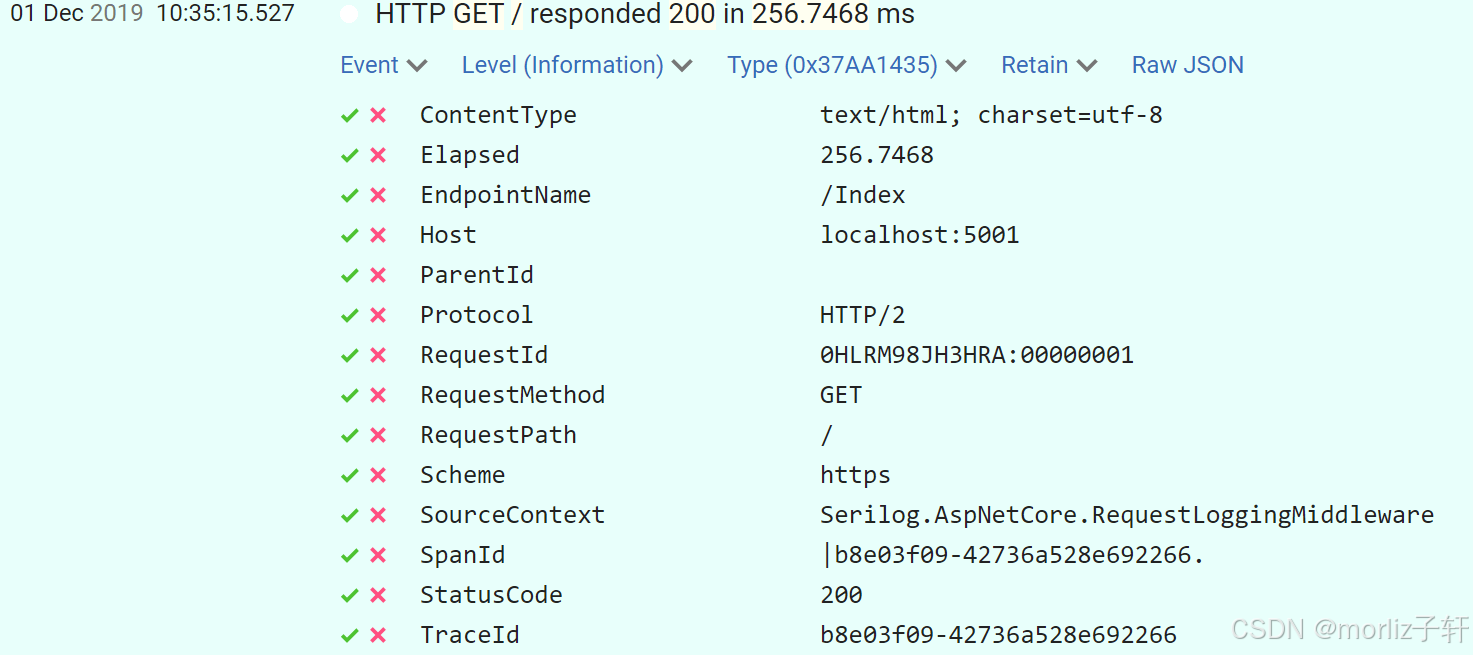

深入浅出Asp.Net Core MVC应用开发系列-AspNetCore中的日志记录

ASP.NET Core 是一个跨平台的开源框架,用于在 Windows、macOS 或 Linux 上生成基于云的新式 Web 应用。 ASP.NET Core 中的日志记录 .NET 通过 ILogger API 支持高性能结构化日志记录,以帮助监视应用程序行为和诊断问题。 可以通过配置不同的记录提供程…...

TDengine 快速体验(Docker 镜像方式)

简介 TDengine 可以通过安装包、Docker 镜像 及云服务快速体验 TDengine 的功能,本节首先介绍如何通过 Docker 快速体验 TDengine,然后介绍如何在 Docker 环境下体验 TDengine 的写入和查询功能。如果你不熟悉 Docker,请使用 安装包的方式快…...

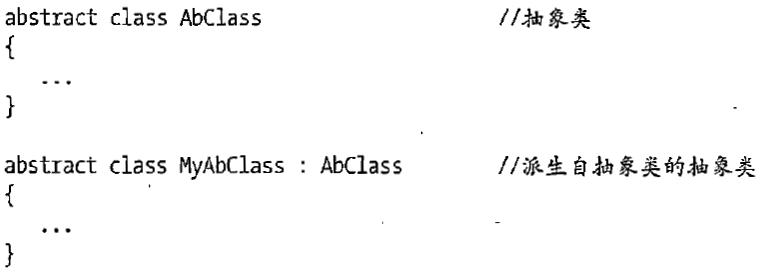

C# 类和继承(抽象类)

抽象类 抽象类是指设计为被继承的类。抽象类只能被用作其他类的基类。 不能创建抽象类的实例。抽象类使用abstract修饰符声明。 抽象类可以包含抽象成员或普通的非抽象成员。抽象类的成员可以是抽象成员和普通带 实现的成员的任意组合。抽象类自己可以派生自另一个抽象类。例…...

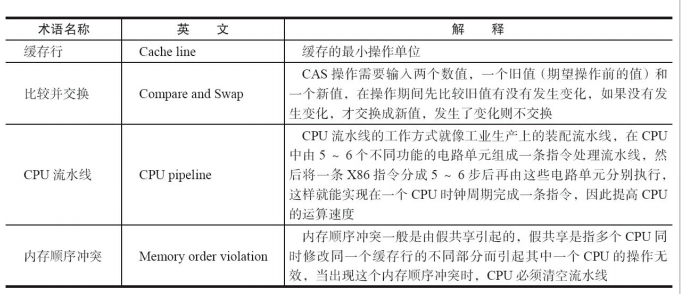

JUC笔记(上)-复习 涉及死锁 volatile synchronized CAS 原子操作

一、上下文切换 即使单核CPU也可以进行多线程执行代码,CPU会给每个线程分配CPU时间片来实现这个机制。时间片非常短,所以CPU会不断地切换线程执行,从而让我们感觉多个线程是同时执行的。时间片一般是十几毫秒(ms)。通过时间片分配算法执行。…...

[Java恶补day16] 238.除自身以外数组的乘积

给你一个整数数组 nums,返回 数组 answer ,其中 answer[i] 等于 nums 中除 nums[i] 之外其余各元素的乘积 。 题目数据 保证 数组 nums之中任意元素的全部前缀元素和后缀的乘积都在 32 位 整数范围内。 请 不要使用除法,且在 O(n) 时间复杂度…...

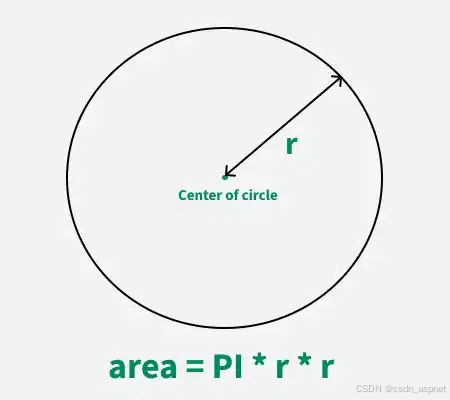

C# 求圆面积的程序(Program to find area of a circle)

给定半径r,求圆的面积。圆的面积应精确到小数点后5位。 例子: 输入:r 5 输出:78.53982 解释:由于面积 PI * r * r 3.14159265358979323846 * 5 * 5 78.53982,因为我们只保留小数点后 5 位数字。 输…...

docker 部署发现spring.profiles.active 问题

报错: org.springframework.boot.context.config.InvalidConfigDataPropertyException: Property spring.profiles.active imported from location class path resource [application-test.yml] is invalid in a profile specific resource [origin: class path re…...

【分享】推荐一些办公小工具

1、PDF 在线转换 https://smallpdf.com/cn/pdf-tools 推荐理由:大部分的转换软件需要收费,要么功能不齐全,而开会员又用不了几次浪费钱,借用别人的又不安全。 这个网站它不需要登录或下载安装。而且提供的免费功能就能满足日常…...

【电力电子】基于STM32F103C8T6单片机双极性SPWM逆变(硬件篇)

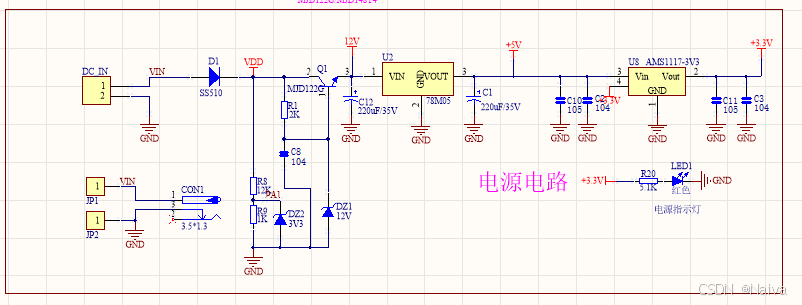

本项目是基于 STM32F103C8T6 微控制器的 SPWM(正弦脉宽调制)电源模块,能够生成可调频率和幅值的正弦波交流电源输出。该项目适用于逆变器、UPS电源、变频器等应用场景。 供电电源 输入电压采集 上图为本设计的电源电路,图中 D1 为二极管, 其目的是防止正负极电源反接, …...