FPGA时序约束(四)主时钟、虚拟时钟和时钟特性的约束

系列文章目录

FPGA时序约束(一)基本概念入门及简单语法

FPGA时序约束(二)利用Quartus18对Altera进行时序约束

FPGA时序约束(三)时序约束基本路径的深入分析

文章目录

- 系列文章目录

- 前言

- 主时钟约束

- 跨时钟域的时序分析

- 虚拟时钟约束

- 系统同步:pin2reg

- 系统同步:reg2pin

- 时钟特性约束

- 时钟抖动(一些只适用于xilinx)

- set_input_jitter

- set_system_jitter

- 时钟不确定性

- set _clock_latency/时钟偏斜

前言

在读《FPGA时序约束与分析》吴厚航时记录的读书笔记,继续总结记录一些知识点,深入一点点。(很详细的一本时序约束的书,非常推荐)

主时钟约束

在《FPGA时序约束(二)利用Quartus18对Altera进行时序约束》中简单的介绍了几种约束,其中提到了主时钟约束

create_clock -name xxxx -period a -waveform {b c} [get_ports {xxx}]

定义名为xxxx的时钟,周期为a ns,上升沿b ns,下降沿c ns,来自端口xxx(FPGA引脚)

有几个注意的地方:

- 当输入时钟是一对差分信号,只需要约束正端(P端)那个输入引脚就行,负端会自动识别

- 如果b的值不为0,相当进行了相移(但是没搞懂一个输入时钟怎么能相移的,又不是衍生时钟,可能意思是时序约束能对该时钟进行相移)

- 如果是get_nets进行定义,取的是FPGA的内部网络作为时钟的物理节点

- -waveform {b c}可以不加,默认是0和50%的占空比

多频率约束:(对同一个输入管脚有多个频率的时钟进行约束)

create_clock -name xxxx1 -period a -waveform {b c} [get_ports {xxx}]

create_clock -name xxxx2 -period d -waveform {e f} [get_ports {xxx}] -add

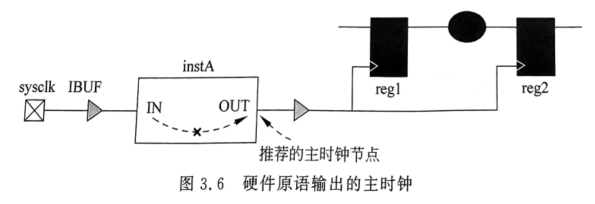

对硬件原语约束(xilinx)(对Altera也是可以的)

对于一些硬件原语的输出时钟引脚,可以将这个硬件原语的输出引脚作为时钟源进行主时钟约束,如instA/OUT。

若此时还是指定BUFG0、BUFG1原语的输出端作为主时钟约束的根节点,就可能由于两条线的时钟偏斜差异而导致时序分析结果的误差。在这种情况下,只需要直接对源时钟 sysclk进行主时钟约束,就能覆盖该时钟所驱动的所有时序路径。(在Altera的quartus里面找了半天没找到,不知道能不能约束buffer后面的节点)

跨时钟域的时序分析

出现上图这样驱动时钟不同的情况:

时序分析工具会竭尽所能地寻找发射沿之后最近的一个锁存沿,以此作为最坏情况的建立时间关系。寻找与发射沿对齐或者在发射沿之前最近的一个锁存沿,以此作为最坏情况的保持时间关系。

会寻找建立时间关系的最坏情况,就是寻找发射沿之后最近的锁存沿(最小的正向时间)。保持时间关系的最坏情况,就是寻找发射沿之前(包括与发射沿对齐)最近的一个锁存沿(最小的负向时间)。

有下图几种情况:

虚拟时钟约束

一些引脚上的数据信号,其同步时钟只存在于外部芯片,并不存在于FPGA器件内。这种情况下必须定义一个时钟用于描述数据引脚,就称为虚拟时钟。定义时无须依附于任何设计中的实际物理节点。

虚拟时钟同样是以create_clock 命令进行约束定义的,但无须指定目标端口或网络。

虚拟时钟通常被用于以下一些情况中的输人或输出延时约束:

- 时序分析(一般是I/O引脚相关的时序路径)的参考时钟并不是FPGA内部的某个设计时钟(主时钟)。

- 与FPGA器件的I/О路径相关的内部驱动时钟与其板级驱动时钟并不是完全同步的。

- 设计者希望对I/O的驱动时钟指定一些特殊的抖动和延时值,但又不希望影响此时钟在FPGA内部的时钟传输特性。

虚拟时钟仅用作参考,以指定相对于该时钟的输入延迟和输出延迟。

例如,时钟周期为10ns,并且不依附于任何目标网络的时钟信号clk_virt,其约束定义时的目标网络属性就无须指定。其名称定义就是clk_virt,约束脚本如下。

create_clock - name clk_virt - period 10

虚拟时钟也必须在其被输入或输出延时约束引用前做好定义。

我现在不太懂,后来网上查了查,后面可能会根据这个clk_virt 来设置set_input_delay这些:

如:

set_input_delay 6 -clock clk_virt [get_ports dina]

系统同步:pin2reg

对于源寄存器reg1的时钟不会传入到FPGA,这个时候就要根据实际情况对VCLK进行虚拟时钟约束,以便时序分析。

create_clock - period 10.000 -name VIR_CLK -waveform {0.000 5.000}

create_clock - period 10.000 -name SYS_CLK -waveform {0.000 5.000} [ get_ports clk]

create_clock - period 10.000 -name VIR_CLK -waveform {2.000 7.000}

create_clock - period 10.000 -name SYS_CLK -waveform {0.000 5.000} [ get_ports clk]

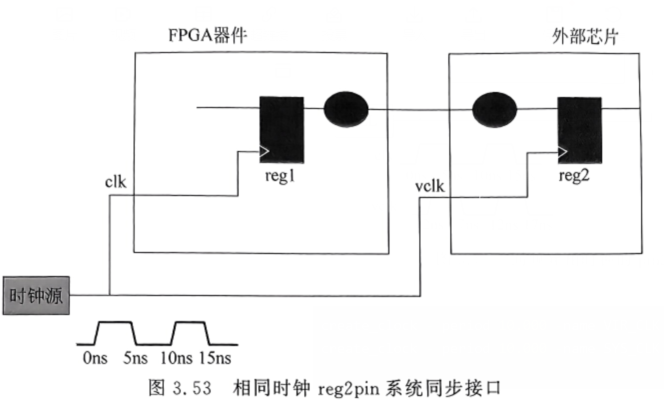

系统同步:reg2pin

源寄存器reg1的驱动时钟是实际存在的,设计者可以对其进行主时钟约束,而目的寄存器的主时钟reg2并不会传输到FPGA器件,此时设计者就可以对其进行虚拟时钟约束,以便于时序分析。

create_clock - period 10.000 -name VIR_CLK -waveform {0.000 5.000}

create_clock - period 10.000 -name SYS_CLK -waveform {0.000 5.000} [ get_ports clk]

create_clock - period 10.000 -name VIR_CLK -waveform {2.000 7.000}

create_clock - period 10.000 -name SYS_CLK -waveform {0.000 5.000} [ get_ports clk]

时钟特性约束

在真实世界中,当时钟在FPGA器件内部传输时,会经过各种时钟缓冲器、时钟管理单元以及固有的时钟走线路径,加上各种不可避免的硬件噪声,都会引起时钟沿的延时和波形变化,称其为时钟的传输时延和时钟不确定性。

在FPGA中,时钟的偏差特性,主要通过时钟抖动(Clock Jitter)和时钟不确定性(Clock Uncertainty)进行约束。

时钟抖动(一些只适用于xilinx)

对于时钟抖动,一般推荐使用Vivado时序工具默认产生的时钟抖动值。

set_input_jitter:

-

更改某个时钟信号的默认时钟抖动值,指定这个时钟的峰峰(peak-to-peak)抖动值。

-

命令只能约束主时钟的抖动值,不能用于约束衍生时钟的抖动值。除了MMCM或PLL外,主时钟所设定的时钟抖动值将会传递给它的衍生时钟。(前面提到xilinx会自动时序约束这些ip核)

-

每条set_input_jitter命令只能约束一个主时钟。

set _system _jitter:

- 若系统电源存在较大噪声,如FPGA器件核压VCCINT由于大量节点的同时开关,串扰、温度突变等因素导致全局的时钟抖动,使用set_system_jitter命令对系统抖动(System Jitter)进行定义。

- Vivado时序工具自动使用set _system _jitter命令约束了0.050ns的默认系统抖动值。通常不建议用set_system_jitter命令去设定一个新的系统抖动值。

使用set_input_jitter命令和set_system_jitter命令约束的系统抖动,在Vivado 工具中进行时序分析时,都会作为时钟不确定性的一部分进行计算。

时钟的系统抖动值和输入抖动值通常都是符合高斯分布的一些随机值,因此以其均方值作为最坏情况进行计算:

Tsj=sqrt(SourceClockSystemJitter ^ 2+DestinationClockSystemJitter^2)

例如,使用默认的0.050ns的系统抖动值:Tsj=sqrt(0.050^ 2+0.050^2)=0.071ns=71ps

set_input_jitter

set_input_jitter [get_clocks <clock_name >]<jitter_in_ns>

get_clocks用于指定需要约束抖动值的主时钟名<clock_name>,这个主时钟必须是事先约束定义好的。

<jitter_in_ns>指定抖动值,取值必须大于或等于0,单位为ns。

例子:

set_input_jitter clk1 0.3

set_input_jitter clk2 0.3

set_system_jitter

set_system_jitter <jitter_in_ns >

<jitter_in_ns >指定所有时钟的系统抖动值,取值必须大于或等于0,单位为 ns。

例子;

create_clock -period 10 -name sysclk [get_ports clk]

set_system_jitter sysclk 0.1

时钟不确定性

除时钟抖动以外的所有可能影响时钟周期性偏差的因素,都可以使用set_clock_uncertainty命令进行约束。

set_clock_uncertainty -setup -from [get_clocks <clock0_name>] -to [get_clocks <clock1_name >]<uncertainty_value >

- -setup表示定义建立时间检查的时钟不确定性时间,也可以使用-hold表示保持时间的时钟不确定性,如果不指定-setup和-hold,则表示同时建立时间和保持时间的不确定性时间。

- -from指定源时钟,-to指定目标时钟,对于非跨时钟域的路径,一般不需要指定-from和-to。

- get_clocks用于指定实际的时钟物理节点名称<clock0_name>或<clockl_name >。

- <uncertainty_value >指定时钟不确定时间,单位为ns。

set_system_jitter和 set_input_jitter命令约束的抖动值都会计算到时钟不确定时间。

set_clock_uncertainty命令约束的时钟不确定性值不会影响set_system_jitter和 set_input_jitter命令约束的抖动值,而是额外增加约束值计算到时钟不确定时间。称set_clock_uncertainty命令约束的时钟不确定性值为用户不确定性(User Uncertainty,UU)时间。

是在计算建立时间余量或保持时间余量时,时钟不确定时间必须作为需要预留出来的一部分余量予以扣除。(最终公式中作为减数)

当希望时钟的时序路径增加时序余量时,也可以使用set_clock_uncertainty命令进行约束定义。相比提高时钟频率增加余量,这种约束方法不更改原有时钟的边沿变化特性和时钟相关性,是更安全稳妥的增加时序余量的约束设计方法。

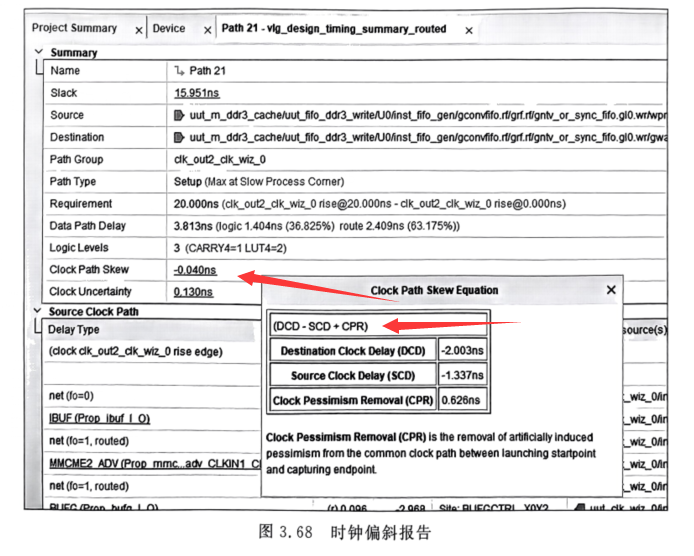

如下图,vivado中的时序报告(什么都抖动和不确定性都没约束时)

例子:

- 给主时钟clk增加500ps(0.5ns)的余量

set_clock_uncertainty -from clk -to clk0 0.500

- 源时钟和目标时钟是两个不同的主时钟,且数据的传输是双向的,这个时候对主时钟clko和 clk1分别设定0.25ns的不确定性时间。

set_clock_uncertainty -from clk0 -to clk1 0.250 -setup

set_clock_uncertainty -from clk1 -to clk0 0.250 -setupset _clock_latency/时钟偏斜

set_clock_latency [-clock<args>] [-rise] [-fall] [-min] [-max] [-source] <latency><objects >

- [-clock]后指定约束时钟(由指定)所相对的时钟名称。若不定义时钟,则时钟延时值将会应用于所有目标时钟所驱动的时序路径。

- [-rise][-fall]指定时钟延时的边沿。

- [-min][-max]指定时钟延时的最大值或最小值。只能指定其一,若不指定则延时值同时作为最大值和最小值。

- [-source]指定时钟延时的基本类型,[-source]即源延时,[-network]即网络延时。默认为[-network]类型。[-source]用于定义时序分析时实际使用的时钟相对于它的理想时钟波形的延时,例如外部晶振源经过PCB板级延时到达FPGA引脚的路径延时。[-network]用于定义时钟信号从设计中的某个指定节点传输到寄存器的时钟输入端口的延时。时钟到达寄存器输人端口的总延时包括了时钟源延时和时钟网络延时。

- < latency >指定时钟延时值,单位为ns。

- < objects >指定约束时钟的名称。

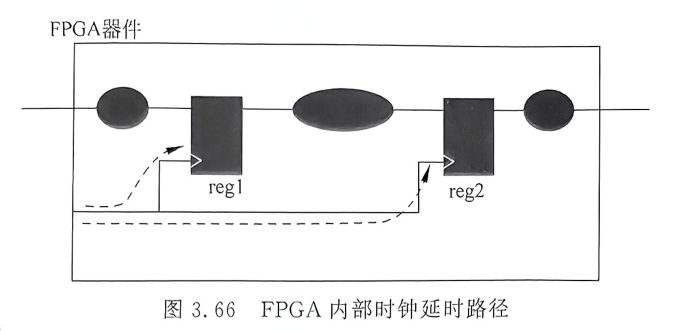

对于已经做过主时钟约束的时钟,时序分析时通常都会自动计算其时钟延时值并给出详细报告,设计者不需要额外约束这些内部时钟的延时。如下图:

对于FPGA外部输入的同步时钟信号,有时需要增加一些时钟延时约束以指定这些时钟在FPGA器件之外的一些时钟延时特性。在上一篇系列文章介绍的引脚到寄存器接口时序约束中,并未专门set _clock_latency,但也利用set_input_delay约束(是一样的),如下图:

例如:指定时钟CLK_A 的上升沿的时钟源延时为0.4ns。

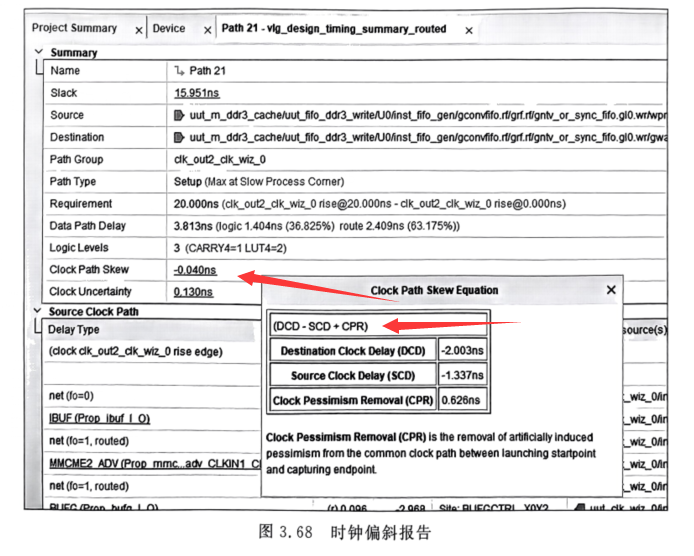

set_clock_latency -source -rise 0.4 [get_ports CLK_A]例如:vivado中,右击可以看到计算公式

分别是源时钟延时(Source Clock Delay,SCD)

目标时钟延时(Destination Clock Delay,DCD)

时钟悲观:这里时钟共同路径延时,Clock Pessimisim Removal(CPR)

DCD-SDC+CPR计算得到时钟偏斜值。

相关文章:

FPGA时序约束(四)主时钟、虚拟时钟和时钟特性的约束

系列文章目录 FPGA时序约束(一)基本概念入门及简单语法 FPGA时序约束(二)利用Quartus18对Altera进行时序约束 FPGA时序约束(三)时序约束基本路径的深入分析 文章目录 系列文章目录前言主时钟约束跨时钟域…...

JNI开发

文件结构(选中的为生成的) CMake构建不需要执行命令,会自动生成so文件打包进apk Android mk构建需要执行命令生成so文件,再打包进apk。命令如下。 # 在jni目录下执行 # 生成com_demo_cppproject_OtherNdkTest.h头文件 javac -h .…...

JAVA有哪些特点?

JAVA有以下特点: 综上所述,Java作为一种先进的面向对象编程语言,具有简单、可移植、健壮、高性能、多线程、动态性、跨平台、开放性和安全性等众多特点,已经成为广泛使用的编程语言之一。 简单易学:JAVA语言的语法与C语…...

使用读写锁提高并发

我们想要的是:允许多个线程同时读,但只要有一个线程在写,其他线程就必须等待。 ReadWriteLock ReadWriteLock的作用: 只允许一个线程写入(其他线程既不能写入也不能读取);没有写入时…...

使用@PropertySource加载配置文件

1.PropertySource和PropertySources注解 1.1.PropertySource注解概述 PropertySource注解是Spring 3.1开始引入的配置类注解。通过**PropertySource注解可以将properties配置文件中的key/value存储到Spring的Environment中,Environment接口提供了方法去读取配置文…...

事务及分布式事务解决方案

基础概念 1.1.事务 事务可以看做是一次大的活动,它由不同的小活动组成,这些活动要么全部成功,要么全部失败。 1.2.本地事务 在计算机系统中,更多的是通过关系型数据库来控制事务,利用数据库本身的事务特性来实现&a…...

【思科、华为、华三、锐捷网络设备巡检命令】

华三 screen-1ength disable 取消分页 displayversion 查看版本 displayclock 查看日期时钟 displayfan 查看风扇状态 displaypower 查看电源信息 displaycpu-usage 查看CPU利用率 displaymemory 查看内存利用率 display environment 查看温度信息 display device 查看设备信息…...

代码随想录算法训练营第五十二天

代码随想录算法训练营第五十二天| 300.最长递增子序列,674. 最长连续递增序列,718. 最长重复子数组 300.最长递增子序列674. 最长连续递增序列718. 最长重复子数组 300.最长递增子序列 题目链接:最长递增子序列 这里是不用处理if nums[i] &l…...

【Linux网络】传输层中UDP和TCP协议

文章目录 1、再谈端口号2、UDP协议3、TCP协议3.1 TCP协议段格式3.2 TCP的三次握手和四次挥手(连接管理机制)3.3 TCP的滑动窗口3.4 TCP的流量控制3.5 拥塞控制3.6 延迟应答和捎带应答3.7 面向字节流和粘包问题3.8 TCP总结 1、再谈端口号 端口号port标识一…...

工具︱ Web3加密浏览器Brave有什么特别之处?

使用浏览器来上网访问和获取各种信息和资源已经成为传统互联网民的普遍活动,下一代互联网协议Web3的核心特点是去中心化,即不依赖于中心化的服务器和数据中心,而是通过分布式的网络节点来实现数据存储和传输。 浏览器承载着信息网络与用户需求…...

绝对不能错过这份沃尔玛实用插件工具大全

龙哥最近发现很多跨境卖家都比较少运营沃尔玛这个平台。沃尔玛除了是世界500强之外,它的线上商城也弄得很好。它的电商平台主要是售卖自营的,然后你也可以入驻来卖自己的产品,就像是我们国内的京东一样。今天龙哥就给大家分享一些沃尔玛专用插…...

【Java】字符串模板拼接的方法

引 在Java中,构建字符串是非常常见的操作。在很多时候,我们都需要使用变量或输入来定制一个文本输出,例如打印日志、生成HTML代码或构建错误消息。而当需要进行字符串连接时,字符串模板是一种常用的方法。在本篇博客中࿰…...

Vue3项目中使用ECharts图表并实现自适应效果

文章目录 一、Vue3项目安装ECharts二、引入、使用ECharts1.创建图表组件,并在父组件中引入使用2.引入ECharts3.ECharts图表自适应 总结 一、Vue3项目安装ECharts 在项目中输入如下代码: npm install echarts --save安装完成可以在package.json中看到&a…...

快速跑通环信IM Android Demo

1、以Android 4.0.0 Demo为例 https://www.easemob.com/download/demo (下载别的版本的demo 可以修改版本号直接下载就就可以) https://downloadsdk.easemob.com/downloads/easemob-sdk-4.0.0.zip 运行时遇到以下报错在项目build.gradle中添加运行时遇…...

1190 - 1196 题)

leetcode解题思路分析(一百三十九)1190 - 1196 题

反转每对括号间的子串 给出一个字符串 s(仅含有小写英文字母和括号)。请你按照从括号内到外的顺序,逐层反转每对匹配括号中的字符串,并返回最终的结果。注意,您的结果中 不应 包含任何括号。 可以简单的用栈保存当前层…...

PHP+vue基于web的小区物业管理管理系统1995a

小区物业管理系统主要是对小区物业以及居民信息进行管理,方便用户使用该资源的一种有效手段。能有效地对物业以及用户信息进行管理并为广大用户服务是该管理系统的基本要求,同时用户也可以及时了解最新的物业信息,方便地查询相关物业情况。基…...

区间预测 | MATLAB实现QRCNN卷积神经网络分位数回归时间序列区间预测

区间预测 | MATLAB实现QRCNN卷积神经网络分位数回归时间序列区间预测 目录 区间预测 | MATLAB实现QRCNN卷积神经网络分位数回归时间序列区间预测效果一览基本介绍模型描述程序设计参考资料 效果一览 基本介绍 区间预测 | MATLAB实现QRCNN卷积神经网络分位数回归时间序列区间预测…...

【AI 导航网站】为了更好的收集 AI 资源,我开发了一个 AI 导航网站

AI 导航网站 目前 AI 应用正呈迸发式增长,然而一个人获取资源的途径有限,对于目前存在的AI工具不能很好的收集总结,所以基于此,我开发了这个一个AI导航网站,希望通过它,收集出目前存在的热门的AI应用&…...

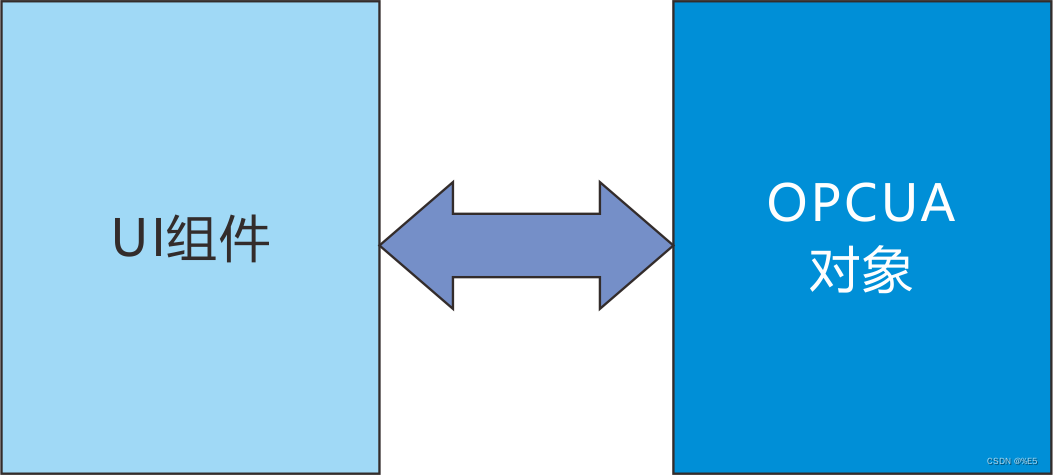

谈谈HMI 的自动化生成技术

人机界面(HMI)是自动化领域不可或缺重要组成部分。尽管人机界面系统的设计看上去并没有太大的技术门槛,但是设计一个HMI系统的工作量是巨大的。如果你没有足够的耐心便完成不了一个通用的HMI系统。构建UI控件库是一个似乎永远完不成的事情&am…...

docker安装elasticsearch

使用docker部署 部署elasticsearch # 拉取镜像 docker pull elasticsearch# 创建容器 docker run --name es -p 9200:9200 \-p 9300:9300 \-e "discovery.typesingle-node" \-e ES_JAVA_OPTS"-Xms64m -Xmx128m" \-v /home/es/conf/elasticsearch.yml:/…...

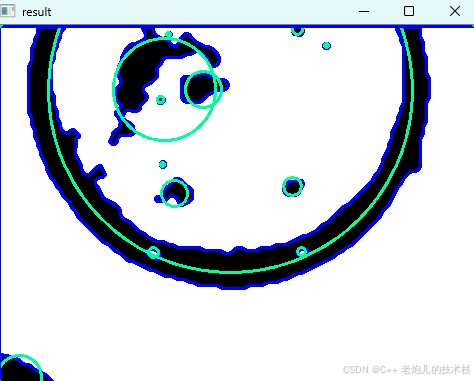

利用最小二乘法找圆心和半径

#include <iostream> #include <vector> #include <cmath> #include <Eigen/Dense> // 需安装Eigen库用于矩阵运算 // 定义点结构 struct Point { double x, y; Point(double x_, double y_) : x(x_), y(y_) {} }; // 最小二乘法求圆心和半径 …...

内存分配函数malloc kmalloc vmalloc

内存分配函数malloc kmalloc vmalloc malloc实现步骤: 1)请求大小调整:首先,malloc 需要调整用户请求的大小,以适应内部数据结构(例如,可能需要存储额外的元数据)。通常,这包括对齐调整,确保分配的内存地址满足特定硬件要求(如对齐到8字节或16字节边界)。 2)空闲…...

基于数字孪生的水厂可视化平台建设:架构与实践

分享大纲: 1、数字孪生水厂可视化平台建设背景 2、数字孪生水厂可视化平台建设架构 3、数字孪生水厂可视化平台建设成效 近几年,数字孪生水厂的建设开展的如火如荼。作为提升水厂管理效率、优化资源的调度手段,基于数字孪生的水厂可视化平台的…...

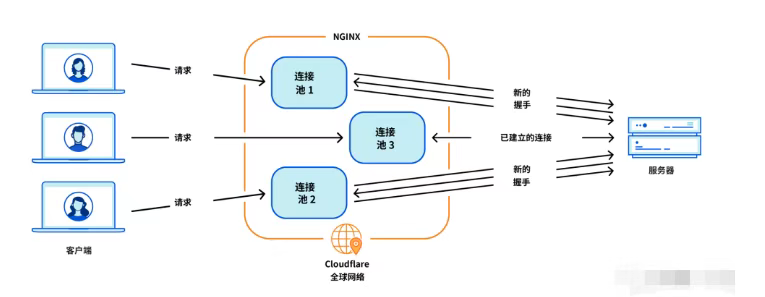

Cloudflare 从 Nginx 到 Pingora:性能、效率与安全的全面升级

在互联网的快速发展中,高性能、高效率和高安全性的网络服务成为了各大互联网基础设施提供商的核心追求。Cloudflare 作为全球领先的互联网安全和基础设施公司,近期做出了一个重大技术决策:弃用长期使用的 Nginx,转而采用其内部开发…...

-HIve数据分析)

大数据学习(132)-HIve数据分析

🍋🍋大数据学习🍋🍋 🔥系列专栏: 👑哲学语录: 用力所能及,改变世界。 💖如果觉得博主的文章还不错的话,请点赞👍收藏⭐️留言Ǵ…...

Go 语言并发编程基础:无缓冲与有缓冲通道

在上一章节中,我们了解了 Channel 的基本用法。本章将重点分析 Go 中通道的两种类型 —— 无缓冲通道与有缓冲通道,它们在并发编程中各具特点和应用场景。 一、通道的基本分类 类型定义形式特点无缓冲通道make(chan T)发送和接收都必须准备好࿰…...

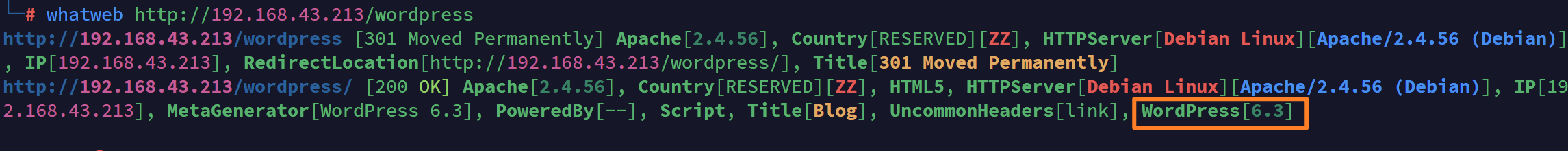

vulnyx Blogger writeup

信息收集 arp-scan nmap 获取userFlag 上web看看 一个默认的页面,gobuster扫一下目录 可以看到扫出的目录中得到了一个有价值的目录/wordpress,说明目标所使用的cms是wordpress,访问http://192.168.43.213/wordpress/然后查看源码能看到 这…...

C语言中提供的第三方库之哈希表实现

一. 简介 前面一篇文章简单学习了C语言中第三方库(uthash库)提供对哈希表的操作,文章如下: C语言中提供的第三方库uthash常用接口-CSDN博客 本文简单学习一下第三方库 uthash库对哈希表的操作。 二. uthash库哈希表操作示例 u…...

k8s从入门到放弃之HPA控制器

k8s从入门到放弃之HPA控制器 Kubernetes中的Horizontal Pod Autoscaler (HPA)控制器是一种用于自动扩展部署、副本集或复制控制器中Pod数量的机制。它可以根据观察到的CPU利用率(或其他自定义指标)来调整这些对象的规模,从而帮助应用程序在负…...

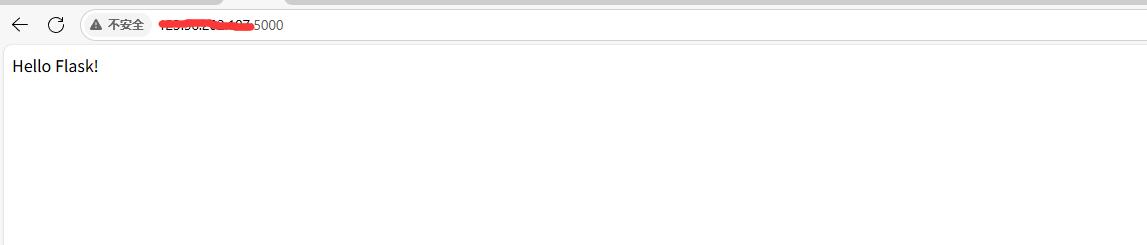

阿里云Ubuntu 22.04 64位搭建Flask流程(亲测)

cd /home 进入home盘 安装虚拟环境: 1、安装virtualenv pip install virtualenv 2.创建新的虚拟环境: virtualenv myenv 3、激活虚拟环境(激活环境可以在当前环境下安装包) source myenv/bin/activate 此时,终端…...