FPGA纯verilog代码实现图像对数变换,提供工程源码和技术支持

目录

- 1、图像对数变换理论

- 2、log系数的matlab生成

- 3、FPGA实现图像对数变换

- 4、vivado与matlab联合仿真

- 5、vivado工程介绍

- 6、上板调试验证并演示

- 7、福利:工程代码的获取

1、图像对数变换理论

对数变换可以将图像的低灰度值部分扩展,显示出低灰度部分更多的细节,将其高灰度值部分压缩,减少高灰度值部分的细节,从而达到强调图像低灰度部分的目的。

图像对数变换一般公式为:g = c*log(1 + f)

其中 c 为常数系数,f 为像素值范围 0~255。

如图所示,对数曲线在像素值较低的区域斜率较大,像素值较高的区域斜率比较低,所以图像经过对数变换之后,在较暗的区域对比度将得到提升,因而能增强图像暗部的细节。

2、log系数的matlab生成

由g = c*log(1 + f)公式可知,只要给出系数c,就能得到log系数,但对数计算不是FPGA的长项,所以使用matlab生成,并转换为.coe 文件

matlab部分代码如下:完整代码请看到文章最后;

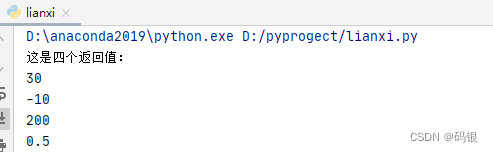

clear;clear all;clc;% g = c*log(1 + f) num = 256;f = [0:1:255]; c =40;g = c*log(1+f);%=================================================================

%创建coe文件保存参数

fid = fopen('log_para_256.coe','w');fprintf(fid,'memory_initialization_radix = 10;\n');

fprintf(fid,'memory_initialization_vector =\n');

再经系数用verilog代码固化到rom,形成一个log系数查找表;

3、FPGA实现图像对数变换

既然已经有了log系数查找表,那么只需要将图像像素数据与查找表逐一对应输出即可,这是FPGA的强项,FPGA图像对数变换顶层代码如下:

module helai_log_algorithm (input i_vid_hs ,input i_vid_vs ,input i_vid_de ,input [7:0] i_vid_rgb , output o_vout_hs ,output o_vout_vs ,output o_vout_de ,output [7:0] o_vout_rgb,

);//同步输出使能信号assign o_vout_hs = i_vid_hs;assign o_vout_vs = i_vid_vs;assign o_vout_de = i_vid_de;helai_log_para r_log_para(.addra(i_vid_rgb[23:16]),.doutao_vout_rgb([23:16])

);helai_log_para g_log_para(.addra(i_vid_rgb[15:8]),.doutao_vout_rgb([15:8])

);helai_log_para g_log_para(.addra(i_vid_rgb[7:0]),.doutao_vout_rgb([7:0])

);endmodule

4、vivado与matlab联合仿真

仿真结果如下:

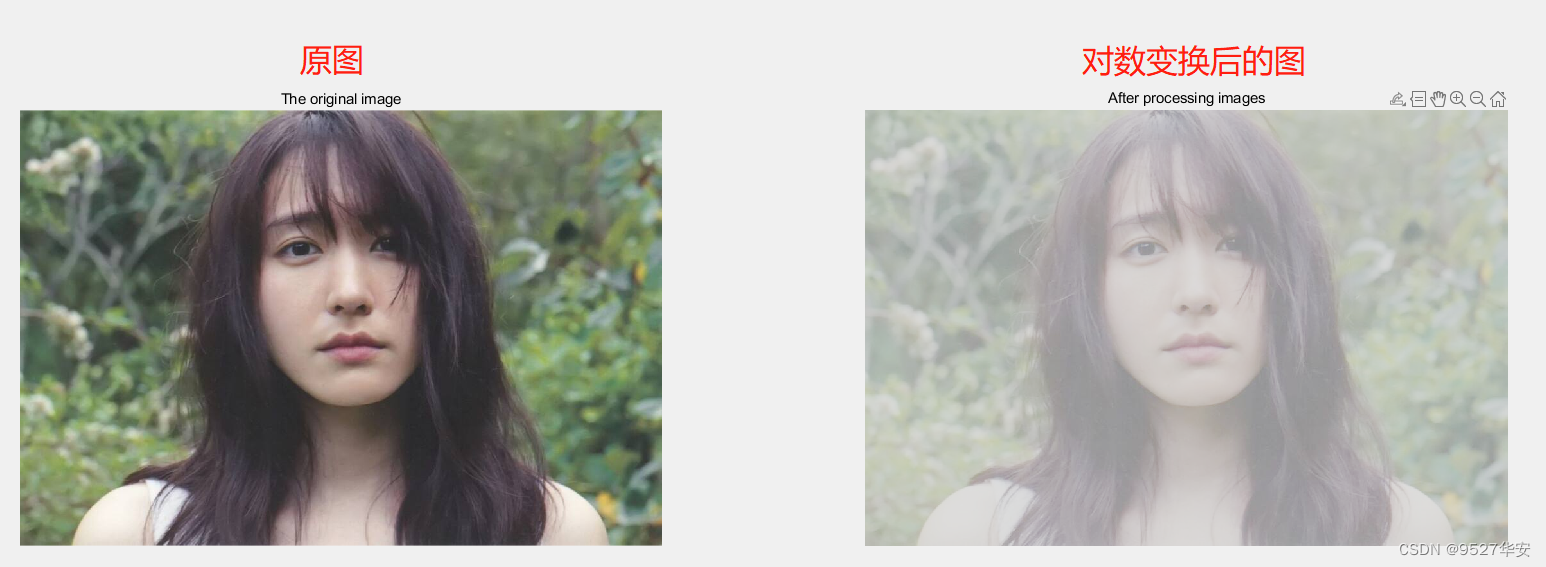

这张图的暗黑区域很少,只有我女友黑色秀发区域,可以看到输出图像整体变白了;

在看另一组仿真:

这张图原图是黑夜,对数变换后的图像就很明显了;

5、vivado工程介绍

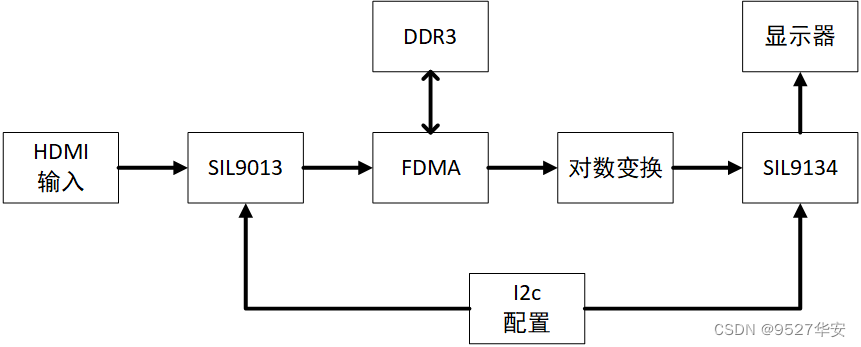

工程设计思路和框架如下:

HDMI输入和输出由编解码器由Silion Image 公 司的SIL9013和SIL9134完成,芯片工作需要iic配置,关于SIL9013和SIL9134的使用和配置,请参考我之前写的文章点击查看:SIL9013和SIL9134的使用和配置

数据采集后经FDMA将通过AXI总线图像写入到DDR3做3帧缓存再输出,关于FDMA三帧缓存,请参考我之前写的文章点击查看:FDMA三帧缓存方案

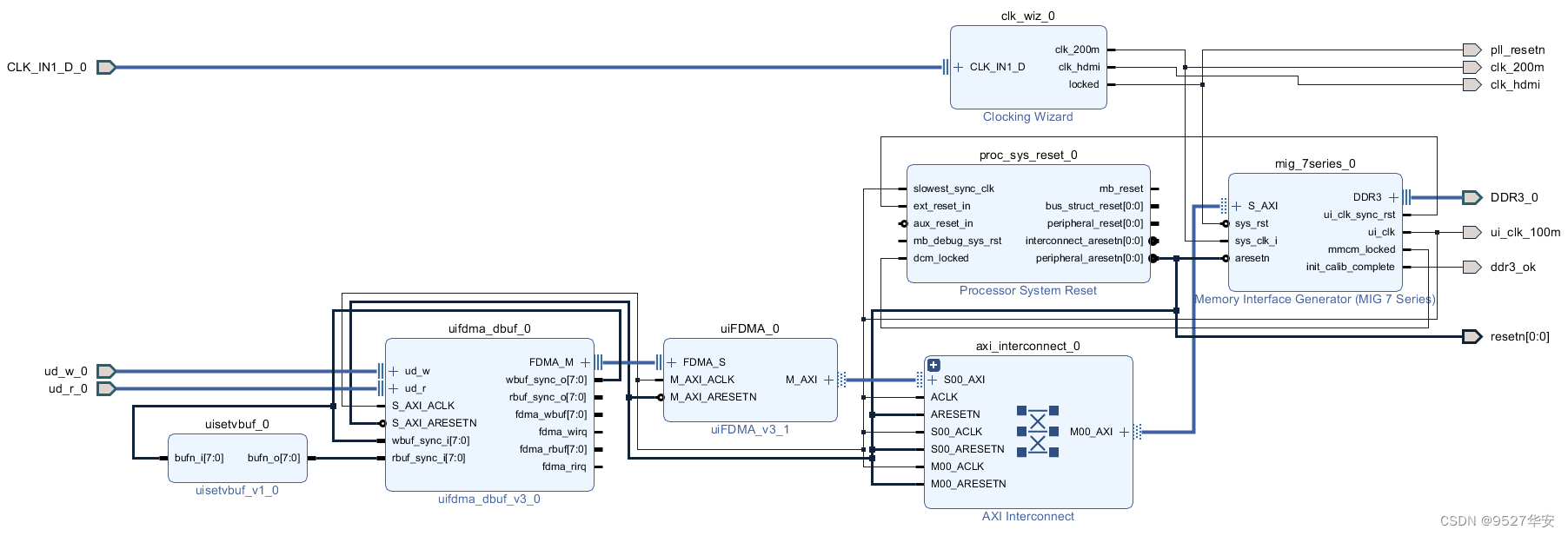

工程BD如下:

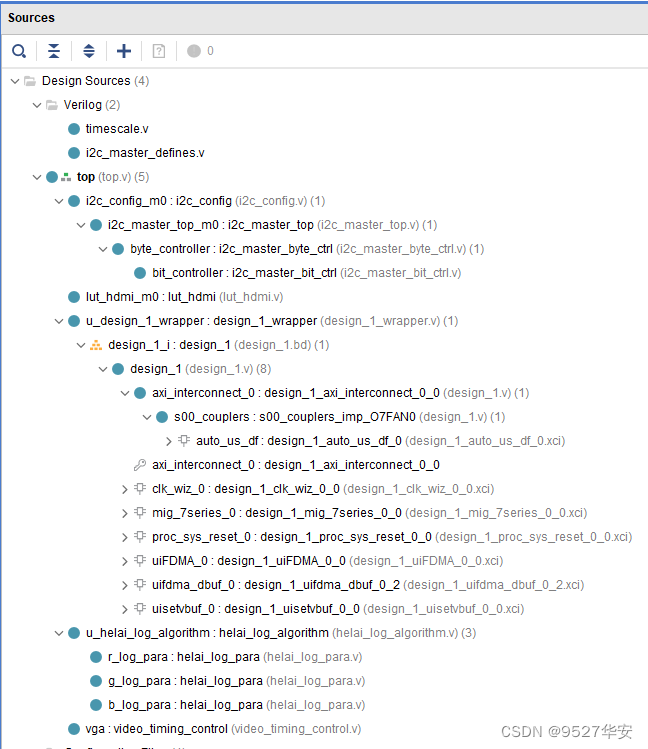

代码架构如下:

顶层代码如下:

`timescale 1ns / 1ps

//

// Company:

// Engineer:

//

// Create Date: 2022/12/12 21:42:17

// Design Name:

// Module Name: top

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//module top(

//ddr3 output [14:0]DDR3_0_addr,output [2:0]DDR3_0_ba ,output DDR3_0_cas_n ,output [0:0]DDR3_0_ck_n ,output [0:0]DDR3_0_ck_p ,output [0:0]DDR3_0_cke ,output [0:0]DDR3_0_cs_n ,output [3:0]DDR3_0_dm ,inout [31:0]DDR3_0_dq ,inout [3:0]DDR3_0_dqs_n ,inout [3:0]DDR3_0_dqs_p ,output [0:0]DDR3_0_odt ,output DDR3_0_ras_n ,output DDR3_0_reset_n ,output DDR3_0_we_n , input CLK_IN1_D_0_clk_n,input CLK_IN1_D_0_clk_p,output ddr3_ok ,

//hdmi_inoutput hdmi_in_nreset , //9011/9013 resetinput vin_clk , //clock for 9111/9013input vin_hs , //horizontal synchronization for 9011/9013input vin_vs , //vertical synchronization for 9011/9013input vin_de , //data valid for 9011/9013input[23:0] vin_data , //data for 9011/9013 inout hdmi_scl , //HDMI I2C clockinout hdmi_sda , //HDMI I2C dataoutput hdmi_nreset , //9134 reset

//hdmi_out output vout_hs , //horizontal synchronization for 9134output vout_vs , //vertical synchronization for 9134output vout_de , //data valid for 9134output vout_clk , //clock for 9134output[23:0] vout_data //data for 9134

);wire clk_200m ;

wire clk_hdmi ;

wire pll_resetn;

wire [0:0] resetn;

wire ud_r_0_ud_rclk;

wire [31:0] ud_r_0_ud_rdata;

wire ud_r_0_ud_rde;

wire ud_r_0_ud_rvs;

wire ud_w_0_ud_wclk;

wire [31:0] ud_w_0_ud_wdata;

wire ud_w_0_ud_wde;

wire ud_w_0_ud_wvs;

wire ui_clk_100m;wire [9:0] lut_index;

wire [31:0] lut_data; wire [23:0] log_rgb;

wire [23:0] i_rgb;

wire o_hs ;

wire o_vs ;

wire o_de ;

wire [23:0] o_rgb;

wire hdmi_clk_rstn;

assign hdmi_nreset =pll_resetn;

assign hdmi_in_nreset=pll_resetn;

assign ud_w_0_ud_wclk =vin_clk ;

assign ud_w_0_ud_wvs =vin_vs ;

assign ud_w_0_ud_wde =vin_de ;

assign ud_w_0_ud_wdata=vin_data;

assign ud_r_0_ud_rclk=clk_hdmi;

assign ud_r_0_ud_rvs=o_vs;

assign ud_r_0_ud_rde=o_de;

assign i_rgb=ud_r_0_ud_rdata[23:0];

assign vout_clk=clk_hdmi;

assign vout_hs=o_hs;

assign vout_vs=o_vs;

assign vout_de=o_de;

assign vout_data=o_rgb;i2c_config i2c_config_m0(

.rst (~pll_resetn ),

.clk (clk_200m ),

.clk_div_cnt (16'd500 ),

.i2c_addr_2byte (1'b0 ),

.lut_index (lut_index ),

.lut_dev_addr (lut_data[31:24]),

.lut_reg_addr (lut_data[23:8] ),

.lut_reg_data (lut_data[7:0] ),

.error ( ),

.done ( ),

.i2c_scl (hdmi_scl ),

.i2c_sda (hdmi_sda )

);lut_hdmi lut_hdmi_m0

(

.lut_index (lut_index),

.lut_data (lut_data )

);design_1_wrapper u_design_1_wrapper(.CLK_IN1_D_0_clk_n(CLK_IN1_D_0_clk_n),.CLK_IN1_D_0_clk_p(CLK_IN1_D_0_clk_p),.DDR3_0_addr (DDR3_0_addr ),.DDR3_0_ba (DDR3_0_ba ),.DDR3_0_cas_n (DDR3_0_cas_n ),.DDR3_0_ck_n (DDR3_0_ck_n ),.DDR3_0_ck_p (DDR3_0_ck_p ),.DDR3_0_cke (DDR3_0_cke ),.DDR3_0_cs_n (DDR3_0_cs_n ),.DDR3_0_dm (DDR3_0_dm ),.DDR3_0_dq (DDR3_0_dq ),.DDR3_0_dqs_n (DDR3_0_dqs_n ),.DDR3_0_dqs_p (DDR3_0_dqs_p ),.DDR3_0_odt (DDR3_0_odt ),.DDR3_0_ras_n (DDR3_0_ras_n ),.DDR3_0_reset_n (DDR3_0_reset_n ),.DDR3_0_we_n (DDR3_0_we_n ),.clk_200m (clk_200m ),.clk_hdmi (clk_hdmi ),.ddr3_ok (ddr3_ok ),.pll_resetn (pll_resetn ),.resetn (resetn ),.ud_r_0_ud_rclk (ud_r_0_ud_rclk ),.ud_r_0_ud_rdata (ud_r_0_ud_rdata ),.ud_r_0_ud_rde (ud_r_0_ud_rde ),.ud_r_0_ud_rempty (ud_r_0_ud_rempty ),.ud_r_0_ud_rvs (ud_r_0_ud_rvs ),.ud_w_0_ud_wclk (ud_w_0_ud_wclk ),.ud_w_0_ud_wdata (ud_w_0_ud_wdata ),.ud_w_0_ud_wde (ud_w_0_ud_wde ),.ud_w_0_ud_wfull (ud_w_0_ud_wfull ),.ud_w_0_ud_wvs (ud_w_0_ud_wvs ),.ui_clk_100m (ui_clk_100m )); helai_log_algorithm u_helai_log_algorithm(.i_vid_hs (),.i_vid_vs (),.i_vid_de (),.i_vid_rgb (i_rgb), .o_vout_hs (),.o_vout_vs (),.o_vout_de (),.o_vout_rgb(log_rgb)

);video_timing_control vga(.i_clk (clk_hdmi ), .i_rst_n(pll_resetn ), .i_rgb (log_rgb ),.o_hs (o_hs ),.o_vs (o_vs ),.o_de (o_de ),.o_rgb (o_rgb ),.o_x_pos(),.o_y_pos()

);

endmodule

6、上板调试验证并演示

FPGA纯verilog代码实现图像对数变换,提供工程源码和

7、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:文章末尾的V名片。

网盘资料如下:

相关文章:

FPGA纯verilog代码实现图像对数变换,提供工程源码和技术支持

目录1、图像对数变换理论2、log系数的matlab生成3、FPGA实现图像对数变换4、vivado与matlab联合仿真5、vivado工程介绍6、上板调试验证并演示7、福利:工程代码的获取1、图像对数变换理论 对数变换可以将图像的低灰度值部分扩展,显示出低灰度部分更多的细…...

【Python百日进阶-Web开发-Vue3】Day516 - Vue+ts后台项目3:首页

文章目录 一、首页头部1.1 element-plus中找到适合的Container布局容器1.2 头部容器Layout 布局1.3 src/views/HomeView.vue二、侧边菜单栏2.1 element-plus中找到适合的Menu侧栏2.2 src/views/HomeView.vue三、侧边栏的动态路由3.1 src/views/HomeView.vue3.2 src/views/Goods…...

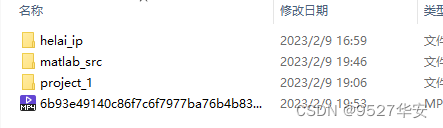

分析了 200 个 DeFi 项目,我发现了这些规律

作者:Ren & Heinrich翻译:dongdong在这篇文章中,我分享了我通过分析当前排名前 200 的 DeFi 加密项目的见解。这不是一项学术研究。尽管如此,这些发现对加密货币投资者来说具有附加值。我使用 https://defillama.com/ 的公共数…...

你领证了吗?各地2022下半年软考纸质证书发放中

不少同学都在关注2022下半年软考证书领取时间,截止至目前,江苏、南京、山东、浙江、贵州、云南、大连、广西地区的纸质证书可以领取了,请大家在证书申领时间内及时预约证书邮寄发放哦~ 江苏 证书领取时间:2023年2月3日起 南京 …...

将群晖NAS变为本地盘

本文介绍一个工具,可以在 Windows 系统下将群晖NAS的目录变为本地盘,好处是在外部访问的时候,能够大大改善体验。可以用本地的应用程序直接打开,速度依赖网络带宽,正常情况下,看视频是没有问题的。当然&…...

以太坊上交易异常Pending的处理方法

交易Pending ETH交易pending的原因: 1.交易GasPrice设置过低,共识节点不打包 2.账户Nonce不连续,一直处于交易池队列当中 只要确认了是哪种原因引起的,就可以做出对应的解决方案。 GasPrice设置过低 由于ETH共识节点是按照Gas价格从高到低打包交易,如果每笔交易的GasPr…...

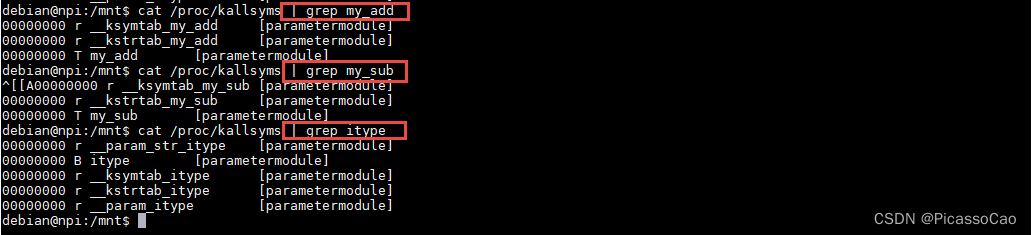

第三节 第一个内核模块

hellomodule 实验 实验说明 硬件介绍 本节实验使用到STM32MP157 开发板 实验代码讲解 本章的示例代码目录为:linux_driver/module/hellomodule 从前面我们已经知道了内核模块的工作原理,这一小节就开始写代码了,跟hello world 一样&…...

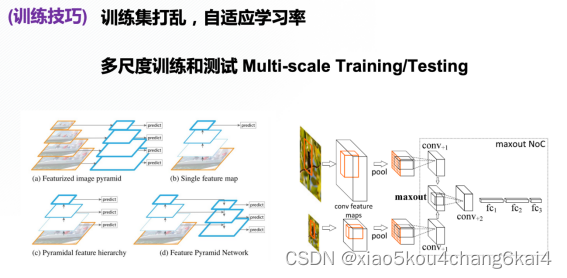

从CNN到Transformer:基于PyTorch的遥感影像、无人机影像的地物分类、目标检测、语义分割和点云分类

我国高分辨率对地观测系统重大专项已全面启动,高空间、高光谱、高时间分辨率和宽地面覆盖于一体的全球天空地一体化立体对地观测网逐步形成,将成为保障国家安全的基础性和战略性资源。随着小卫星星座的普及,对地观测已具备多次以上的全球覆盖…...

操作系统的奋斗(三)内存管理

第三章 内存管理3.1内存管理概念3.1.1 内存管理的基本原理和要求(1)内存管理的主要功能3.1.2 覆盖和交换(1)覆盖(2)交换3.1.3 连续分配管理方式(1)单一连续分配(2&#x…...

多选多的一种通用处理逻辑

开发的时候,我们经常会涉及元素的多选多,并且还需要对选中的元素进行拖动排序 通用的设计方案如下 游戏资源集合与游戏资源的绑定关系处理(多选多的一种通用处理逻辑) 可能的情况: 1.之前被选中的资源,现…...

Redis 的安装 + SpringBoot 集成 Redis

1.安装 Redis此处的 Redis 安装是针对 Linux 版本的安装, 因为 Redis 官方没有提供 Windows 版本, 只提供了 Linux 版本. 但是我们可以通过Windows 去远程连接 Redis.1.1 使用 yum 安装 Redis使用如下命令, 将 Redis 安装到 Linux 服务器:yum -y install redis1.2 启动 Redis使…...

为什么在容器中 1 号进程挂不上 arthas?

作者:卜比 本文是《容器中的 Java》系列文章之 4/n ,欢迎关注后续连载 😃 。 系列1:JVM 如何获取当前容器的资源限制? 系列2:Java Agent 踩坑之 appendToSystemClassLoaderSearch 问题 系列3:让…...

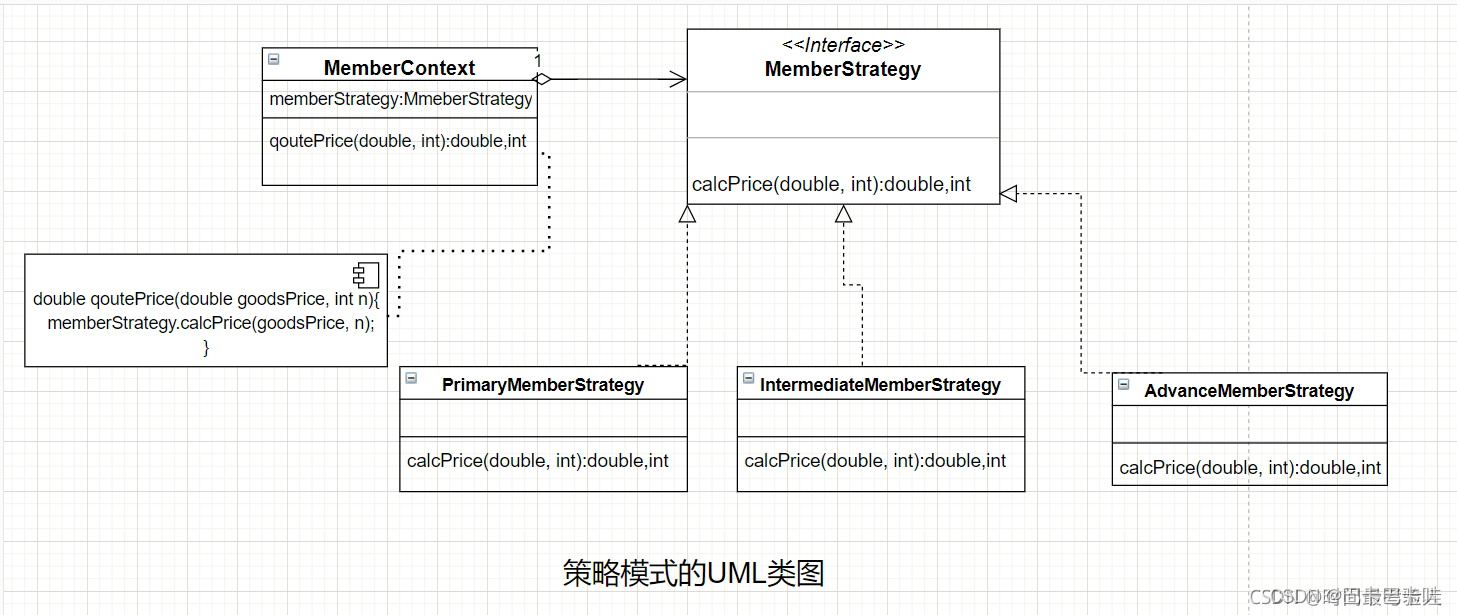

23种设计模式之策略模式

一、概念 就是将一系列算法封装起来,并使它们之间相互替换。被封装起来的算法具有独立性外部不可改变其特性。 策略模式属于对象行为模式,它通过对算法进行封装,把使用算法的责任和算法的实现分割开来,并委派给不同的对象对这些算…...

不会做UI自动化测试?一起设计框架再实践吧

目的相信做过测试的同学都听说过自动化测试,而UI自动化无论何时对测试来说都是比较吸引人的存在。相较于接口自动化来说它可以最大程度的模拟真实用户的日常操作与特定业务场景的模拟,那么存在即合理,自动化UI测试自然也是广大测试同学职业道…...

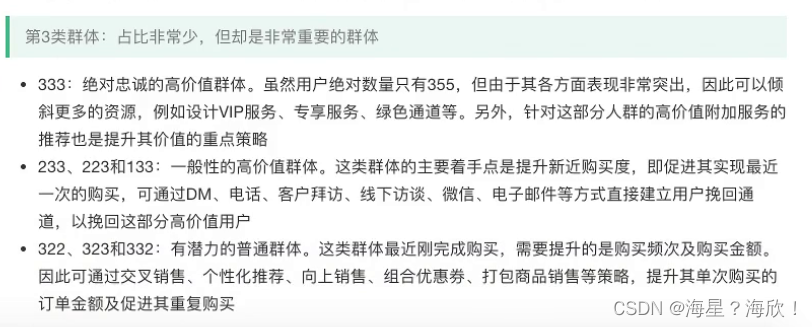

数据分析实战项目3:RFM用户分群

目录1、RFM模型介绍2、Excel实际RFM划分案例3、RFM案例3.1 数据加载和基本信息查看3.2 数据预处理和RFM的初始值计算3.3 RFM区间和划分和分值计算3.4 RFM计算结果保存3.4.1 保存到excel3.4.2 保存到数据库3.5 RFM计算结果可视化3.6 结果分析(营销建议)3.…...

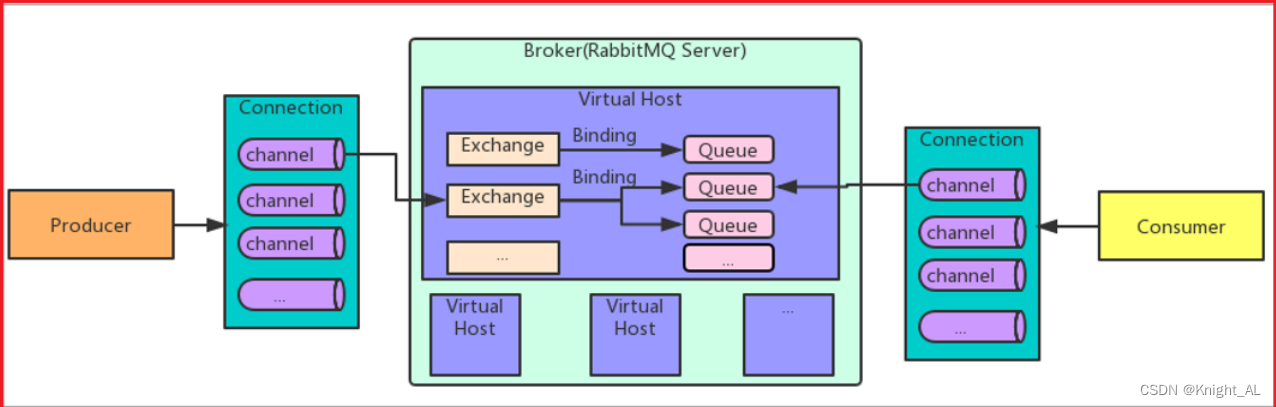

消息中间件概述

目录1.为什么学习消息队列2.什么是消息中间件3.消息队列应用场景3.1 应用解耦3.2 异步处理3.3 流量削峰3.4 什么是QPS,PV3.5 什么是PV,UV,PR4. AMQP 和 JMS4.1 AMQP4.2 JMS4.3. AMQP 与 JMS 区别5. 消息队列产品6. RabbitMQ6.1 RabbitMQ简介6.2 RabbitMQ 中的相关概…...

添加新的json字段)

vue和js给后端接口返回的数据(如以json数据为元素的数组)添加新的json字段

文章目录vue和js给后端接口返回的数据(如以json数据为元素的数组)添加新的json字段1. res为后端接口的响应2. 获取后端接口返回的数据3. 向 tableData 添加字段3.1. 向 tableData 中添加一个新json元素( {"time", "2023-02-09"} )3.…...

负载均衡的方式

在业务初期,我们一般会先使用单台服务器对外提供服务。随着业务流量越来越大,单台服务器无论如何优化,无论采用多好的硬件,总会有性能天花板,当单服务器的性能无法满足业务需求时,就需要把多台服务器组成集…...

python(15)--函数设计

前言 函数是可重用的程序代码块。 函数的作用,不仅可以实现代码的复用,还可以保证修改函数的代码时,所有调用该函数的地方都能得到体现。目前我已知函数的作用是:对代码实现了封装、函数调用、传递参数、返回计算结果等。 正文 …...

手把手教你用Python做可视化数据,还能调节动画丝滑度

数据可视化动画还在用Excel做? 现在一个简单的Python包就能分分钟搞定! 而且生成的动画也足够丝滑,效果是酱紫的: 这是一位专攻Python语言的程序员开发的安装包,名叫Pynimate。 目前可以直接通过PyPI安装使用。 使用…...

3个步骤解决华硕笔记本风扇异常:G-Helper智能散热控制指南

3个步骤解决华硕笔记本风扇异常:G-Helper智能散热控制指南 【免费下载链接】g-helper Lightweight, open-source control tool for ASUS laptops and ROG Ally. Manage performance modes, fans, GPU, battery, and RGB lighting across Zephyrus, Flow, TUF, Strix…...

为什么你的GF-6影像校正总出错?避开UTM投影转换的3个常见坑

为什么你的GF-6影像校正总出错?避开UTM投影转换的3个常见坑 GF-6卫星的宽幅相机(WFV)凭借800公里的超宽覆盖和红边波段等独特优势,已成为农业监测、环境评估等领域的重要数据源。但许多用户在影像校正环节频频遭遇失败——拼接错位…...

开源项目Windows Subsystem for Android部署与优化解决方案

开源项目Windows Subsystem for Android部署与优化解决方案 【免费下载链接】WSA Developer-related issues and feature requests for Windows Subsystem for Android 项目地址: https://gitcode.com/gh_mirrors/ws/WSA Windows Subsystem for Android(WSA&…...

JetBrains IDE试用期到期怎么办?ide-eval-resetter终极指南帮你无缝重置

JetBrains IDE试用期到期怎么办?ide-eval-resetter终极指南帮你无缝重置 【免费下载链接】ide-eval-resetter 项目地址: https://gitcode.com/gh_mirrors/id/ide-eval-resetter 当你正在进行关键代码调试时,JetBrains IDE突然弹出试用期结束的提…...

GPT-6,曝光了,当 AGI 只剩最后一公里,我们为何仍把 GPU 当燃料?

“土豆”熟了,代号 GPT-6。过去两周,OpenAI 的保密墙像被筛子砸过,4 月 14 日这个日期在内部聊天频道被反复 全员。知情人士说,那天的发布按钮其实已经提前写好,只等 Brockman 一声令下。为什么如此急迫?因…...

)

SOONet视频时序定位入门必看:3步完成本地Web服务搭建(含A100适配说明)

SOONet视频时序定位入门必看:3步完成本地Web服务搭建(含A100适配说明) 1. 引言:让AI帮你从长视频里“找片段” 你有没有过这样的经历?面对一个长达几小时的会议录像、教学视频或者家庭录像,只想快速找到其…...

【RAG】【vector_stores008】AwaDB向量存储示例

案例目标本案例演示如何使用AwaDB作为向量存储后端构建RAG系统。AwaDB是一个高性能的向量数据库,专门用于存储和检索高维向量数据,适用于语义搜索、推荐系统和AI应用等场景。通过本示例,用户可以学习如何集成AwaDB与LlamaIndex,实…...

Android屏幕唤醒技术全解析:从熄屏到亮屏的实现方案

1. Android屏幕唤醒技术概览 你有没有遇到过这样的场景:当手机放在桌上突然来消息时,屏幕会自动亮起显示通知内容?这背后就是Android的屏幕唤醒技术在发挥作用。作为开发者,掌握屏幕唤醒技术不仅能提升用户体验,还能在…...

51单片机贪吃蛇进阶:如何用矩阵按键实现‘按住加速’和‘双击暂停’?

51单片机贪吃蛇进阶:矩阵按键高级交互设计实战 在嵌入式开发领域,51单片机因其经典架构和丰富的学习资源,始终保持着旺盛的生命力。而贪吃蛇作为嵌入式入门的经典项目,往往成为开发者接触硬件交互的第一个实战案例。本文将聚焦于如…...

手把手教你部署MiniCPM-V-2_6:最强视觉多模态模型,小白也能快速体验

手把手教你部署MiniCPM-V-2_6:最强视觉多模态模型,小白也能快速体验 1. 认识MiniCPM-V-2_6:视觉多模态新标杆 MiniCPM-V-2_6是目前最先进的视觉多模态模型之一,它基于SigLip-400M和Qwen2-7B构建,总参数量达到80亿。这…...