SystemVerilog interface使用说明

1. Interface概念

System Verilog中引入了接口定义,接口与module 等价的定义,是要在其他的接口、module中直接定义,不能写在块语句中,跟class是不同的。接口是将一组线捆绑起来,可以将接口传递给module。

2. 接口的优点

一)通过接口在module之间或内部进行信号,模块的输入列表就是一个接口,这样简单,避免手动连线的错误。

二)如果需要增加模块的IO,只需要在接口中增加,不需要改变模块的输入列表,防止输入错误、少改了哪个模块的列表。

三)在UVM 中需要在不同的class之间传递信号,用接口的话,传递一组信号只需要uvm_config_db一个接口就可以了,如果不用接口,那么就需要好多条uvm_config_db语句。

四)接口中可以定义一些initial(生成时钟),always块,任务,函数,类的句柄。

3. 定义接口

可以在接口中定义一些信号、函数、任务、class对象,也可以有always,initial语句块。比如可以在initial块中生成时钟clk。

3.1 定义

interface if(input bit clk);logic data;logic valid;logic addr;

endinterface3.2 modport

可以用modport将接口中的信号分组。比如总线接口中,master、slave、arbiter需要的信号是不同的,输入输出也不同。

interface if(input bit clk);logic [7:0] data;logic valid;logic [7:0] addr;logic request;logic grant;logic command;logic ready;modport MASTER(output request,addr,command);modport SLAVE(input request,addr,command,output ready);modport ARBITER(input request,output grant);

endinterface

module Master (if.MASTER if_u);

...

endmodule

module test;if if_u;Master m_u(if_u.MASTER);

endmodule 4. 激励时序

测试平台需要和设计之间的时序密切配合。比如在同一个时间片内,一个信号需要被同时写入和读取,那么采样到新值还是旧值?非阻塞赋值可以解决这个问题,值的计算在active区域,值的更新在NBA区域——采样到的是旧值。

4.1 时钟块控制同步信号的时序

在接口中定义时钟块,时钟块中的任何信号都相对于时钟同步驱动和采样。时钟块大都在测试平台中使用。

interface if(input bit clk);logic [7:0] data;logic valid;logic [7:0] addr;clocking cb@(posedge clk);input valid;input data;input addr;endclockingmodport TEST(clocking cb);modport DUT(input valid ,input data);

endinterface一个接口中可以有多个时钟块,但每个时钟块只有一个时钟表达式。如@(posedge clk)定义了单时钟;@(clk)定义了DDR时钟(双数据率,两个沿)。

4.2 logic还是wire

在测试平台中,如果用过程赋值语句驱动接口中的信号,那么信号要在接口中定义为logic,如果是连续赋值驱动,定义成wire。

定义成logic的一个好处是,如果多个信号驱动logic,那么编译器会报错,这样你就知道写错了,如果是wire,这个错误就隐藏了。

4.3 对测试平台和DUT中事件的调度

如果没有用时钟块,测试平台对DUT的驱动和采样存在竞争,这是因为测试平台的事件和DUT的事件混合在同一个时间片中。

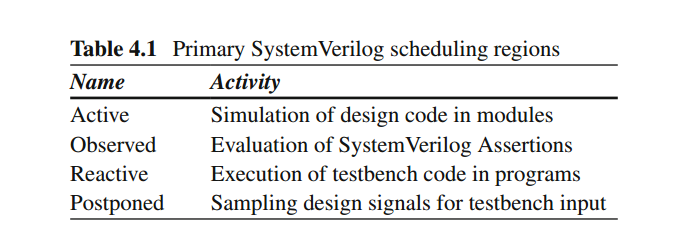

SV中将测试平台中的事件和DUT中的事件分离。时间片划分:

SV的主要调度区域:

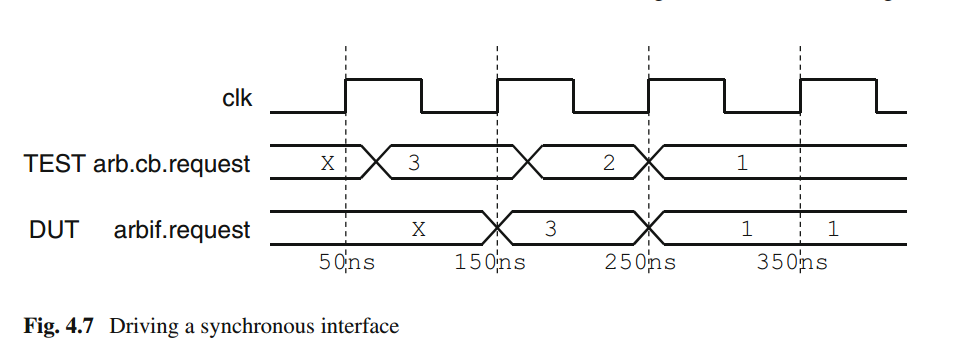

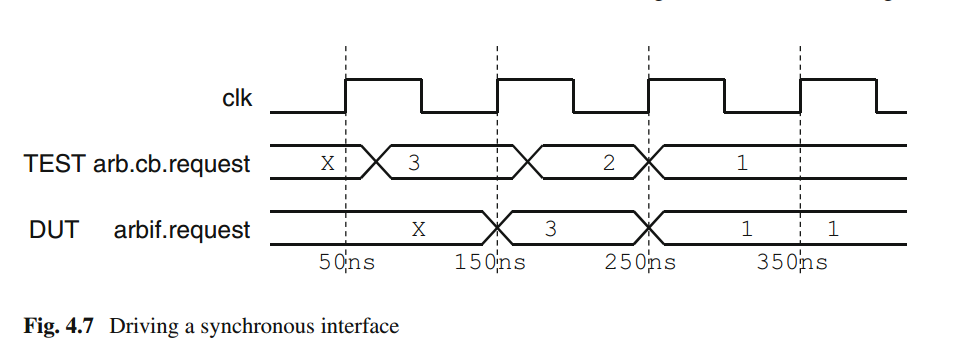

4.4 设计和测试平台之间的时序

时钟块(测试平台)在#1step延时之后采样DUT,也就是采样上一个时间片postponed区域的数据。也就是前面讲的采样旧值。

时钟块(测试平台)在#0延时之后驱动DUT信号。0延迟说明还在同一个time slot,DUT能够捕捉到变化。

更细致的时间片划分:

| time slot | |

|---|---|

| active | design |

| inactive | 显示0延迟阻塞赋值; |

| observed | SVA |

| reactive | SV |

| postponed | SV 采样 |

5. 接口采样和驱动信号的时序

为了同步接口中的信号,可以在时钟沿采样或者驱动接口信号。可以在接口中定义时钟块来同步接口信号:

interface if(input bit clk);logic data;logic valid;logic addr;clocking cb@(posedge clk);input valid;input data;input addr;endclockingmodport TEST(clocking cb);modport DUT(input valid ,input data);

endinterface在测试平台中的信号才需要同步。

5.1 接口信号采样时序

如果时钟块中的信号采样DUT中的信号,采样的是上一个时间片(time slot)postponed区域的数据。即如果DUT信号在时钟沿发生0-1跳变,那么采样到0。DUT接口想要驱动TEST接口中时钟块里的信号,需要先给DUT接口信号赋值:

module dut(if.DUT if0);....#10 if0.valid = 1;#10 if0.valid = 2;....

endmodule

5.2 接口信号驱动时序

如果时钟块驱动DUT信号,值会立即传入到设计中。即如果时钟块中的信号在时钟沿发生0-1跳变,则时钟沿之后DUT中为1。时钟块想要驱动DUT,需要在testbench给时钟块中的信号赋值,在tb中驱动时钟块中的信号需要同步驱动,用“<=”符号。时钟块中的信号驱动采样

program tb(if.TEST if1);...#10 if1.cb.valid <= 1;#10 if1.cb.valid <= 0;...

endprogram

6. 使用虚接口

之前介绍的接口都是跟module一样来描述硬件的;在SV中有面向对象的概念,在class里面使用虚接口——virtual interface。

虚接口是一个物理接口的句柄(handler),同这个句柄来访问硬件接口。虚接口是唯一链接动态对象和静态模块、接口的一种机制。

6.1 在测试平台中使用接口

interface inf; //定义接口

...

endinterface

program test(inf if0); // 接口传入测试平台driver drv;initial begindrv = new(if0); // 接口传给driver对象end

endprogram

class driver;virtual vif; // 在class中为虚接口function new(inf i);vif=i;endfunction

endclass

module top;inf inf0(); // 例化接口test t1(inf0);dut d1(inf0);

endmodule也可以在tb中跨模块引用XMR(cross module reference)接口

program test(); //没有接口参数virtual inf if0=top.inf0;//top是顶层模块...

endprogram

module top;inf inf0(); // 例化接口test t1(); // tb无接口列表dut d1(inf0);

endmodule6.2 使用端口传递接口数组

interface inf(input clk);

...

endinterface

parameter NUM=10;

module top;inf xi[NUM](clk); // 顶层例化多个接口,接口名后跟个数test t1(xi);// 接口作为参数dut...

endmodule

program test(inf xi[NUM]); // 接口参数列表virtual inf vxi[NUM];initial beginvxi=xi;end

endprogram也可以用跨模块引用。

7. 接口中的代码

接口中可以定义信号、函数、任务、class对象,也可以有always,initial语句块。

下面给一个在《UVMPrimer》中的例子:

interface tinyalu_bfm;import tinyalu_pkg::*;

byte unsigned A;byte unsigned B;bit clk;bit reset_n;wire [2:0] op;bit start;wire done;wire [15:0] result;operation_t op_set;

assign op = op_set;

task reset_alu();reset_n = 1'b0;@(negedge clk);@(negedge clk);reset_n = 1'b1;start = 1'b0;endtask : reset_alutask send_op(input byte iA, input byte iB, input operation_t iop, shortint result);if (iop == rst_op) begin@(posedge clk);reset_n = 1'b0;start = 1'b0;@(posedge clk);#1;reset_n = 1'b1;end else begin@(negedge clk);op_set = iop;A = iA;B = iB;start = 1'b1;if (iop == no_op) begin@(posedge clk);#1;start = 1'b0; end else begindo@(negedge clk);while (done == 0);start = 1'b0;endend // else: !if(iop == rst_op)endtask : send_opcommand_monitor command_monitor_h;

function operation_t op2enum();case(op)3'b000 : return no_op;3'b001 : return add_op;3'b010 : return and_op;3'b011 : return xor_op;3'b100 : return mul_op;default : $fatal("Illegal operation on op bus");endcase // case (op)endfunction : op2enum

always @(posedge clk) begin : op_monitorstatic bit in_command = 0;command_s command;if (start) begin : start_highif (!in_command) begin : new_commandcommand.A = A;command.B = B;command.op = op2enum();command_monitor_h.write_to_monitor(command);in_command = (command.op != no_op);end : new_commandend : start_highelse // start lowin_command = 0;end : op_monitor

always @(negedge reset_n) begin : rst_monitorcommand_s command;command.op = rst_op;command_monitor_h.write_to_monitor(command);end : rst_monitorresult_monitor result_monitor_h;

initial begin : result_monitor_threadforever begin@(posedge clk) ;if (done) result_monitor_h.write_to_monitor(result);endend : result_monitor_threadinitial beginclk = 0;forever begin#10;clk = ~clk;endend

endinterface : tinyalu_bfm函数使用的时候通过接口对象调用就行了

virtual tinyalu_bfm inf;

initial begininf.send_op(..);

end8. 接口使用注意事项

-

接口不能在package中被`include 。

下面这种写法是会报错的。

package pkg;`include "apb_if.sv"…… endpackage而要放在package外面

`include "apb_if.sv" package pkg;…… endpackage如果要在UVM中要通过hierarchy访问DUT中的信号,最好将这些信号放在interface中,然后将virtual interface传给UVM

// 在接口中定义信号 interface bfm;bit[7:0 addr; endinterface// 实例化接口 bfm u_bfm();// 将虚接口传给UVM initial beginuvm_config_db#(vitual bfm)::set("", uvm_test_top, "bfm", bfm); end// 在UVM可直接操作虚接口如果不这样的话,当uvm component(driver, monitor, agent等)文件是通过package来管理的话,就不能在UVM中hierarchy引用DUT中的信号。

相关文章:

SystemVerilog interface使用说明

1. Interface概念 System Verilog中引入了接口定义,接口与module 等价的定义,是要在其他的接口、module中直接定义,不能写在块语句中,跟class是不同的。接口是将一组线捆绑起来,可以将接口传递给module。 2. 接口的优…...

机器人制作开源方案 | 送餐机器人

作者:赖志彩、曹柳洲、王恩开、李雪儿、杨玉凯 单位:华北科技学院 指导老师:张伟杰、罗建国 一、作品简介 1. 场景调研 1.1项目目的 近年来,全国多地疫情频发,且其传染性极高,食品接触是传播途径之一。…...

Gradio部署应用到服务器不能正常访问

用Gradio部署一个基于ChatGLM-6B的应用,发布到团队的服务器上(局域网,公网不能访问),我将gradio应用发布到服务器的9001端口 import gradio as gr with gr.Blocks() as demo:......demo.queue().launch(server_port90…...

数据暴涨时代,该如何数据治理?_光点科技

随着信息技术的迅猛发展,数据已经成为现代社会的核心资源。在这个被称为"数据暴涨时代"的时代里,大量的数据源源不断地被产生和积累,但如何有效地管理、分析和利用这些数据成为了一个迫切需要解决的问题。数据治理,作为…...

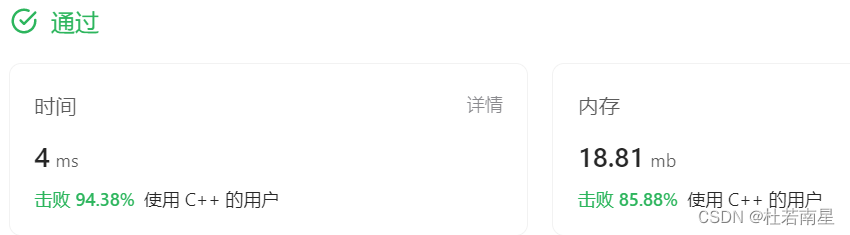

2021年03月 C/C++(三级)真题解析#中国电子学会#全国青少年软件编程等级考试

第1题:找和为K的两个元素 在一个长度为n(n < 1000)的整数序列中,判断是否存在某两个元素之和为k。 时间限制:1000 内存限制:65536 输入 第一行输入序列的长度n和k,用空格分开。 第二行输入序列中的n个整数ÿ…...

GPT-5出世?OpenAI GPT-5商标已注册

OpenAI的GPT已经成为了业界标杆,升级速度之快让人瞠目,别人追GPT-3.5的时候GPT-4横空出世,差距被拉开了,现在GPT-5就要来了。 据商标律师泄露的消息,OpenAI已于7月18日注册了GPT-5商标。虽然注册商标并不罕见…...

优雅的使用 Dockerfile 定制镜像

一、使用 Dockerfile 定制镜像 1.1、Dockerfile 定制镜像 镜像的定制实际上就是定制每一层所添加的配置、文件。如果我们可以把每一层修改、安装、构建、操作的命令都写入一个脚本,用这个脚本来构建、定制镜像,无法重复的问题、镜像构建透明性的问题、…...

limit的用法mysql

当你在 MySQL 数据库中使用 LIMIT 语句,它可以用于限制查询结果的行数。这在分页查询或者限制返回的数据量时非常有用。下面是一些示例: 返回前几行数据: SELECT * FROM Customers LIMIT 5;这将返回 Customers 表中的前 5 行数据。 分页查…...

clickhouse Checksum doesn‘t match: 问题修复

1. 问题描述 SQL 错误 [40] [07000]: Code: 40. DB::Exception: Checksum doesnt match: corrupted data. Reference: 50e8c1efa78de2881b725d44b04be1fe. Actual: 161c99eb681ec36b83540ecdd65ad8c9. Size of compressed block: 32846. The mismatch is caused by single bit…...

企业如何开展个人信息安全影响评估(PIA)二

基本概念 根据《信息安全 技术个人信息安全影响评估指南》(GB/T 39335—2020;personal information security impact assessment,简称“PIA”),个人信息安全影响评估是指针对个人信息处理活动,检验其合法合…...

android TextView 超出长度使用省略号

在Android中最常见的需求,就是在在外部展示信息时,需要简要展示内容。TextView仅需在静态布局文件中设置以下几个属性: android:maxWidth“100dp” // 宽度是多少才算超出 android:maxLines"2" // 高度多少才算超出 android:elli…...

c++ | 字节转换 | 字长 | 机器位数

为什么有的时候脑子转不过来?? 为什么要对字节、机器长啊、位啊都要门清 位数 一般的就是指计算机的位数,比如64位/32位,更简单的理解,计算机就是在不停的做二进制的计算,比如32位计算机,在长…...

7-4 交换最小值和最大值

分数 15 全屏浏览题目 切换布局 作者 C课程组 单位 浙江大学 本题要求编写程序,先将输入的一系列整数中的最小值与第一个数交换,然后将最大值与最后一个数交换,最后输出交换后的序列。 注意:题目保证最大和最小值都是唯一的。…...

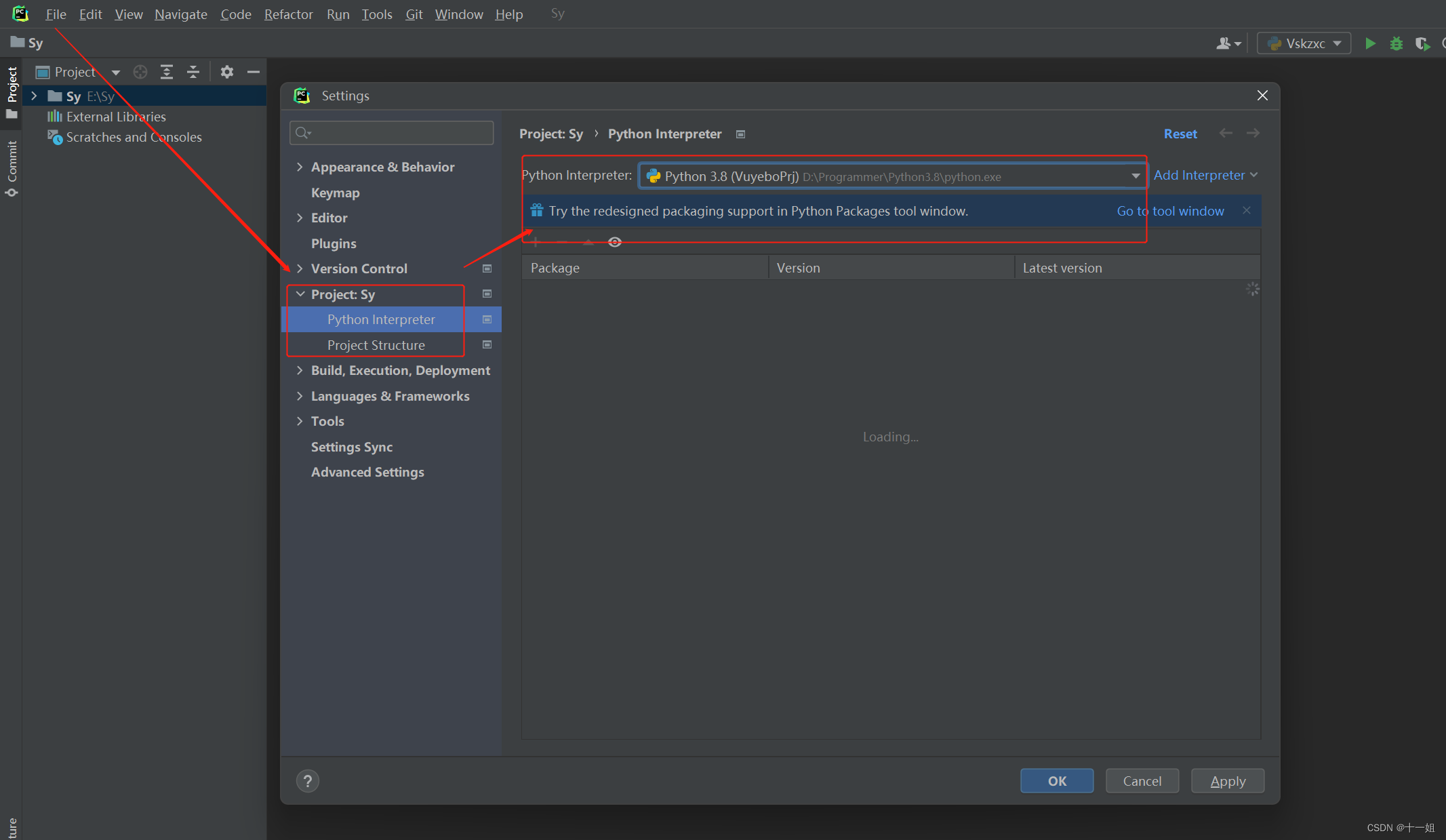

解决Pycharm的Settings中Project不见了也无法选择Python Interpreter的方法

目录 一、问题如下二、解决方法 一、问题如下 突然打开项目没有python解释器,也无法重新配置python Interpreter,而且整个文件夹是黄色高亮的形式,如下显示,而且重新安装了pycharm也没用甚至说打开File–>Setting–>Projec…...

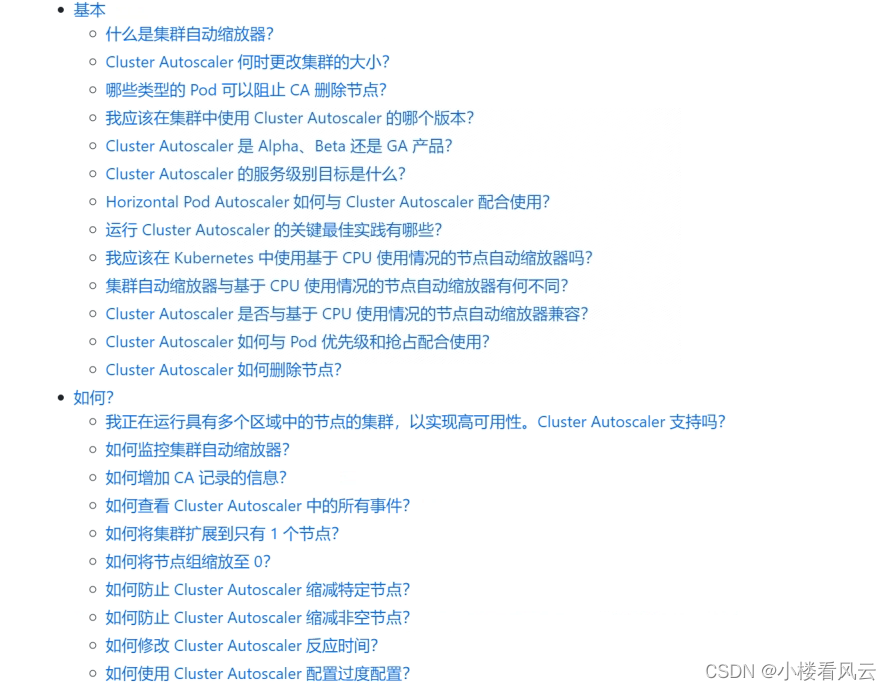

AWS EKS 集群自动扩容 Cluster Autoscaler

文章目录 一,需求工作需求说明 二,部署精简命令执行1,要求2,查看EC2 Auto Scaling groups Tag3,创建Serviceaccount需要的Policy,Role4,部署Cluster Autoscaler5,验证6,常…...

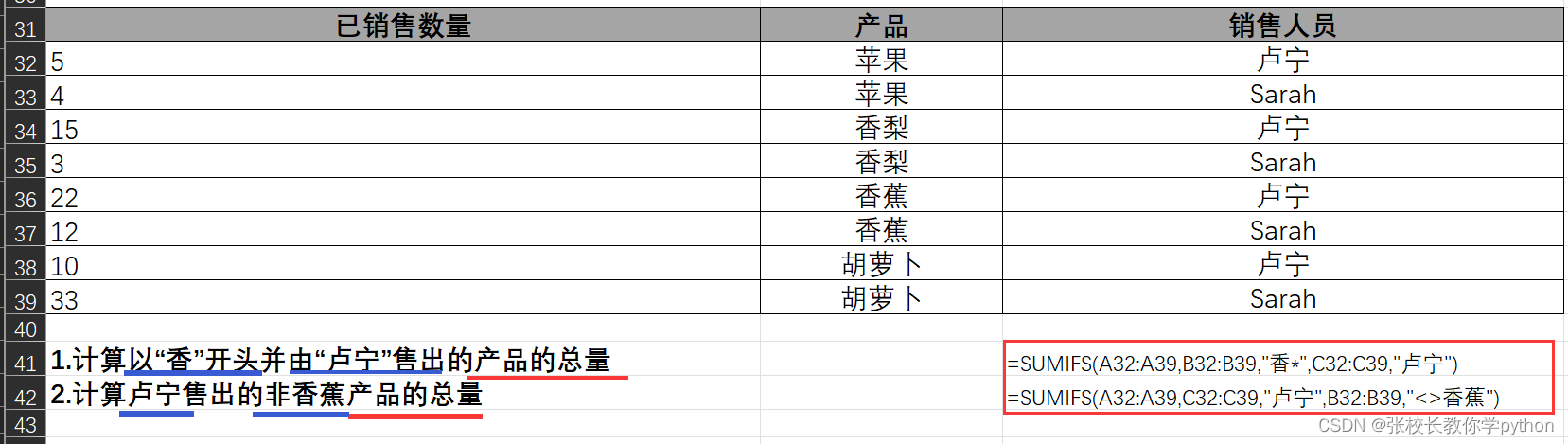

excel中有哪些通配符、excel配置问题,数学函数篇1之sum系列

学习excel前需要明确的是事: 在学习excel函数之前,大家需要明确一件事,excel现在设计到了一些新函数,这些新函数只能存在于office365、office2019及更 新版本之中,所以建议大家在学习时安装较新的版本,…...

工控行业需要熟悉的工业级通信协议

1. Modbus RTU Modbus RTU 是一种串行通信协议,常用于工控行业。它具有以下特点和优势: 采用二进制编码,数据传输更加高效。支持多种传输介质,如RS-232、RS-485等。容易实现和使用,适用于各种设备。具备强大的错误检…...

,带注释)

力扣题解(1030. 距离顺序排列矩阵单元格),带注释

题目描述 链接:点我 注意:多看几遍题目,开始没看懂…相当于计算矩阵网格里面的点(不要计算边界) 我开了题解才明白题的意思 orz… 题解 class Solution {public int[][] allCellsDistOrder(int rows, int cols, int rCenter, …...

每天一道leetcode:剑指 Offer 34. 二叉树中和为某一值的路径(中等图论深度优先遍历递归)

今日份题目: 给你二叉树的根节点 root 和一个整数目标和 targetSum ,找出所有 从根节点到叶子节点 路径总和等于给定目标和的路径。 叶子节点 是指没有子节点的节点。 示例1 输入:root [5,4,8,11,null,13,4,7,2,null,null,5,1], targetSu…...

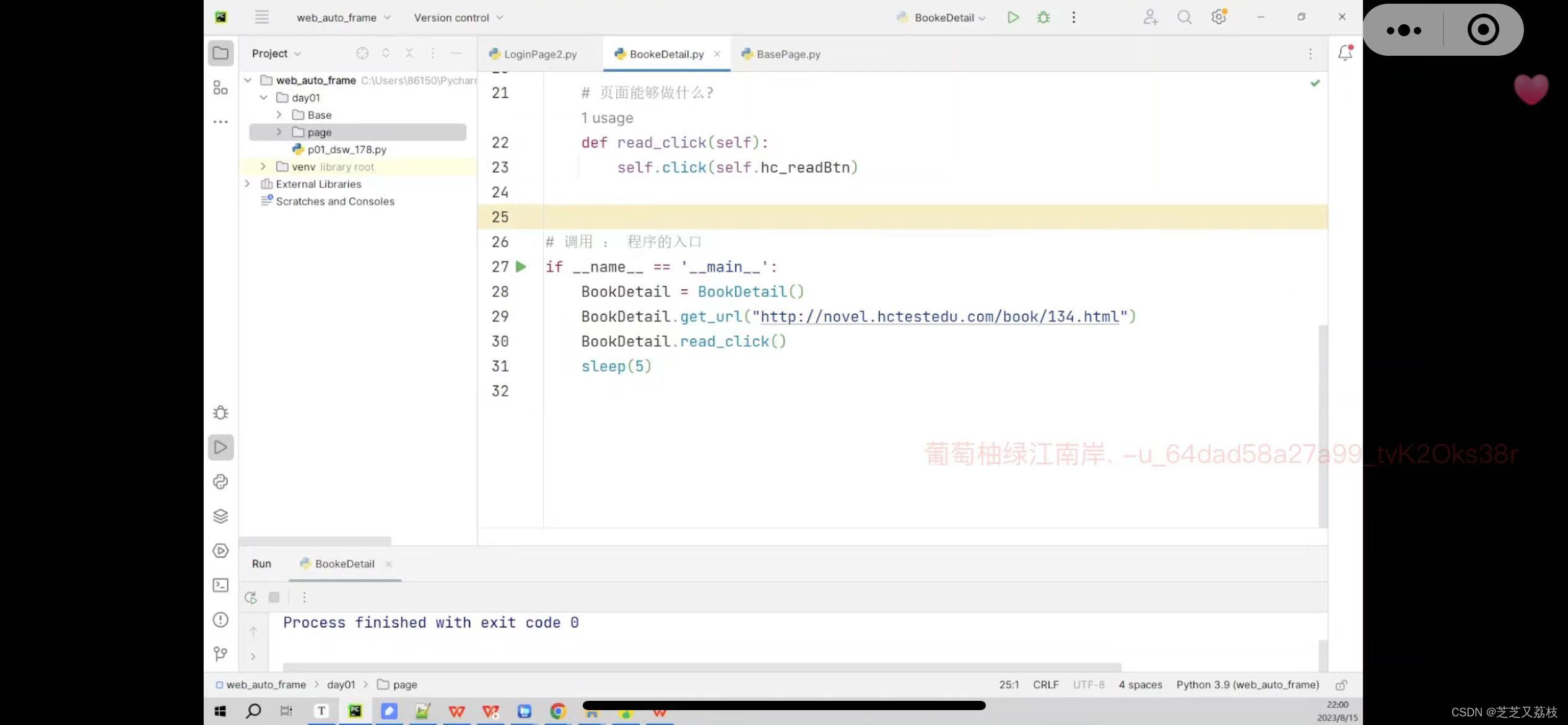

利用POM完成脚本分离实现企业级自动化(POM设计模式+页面的框架封装+测试报告截图)

利用POM完成脚本分离实现企业级自动化(POM设计模式页面的框架封装测试报告截图) 项目-测试-手工测试 项目-测试-手工测试 1.了解需求; 2.编写测试用例(开始)——功能测试组会去做的事情 3.执行测试用例——发送测试报…...

)

云计算——弹性云计算器(ECS)

弹性云服务器:ECS 概述 云计算重构了ICT系统,云计算平台厂商推出使得厂家能够主要关注应用管理而非平台管理的云平台,包含如下主要概念。 ECS(Elastic Cloud Server):即弹性云服务器,是云计算…...

前端倒计时误差!

提示:记录工作中遇到的需求及解决办法 文章目录 前言一、误差从何而来?二、五大解决方案1. 动态校准法(基础版)2. Web Worker 计时3. 服务器时间同步4. Performance API 高精度计时5. 页面可见性API优化三、生产环境最佳实践四、终极解决方案架构前言 前几天听说公司某个项…...

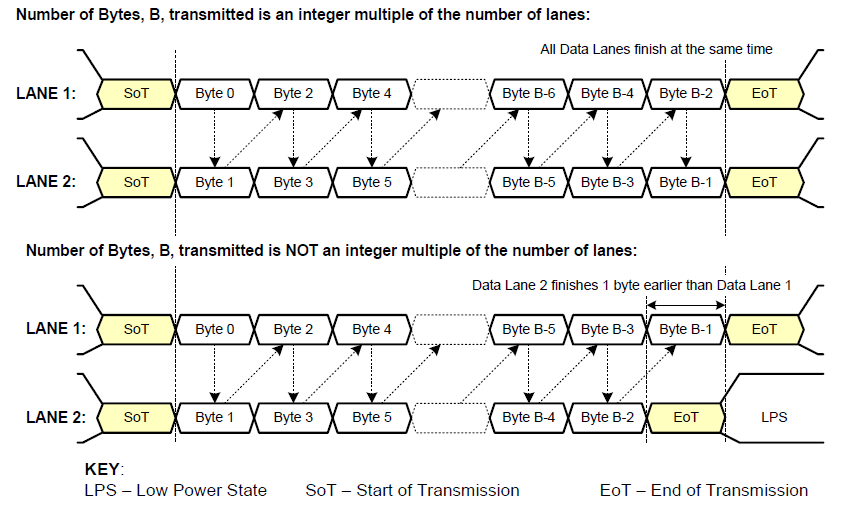

《从零掌握MIPI CSI-2: 协议精解与FPGA摄像头开发实战》-- CSI-2 协议详细解析 (一)

CSI-2 协议详细解析 (一) 1. CSI-2层定义(CSI-2 Layer Definitions) 分层结构 :CSI-2协议分为6层: 物理层(PHY Layer) : 定义电气特性、时钟机制和传输介质(导线&#…...

STM32F4基本定时器使用和原理详解

STM32F4基本定时器使用和原理详解 前言如何确定定时器挂载在哪条时钟线上配置及使用方法参数配置PrescalerCounter ModeCounter Periodauto-reload preloadTrigger Event Selection 中断配置生成的代码及使用方法初始化代码基本定时器触发DCA或者ADC的代码讲解中断代码定时启动…...

ESP32 I2S音频总线学习笔记(四): INMP441采集音频并实时播放

简介 前面两期文章我们介绍了I2S的读取和写入,一个是通过INMP441麦克风模块采集音频,一个是通过PCM5102A模块播放音频,那如果我们将两者结合起来,将麦克风采集到的音频通过PCM5102A播放,是不是就可以做一个扩音器了呢…...

)

OpenLayers 分屏对比(地图联动)

注:当前使用的是 ol 5.3.0 版本,天地图使用的key请到天地图官网申请,并替换为自己的key 地图分屏对比在WebGIS开发中是很常见的功能,和卷帘图层不一样的是,分屏对比是在各个地图中添加相同或者不同的图层进行对比查看。…...

图表类系列各种样式PPT模版分享

图标图表系列PPT模版,柱状图PPT模版,线状图PPT模版,折线图PPT模版,饼状图PPT模版,雷达图PPT模版,树状图PPT模版 图表类系列各种样式PPT模版分享:图表系列PPT模板https://pan.quark.cn/s/20d40aa…...

Spring AI Chat Memory 实战指南:Local 与 JDBC 存储集成

一个面向 Java 开发者的 Sring-Ai 示例工程项目,该项目是一个 Spring AI 快速入门的样例工程项目,旨在通过一些小的案例展示 Spring AI 框架的核心功能和使用方法。 项目采用模块化设计,每个模块都专注于特定的功能领域,便于学习和…...

LOOI机器人的技术实现解析:从手势识别到边缘检测

LOOI机器人作为一款创新的AI硬件产品,通过将智能手机转变为具有情感交互能力的桌面机器人,展示了前沿AI技术与传统硬件设计的完美结合。作为AI与玩具领域的专家,我将全面解析LOOI的技术实现架构,特别是其手势识别、物体识别和环境…...

协议转换利器,profinet转ethercat网关的两大派系,各有千秋

随着工业以太网的发展,其高效、便捷、协议开放、易于冗余等诸多优点,被越来越多的工业现场所采用。西门子SIMATIC S7-1200/1500系列PLC集成有Profinet接口,具有实时性、开放性,使用TCP/IP和IT标准,符合基于工业以太网的…...