【两周学会FPGA】从0到1学习紫光同创FPGA开发|盘古PGL22G开发板学习之DDR3 IP简单读写测试(六)

本原创教程由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处

适用于板卡型号:

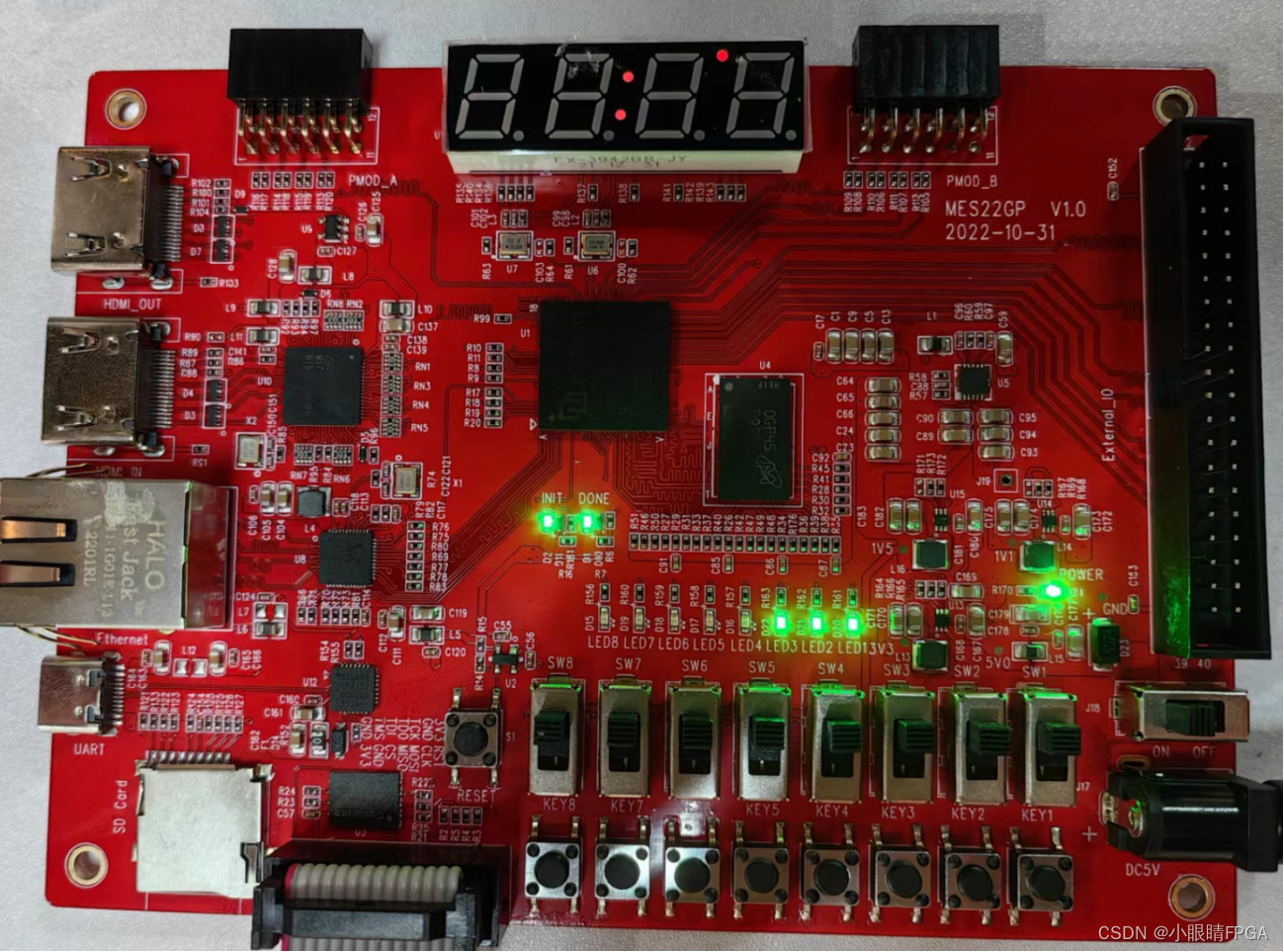

紫光同创PGL22G开发平台(盘古22K)

一:盘古22K开发板(紫光同创PGL22G开发平台)简介

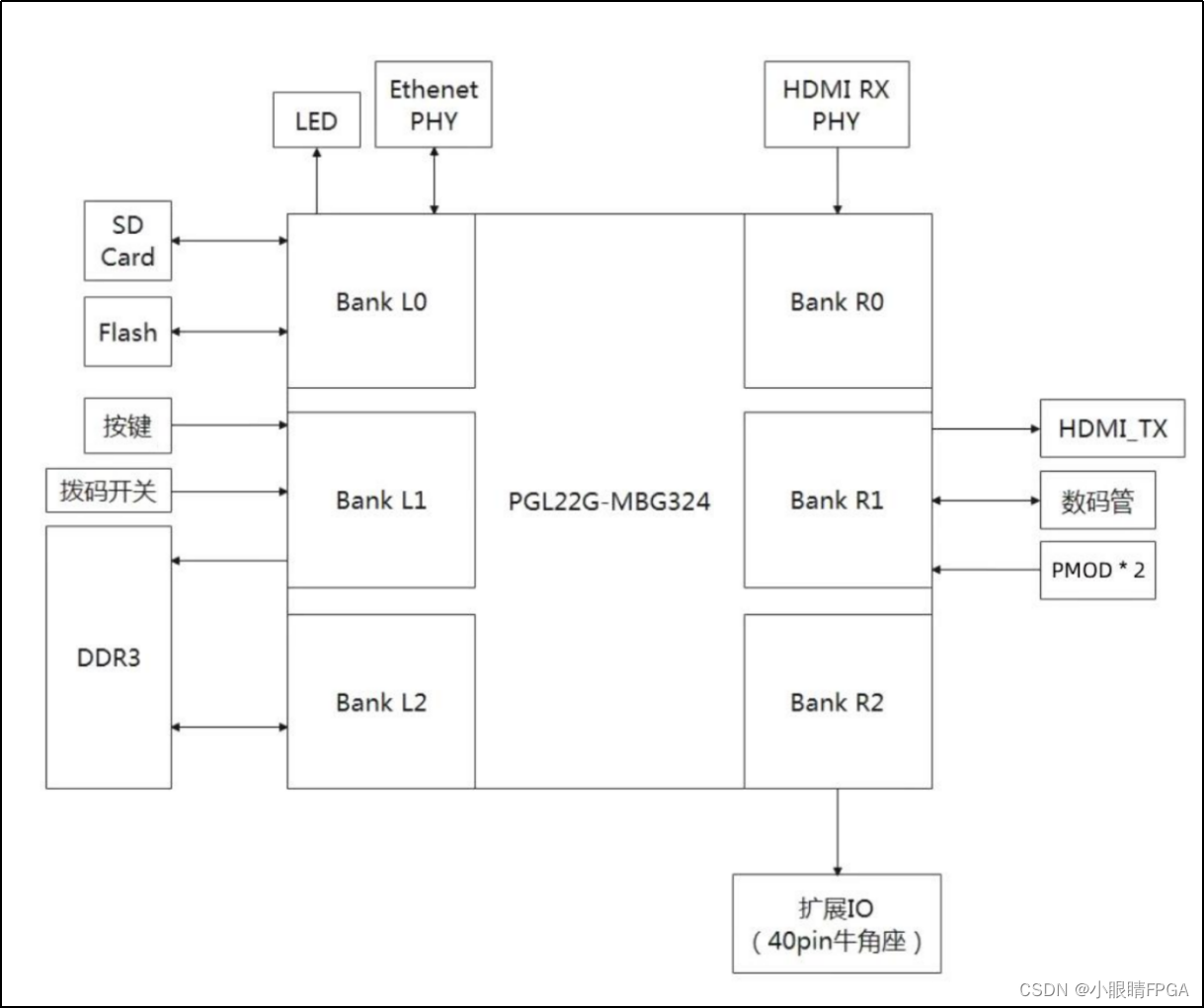

盘古22K开发板是基于紫光同创Logos系列PGL22G芯片设计的一款FPGA开发板,全面实现国产化方案,板载资源丰富,高容量、高带宽,外围接口丰富,不仅适用于高校教学,还可以用于实验项目、项目开发,一板多用,满足多方位的开发需求。

二:实验目的

MES22GP 开发板上有一片 Micron 的 DDR3(MT41K256M16 TW107:P)内存组件,拥有 16bit 位宽的存储空间(MT41J系列是旧的产品,目前很多型号已经停产,后续替代就是MT41K系列。硬件上的差异是MT41K支持1.35V低电压,同时也兼容1.5V电压,所以可以用MT41K直接替换相应型号的MT41J芯片)。该DDR3 存储系统直接连接到了 PGL22G 的 Bank L1 及 Bank L2 上。PGL22G的DDR IP为硬核IP,需选择正确的IP添加。

本次实验目的为生成DDR3 IP,实现DDR3的基于AXI4的简单读写控制,了解其工作原理和用户接口,然后通过在线Debugger工具查看写入和读出的数据是否一致。

三:DDR3控制器简介

HMIC_H IP 是深圳市紫光同创电子有限公司FPGA 产品中用于实现对SDRAM 读写而设计的IP,通过公司Pango Design Suite 套件(后文简称PDS)中IP Compiler 工具(后文简称IPC)例化生成IP 模块。

HMIC_H IP 系统框图如下图所示:

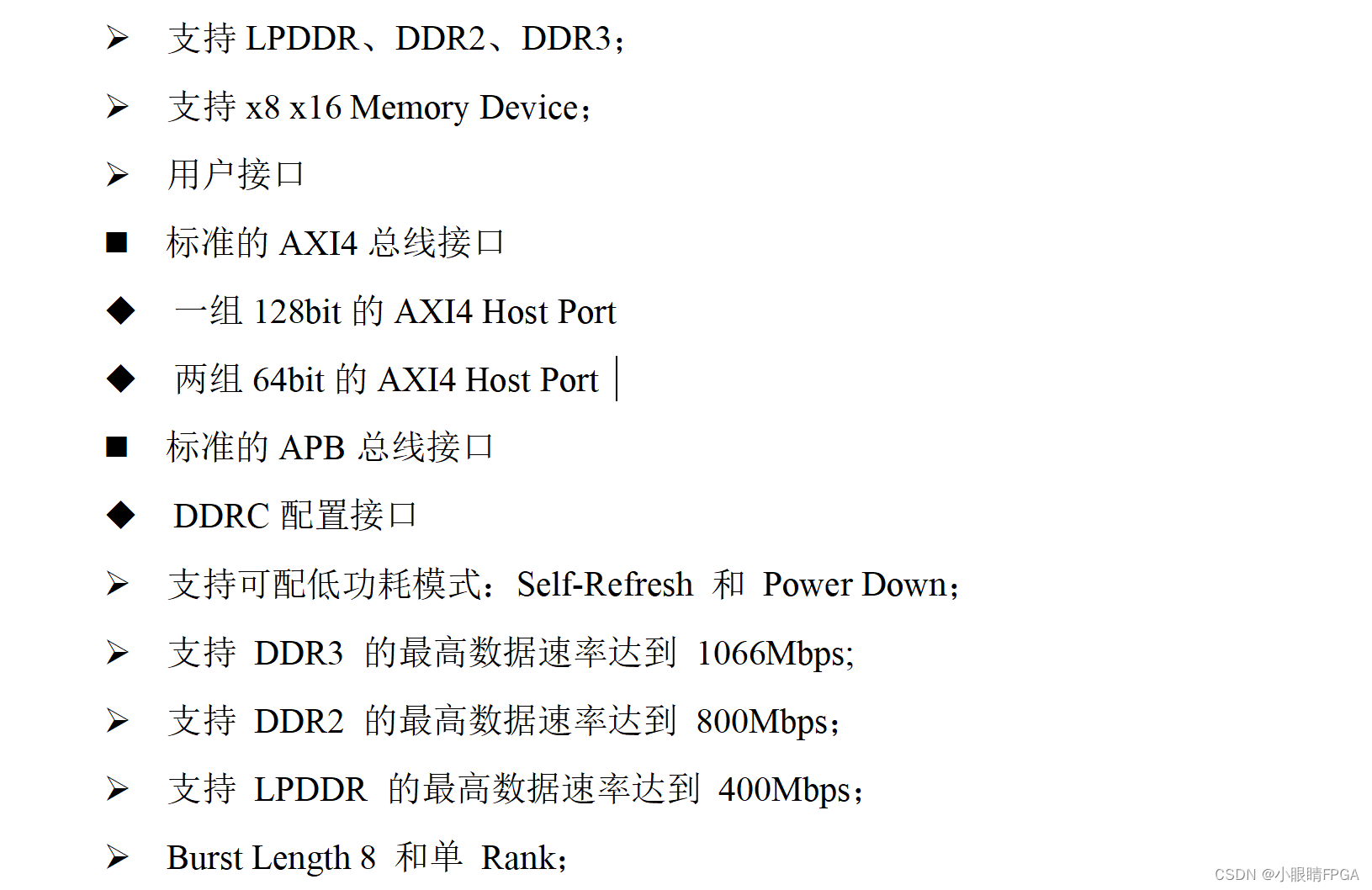

HMIC_H IP 包括了DDR Controller、DDR PHY 和 PLL,用户通过 AXI4 接口实现数据的 读写,通过 APB 接口可配置 DDR Controller 内部寄存器,PLL 用于产生需要的各种时钟。

AXI4 接口:HMIC_H IP 提供三组 AXI4 Host Port:AXI4 Port0(128bit)、AXI4 Port1(64bit)、

AXI4 Port2(64bit)。用户通过 HMIC_H IP 界面可以选择使能这三组 AXI4 Port。三组 AXI4 Host Port 均为标准 AXI4 接口。

APB 接口:HMIC_H IP 提供一个 APB 配置接口,通过该接口,可配置 DDR Controller 内部寄存器。HMIC_H IP 初始化完成后使能该接口。

详细的端口说明请点击IP配置界面的View Datasheet查看IP手册。

DDR的IP需要手动添加,操作流程请查阅文件目录1_Demo_document/工具使用篇的《03_IP核安装与查看用户指南》。

DDR3 IP例化流程简述

打开IPC 软件,进入 IP 选择界面,如下图所示,选取 System/DDR/Hard 目录下的 Logos HMIC_H,然后在右侧页面设置 Instance Name 名称,并选择 FPGA 的器件类型。

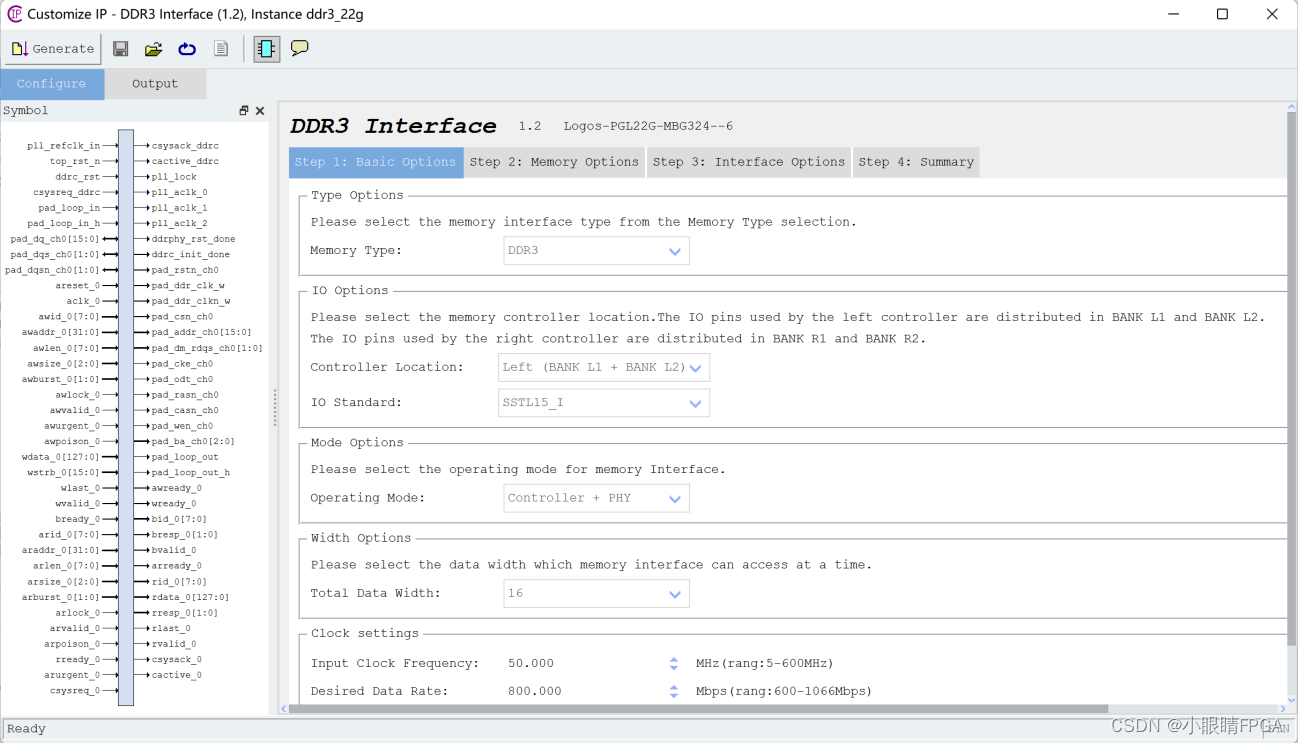

IP 选择完成后点击Customize 进入Logos HMIC_H IP 参数设置界面,如下图所示,左边Symbol 为接口框图,右边为参数配置窗口:

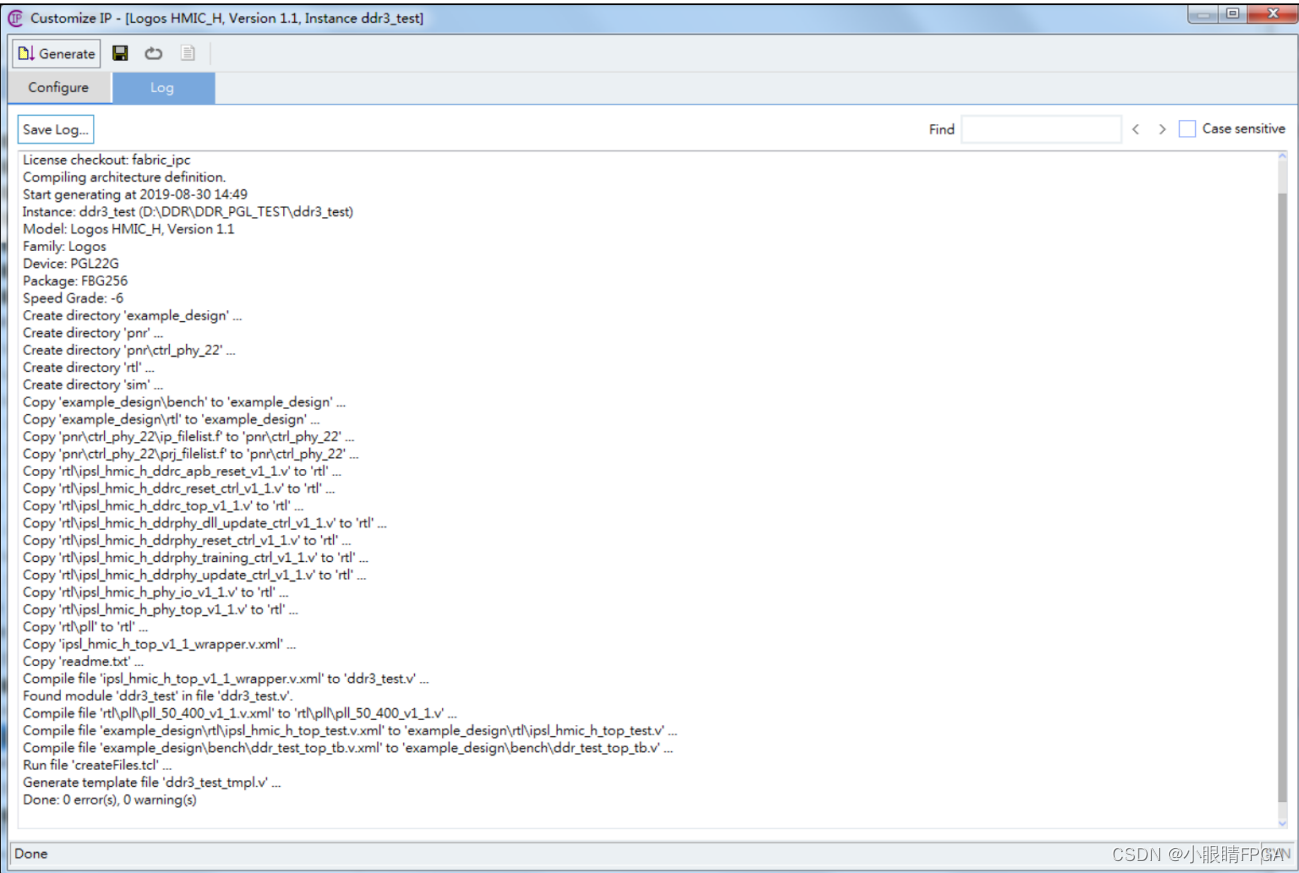

参数配置完成后点击左上角的Generate按钮,生成 IP,即可生成相应于用户特定设置的 HMIC_H IP 代码。生成 IP 的信息报告界面如下图所示:

注 : IP 自带生成的.pds 文件和.fdc 文件仅供参考,需要根据实际单板进行修改。成功生成 IP 后会在生产IP时指定的Pathname 路径下输出如下文件:

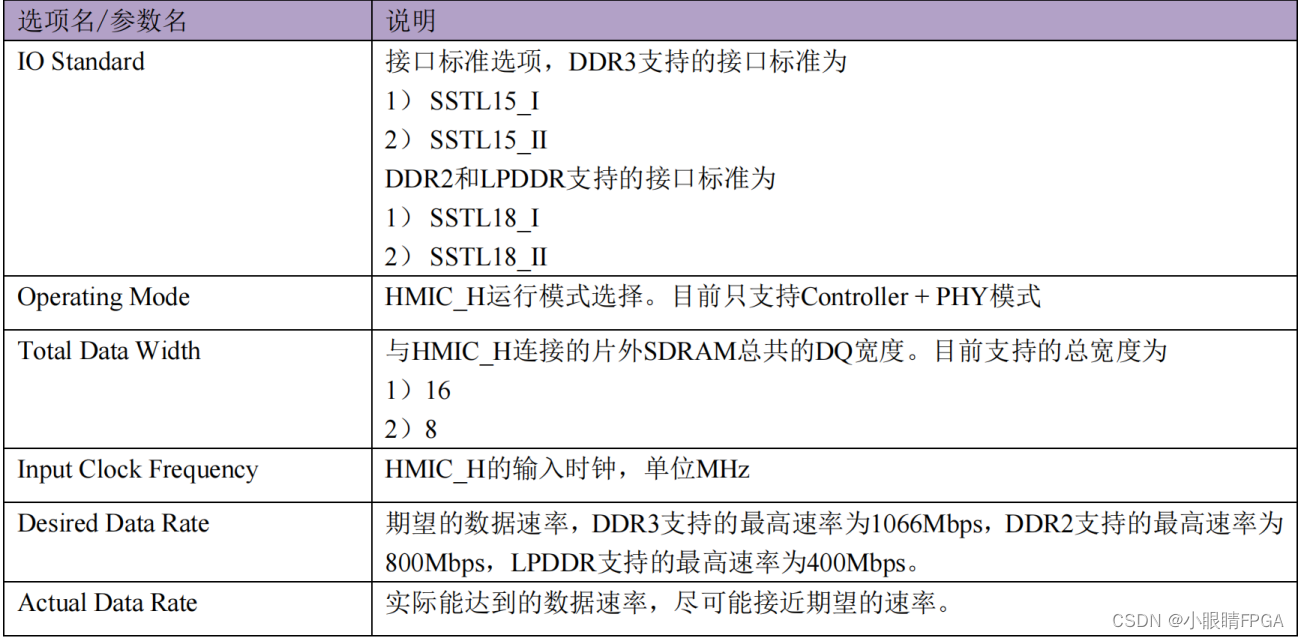

DDR3 IP配置说明

HMIC_H IP 配置分为四个页面,分别为 Step1: Basic Options,Step2: Memory Options,Step3: Interface Options,Step4: Summary,请务必按照该页面顺序配置。

Step 1: Basic Options

是 IP 的基本配置页面,页面如下图所示:

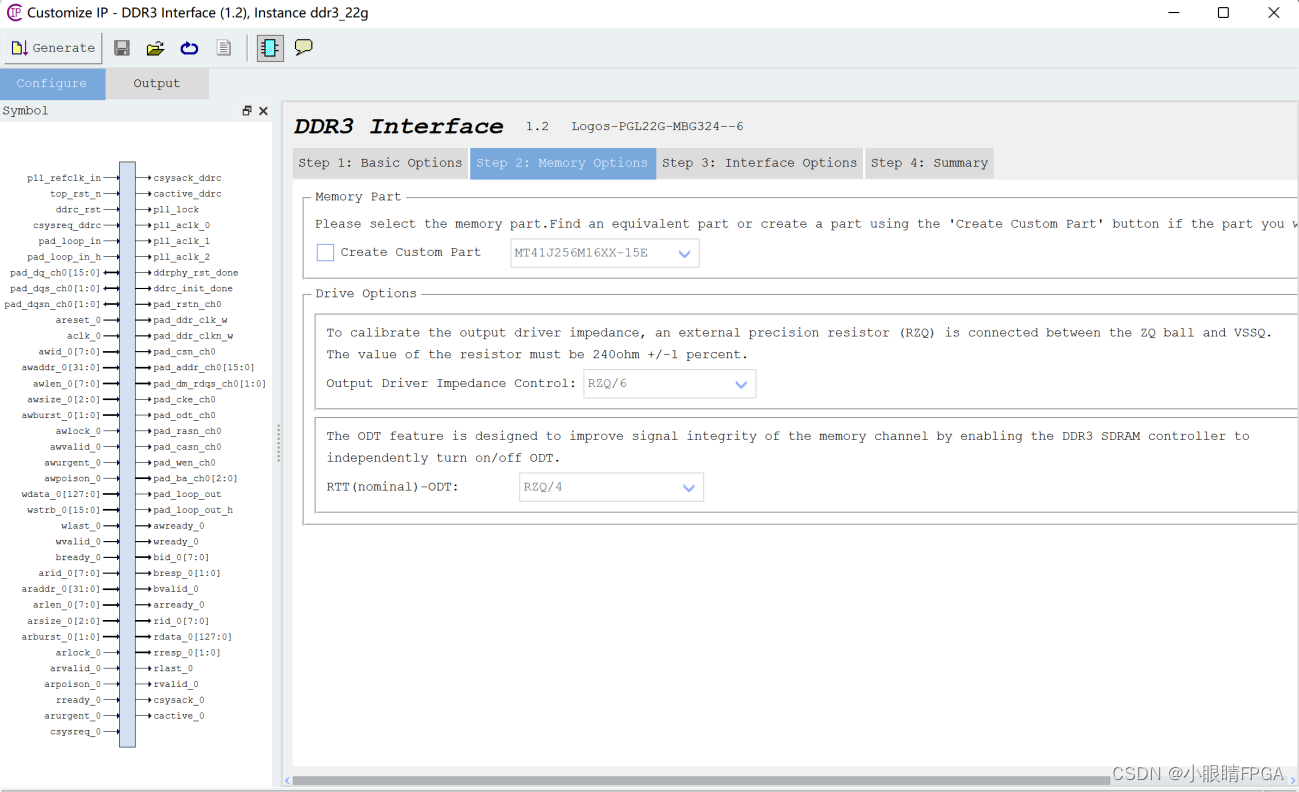

Step 2: Memory Options

是Memory 参数的配置页面,页面如下图所示:

Step 3: Interface Options

是接口参数的配置页面,页面如下图所示:

Step 4: Summary

用于打印当前的配置信息,不需要配置参数,页面如下图所示:

四: 实验源码

DDR3 IP配置完成后会生成一个可用于例化的模块。

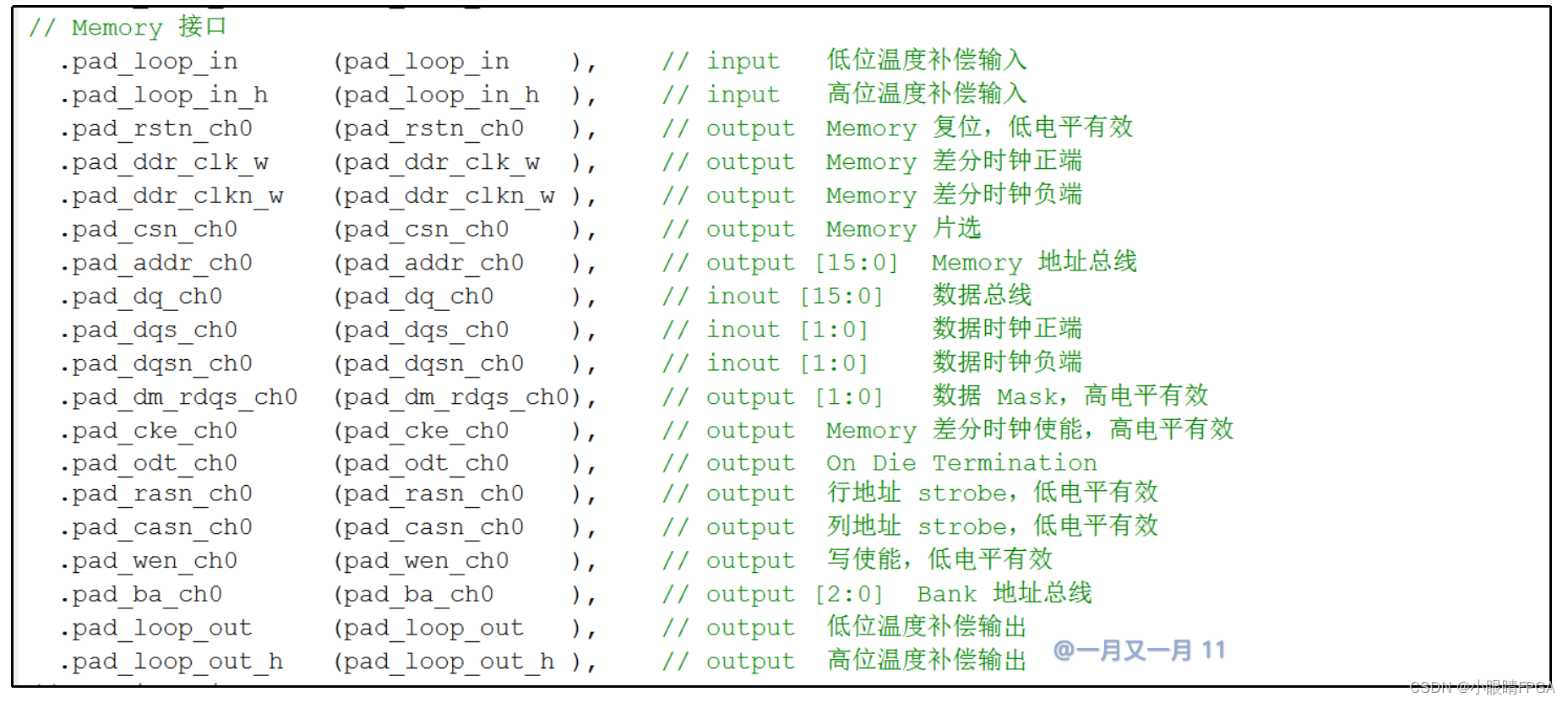

DDR3 IP 模块接口说明

如下图所示为DDR3 IP的Memory Interface(PHY),不需要我们直接操作。

以下所示为外部输入时钟,复位,输出的用户时钟axi4 port0/port1/port2以及一些复位或者初始化完成的标志信号(可以通过连接LED灯来直观显示,更易观察)。

以下所示为AXI4协议的读写控制端口,也是用户可以直接操作用于控制DDR3读写的端口。

AXI4协议的读写控制这里不进行具体讲解。

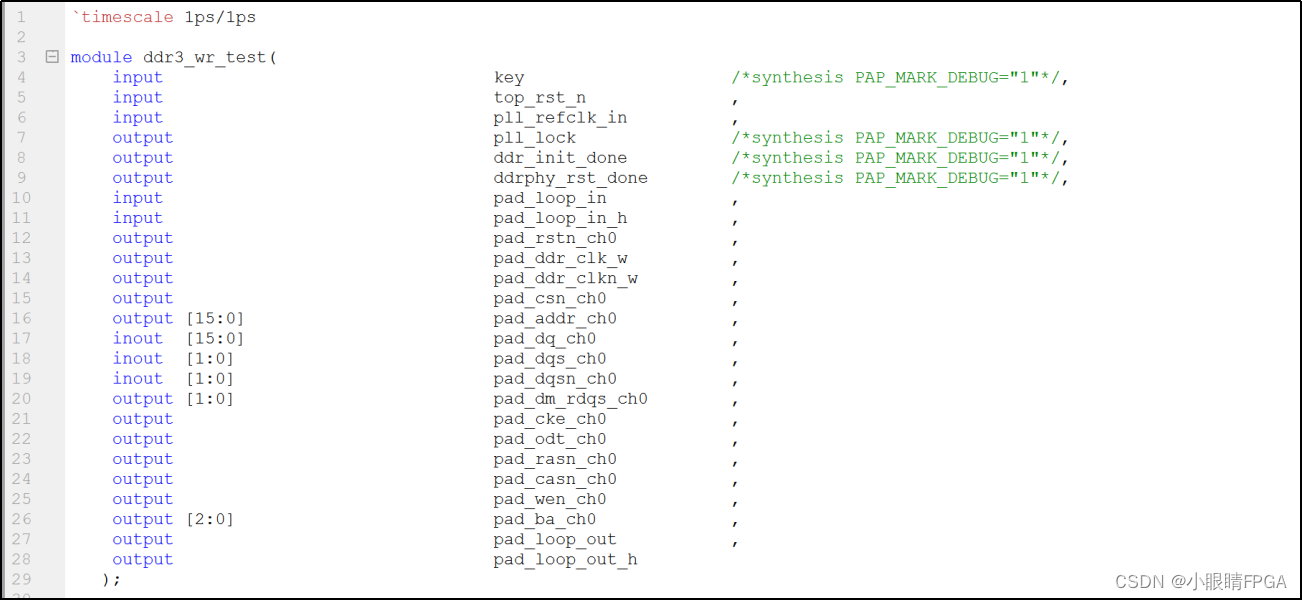

DDR3 读写测试顶层模块设计

顶层模块的输入输出端口便是DDR3例化模块中的Memory Interface(PHY)和一些直连LED灯的用于观察的标志信号,因为本次实验通过按键来控制开始向DDR3写入数据,所以还需要一个输入按键。

然后对应DDR3的AXI4读写我们单独用一个模块来控制,顶层模块中的例化如下所示。

使用按键,所以需要一个按键消抖模块,顶层模块中的例化如下所示。

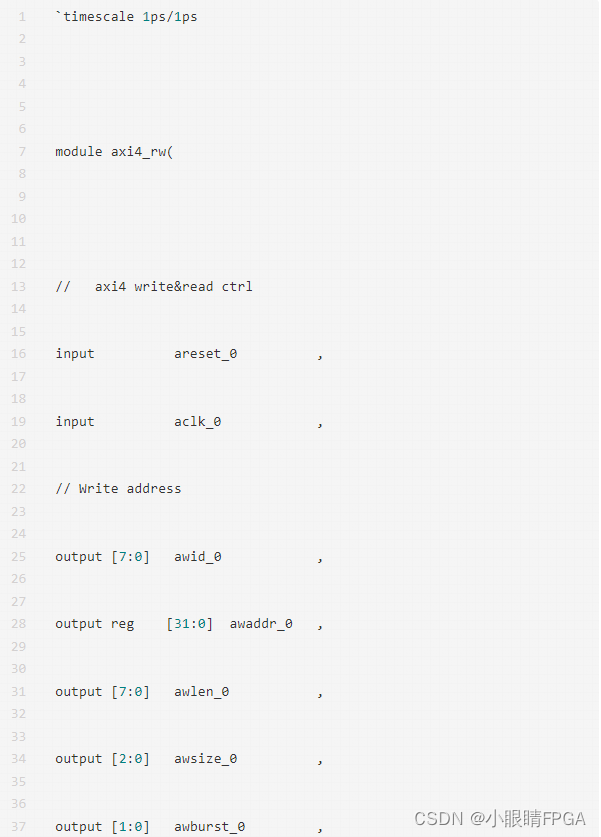

DDR3 AXI4读写控制模块

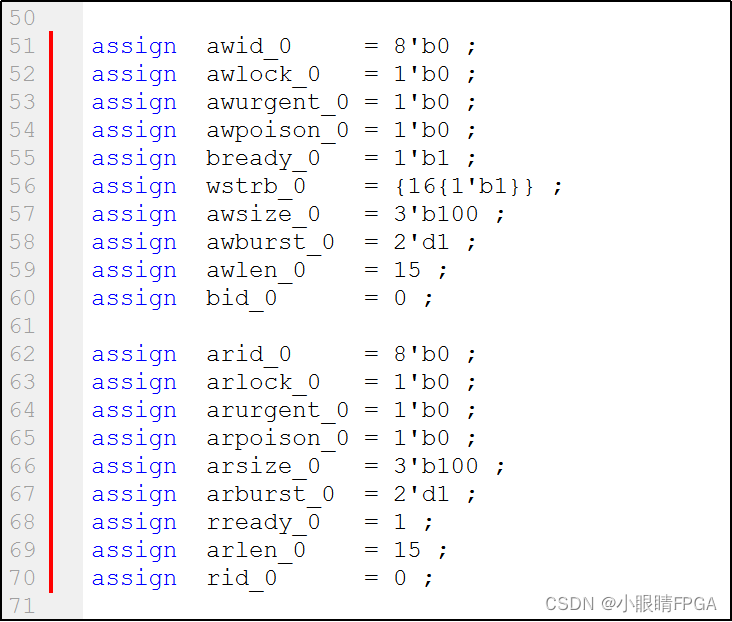

本次实验只是一个简单的读写测试实验,故可以将一些AXI4的信号配置为常量。

使用按键控制数据开始写入DDR3,通过一个移位寄存器来产生这个写标志。

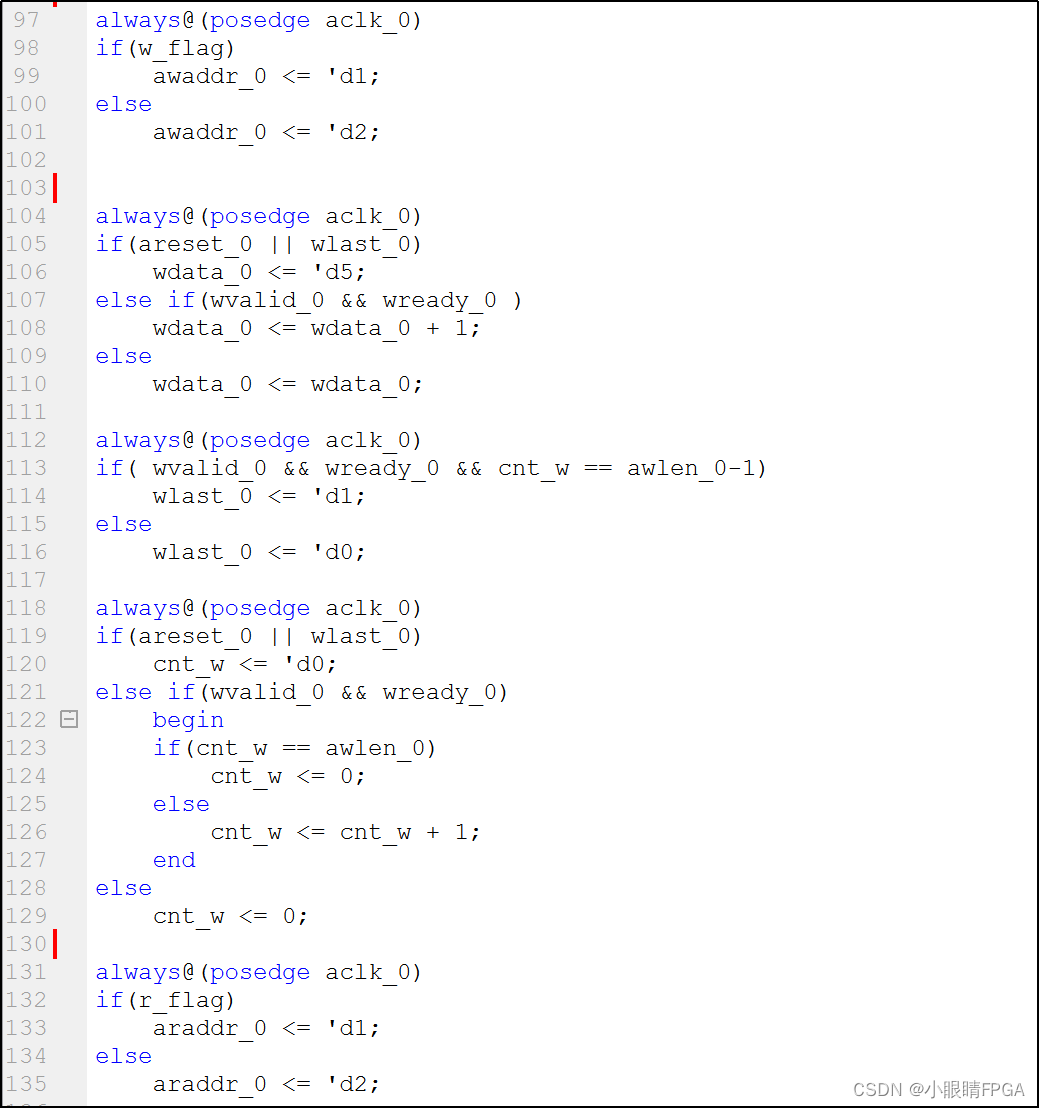

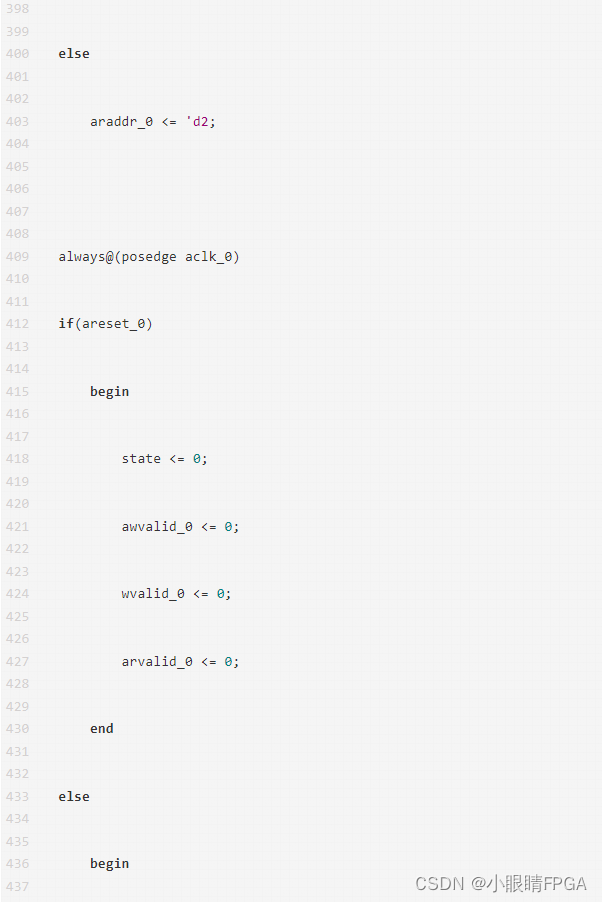

使用状态机来控制写地址信号,写数据信号,读地址信号,读数据信号的产生及状态的切换和跳转。

当按键按下,写标志触发,状态机进入写地址状态,awvalid_0信号为高电平,当awready_0和awvalid_0同时为高电平时,写地址被有效写入,下一个周期awvalid_0为低电平同时状态机跳转到写数据的状态;

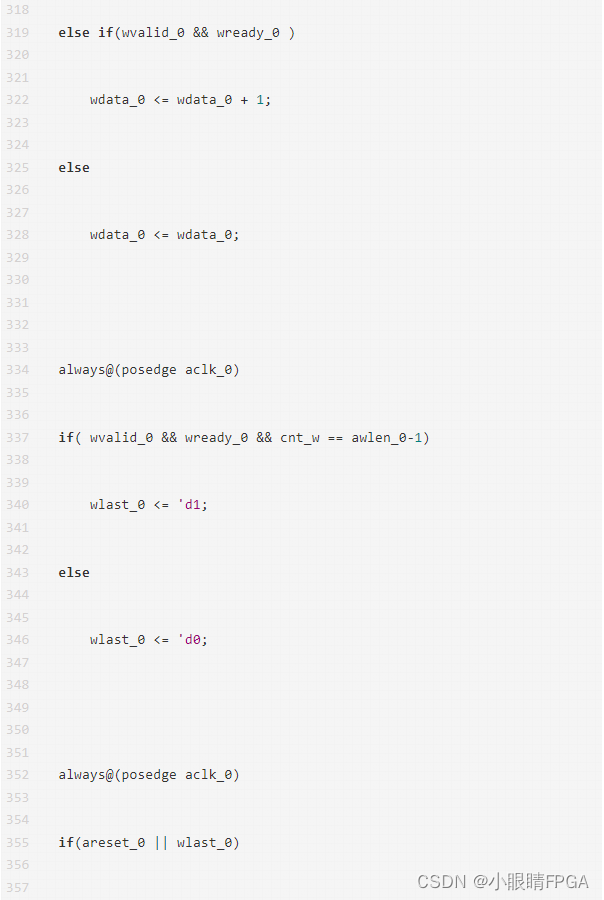

写数据状态中,wvalid_0为高电平,当wready_0和wvalid_0同时为高电平时,数据开始被写入,一共写入5~20总计16个数据(从0开始计数长度便为15)。当写到最后一个数据时wlast_0保持一个周期的高电平。这里我们用一个计数器来产生写入数据,当wready_0和wvalid_0同时为高电平时开始计数器开始自加,当计数到15时(最后一个写入数据),下一个周期计数器清零,状态机跳转至等待写响应的状态;

写响应的状态中,通过一个移位寄存器抓取写响应有效bvalid_0信号为高电平的时刻,当bvalid_0且bresp_0为2’b00(表示写响应ok)时触发读开始的标志,状态机进入读地址写入状态;

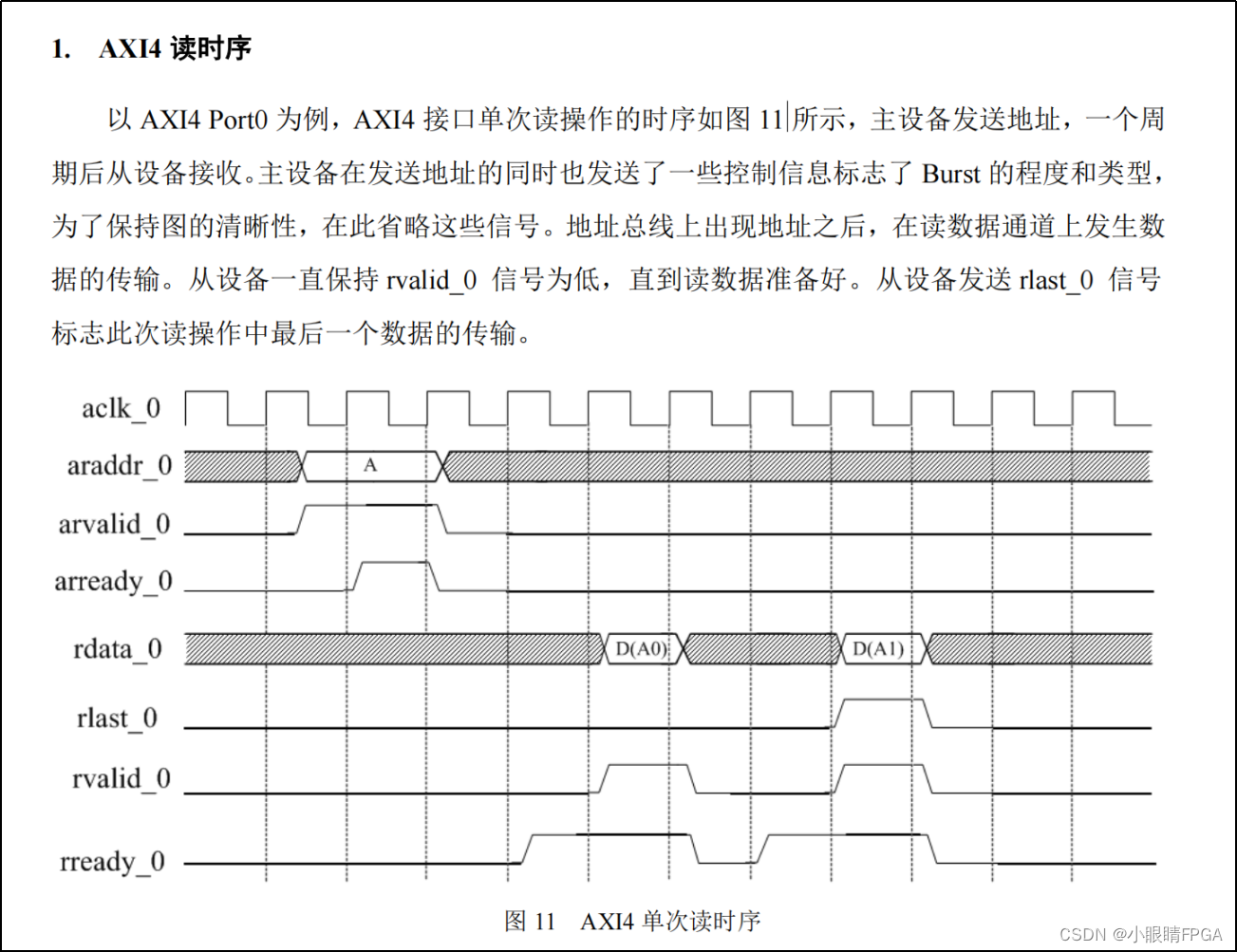

读地址写入状态中,arvalid_0为高电平,当arready_0和arvalid_0同时为高电平时,读地址被有效写入(地址与写数据地址一致),下一个周期arvalid_0为低电平同时状态机跳转到读数据的状态;

读数据状态中,当rvalid_0 和 rready_和 rlast_0均为高电平时,状态机跳转至最初的状态等待按键被再次按下。读出的数据可以通过在线调试Debugger工具来查看。

DDR3 IP的时钟约束

IP 有 5 个时钟,分别为 pll_refclk_in、phy_clk、pll_aclk0、pll_aclk1、pll_aclk2、pll_pclk,其中 pll_refclk_in 是输入时钟,phy_clk、pll_aclk0、pll_aclk1、pll_aclk2、pll_pclk 都是 PLL 倍频得到,phy_clk 用作 HMIC_H 硬核的输入时钟,pll_aclk0 用做 AXI4 port0 的输入时钟,pll_aclk1 用做 AXI4 port1 的输入时钟,pll_aclk2 用做 AXI4 port2 的输入时钟,pll_pclk 用做APB port的输入时钟。phy_clk 是HMIC_H专用时钟,在IP内部使用,不允许外接使用。pll_pclk,pll_aclk_0,pll_aclk_1,pll_aclk_2 四路时钟供外部逻辑使用,彼此没有相位关系,都是异步时钟。

外部输入时钟约束如下。

Pll产生的时钟约束如下。

五:实验现象

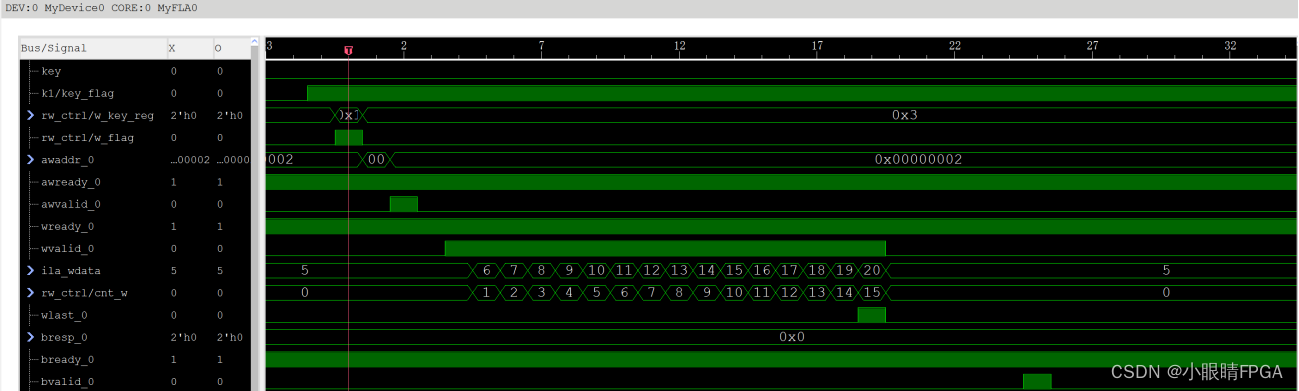

点击Debugger按钮,下载程序,便可通过Debugger工具进行在线调试,查看具体信号的波形情况。

按下开发板的按键,产生写触发信号,awvalid_0信号为高电平,当awready_0和awvalid_0同时为高电平时,awvalid_0拉低同时进入写数据状态,wvalid_0拉高,随后wready_0和wvalid_0同时为高电平时开始写入数据5~20,wlast_0在写入最后一个数据时拉高。一段时间后bvalid_0拉高且bresp_0为2’b00,表示写入数据成功,然后进入读数据状态。

读地址写入状态中,arvalid_0为高电平,当arready_0和arvalid_0同时为高电平时,读地址被有效写入(地址与写数据地址一致),下一个周期arvalid_0拉低同时状态机跳转到读数据的状态。

通过Debugger工具查看DDR3先写入后读出的数据是一致的,表明DDR3的读写测试正常。

同时在烧录程序后,可以观察LED灯的亮灭情况来查看DDR的PLL输出的时钟是否已经稳定,DDR PHY复位是否完成和DDR的控制器是否初始化成功。

ddr3 axi4 读写控制模块源码如下:

相关文章:

【两周学会FPGA】从0到1学习紫光同创FPGA开发|盘古PGL22G开发板学习之DDR3 IP简单读写测试(六)

本原创教程由深圳市小眼睛科技有限公司创作,版权归本公司所有,如需转载,需授权并注明出处 适用于板卡型号: 紫光同创PGL22G开发平台(盘古22K) 一:盘古22K开发板(紫光同创PGL22G开发…...

第6章 内核模块符号导出实验(iTOP-RK3568开发板驱动开发指南 )

在上一小节中,给大家讲解了驱动模块传参实验,使用insmod命令加载驱动时可以进行参数的传递,但是每一个内核模块之间是相互独立的,那模块间的符号传递要怎样进行呢,让我们带着疑问来进行本章节的学习吧! 6.…...

第二种方法)

Android12.0首次开机默认授予app运行时权限(去掉运行时授权弹窗)第二种方法

1.概述 在12.0的系统产品开发中,在6.0以后对于权限的申请,都需要动态申请,所以会在系统首次启动后,在app的首次运行时,会弹出授权窗口,会让用户手动授予app运行时权限,在由于系统产品开发需要要求默认授予app运行时权限,不需要用户默认授予运行时弹窗,所以需要在首次开…...

conda和Python的虚拟环境如何结合使用,以及二者之间到底有什么区别?

问题描述 今天在复现streamlit的代码时(参考Streamlit 讲解专栏(一):安装以及初步应用),根据这篇博文指导,要先用以下指令创建一个虚拟环境: # 创建虚拟环境(使用venv&a…...

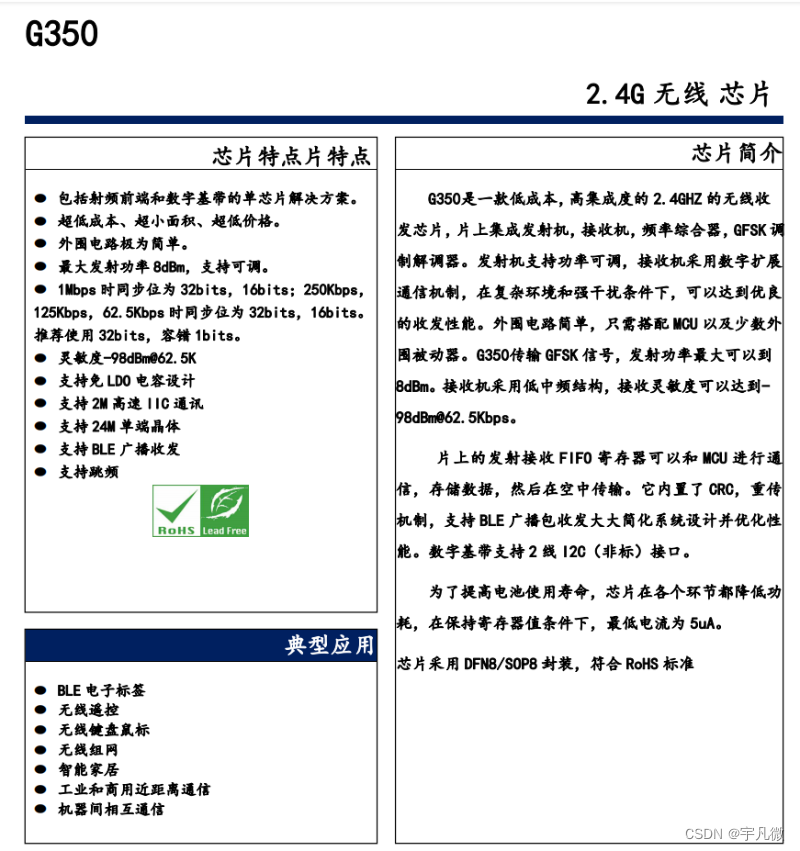

宇凡微YE09合封芯片,集成高性能32位mcu和2.4G芯片

合封芯片是指将主控芯片和外部器件合并封装的芯片,能大幅降低开发成本、采购成本、减少pcb面积等等。宇凡微YE09合封芯片,将技术领域推向新的高度。这款高度创新性的芯片融合了32位MCU和2.4G芯片,为各种应用场景提供卓越的功能和性能。 32位M…...

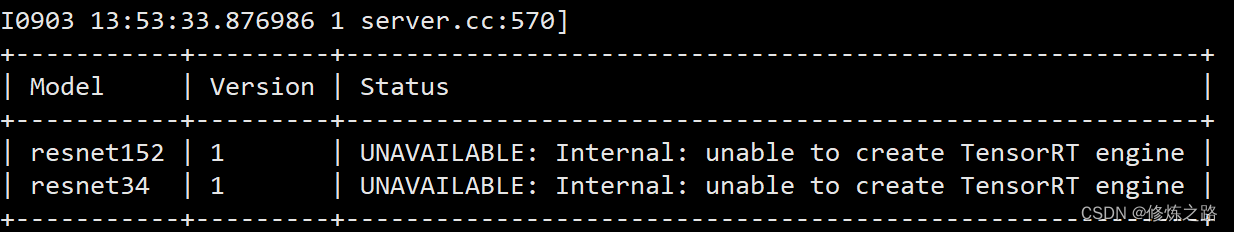

使用perf_analyzer和model-analyzer测试tritonserver的模型性能超详细完整版

导读 当我们在使用tritonserver部署模型之后,通常需要测试一下模型的服务QPS的能力,也就是1s我们的模型能处理多少的请求,也被称为吞吐量。 测试tritonserver模型服务的QPS通常有两种方法,一种是使用perf_analyzer 来测试&#…...

docker 部署springboot(成功、截图)

1.新建sringboot工程并打包 2.编写Dockerfile文件 # 基础镜像使用java FROM openjdk:8 # 作者 MAINTAINER feng # VOLUME 指定了临时文件目录为/tmp。 # 其效果是在主机 /var/lib/docker 目录下创建了一个临时文件,并链接到容器的/tmp VOLUME /tmp # 将jar包添加…...

VMware ubuntu空间越用越大

前言 用Ubuntu 1604编译了RK3399的SDK,之后删了一些多余的文件,df - h 已用21G,但window硬盘上还总用了185GB,采用了碎片整理,压缩无法解决 1 启动Ubuntu后, 安装 VMware Tools(T) 、 2 打开ubuntu终端,压…...

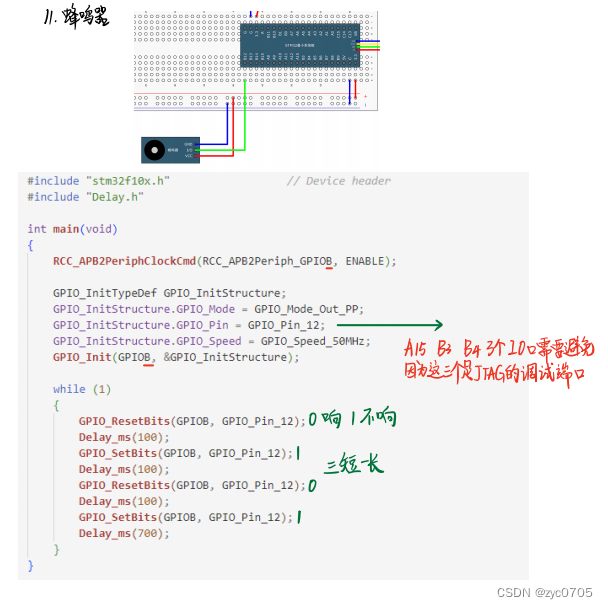

stm32 学习笔记:GPIO输出

一、GPIO简介 引脚电平 0-3.3V,部分可容忍5V,对输出而言最大只能输出3.3V, 只要可以用高低电平来控制的地方,都可以用GPIO来完成,如果控制的功率比较大的设备,只需加入驱动电路即可 GPIO 通用输入输出口,可配置为 8种 …...

css换行

强制显示一行,超出... .box{white-space: nowrap; /* 强制显示一行 */overflow: hidden;text-overflow: ellipsis; /* 超出... */ } 自动换行 一般默认制动换行 .box1{word-wrap:break-word; } 显示2行,超出... .box2 {overflow: hidden;display: -…...

面试算法-常用数据结构

文章目录 数据结构数组链表 栈队列双端队列树 1)算法和数据结构 2)判断候选人的标准 算法能力能够准确辨别一个程序员的功底是否扎实 数据结构 数组 链表 优点: 1)O(1)时间删除或者添加 灵活分配内存空间 缺点: 2&…...

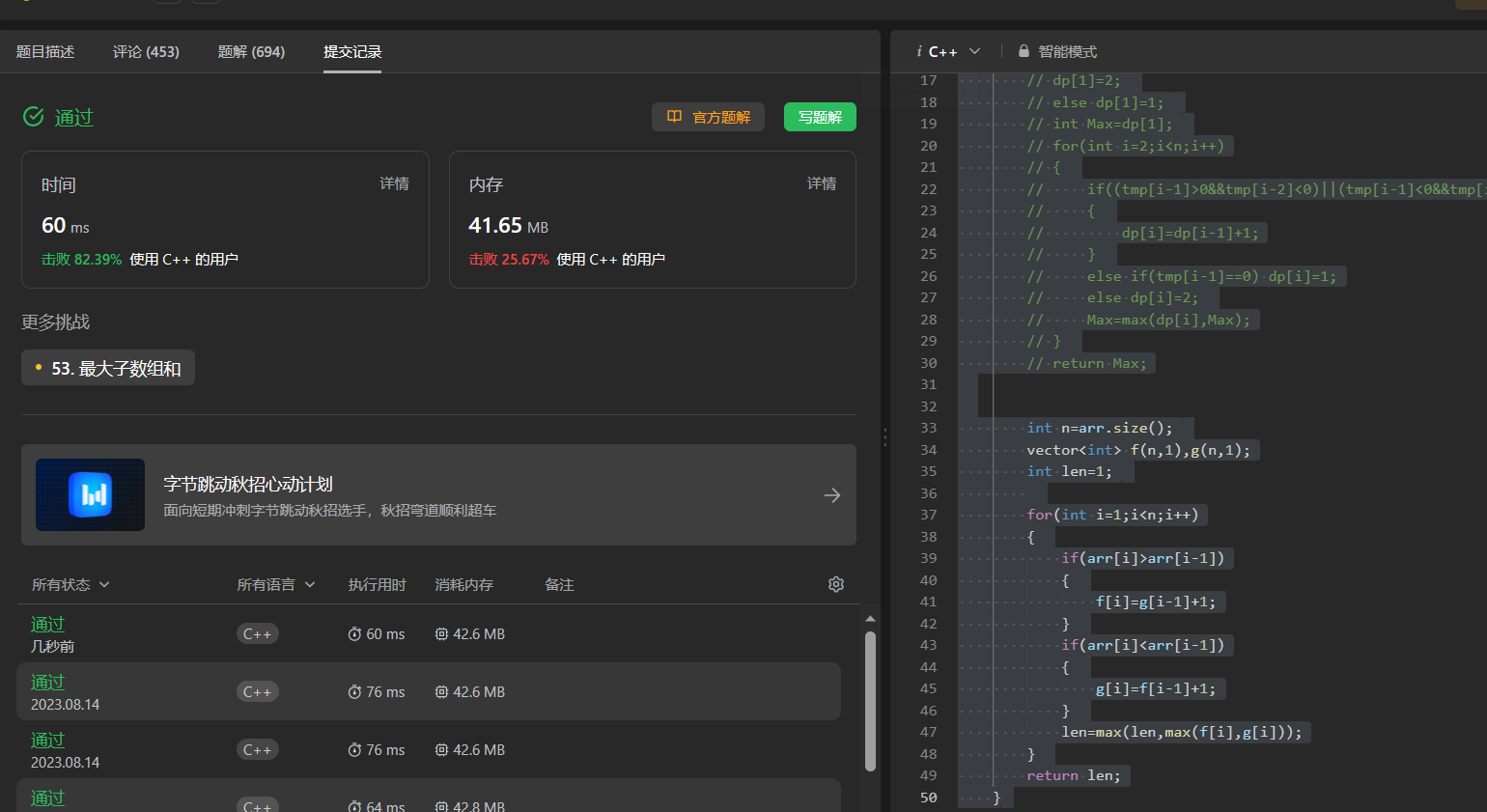

【动态规划刷题 10】等差数列划分 最长湍流子数组

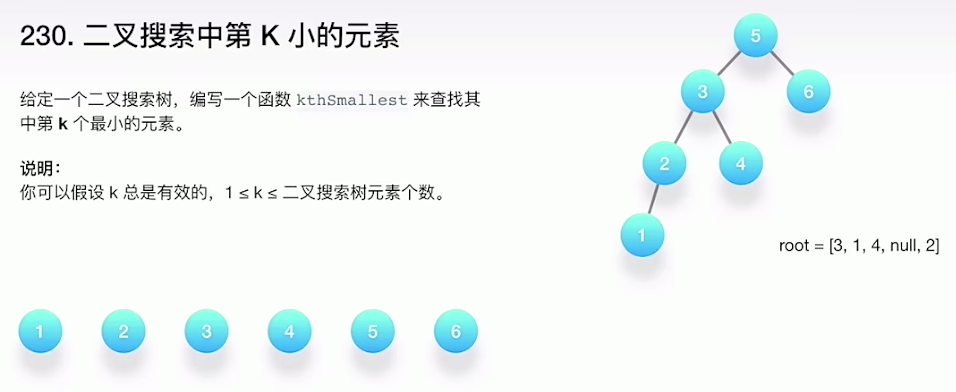

413. 等差数列划分 链接: 413. 等差数列划分 如果一个数列 至少有三个元素 ,并且任意两个相邻元素之差相同,则称该数列为等差数列。 例如,[1,3,5,7,9]、[7,7,7,7] 和 [3,-1,-5,-9] 都是等差数列。 给你一个整数数组 nums ,返回…...

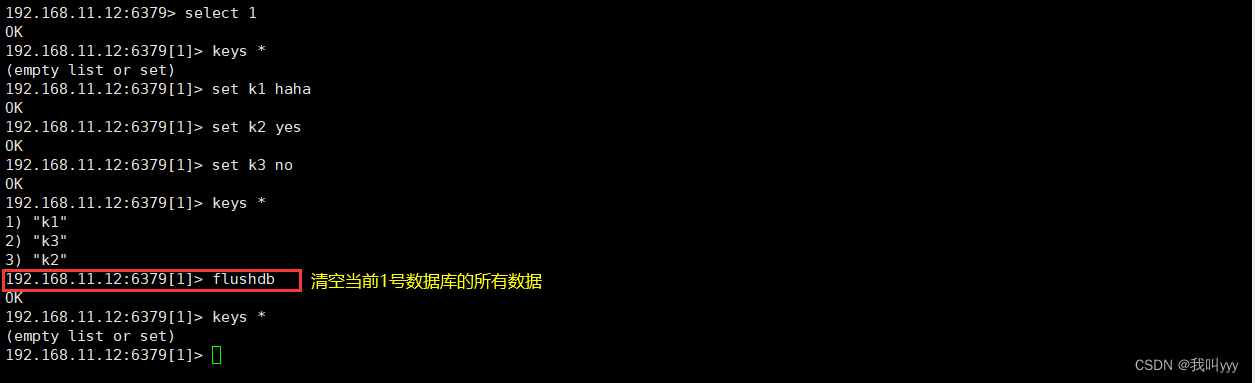

redis 配置与优化

目录 一、关系数据库和非关系型数据库 二、关系型数据库和非关系型数据库区别 三、非关系型数据库产生背景 四、redis 1、概念 2、redis的优点 3、redis为什么这么快 五、redis安装与配置 一、关系数据库和非关系型数据库 关系型数据库:关系型数据库是一个结…...

数据结构例题代码及其讲解-递归与树

树 树的很多题目中都包含递归的思想 递归 递归包括递归边界以及递归式 即:往下递,往上归 递归写法的特点:写起来代码较短,但是时间复杂度较高 01 利用递归求解 n 的阶乘。 int Func(int n) {if (n 0) {return 1;}else …...

Jenkins | 流水线构建使用expect免密交互时卡住,直接退出

注意: expect 脚本必须以 interact 或 expect eof 结束。 原因: interact:使用interact会保持在终端而不会退回到原终端,所以就卡在这里。 expect eof:expect脚本默认的是等待10s,当执行完命令后,自动切回…...

git修改默认分支

git checkout 分支 切换到当前分支 git branch --set-upstream-toorigin/complete(远程分支名) 设置当前分支的上游分支为远程分支complete git branch --unset-upstream master 取消master上游分支的身份 现在,使用git commit,git push 命令可以直接…...

Android Studio开发入门教程:如何更改APP的图标?

更改APP的图标(安卓系统) 环境:Windows10、Android Studio版本如下图、雷电模拟器。 推荐图标库 默认APP图标 将新图标拉进src/main/res/mipmap-hdpi文件夹(一般app的icon图标是存放在mipmap打头的文件夹下的) 更改sr…...

MATLAB/Python的编程教程: 匹配滤波器的实现

MATLAB/Python的编程教程: 匹配滤波器的实现 注1:本文系“MATLAB/Python的编程教程”系列之一,致力于使用Python和Matlab实现特定的功能。本次要实现的功能是:匹配滤波器的实现。 匹配滤波器,这是一个在信号处理领域常见的主题,主要用于增强特定信号的检测性能,特别是在噪…...

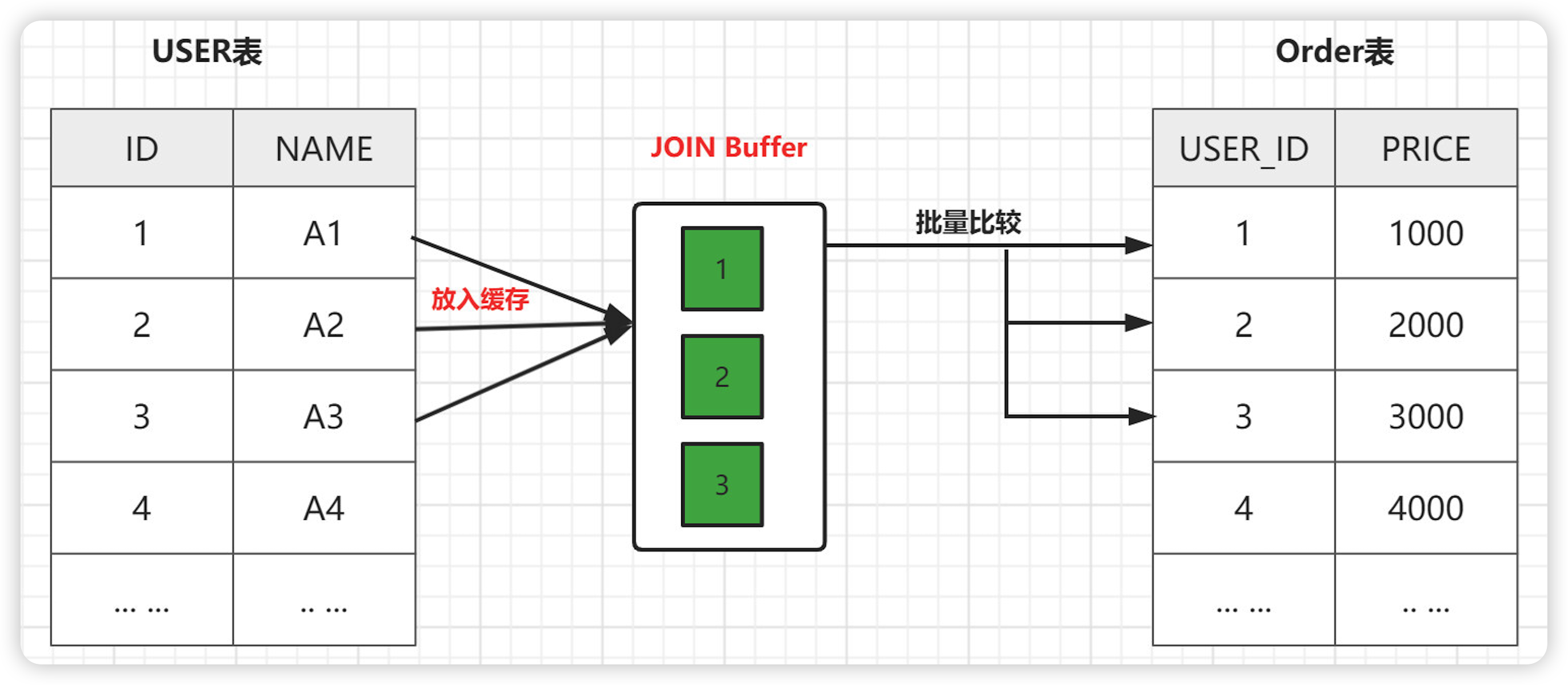

java八股文面试[数据库]——JOIN优化

JOIN 是 MySQL 用来进行联表操作的,用来匹配两个表的数据,筛选并合并出符合我们要求的结果集。 JOIN 操作有多种方式,取决于最终数据的合并效果。常用连接方式的有以下几种: 什么是驱动表 ? 多表关联查询时,第一个被处理的表就是驱动表,使用…...

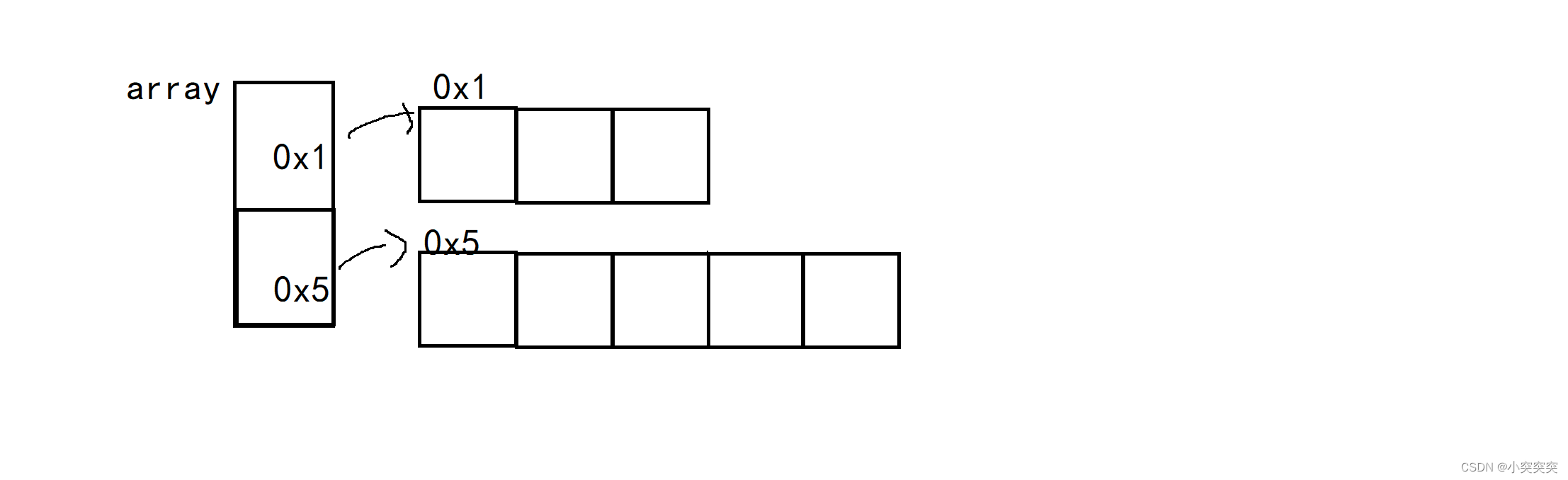

Java语法中一些需要注意的点(仅用于个人学习)

1.当字符串和其他类型相加时,基本都是字符串,这与运算顺序有关。 2.Java中用ctrl d 来结束循环输入。 3.nextLine() 遇到空格不会结束。 4.方法重载 4.1. 方法名必须相同 4.2. 参数列表必须不同(参数的个数不同、参数的类型不同、类型的次序必须不…...

23-Oracle 23 ai 区块链表(Blockchain Table)

小伙伴有没有在金融强合规的领域中遇见,必须要保持数据不可变,管理员都无法修改和留痕的要求。比如医疗的电子病历中,影像检查检验结果不可篡改行的,药品追溯过程中数据只可插入无法删除的特性需求;登录日志、修改日志…...

连锁超市冷库节能解决方案:如何实现超市降本增效

在连锁超市冷库运营中,高能耗、设备损耗快、人工管理低效等问题长期困扰企业。御控冷库节能解决方案通过智能控制化霜、按需化霜、实时监控、故障诊断、自动预警、远程控制开关六大核心技术,实现年省电费15%-60%,且不改动原有装备、安装快捷、…...

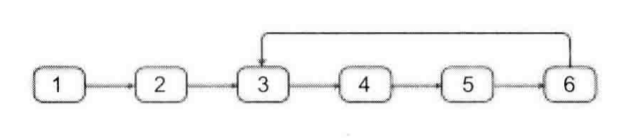

剑指offer20_链表中环的入口节点

链表中环的入口节点 给定一个链表,若其中包含环,则输出环的入口节点。 若其中不包含环,则输出null。 数据范围 节点 val 值取值范围 [ 1 , 1000 ] [1,1000] [1,1000]。 节点 val 值各不相同。 链表长度 [ 0 , 500 ] [0,500] [0,500]。 …...

Java多线程实现之Callable接口深度解析

Java多线程实现之Callable接口深度解析 一、Callable接口概述1.1 接口定义1.2 与Runnable接口的对比1.3 Future接口与FutureTask类 二、Callable接口的基本使用方法2.1 传统方式实现Callable接口2.2 使用Lambda表达式简化Callable实现2.3 使用FutureTask类执行Callable任务 三、…...

【git】把本地更改提交远程新分支feature_g

创建并切换新分支 git checkout -b feature_g 添加并提交更改 git add . git commit -m “实现图片上传功能” 推送到远程 git push -u origin feature_g...

基于Springboot+Vue的办公管理系统

角色: 管理员、员工 技术: 后端: SpringBoot, Vue2, MySQL, Mybatis-Plus 前端: Vue2, Element-UI, Axios, Echarts, Vue-Router 核心功能: 该办公管理系统是一个综合性的企业内部管理平台,旨在提升企业运营效率和员工管理水…...

Module Federation:Webpack.config.js文件中每个属性的含义解释)

MFE(微前端) Module Federation:Webpack.config.js文件中每个属性的含义解释

以Module Federation 插件详为例,Webpack.config.js它可能的配置和含义如下: 前言 Module Federation 的Webpack.config.js核心配置包括: name filename(定义应用标识) remotes(引用远程模块࿰…...

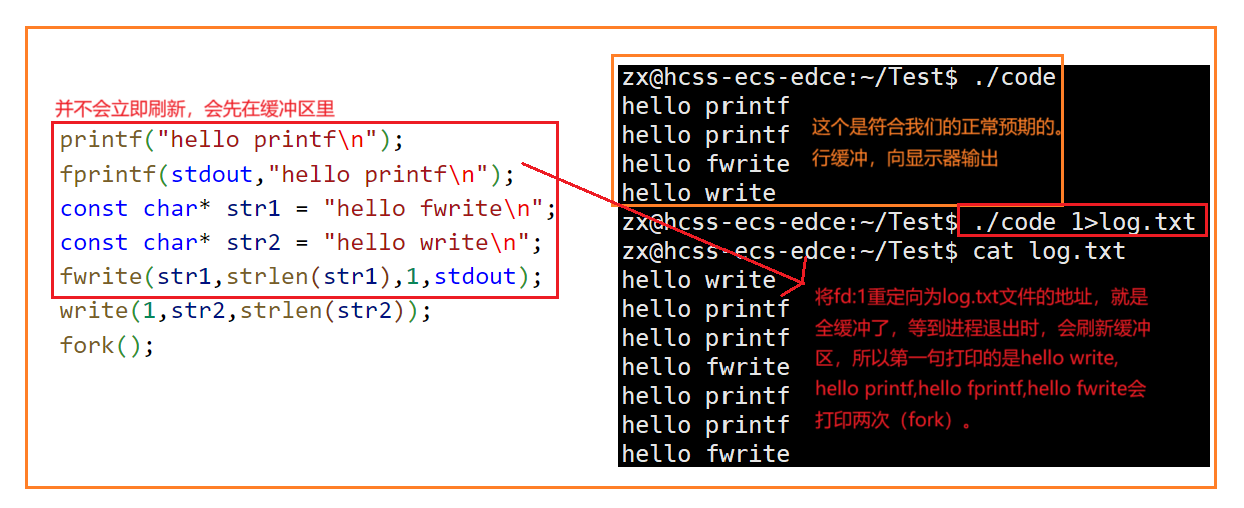

Linux中《基础IO》详细介绍

目录 理解"文件"狭义理解广义理解文件操作的归类认知系统角度文件类别 回顾C文件接口打开文件写文件读文件稍作修改,实现简单cat命令 输出信息到显示器,你有哪些方法stdin & stdout & stderr打开文件的方式 系统⽂件I/O⼀种传递标志位…...

Ubuntu系统多网卡多相机IP设置方法

目录 1、硬件情况 2、如何设置网卡和相机IP 2.1 万兆网卡连接交换机,交换机再连相机 2.1.1 网卡设置 2.1.2 相机设置 2.3 万兆网卡直连相机 1、硬件情况 2个网卡n个相机 电脑系统信息,系统版本:Ubuntu22.04.5 LTS;内核版本…...

ubuntu系统文件误删(/lib/x86_64-linux-gnu/libc.so.6)修复方案 [成功解决]

报错信息:libc.so.6: cannot open shared object file: No such file or directory: #ls, ln, sudo...命令都不能用 error while loading shared libraries: libc.so.6: cannot open shared object file: No such file or directory重启后报错信息&…...