FPGA project :HDMI

实验目标:驱动HdMI显示十色等宽彩条。

本实验的重点是:

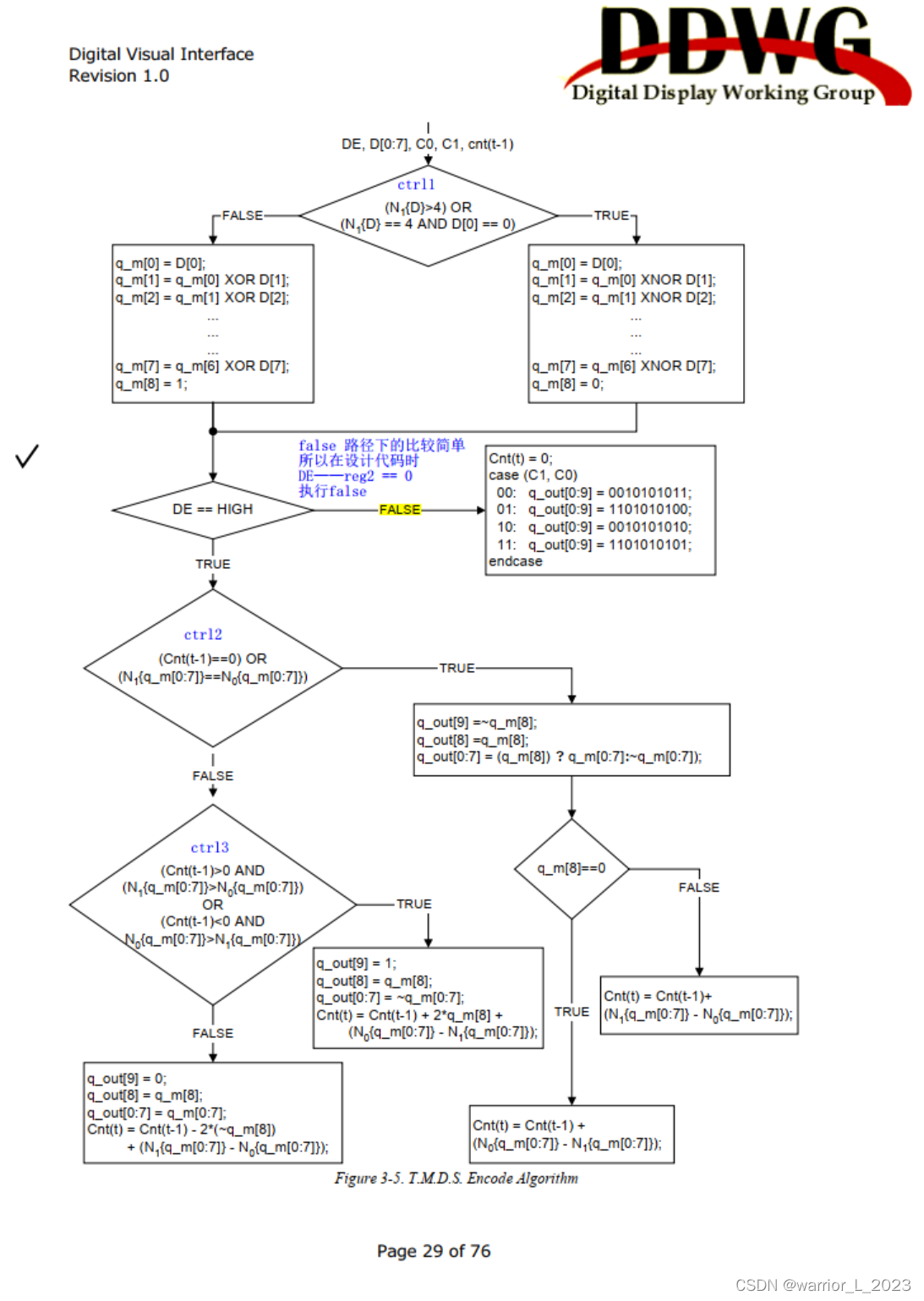

1掌握TMDS通信协议。

2rgb565转rgb888。

3编写HDMI驱动程序。

4学会看流程图编写代码。

值得注意的事情

1注意数据与解析数据的信号(比如传入的数据中0或者1的个数),要在时序上与数据进行对齐。

如果解析数据的信号是时序信号,那么它将会滞后数据一个clk。如果后面要用到,数据与对应的解析数据的信号同时做条件,那么需要对数据进行打一拍处理。用打拍过后的数据与解析数据的信号作为条件去做判断。

2如果一个数据是有符号位的,那么判断它的正负,就不能用简单的 > 0 来判断。

比如本实验中cnt就是5位宽的有符号数,判断其正负(cnt[4] == 1) 为负数;(cnt[4] == 0) 为正数。如果是cnt < 0 表述负数的话,那么cnt永远不会被判定为负数。

看仿真波形的经验之谈:

1在本实验与官方的编码模块代码,那么在通过功能方正,验证自己编写的编码模块代码是否正确时,可以把官方的模块例化进工程,然后仿真对比波形是否一致,即可判断自己编写的代码是否正确。

2在遇到不一致的时候,比如输入信号都一致,某个输出信号不一致。

先不要着急看去检查哪些信号会直接影响这个输出信号赋值,因为前面的一些信号,会间接影响输出信号赋值。比如影响直接影响输出信号赋值的信号。

那么此时应该先检查一些直接受输入信号影响的信号,是否正确,是否和官方给的代码波形一致;

然后再看一些”条件“波形是否正确;

也就是说由输入信号逐渐到输出信号这个过程中一次产生(你编写代码的顺序)去检查这些信号是否正确。(自顶向下)。慢慢检查。

3实在检查不出来,看看自己的代码和官方的代码编写的差在哪里。

TMDS通信协议:

一种传输视频/音频/辅助数据的传输技术:最小化传输差分信号。

采用DIV编码。附上几张图:

8bit像素信息到最小化传输直流均衡10bit数据,编码流程:

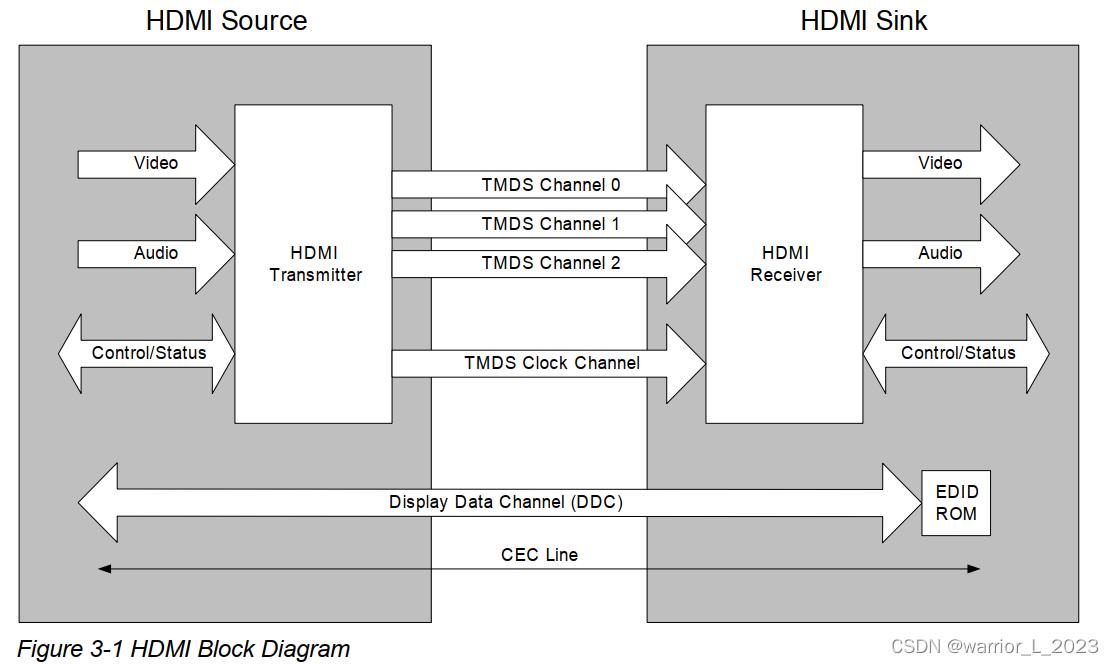

信源端与接收端的数据传输框图:由图可知,3路差分信号传输,由rgb888转10bit的数据。一路差分信号传输clock。

下面两路ddc信号是从接收端读取硬件工作模式相关信息的,本实验没有用到。(IIC通信协议。)

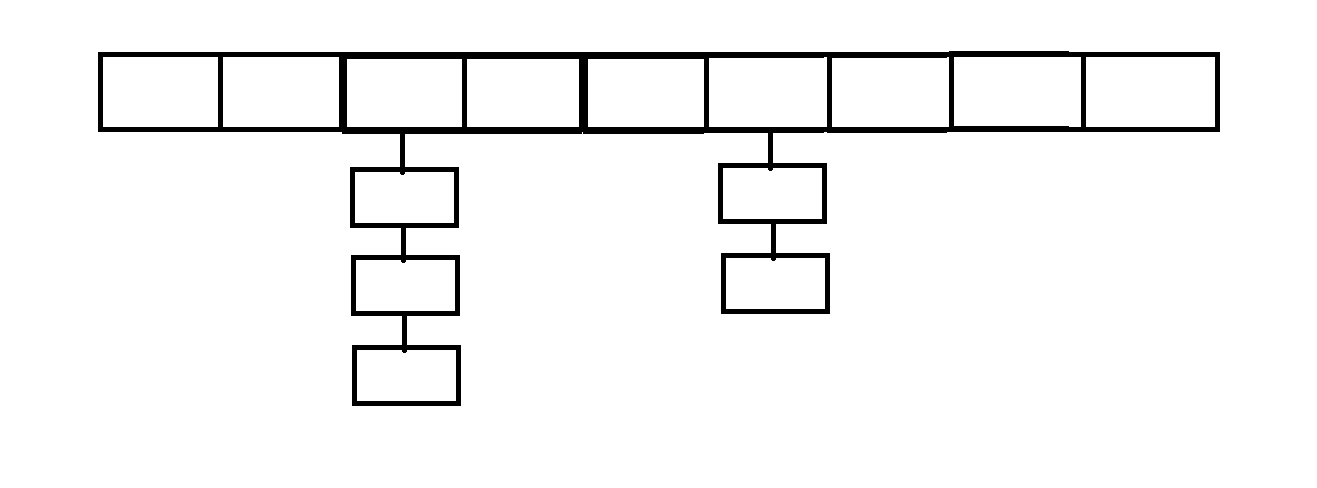

模块框图:

时序图:

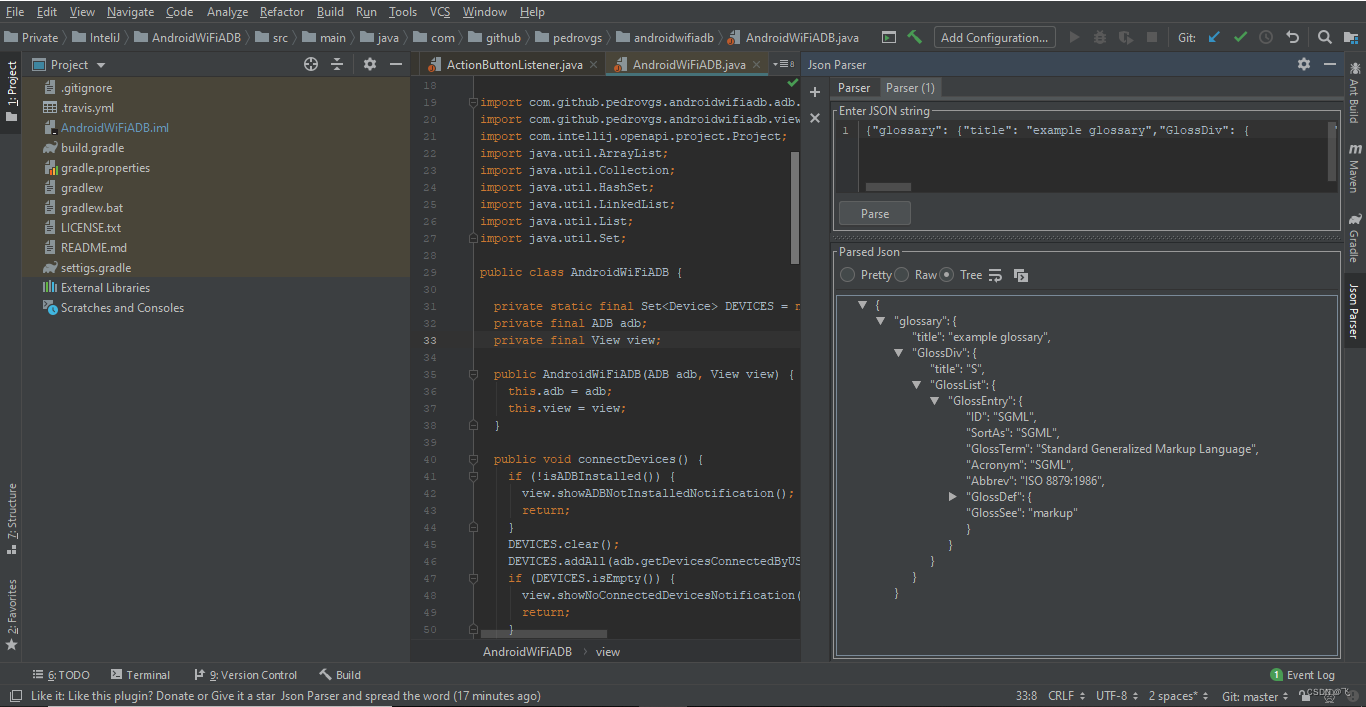

代码:

/*********************功能: 将8位rgb信号,转换成10位信号。编码cnt 当前时钟的值cnt(t - 1) 相对于当前时钟,上一个时钟周期的值

*/module encode(input wire clk_25 ,input wire rst_n ,input wire [7:0] data_in ,input wire hsync , input wire vsync ,input wire DE ,output wire [9:0] data_out

);reg [7:0] data_in_reg1 ;reg [3:0] data_in_n1 ; // 保存传入数据1的个数.wire crtl_1 ; // 一个判断条件,data_in中1的个数大于4 or 个数等于4且data_in[0] == 0wire [8:0] q_m ;reg [8:0] q_m_reg1 ;reg DE_reg1 ;reg DE_reg2 ;reg C0_reg1 ; // 行同步信号,打拍,为了和数据对齐。reg C1_reg1 ; // 场同步信号,打拍,为了和数据对齐。reg C0_reg2 ; reg C1_reg2 ; reg [9:0] q_out ; // 最终要输出的10为数据,经过一系列编码。wire ctrl_2 ;wire ctrl_3 ;reg [4:0] cnt ; // 这是一个用于跟踪数据流差异的寄存器。正值表示已传输的“1”的超额数量。负值表示已传输的“0”的超额数量。reg [3:0] q_m_n1 ; // q_m中1的个数。cnt的最高位是符号位。有符号位的数据不能简单通过是否大于小于0来判断正负,应该判断最高位符号位的0/1(1负数,0正数)reg [3:0] q_m_n0 ; // q_m中0的个数。/**********************************************************************************/// 产生第一个条件:计算输入数据中1的个数。always @(posedge clk_25 or negedge rst_n) begin // 计算传入数据1的个数.if(~rst_n) begindata_in_n1 <= 4'd0 ;end else begindata_in_n1 <= data_in[0] + data_in[1]+ data_in[2] + data_in[3] + data_in[4] + data_in[5] + data_in[6]+ data_in[7] ;endend// 对输入数据打一拍,以对齐数据data_in_n1。always @(posedge clk_25 or negedge rst_n) beginif(~rst_n) begindata_in_reg1 <= 8'd0 ;end else begindata_in_reg1 <= data_in ;endend// 根据data_in_n1与输入数据的打拍信号,描述出crtl_1判断条件。assign crtl_1 = ( data_in_n1 > 4 || (data_in_n1 == 4 && data_in_reg1[0] == 1'b0) ) ? 1'b1 : 1'b0 ;// 8bit 到 9bit 编码逻辑。assign q_m[0] = data_in_reg1[0] ;assign q_m[1] = (crtl_1) ? q_m[0]~^data_in_reg1[1] : q_m[0]^data_in_reg1[1] ;assign q_m[2] = (crtl_1) ? q_m[1]~^data_in_reg1[2] : q_m[1]^data_in_reg1[2] ;assign q_m[3] = (crtl_1) ? q_m[2]~^data_in_reg1[3] : q_m[2]^data_in_reg1[3] ;assign q_m[4] = (crtl_1) ? q_m[3]~^data_in_reg1[4] : q_m[3]^data_in_reg1[4] ;assign q_m[5] = (crtl_1) ? q_m[4]~^data_in_reg1[5] : q_m[4]^data_in_reg1[5] ;assign q_m[6] = (crtl_1) ? q_m[5]~^data_in_reg1[6] : q_m[5]^data_in_reg1[6] ;assign q_m[7] = (crtl_1) ? q_m[6]~^data_in_reg1[7] : q_m[6]^data_in_reg1[7] ;assign q_m[8] = (crtl_1) ? 1'b0 : 1'b1 ;/********************* 对q_out和cnt赋值,用到的条件 ***************************/// 数据q_m中1的个数和0的个数。always @(posedge clk_25 or negedge rst_n) begin if(~rst_n) beginq_m_n1 <= 4'd0 ;q_m_n0 <= 4'd0 ;end else beginq_m_n1 <= q_m[0] + q_m[1] + q_m[2] + q_m[3] + q_m[4] + q_m[5] + q_m[6] + q_m[7] ;// q_m_n0 <= ~q_m[0] + ~q_m[1] + ~q_m[2] + ~q_m[3] // + ~q_m[4] + ~q_m[5] + ~q_m[6] + ~q_m[7] ;q_m_n0 <= 4'd8 - (q_m[0] + q_m[1] + q_m[2] + q_m[3] + q_m[4] + q_m[5] + q_m[6] + q_m[7]) ;endend// 根据cnt和q_m_n1 q_m_n2 产生判断条件ctrl_2,ctrl_3。assign ctrl_2 = ((cnt == 5'd0) || (q_m_n1 == q_m_n0)) ? 1'b1 : 1'b0 ; // 其实可以直接写逻辑运算关系式。assign ctrl_3 = (((~cnt[4]) && (q_m_n1 > q_m_n0)) || ((cnt[4]) && (q_m_n1 < q_m_n0))) ? 1'b1 : 1'b0 ;// reg [8:0] q_m_reg1 ;// 由于q_m_n1 q_m_n0 是时序逻辑,相对于q_m就延后了一个时钟周期,为了保证qm数据与q_m_n1 q_m_n0 对齐,所以要对qm打一拍。always @(posedge clk_25 or negedge rst_n) beginif(~rst_n) beginq_m_reg1 <= 8'd0 ;end else beginq_m_reg1 <= q_m ;endend// reg DE_reg1 ;// reg DE_reg2 ;// DE 逐渐的要与q_m_reg1对齐always @(posedge clk_25 or negedge rst_n) beginif(~rst_n) beginDE_reg1 <= 1'b0 ;DE_reg2 <= 1'b0 ; end else beginDE_reg1 <= DE ;DE_reg2 <= DE_reg1 ; endend// reg C0_reg1 ; // 行同步信号,打拍,为了和数据对齐。// reg C0_reg2 ; // 行场同步信号,也是要与q_m_reg1对齐。always @(posedge clk_25 or negedge rst_n) beginif(~rst_n) beginC0_reg1 <= 1'b0 ;C0_reg2 <= 1'b0 ; end else beginC0_reg1 <= hsync ;C0_reg2 <= C0_reg1 ; endend// reg C1_reg1 ; // 场同步信号,打拍,为了和数据对齐。// reg C1_reg2 ;always @(posedge clk_25 or negedge rst_n) beginif(~rst_n) beginC1_reg1 <= 1'b0 ;C1_reg2 <= 1'b0 ; end else beginC1_reg1 <= vsync ;C1_reg2 <= C1_reg1 ; endend// 对q_out 与 cnt 赋值// q_outalways @(posedge clk_25 or negedge rst_n) beginif(~rst_n) beginq_out <= 10'd0 ;cnt <= 5'd0 ;end else beginif(DE_reg2 == 1'b0) begincase ({C1_reg2 ,C0_reg2})2'b00: q_out[9:0] <= 10'b11010_10100 ;2'b01: q_out[9:0] <= 10'b00101_01011 ;2'b10: q_out[9:0] <= 10'b01010_10100 ;2'b11: q_out[9:0] <= 10'b10101_01011 ;default: q_out[9:0] <= 10'b11010_10100 ; // 随便挑一个。endcasecnt <= 5'd0 ;end else beginif(ctrl_2 == 1'b1) beginq_out[9] <= ~q_m_reg1[8] ; // q_out[9] <= ~q_m_reg1[8] ;q_out[8] <= q_m_reg1[8] ; // q_out[8] <= q_m_reg1[8] ;q_out[7:0] <= (q_m_reg1[8] == 1'b1) ? q_m_reg1[7:0] : ~q_m_reg1[7:0] ; // q_out[7:0] = (q_m_reg1[8] == 1'b1) ? q_m_reg1[7:0] : ~q_m_reg1[7:0] ;if(q_m_reg1[8] == 1'b0) begincnt <= cnt + q_m_n0 - q_m_n1 ;end else begincnt <= cnt - q_m_n0 + q_m_n1 ;endend else beginif(ctrl_3 == 1'b1) beginq_out[9] <= 1'b1 ;q_out[8] <= q_m_reg1[8] ;q_out[7:0] <= ~q_m_reg1[7:0] ;cnt <= cnt + {q_m_reg1[8], 1'b0} + q_m_n0 - q_m_n1 ; // 2 乘以 1位宽的数据,相当于把该数据左移一位。 + {q_m_reg1[8],0} + end else beginq_out[9] <= 1'b0 ;q_out[8] <= q_m_reg1[8] ;q_out[7:0] <= q_m_reg1[7:0] ;cnt <= cnt - {~q_m_reg1[8], 1'b0} - q_m_n0 + q_m_n1 ;endendendendend/************output signal descrable **************/assign data_out = q_out ;

endmodule// 10位并行数据信号转换为,串行差分信号。

module par_to_ser(input wire clk_125 ,input wire rst_n ,input wire [9:0] data_out, // 应该在一个周期内把并行转串行?应该用到流水线技术?output wire ser_p ,output wire ser_n

);/**********************************************************************************// // wire signal define

// wire dataout_flag ;

// wire [3:0] datain_h_num ;

// wire [3:0] datain_l_num ;

// // reg signal define

// reg datain_h ;

// reg datain_l ;

// reg [3:0] cnt_bit ;

// reg [9:0] data_out_reg1 ;//

// // wire dataout_flag ;

// assign dataout_flag = (data_out != data_out_reg1) ? 1'b1 : 1'b0 ;

// assign datain_h_num = 2'd2*cnt_bit ;

// assign datain_l_num = 2'd2*cnt_bit + 1'b1 ;

// // reg datain_h ;

// always @(posedge clk_125 or negedge rst_n) begin

// if(~rst_n) begin

// datain_h <= 1'b0 ;

// end else begin

// datain_h <= data_out_reg1[datain_h_num] ; // 其实这里可能有一个问题,datain_h_num如果计算慢了,那么datain_h将会滞后一个clk_125.

// end

// end

// // reg datain_l ;

// always @(posedge clk_125 or negedge rst_n) begin

// if(~rst_n) begin

// datain_l <= 1'b0 ;

// end else begin

// datain_l <= data_out_reg1[datain_l_num] ;

// end

// end

// // reg [3:0] cnt_bit ;

// always @(posedge clk_125 or negedge rst_n) begin

// if(~rst_n) begin

// cnt_bit <= 4'd0 ;

// end else begin

// if(dataout_flag == 1'b1 || cnt_bit == 4'd4) begin

// cnt_bit <= 4'd0 ;

// end else begin

// cnt_bit <= cnt_bit + 1'b1 ;

// end

// end

// end

// // reg [9:0] data_out_reg1 ;

// always @(posedge clk_125 or negedge rst_n) begin

// if(~rst_n) begin

// data_out_reg1 <= 10'd0 ;

// end else begin

// data_out_reg1 <= data_out ;

// end

// end

************************************************************************************//***********************************************************************************/

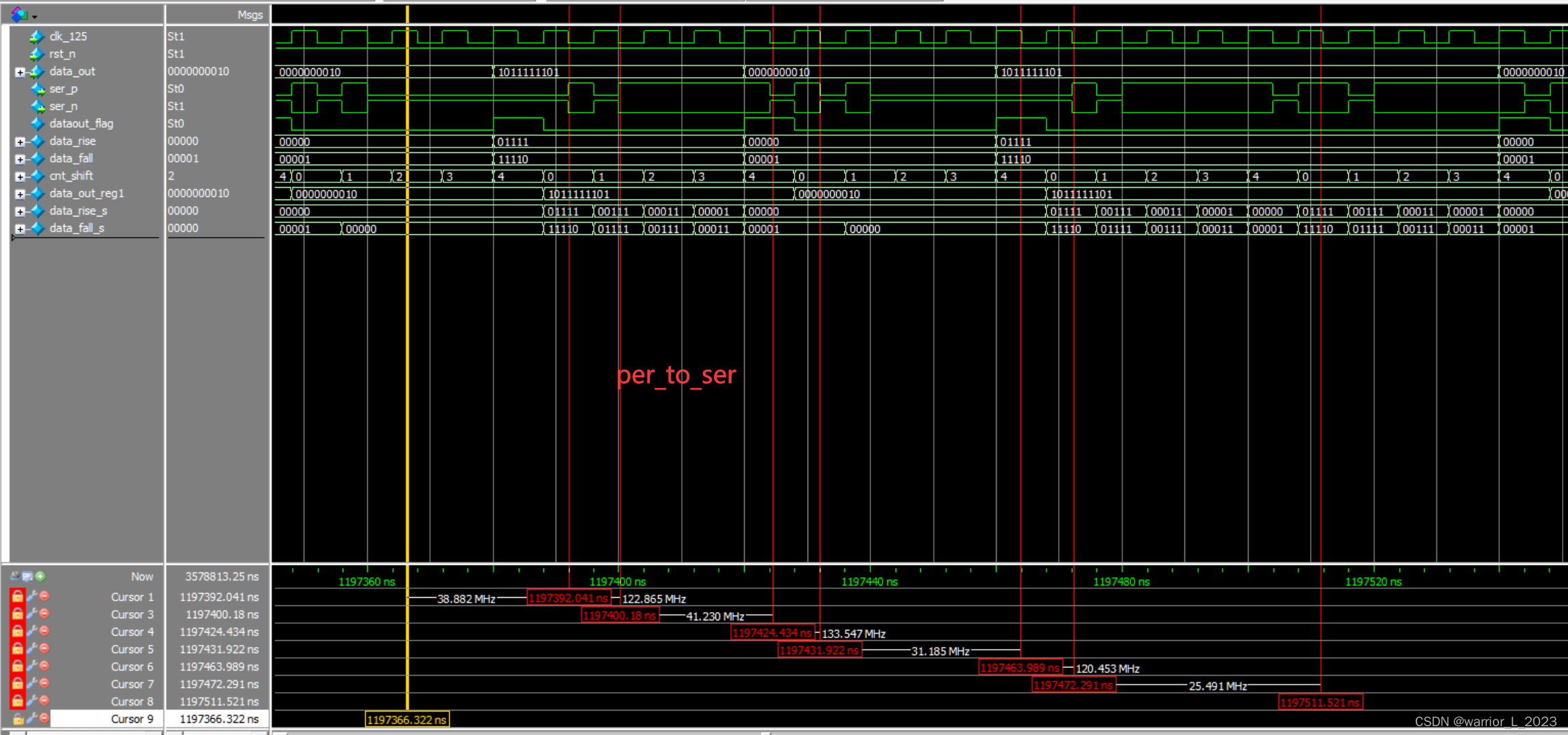

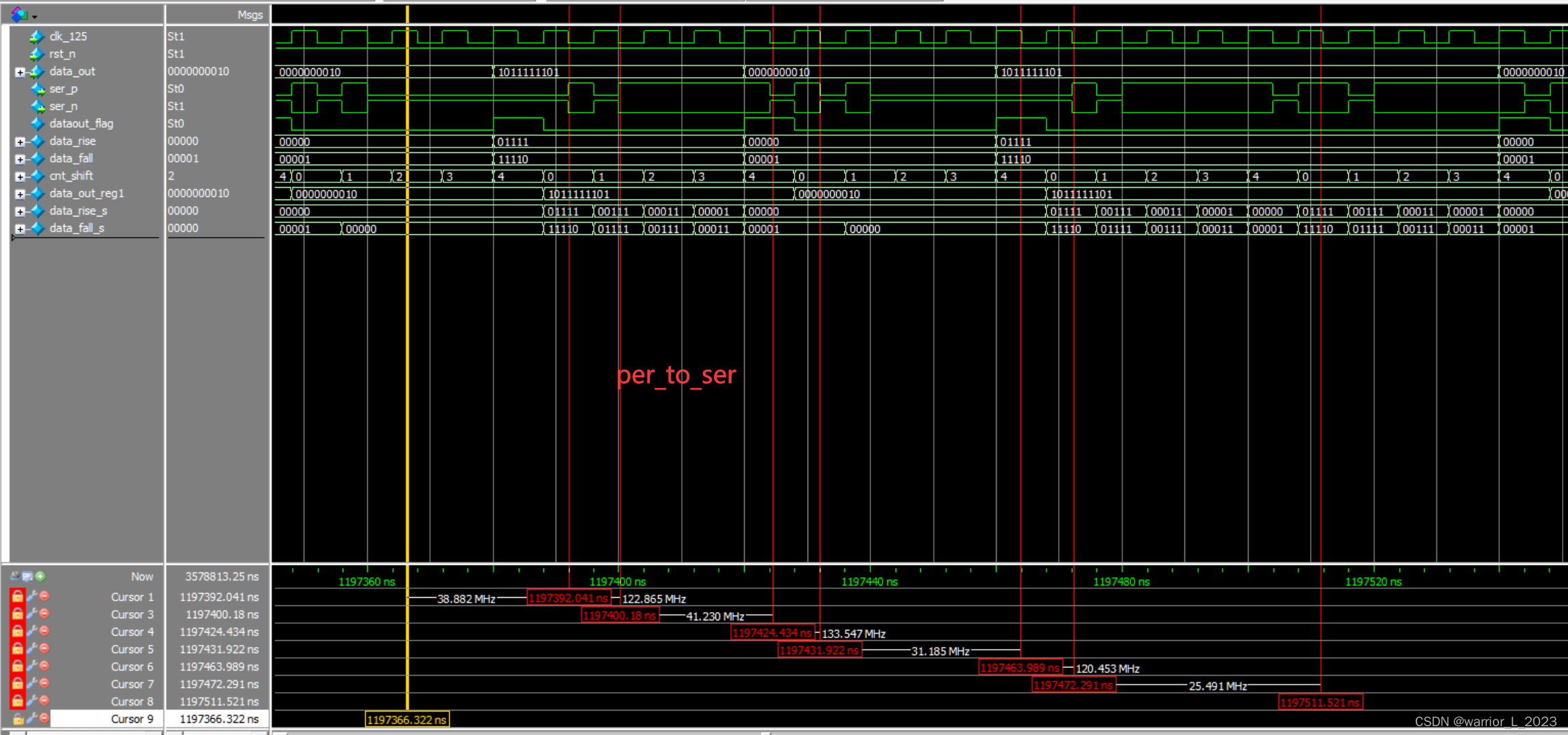

// 野火教程里的方法,10bit并行数据转串行数据。// wire signal deginewire dataout_flag ;wire [4:0] data_rise ;wire [4:0] data_fall ;// reg signal definereg [3:0] cnt_shift ;reg [9:0] data_out_reg1 ;reg [4:0] data_rise_s ;reg [4:0] data_fall_s ;// [4:0] data_rise ;assign data_rise = {data_out[8],data_out[6],data_out[4],data_out[2],data_out[0]} ;// [4:0] data_fall ;assign data_fall = {data_out[9],data_out[7],data_out[5],data_out[3],data_out[1]} ;// wire dataout_flag;assign dataout_flag = (data_out != data_out_reg1) ? 1'b1 : 1'b0 ;// reg [9:0] data_out_reg1 ;always @(posedge clk_125 or negedge rst_n) beginif(~rst_n) begindata_out_reg1 <= 10'd0 ;end else begindata_out_reg1 <= data_out ;endend// reg [3:0] cnt_shift ;always @(posedge clk_125 or negedge rst_n) beginif(~rst_n) begincnt_shift <= 4'd0 ;end else beginif(dataout_flag == 1'b1 || cnt_shift == 4'd4) begincnt_shift <= 4'd0 ;end else begincnt_shift <= cnt_shift + 1'b1 ; endendend// reg [4:0] data_rise_s ;// reg [4:0] data_fall_s ;always @(posedge clk_125 or negedge rst_n) beginif(~rst_n) begindata_rise_s <= 5'd0 ;data_fall_s <= 5'd0 ;end else beginif(cnt_shift == 4'd4) begindata_rise_s <= data_rise ;data_fall_s <= data_fall ;end else begindata_rise_s <= data_rise_s[4:1] ; // 相当于右移1位。data_fall_s <= data_fall_s[4:1] ;endendend// 单沿到双沿采样,通过调用ddio_out实现。相当于把采样时钟翻倍。

ddio_out ddio_out_inst0 (.datain_h ( data_rise_s[0] ), // 在outclk上升沿对datain_h采样传给data_out。1bit的串行数据。.datain_l ( data_fall_s[0] ), // 在outclk下降沿对datain_l采样传给data_out。1bit的串行数据。.outclock ( ~clk_125 ), // 采样时钟。.dataout ( ser_p )

);ddio_out ddio_out_inst1 (.datain_h ( ~data_rise_s[0] ), // 单端到差分之间的转换。.datain_l ( ~data_fall_s[0] ), .outclock ( ~clk_125 ), .dataout ( ser_n )

);endmodule只放了两个新模块的代码。

`timescale 1ns/1ns

module test();reg sys_clk ;reg sys_rst_n ;wire clk_p ;wire clk_n ;wire r_p ;wire r_n ;wire g_p ;wire g_n ;wire b_p ;wire b_n ;wire DDC_SCL ;wire DDC_SDA ;top top_insert(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.clk_p ( clk_p ) ,.clk_n ( clk_n ) ,.r_p ( r_p ) ,.r_n ( r_n ) ,.g_p ( g_p ) ,.g_n ( g_n ) ,.b_p ( b_p ) ,.b_n ( b_n ) ,.DDC_SCL ( DDC_SCL ) ,.DDC_SDA ( DDC_SDA )

);parameter CYCLE = 20 ;initial beginsys_clk = 1'b1 ;sys_rst_n = 1'b0 ;#( CYCLE ) ;sys_rst_n = 1'b1 ;endalways #( CYCLE / 2 ) sys_clk = ~sys_clk ;

endmodule

相关文章:

FPGA project :HDMI

实验目标:驱动HdMI显示十色等宽彩条。 本实验的重点是: 1掌握TMDS通信协议。 2rgb565转rgb888。 3编写HDMI驱动程序。 4学会看流程图编写代码。 值得注意的事情 1注意数据与解析数据的信号(比如传入的数据中0或者1的个数)&…...

基于微信小程序的物流快递信息查询平台同城急送小程序(亮点:寄件、发票申请、在线聊天)

文章目录 前言系统主要功能:具体实现截图论文参考详细视频演示为什么选择我自己的网站自己的小程序(小蔡coding)有保障的售后福利 代码参考源码获取 前言 💗博主介绍:✌全网粉丝10W,CSDN特邀作者、博客专家、CSDN新星计…...

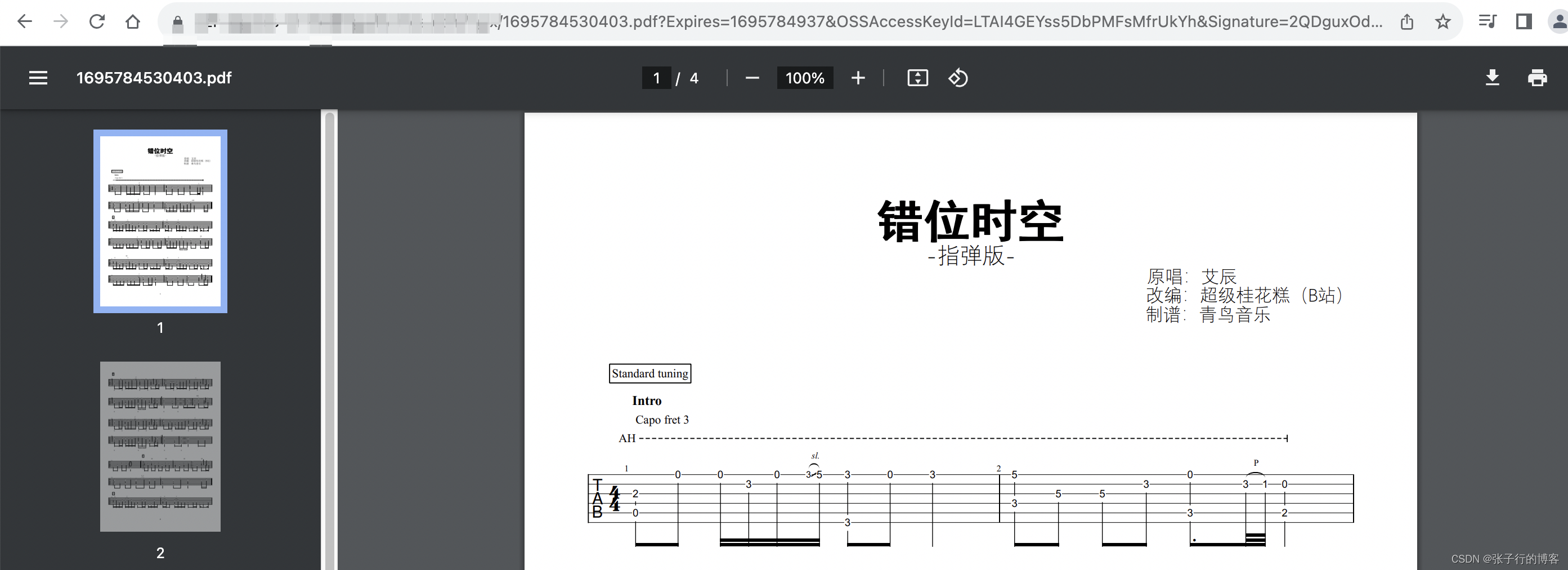

idea插件推荐

目录 一、插件安装方式 file->settings->plugins->macketplace 各个版本IDE插件界面略有不同,不一一赘述 二、常用插件 1、Background Image Plus 推荐指数:★★★★☆ 这款插件并不能直接提高你的开发效率,但是可以让你面对的ID…...

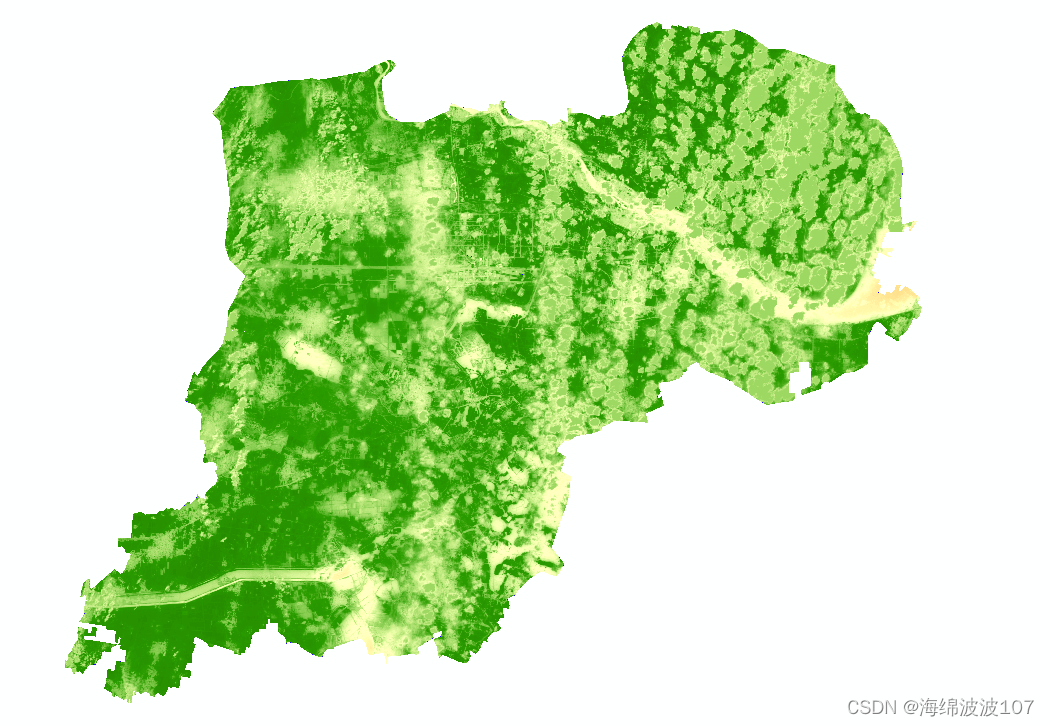

Arcgis快速计算NDVI

Arcgis快速计算NDVI 一、问题描述 如何使用Arcgis像ENVI一样波段计算NDVI的值,事实上,Arcgis更快速一些。 二、操作步骤 首先准备好影像 打开窗口-影像分析 点击左上角 点击确定 (发现自己使用的遥感影像不对劲,是计算好了…...

SpringCloud Alibaba - 基于 FeignClient 整合 Sentinel,实现“线程隔离”和“熔断降级”

目录 一、FeignClient 整合 Sentinel 1.1、整合原因 1.2、实现步骤 1.2.1、修改 OrderService 中的 application.yml 文件 1.2.2、给 FeignClient 编写失败后的降级逻辑 二、线程隔离 2.1、线程隔离的两种方式 2.1.1、线程池隔离 2.1.2、信号量隔离(Sentin…...

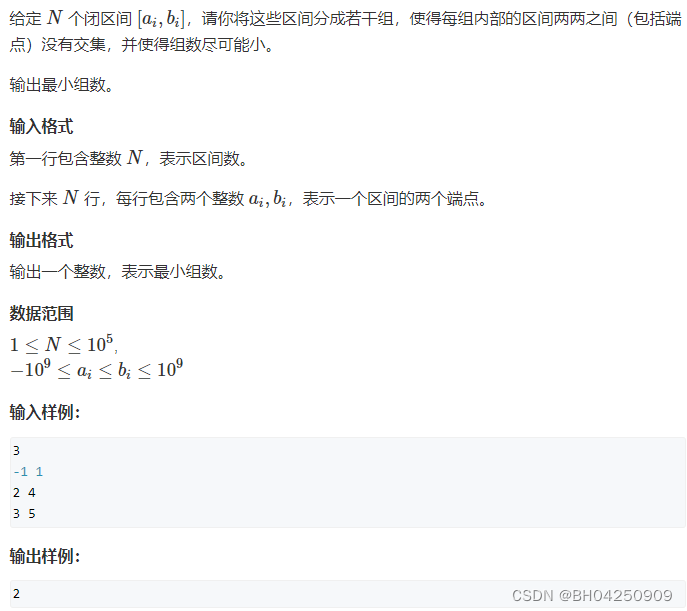

Acwing 906. 区间分组

Acwing 906. 区间分组 知识点题目描述思路讲解代码展示 知识点 贪心 题目描述 思路讲解 这段代码是用来维护一个最小堆,以确保右边界不相交的区间被正确地保留在堆中。让我详细解释这段代码: heap.empty():这个条件检查最小堆 heap 是否为…...

阿里云 Oss 权限控制

前言 最近公司的私有 Oss 服务满了,且 Oss 地址需要设置权限,只有当前系统的登录用户才能访问 Oss 下载地址。一开始想着用 Nginx 做个转发来着,Nginx 每当检测当前请求包含特定的 Oss 地址就转发到我们的统一鉴权接口上去,但是紧…...

CSS详细基础(六)边框样式

本期是CSS基础的最后一篇~ 目录 一.border属性 二.边框属性复合写法 三.CSS修改表格标签 四.内边距属性 五.外边距属性 六.其他杂例 1.盒子元素水平居中 2.清除网页内外元素边距 3.外边距的合并与塌陷 4.padding不会撑大盒子的情况 七.综合案例——新浪导航栏仿真 …...

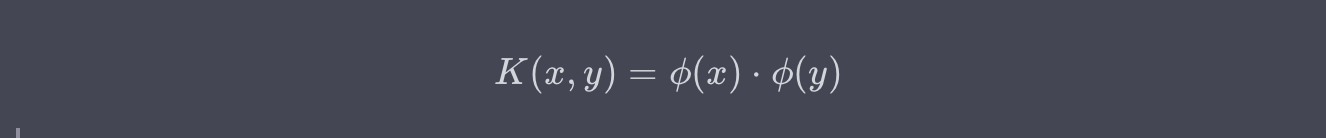

支持向量机SVM:从数学原理到实际应用

目录 一、引言背景SVM算法的重要性 二、SVM基础线性分类器简介什么是支持向量?超平面和决策边界SVM的目标函数 三、数学背景和优化拉格朗日乘子法(Lagrange Multipliers)KKT条件核技巧(Kernel Trick)双重问题和主问题&…...

【办公自动化】在Excel中按条件筛选数据并存入新的表(文末送书)

🤵♂️ 个人主页:艾派森的个人主页 ✍🏻作者简介:Python学习者 🐋 希望大家多多支持,我们一起进步!😄 如果文章对你有帮助的话, 欢迎评论 💬点赞Ǵ…...

)

第三章:最新版零基础学习 PYTHON 教程(第十一节 - Python 运算符—Python 中的any与all)

Any 和 All 是 python 中提供的两个内置函数,用于连续的与/或。Any如果任何一项为 True,则返回 true。如果为空或全部为 false,则返回 False。Any 可以被认为是对所提供的可迭代对象进行 OR 操作的序列。它会短路执行,即一旦知道结果就停止执行。 句法: any(iterable) 函…...

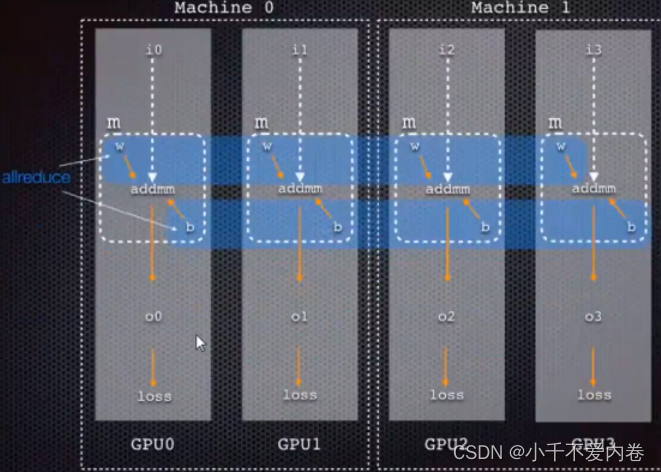

Pytorch单机多卡分布式训练

Pytorch单机多卡分布式训练 数据并行: DP和DDP 这两个都是pytorch下实现多GPU训练的库,DP是pytorch以前实现的库,现在官方更推荐使用DDP,即使是单机训练也比DP快。 DataParallel(DP) 只支持单进程多线程…...

asp.net coremvc+efcore增删改查

下面是一个使用 EF Core 在 ASP.NET Core MVC 中完成增删改查的示例: 创建一个新的 ASP.NET Core MVC 项目。 安装 EF Core 相关的 NuGet 包。在项目文件 (.csproj) 中添加以下依赖项: <ItemGroup><PackageReference Include"Microsoft…...

Java基础面试,什么是面向对象,谈谈你对面向对象的理解

前言 马上就要找工作了,从今天开始一天准备1~2道面试题,来打基础,就从Java基础开始吧。 什么是面向对象,谈谈你对面向对象的理解? 谈到面向对象,那就不得不谈到面向过程。面向过程更加注重的是完成一个任…...

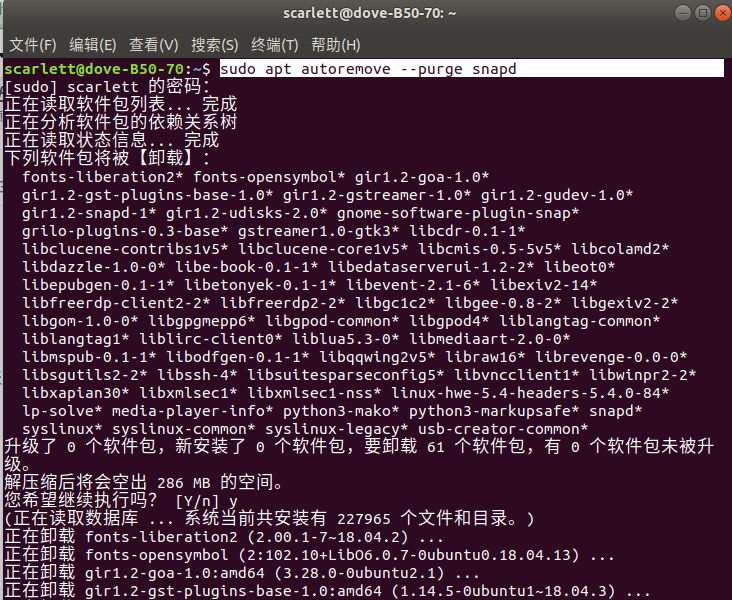

Ubuntu系统初始设置

更换国内源 安装截图工具 安装中文输入法 安装QQ 参考: 安装双系统win10Ubuntu20.04LTS(详细到我自己都害怕) 引导方式磁盘分区方法UEFIGPTLegancyMBR 安装网络助手 sudo apt install net-tools 安装VS Code 使用从官网下载.deb安装包…...

焕新古文化传承之路,AI为古彝文识别赋能

目录 1 古彝文与古典保护 2 古文识别的挑战 2.1 西文与汉文OCR 2.2 古彝文识别难点 3 合合信息:古彝文保护新思路 3.1 图像矫正 3.2 图像增强 3.3 语义理解 3.4 工程技巧 4 总结 1 古彝文与古典保护 彝文指的是云南、贵州、四川等地的彝族人使用的文字&am…...

毛玻璃动画交互效果

效果展示 页面结构组成 从上述的效果展示页面结构来看,页面布局都是比较简单的,只是元素的动画交互比较麻烦。 第一个动画交互是两个圆相互交错来回运动。第二个动画交互是三角绕着圆进行 360 度旋转。 CSS 知识点 animationanimation-delay绝对定位…...

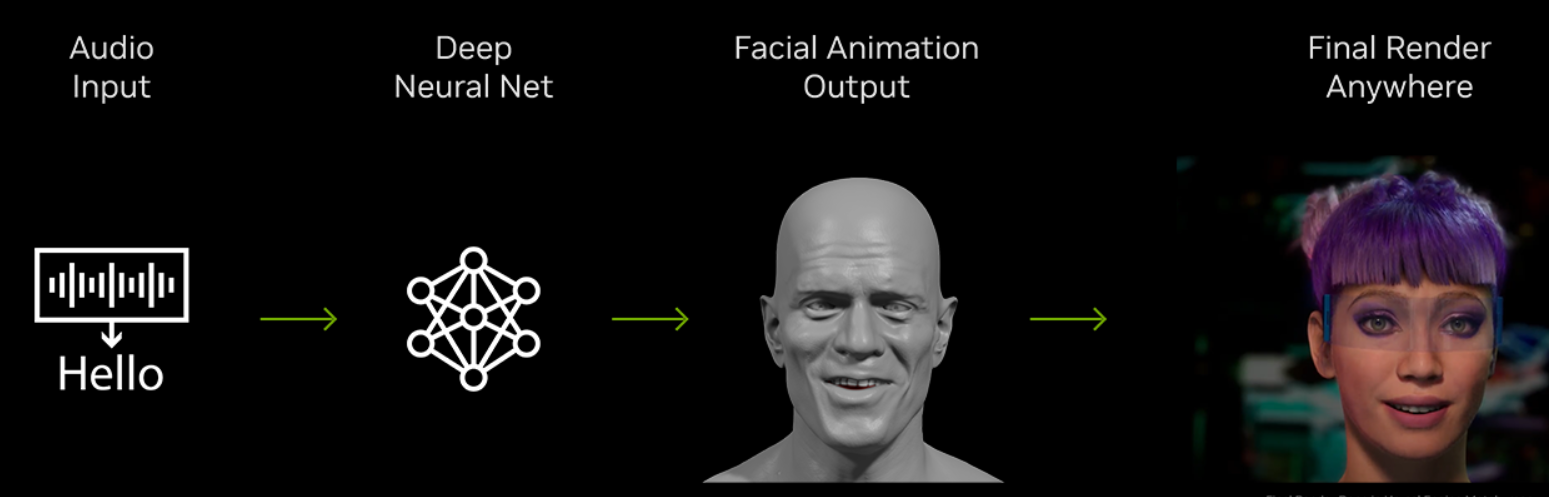

Audio2Face的工作原理

预加载一个3D数字人物模型(Digital Mark),该模型可以通过音频驱动进行面部动画。 用户上传音频文件作为输入。 将音频输入馈送到预训练的深度神经网络中。 Audio2Face加载预制的3d人头mesh 3D数字人物面部模型由大量顶点组成,每个顶点都有xyz坐标。 深度神经网络输入音频特征,…...

【面试题】2023前端面试真题之JS篇

前端面试题库 (面试必备) 推荐:★★★★★ 地址:前端面试题库 表妹一键制作自己的五星红旗国庆头像,超好看 世界上只有一种真正的英雄主义,那就是看清生活的真相之后,依然热爱生活。…...

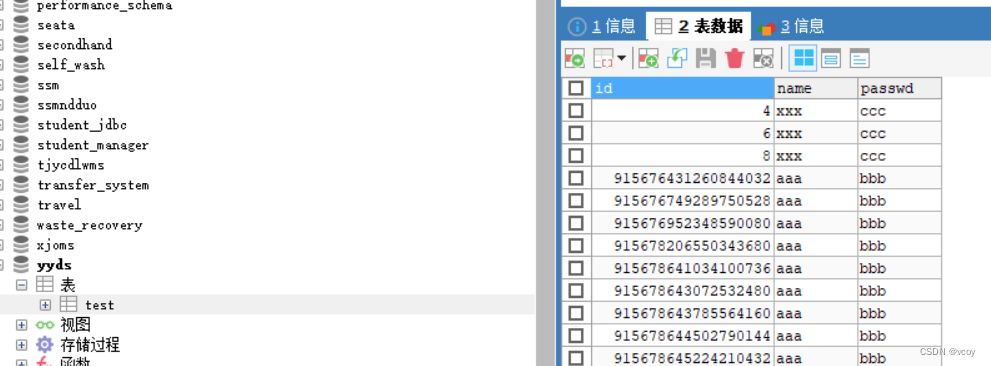

Mysql 分布式序列算法

接上文 Mysql分库分表 1.分布式序列简介 在分布式系统下,怎么保证ID的生成满足以上需求? ShardingJDBC支持以上两种算法自动生成ID。这里,使用ShardingJDBC让主键ID以雪花算法进行生成,首先配置数据库,因为默认的注…...

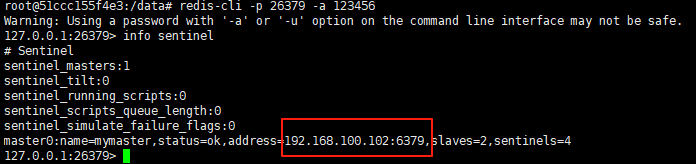

使用docker在3台服务器上搭建基于redis 6.x的一主两从三台均是哨兵模式

一、环境及版本说明 如果服务器已经安装了docker,则忽略此步骤,如果没有安装,则可以按照一下方式安装: 1. 在线安装(有互联网环境): 请看我这篇文章 传送阵>> 点我查看 2. 离线安装(内网环境):请看我这篇文章 传送阵>> 点我查看 说明:假设每台服务器已…...

)

云计算——弹性云计算器(ECS)

弹性云服务器:ECS 概述 云计算重构了ICT系统,云计算平台厂商推出使得厂家能够主要关注应用管理而非平台管理的云平台,包含如下主要概念。 ECS(Elastic Cloud Server):即弹性云服务器,是云计算…...

)

python爬虫:Newspaper3k 的详细使用(好用的新闻网站文章抓取和解析的Python库)

更多内容请见: 爬虫和逆向教程-专栏介绍和目录 文章目录 一、Newspaper3k 概述1.1 Newspaper3k 介绍1.2 主要功能1.3 典型应用场景1.4 安装二、基本用法2.2 提取单篇文章的内容2.2 处理多篇文档三、高级选项3.1 自定义配置3.2 分析文章情感四、实战案例4.1 构建新闻摘要聚合器…...

成都鼎讯硬核科技!雷达目标与干扰模拟器,以卓越性能制胜电磁频谱战

在现代战争中,电磁频谱已成为继陆、海、空、天之后的 “第五维战场”,雷达作为电磁频谱领域的关键装备,其干扰与抗干扰能力的较量,直接影响着战争的胜负走向。由成都鼎讯科技匠心打造的雷达目标与干扰模拟器,凭借数字射…...

uniapp中使用aixos 报错

问题: 在uniapp中使用aixos,运行后报如下错误: AxiosError: There is no suitable adapter to dispatch the request since : - adapter xhr is not supported by the environment - adapter http is not available in the build 解决方案&…...

【HTTP三个基础问题】

面试官您好!HTTP是超文本传输协议,是互联网上客户端和服务器之间传输超文本数据(比如文字、图片、音频、视频等)的核心协议,当前互联网应用最广泛的版本是HTTP1.1,它基于经典的C/S模型,也就是客…...

Swagger和OpenApi的前世今生

Swagger与OpenAPI的关系演进是API标准化进程中的重要篇章,二者共同塑造了现代RESTful API的开发范式。 本期就扒一扒其技术演进的关键节点与核心逻辑: 🔄 一、起源与初创期:Swagger的诞生(2010-2014) 核心…...

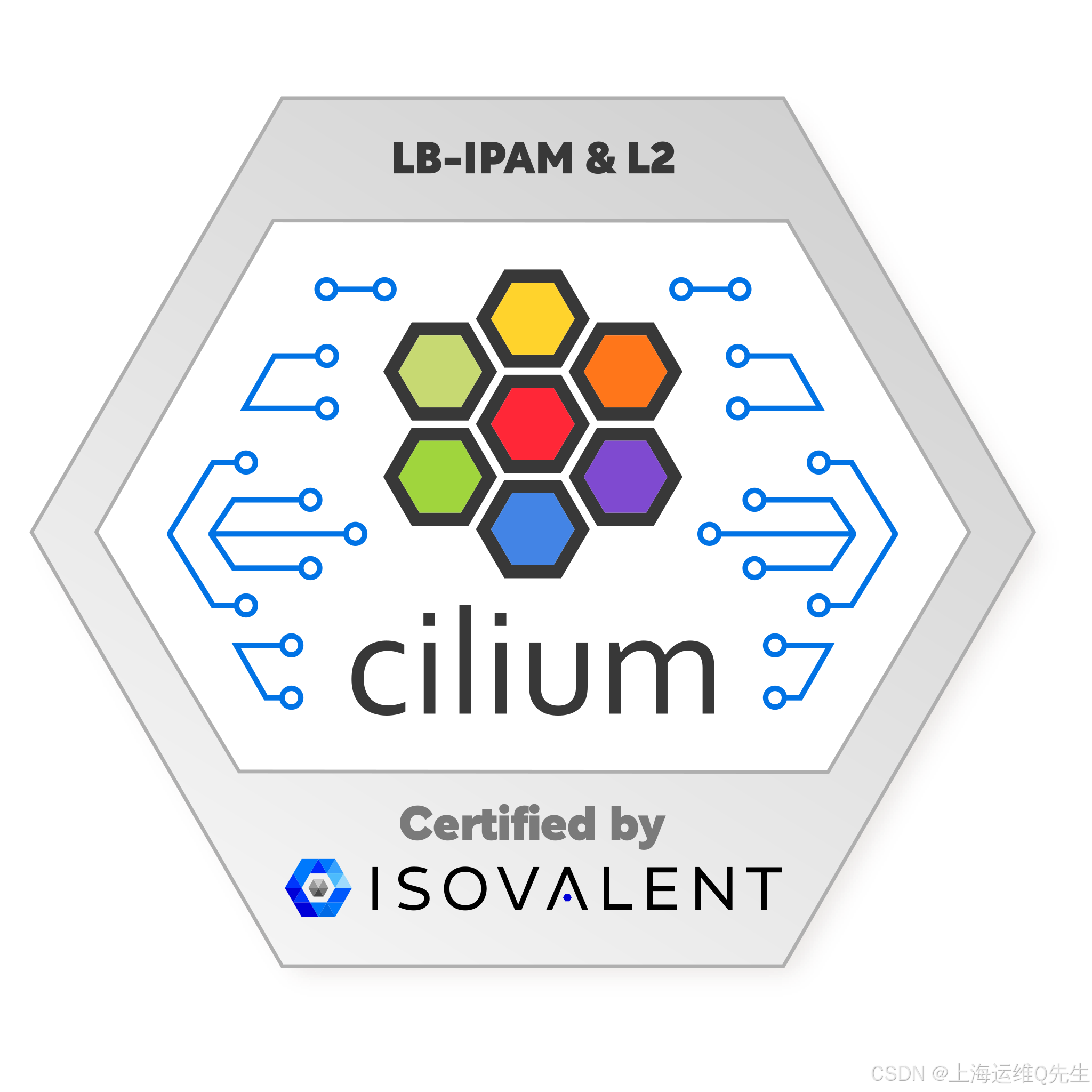

Cilium动手实验室: 精通之旅---13.Cilium LoadBalancer IPAM and L2 Service Announcement

Cilium动手实验室: 精通之旅---13.Cilium LoadBalancer IPAM and L2 Service Announcement 1. LAB环境2. L2公告策略2.1 部署Death Star2.2 访问服务2.3 部署L2公告策略2.4 服务宣告 3. 可视化 ARP 流量3.1 部署新服务3.2 准备可视化3.3 再次请求 4. 自动IPAM4.1 IPAM Pool4.2 …...

C++_哈希表

本篇文章是对C学习的哈希表部分的学习分享 相信一定会对你有所帮助~ 那咱们废话不多说,直接开始吧! 一、基础概念 1. 哈希核心思想: 哈希函数的作用:通过此函数建立一个Key与存储位置之间的映射关系。理想目标:实现…...

多元隐函数 偏导公式

我们来推导隐函数 z z ( x , y ) z z(x, y) zz(x,y) 的偏导公式,给定一个隐函数关系: F ( x , y , z ( x , y ) ) 0 F(x, y, z(x, y)) 0 F(x,y,z(x,y))0 🧠 目标: 求 ∂ z ∂ x \frac{\partial z}{\partial x} ∂x∂z、 …...