状态机的练习:按键控制led灯

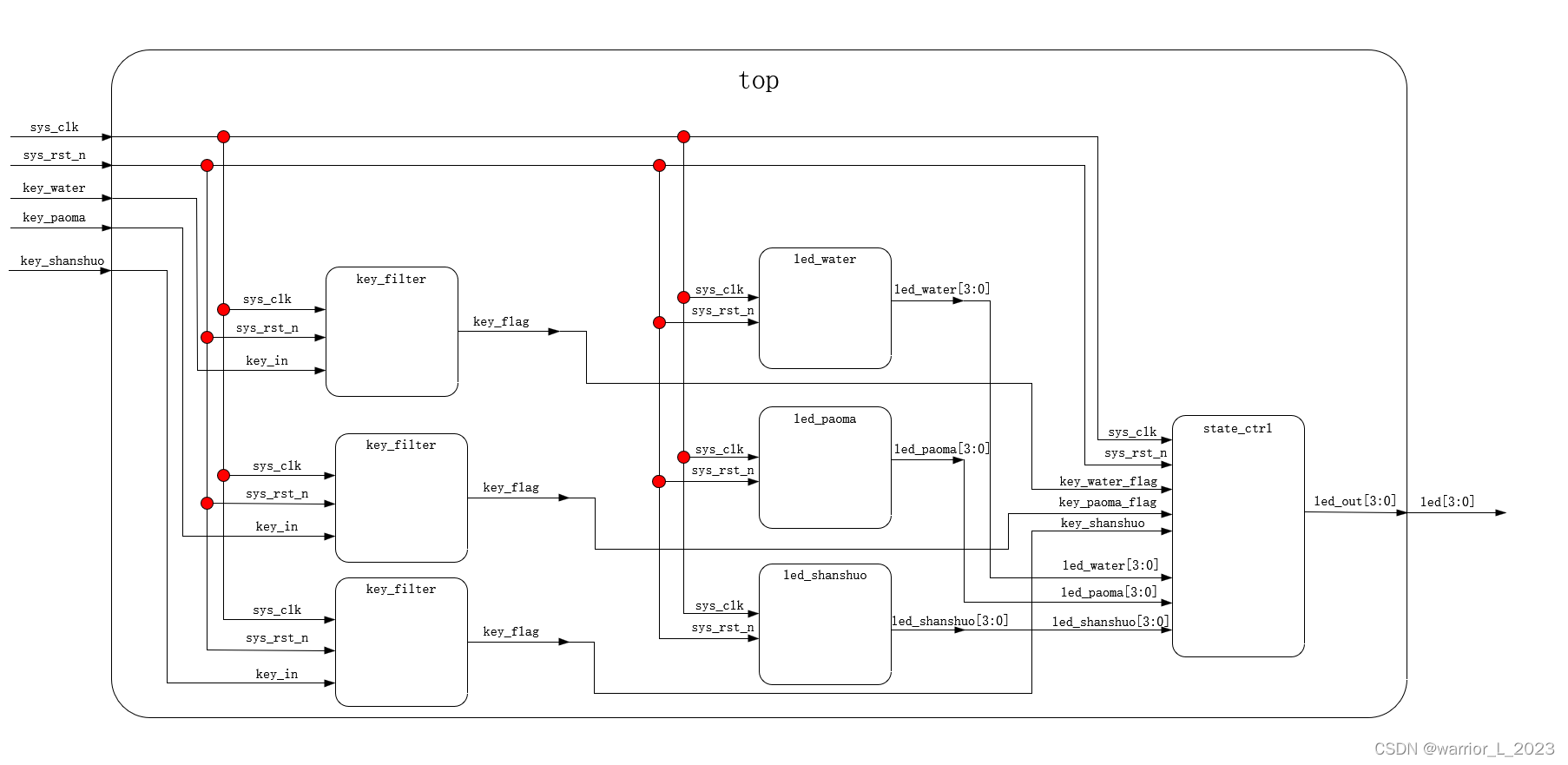

设计思路:

三个按键控制led输出。

三个按键经过滤波(消抖),产生三个按键标志信号。

三个led数据的产生模块(流水,跑马,闪烁模块),分别产生led信号。

这六路信号(三路按键信号,三路led信号),接入state_led_ctrl模块,进行led_out的控制。

状态机:

模块框图:

代码:

/*1位按键消抖

*/

module key_filter (input wire sys_clk ,input wire sys_rst_n ,input wire key_in ,output reg key_flag

);// 参数定义parameter MAX_CNT_10MS = 500_000 ;localparam IDLE = 4'b0001 ,FILTER_UP = 4'b0010 ,SAMPLING = 4'b0100 ,FILTER_BACK = 4'b1000 ;// reg signal define reg key_in_r1 ; reg key_in_r2 ;reg [18:0] cnt_core ;reg [3:0] state_c ;reg [3:0] state_n ;// wire signal define wire nege ;wire pose ;wire IDLEtoFILTER_UP ;wire FILTER_UPtoIDLE ;wire FILTER_UPtoSAMPLING ;wire SAMPLINGtoFILTER_BACK ;wire FILTER_BACKtoIDLE ;wire filter_done ; /******************************************************************/// reg key_in_r1 ; always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) key_in_r1 <= 1'b1 ;elsekey_in_r1 <= key_in ;end // reg key_in_r2 ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) key_in_r2 <= 1'b1 ;elsekey_in_r2 <= key_in_r1 ;end // wire nege ;assign nege = ~key_in_r1 && key_in_r2 ;// wire pose ; assign pose = key_in_r1 && ~key_in_r2 ;// reg [3:0] state_c ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) state_c <= IDLE ;elsestate_c <= state_n ;end// reg [3:0] state_n ;always @(*) begincase(state_c)IDLE : if(IDLEtoFILTER_UP)state_n = FILTER_UP ;else state_n = IDLE ;FILTER_UP : if(FILTER_UPtoIDLE)state_n = IDLE ;else if(FILTER_UPtoSAMPLING)state_n = SAMPLING ;else state_n = FILTER_UP ;SAMPLING : if(SAMPLINGtoFILTER_BACK)state_n = FILTER_BACK ;else state_n = SAMPLING ;FILTER_BACK:if(FILTER_BACKtoIDLE)state_n = IDLE ;elsestate_n = FILTER_BACK ;default : state_n = IDLE ;endcaseendassign IDLEtoFILTER_UP = (state_c == IDLE) && (nege) ;assign FILTER_UPtoIDLE = (state_c == FILTER_UP) && (pose) ;assign FILTER_UPtoSAMPLING = (state_c == FILTER_UP) && (filter_done) ;assign SAMPLINGtoFILTER_BACK = (state_c == SAMPLING) && (pose) ;assign FILTER_BACKtoIDLE = (state_c == FILTER_BACK)&& (filter_done) ;// reg [18:0] cnt_core ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) cnt_core <= 19'd0 ;elsecase (state_c)IDLE :cnt_core <= 19'd0 ; FILTER_UP :if(filter_done)cnt_core <= 19'd0 ;else cnt_core <= cnt_core + 1'b1 ;SAMPLING :cnt_core <= 19'd0 ; FILTER_BACK:if(filter_done)cnt_core <= 19'd0 ;else cnt_core <= cnt_core + 1'b1 ;default : cnt_core <= 19'd0 ;endcaseend// wire filter_doneassign filter_done = (cnt_core == MAX_CNT_10MS - 1) ;// output reg key_flagalways @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) key_flag <= 1'b0 ;else if(FILTER_UPtoSAMPLING)key_flag <= ~key_in_r2 ;else key_flag <= 1'b0 ;endendmodule

module led_paoma (input wire sys_clk ,input wire sys_rst_n ,output reg [3:0] led_out

);parameter MAX_CNT_500MS = 25_000_000 ;// reg signal definereg [24:0] cnt_500ms ;reg [ 1:0] cnt_state ;// wire signal definewire add_cnt_500ms ;wire end_cnt_500ms ;wire add_cnt_state ;wire end_cnt_state ;

/******************************************************************************************

********************************************main code**************************************

*******************************************************************************************/// reg [24:0] cnt_500ms ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) cnt_500ms <= 25'd0 ;else if(add_cnt_500ms) beginif(end_cnt_500ms)cnt_500ms <= 25'd0 ;else cnt_500ms <= cnt_500ms + 1'b1 ;endelse cnt_500ms <= 25'd0 ;end// reg [ 1:0] cnt_state ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) cnt_state <= 2'd0 ;else if(add_cnt_state) beginif(end_cnt_state)cnt_state <= 2'd0 ;else cnt_state <= cnt_state + 1'b1 ;end else cnt_state <= cnt_state ;end// // wire signal define// wire add_cnt_500ms ;assign add_cnt_500ms = 1'b1 ;// wire end_cnt_500ms ;assign end_cnt_500ms = add_cnt_500ms && (cnt_500ms == (MAX_CNT_500MS - 1)) ;// wire add_cnt_state ;assign add_cnt_state = end_cnt_500ms ;// wire end_cnt_state ;assign end_cnt_state = ((add_cnt_state && (cnt_state == 2'b11 )) ) ; // output reg [3:0] led_out always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) led_out <= 4'b0000 ;else case (cnt_state)2'b00 : led_out <= 4'b0001 ;2'b01 : led_out <= 4'b0010 ;2'b10 : led_out <= 4'b0100 ;2'b11 : led_out <= 4'b1000 ;default: led_out <= 4'b0000 ;endcaseend

endmodule

module shanshuo (input wire sys_clk ,input wire sys_rst_n ,output reg [3:0] led_out

);parameter MAX_CNT_500MS = 25_000_000 ;// reg signal definereg [24:0] cnt_500ms ;// wire signal definewire add_cnt_500ms ;wire end_cnt_500ms ;

/******************************************************************************************

********************************************main code**************************************

*******************************************************************************************/// reg [24:0] cnt_500ms ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) cnt_500ms <= 25'd0 ;else if(add_cnt_500ms) beginif(end_cnt_500ms)cnt_500ms <= 25'd0 ;else cnt_500ms <= cnt_500ms + 1'b1 ;endelse cnt_500ms <= 25'd0 ;end// // wire signal define// wire add_cnt_500ms ;assign add_cnt_500ms = 1'b1 ;// wire end_cnt_500ms ;assign end_cnt_500ms = add_cnt_500ms && (cnt_500ms == (MAX_CNT_500MS - 1)) ;// output reg [3:0] led_out always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) led_out <= 4'b0000 ;else if(end_cnt_500ms)led_out <= ~led_out ;else led_out <= led_out ;endendmodule

module led_water (input wire sys_clk ,input wire sys_rst_n ,output reg [3:0] led_out

);parameter MAX_CNT_500MS = 25_000_000 ;// reg signal definereg [24:0] cnt_500ms ;reg [ 2:0] cnt_state ; // wire signal definewire add_cnt_500ms ;wire end_cnt_500ms ;wire add_cnt_state ;wire end_cnt_state ;

/******************************************************************************************

********************************************main code**************************************

*******************************************************************************************/// reg [24:0] cnt_500ms ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) cnt_500ms <= 25'd0 ;else if(add_cnt_500ms) beginif(end_cnt_500ms)cnt_500ms <= 25'd0 ;else cnt_500ms <= cnt_500ms + 1'b1 ;endelse cnt_500ms <= 25'd0 ;end// reg [ 1:0] cnt_state ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) cnt_state <= 2'd0 ;else if(add_cnt_state) beginif(end_cnt_state)cnt_state <= 2'd0 ;else cnt_state <= cnt_state + 1'b1 ;end else cnt_state <= cnt_state ;end// // wire signal define// wire add_cnt_500ms ;assign add_cnt_500ms = 1'b1 ;// wire end_cnt_500ms ;assign end_cnt_500ms = add_cnt_500ms && (cnt_500ms == (MAX_CNT_500MS - 1)) ;// wire add_cnt_state ;assign add_cnt_state = end_cnt_500ms ;// && led_flag// wire end_cnt_state ;assign end_cnt_state = ((add_cnt_state && (cnt_state == 3'b101 )) ) ; // output reg [3:0] led_out always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) led_out <= 4'b0000 ;else case (cnt_state)3'b000 : led_out <= 4'b0001 ;3'b001 : led_out <= 4'b0010 ;3'b010 : led_out <= 4'b0100 ;3'b011 : led_out <= 4'b1000 ;3'b100 : led_out <= 4'b0100 ;3'b101 : led_out <= 4'b0010 ;default: led_out <= 4'b0000 ;endcaseend

endmodule

module state_led_ctrl (input wire sys_clk ,input wire sys_rst_n ,input wire water_flag ,input wire paoma_flag ,input wire shanshuo_flag ,input wire [3:0] led_water ,input wire [3:0] led_paoma ,input wire [3:0] led_shanshuo ,output reg [3:0] led_out

);localparam IDLE = 4'b0001 ,WATER = 4'b0010 ,PAOMA = 4'b0100 ,SHANSHUO = 4'b1000 ;// reg signal definereg [3:0] state_c ;reg [3:0] state_n ;// wire signalwire IDLEtoWATER ;wire IDLEtoPAOMA ;wire IDLEtoSHANSHUO ;wire WATERtoPAOMA ;wire WATERtoSHANSHUO ;wire PAOMAtoWATER ;wire PAOMAtoSHANSHUO ;wire SHANSHUOtoPAOMA ;wire SHANSHUOtoWATER ;

/******************************************************************************************

********************************************main code**************************************

*******************************************************************************************/// // reg signal define// reg state_c ;always @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) state_c <= IDLE ;elsestate_c <= state_n ;end// reg state_n ;always @(*) begincase(state_c)IDLE : if(IDLEtoWATER)state_n = WATER ;else if(IDLEtoPAOMA)state_n = PAOMA ;else if(IDLEtoSHANSHUO)state_n = SHANSHUO ;else state_n = IDLE ;WATER : if(WATERtoPAOMA)state_n = PAOMA ;else if(WATERtoSHANSHUO)state_n = SHANSHUO ;else state_n = WATER ;PAOMA : if(PAOMAtoWATER)state_n = WATER ;else if(PAOMAtoSHANSHUO)state_n = SHANSHUO ;else state_n = PAOMA ;SHANSHUO : if(SHANSHUOtoPAOMA)state_n = PAOMA ;else if(SHANSHUOtoWATER)state_n = WATER ;else state_n = SHANSHUO ;default : state_n = IDLE ;endcaseendassign IDLEtoWATER = (state_c == IDLE ) && (water_flag ) ;assign IDLEtoPAOMA = (state_c == IDLE ) && (paoma_flag ) ;assign IDLEtoSHANSHUO = (state_c == IDLE ) && (shanshuo_flag) ;assign WATERtoPAOMA = (state_c == WATER ) && (paoma_flag ) ;assign WATERtoSHANSHUO = (state_c == WATER ) && (shanshuo_flag) ;assign PAOMAtoWATER = (state_c == PAOMA ) && (water_flag ) ;assign PAOMAtoSHANSHUO = (state_c == PAOMA ) && (shanshuo_flag) ;assign SHANSHUOtoPAOMA = (state_c == SHANSHUO ) && (paoma_flag ) ;assign SHANSHUOtoWATER = (state_c == SHANSHUO ) && (water_flag ) ;// led_outalways @(posedge sys_clk or negedge sys_rst_n) beginif(~sys_rst_n) led_out <= 4'hf ;else case (state_c)IDLE : led_out <= 4'hf ;WATER : led_out <= led_water ;PAOMA : led_out <= led_paoma ;SHANSHUO: led_out <= led_shanshuo ;default: led_out <= 4'hf ;endcaseendendmodule

module top (input wire sys_clk ,input wire sys_rst_n ,input wire key_water ,input wire key_paoma ,input wire key_shanshuo ,output wire [3:0] led_out

);// inst wirewire water_flag ;wire paoma_flag ;wire shanshuo_flag ;wire [3:0] led_water ;wire [3:0] led_paoma ;wire [3:0] led_shanshuo ;// inst

key_filter key_filter_inst_water(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_in ( key_water ) ,.key_flag ( water_flag )

);key_filter key_filter_inst_paoma(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_in ( key_paoma ) ,.key_flag ( paoma_flag )

);key_filter key_filter_inst_shanshuo(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_in ( key_shanshuo ) ,.key_flag ( shanshuo_flag )

);led_water led_water_isnt (.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.led_out ( led_water )

);led_paoma led_paoma_inst(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.led_out ( led_paoma )

);shanshuo shanshuo_inst(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.led_out ( led_shanshuo )

);state_led_ctrl state_led_ctrl_inst(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.water_flag ( water_flag ) ,.paoma_flag ( paoma_flag ) ,.shanshuo_flag ( shanshuo_flag ) ,.led_water ( led_water ) ,.led_paoma ( led_paoma ) ,.led_shanshuo ( led_shanshuo ) ,.led_out ( led_out )

);endmodule

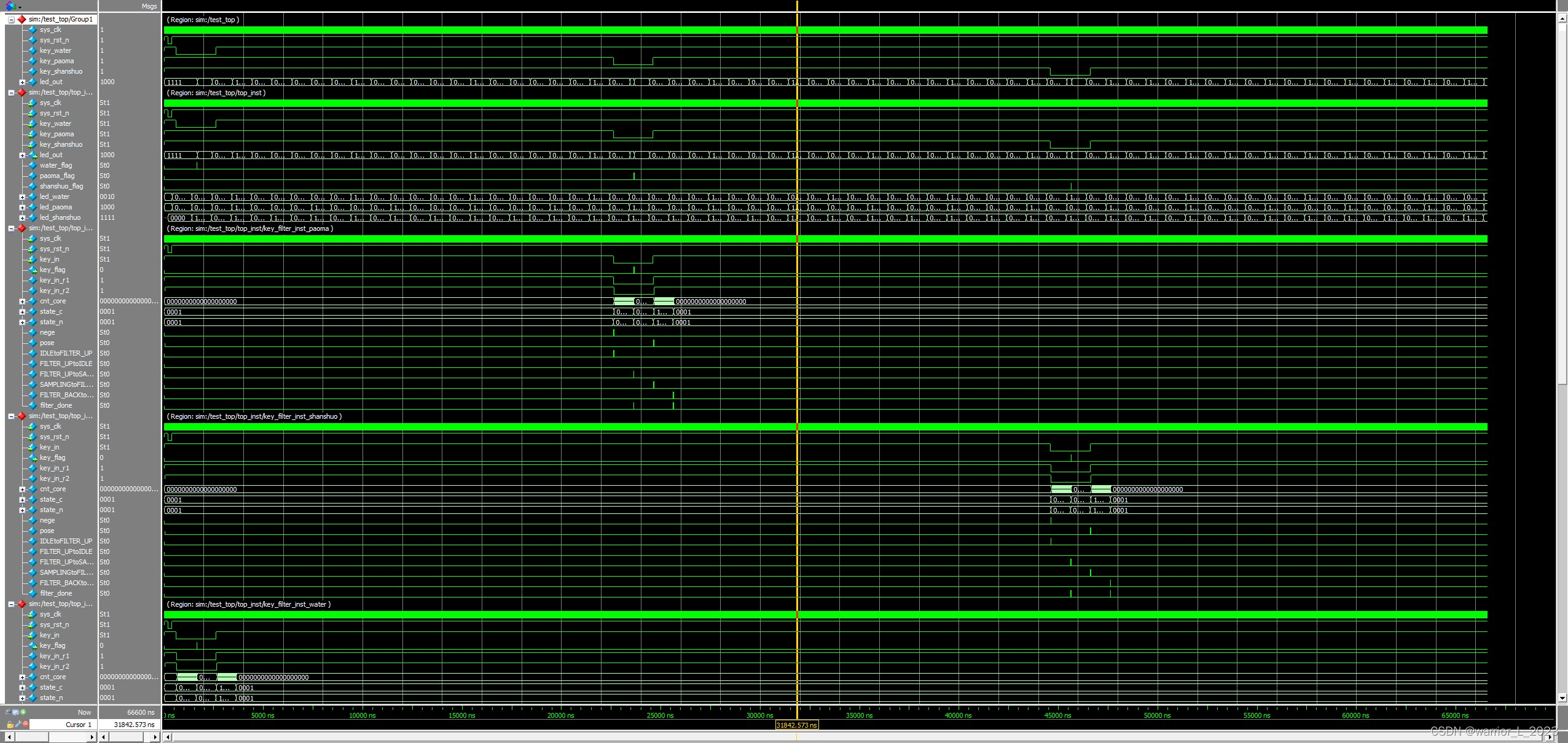

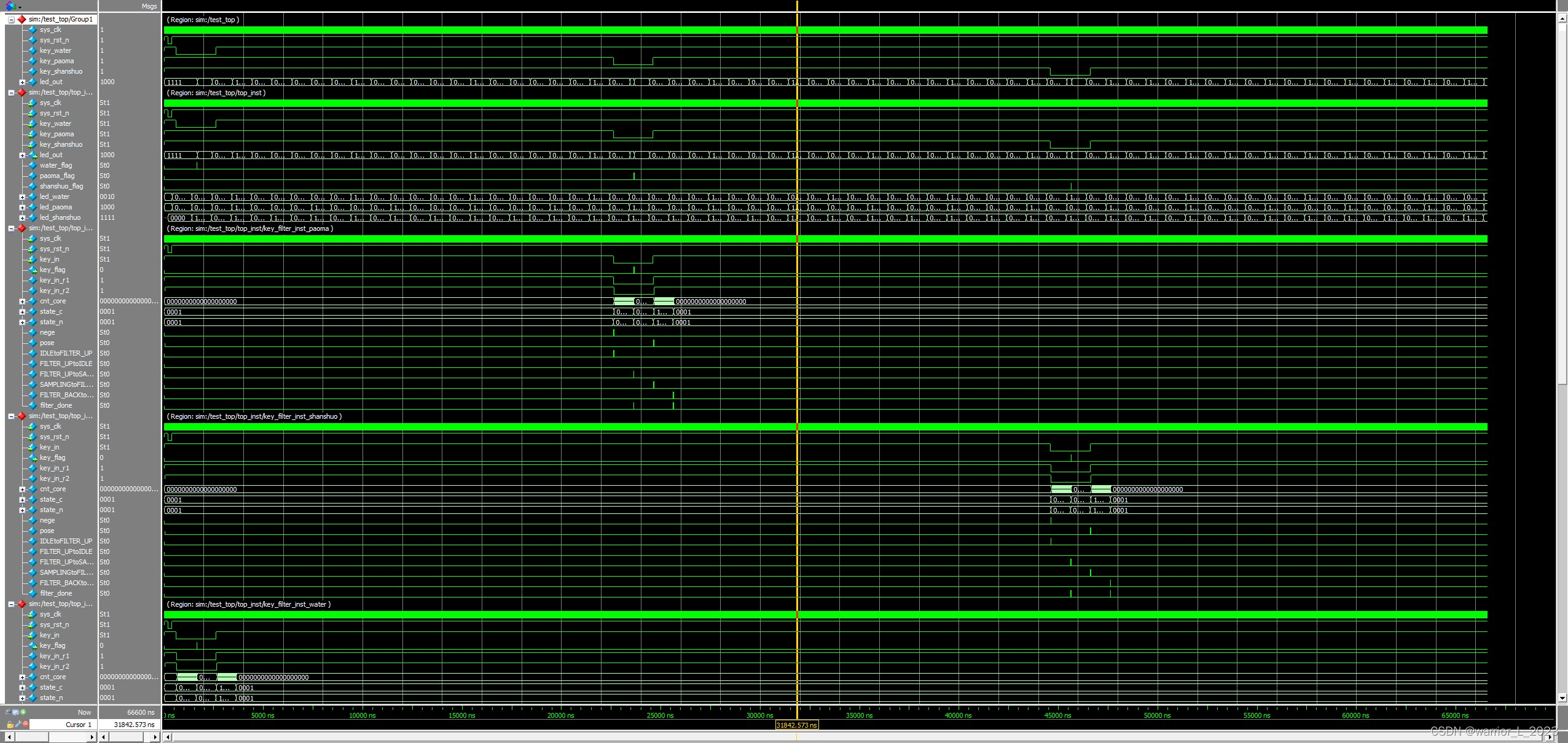

仿真:

`timescale 1ns/1ns

module test_top ();reg sys_clk ;reg sys_rst_n ;reg key_water ;reg key_paoma ;reg key_shanshuo ;wire [3:0] led_out ;top top_inst(.sys_clk ( sys_clk ) ,.sys_rst_n ( sys_rst_n ) ,.key_water ( key_water ) ,.key_paoma ( key_paoma ) ,.key_shanshuo ( key_shanshuo ) ,.led_out ( led_out )

);defparam top_inst.key_filter_inst_water.MAX_CNT_10MS = 50 ;defparam top_inst.key_filter_inst_paoma.MAX_CNT_10MS = 50 ;defparam top_inst.key_filter_inst_shanshuo.MAX_CNT_10MS = 50 ;defparam top_inst.led_water_isnt.MAX_CNT_500MS = 50 ;defparam top_inst.led_paoma_inst.MAX_CNT_500MS = 50 ;defparam top_inst.shanshuo_inst.MAX_CNT_500MS = 50 ;parameter CYCLE = 20 ;initial beginsys_clk = 1'b1 ;sys_rst_n <= 1'b1 ;key_water <= 1'b1 ;key_paoma <= 1'b1 ;key_shanshuo<= 1'b1 ;#( CYCLE * 10 ) ;sys_rst_n <= 1'b0 ;#( 200 ) ;sys_rst_n <= 1'b1 ;#( CYCLE * 10 ) ;key_water <= 1'b0 ;#( CYCLE * 100 ) ;key_water <= 1'b1 ;#( CYCLE * 1000 ) ;key_paoma <= 1'b0 ;#( CYCLE * 100 ) ;key_paoma <= 1'b1 ;#( CYCLE * 1000 ) ;key_shanshuo <= 1'b0;#( CYCLE * 100 ) ;key_shanshuo <= 1'b1;#( CYCLE * 1000 ) ;$stop ;endalways #( CYCLE / 2 ) sys_clk = ~sys_clk ;endmodule

相关文章:

状态机的练习:按键控制led灯

设计思路: 三个按键控制led输出。 三个按键经过滤波(消抖),产生三个按键标志信号。 三个led数据的产生模块(流水,跑马,闪烁模块),分别产生led信号。 这六路信号(三路按键信号&am…...

看图学源码之 CopyOnWriteArraySet源码分析

基本介绍 使用内部CopyOnWriteArrayList进行所有操作的Set 特点 它最适合以下应用程序:集合大小通常较小、只读操作的数量远远多于可变操作,并且您需要在遍历期间防止线程之间的干扰。它是线程安全的。突变操作( add 、 set 、 remove等&…...

almaLinux centos8 下载ffmpeg离线安装包、离线安装

脚本 # 添加RPMfusion仓库 sudo yum install https://download1.rpmfusion.org/free/el/rpmfusion-free-release-8.noarch.rpm wget -ymkdir -p /root/ffmpeg cd /root/ffmpegwget http://rpmfind.net/linux/epel/7/x86_64/Packages/s/SDL2-2.0.14-2.el7.x86_64.rpmyum instal…...

CSS3 属性: transition过渡 与 transform动画

CSS3 提供了很多强大的功能,使开发人员可以创建更加吸引人的视觉效果,而不需要依赖于 JavaScript 或 Flash。其中,transition 和 transform 是两个常用的属性,它们分别用于创建平滑的过渡效果和元素的变形效果。下面我们将详细介绍…...

TCP通讯

第二十一章 网络通信 本章节主要讲解的是TCP和UDP两种通信方式它们都有着自己的优点和缺点 这两种通讯方式不通的地方就是TCP是一对一通信 UDP是一对多的通信方式 接下来会一一讲解 TCP通信 TCP通信方式呢 主要的通讯方式是一对一的通讯方式,也有着优点和缺点 …...

(NeRF学习)3D Gaussian Splatting Instant-NGP

学习参考: 3D Gaussian Splatting入门指南【五分钟学会渲染自己的NeRF模型,有手就行!】 三维重建instant-ngp环境部署与colmap、ffmpeg的脚本参数使用 一、3D Gaussian Splatting (一)3D Gaussian Splatting环境配置…...

uni-app 微信小程序之好看的ui登录页面(三)

文章目录 1. 页面效果2. 页面样式代码 更多登录ui页面 uni-app 微信小程序之好看的ui登录页面(一) uni-app 微信小程序之好看的ui登录页面(二) uni-app 微信小程序之好看的ui登录页面(三) uni-app 微信小程…...

Android 默认打开应用的权限

有项目需要客户要安装第三方软件,但是要手动点击打开权限,就想不动手就打开。 //安装第三方软件,修改方式 frameworks\base\services\core\java\com\android\server\pm\PackageManagerService.java //找到如下源码: //有三种方…...

2023年广东工业大学腾讯杯新生程序设计竞赛

E.不知道叫什么名字 题意:找一段连续的区间,使得区间和为0且区间长度最大,输出区间长度。 思路:考虑前缀和,然后使用map去记录每个前缀和第一次出现的位置,然后对数组进行扫描即可。原理:若 s …...

如何访问Github下载FFmpeg源码)

FFmpeg开发笔记(六)如何访问Github下载FFmpeg源码

学习FFmpeg的时候,经常要到GitHub下载各种开源代码,比如FFmpeg的源码页面位于https://github.com/FFmpeg/FFmpeg。然而国内访问GitHub很不稳定,经常打不开该网站,比如在命令行执行下面的ping命令。 ping github.com 上面的ping结…...

SpringCloud | Dubbo 微服务实战——注册中心详解

前言 「作者主页」:雪碧有白泡泡 「个人网站」:雪碧的个人网站 |Eureka,Nacos,Consul,Zookeeper在Spring Cloud和Dubbo中实战 引言 在项目开发过程中,随着项目不断扩大,也就是业务的不断增多,我们将采用集群…...

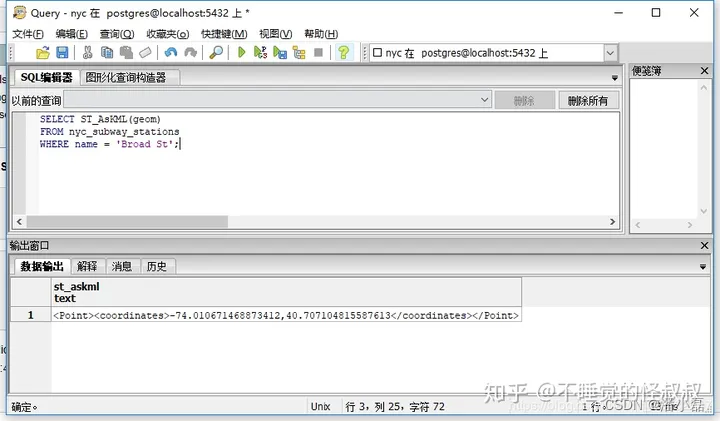

PostGIS学习教程十一:投影数据

PostGIS学习教程十一:投影数据 地球不是平的,也没有简单的方法把它放在一张平面纸地图上(或电脑屏幕上),所以人们想出了各种巧妙的解决方案(投影)。 每种投影方案都有优点和缺点,一…...

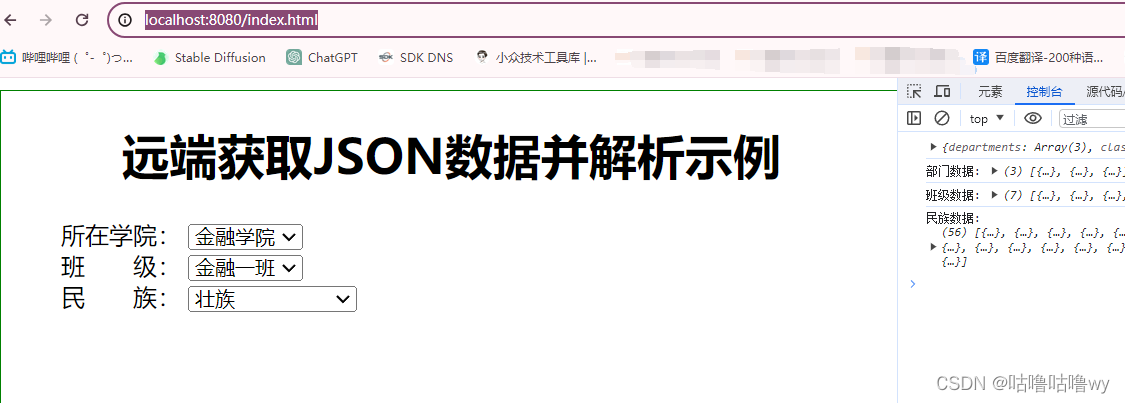

jQuery ajax读取本地json文件 三级联动下拉框

步骤 1:创建本地JSON文件 {"departments": [{"name": "会计学院","code": "052"},{"name": "金融学院","code": "053"},{"name": "财税学院",&qu…...

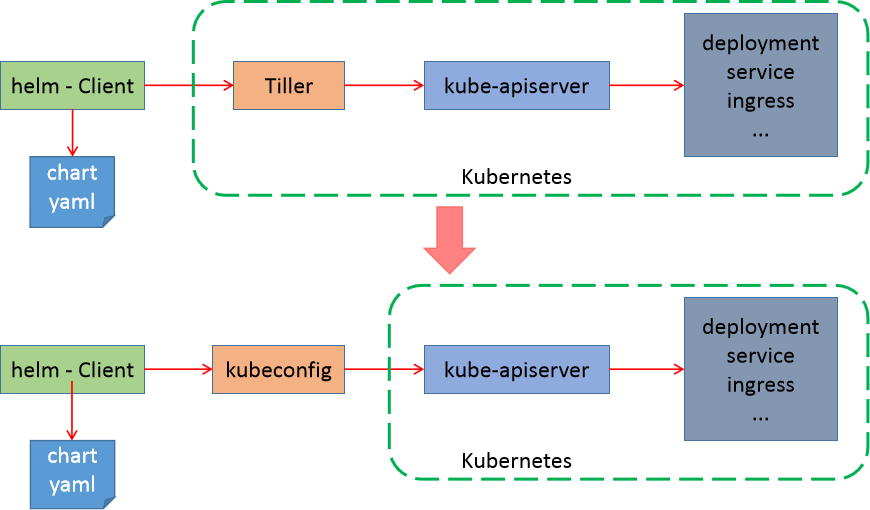

Kubernetes(K8s 1.27.x) 快速上手+实践,无废话纯享版(视频笔记)

视频源:1.03-k8s是什么?_哔哩哔哩_bilibili 1 基础知识 1.1 K8s 有用么? K8s有没有用 K8s要不要学? 参考资料: https://www.infoq.com/articles/devops-and-cloud-trends-2022/?itm_sourcearticles_about_InfoQ-trends-report…...

深度学习实战66-基于计算机视觉的自动驾驶技术,利用YOLOP模型实现车辆区域检测框、可行驶区域和车道线分割图

大家好,我是微学AI,今天给大家介绍一下深度学习实战66-基于计算机视觉的自动驾驶技术,利用YOLOP模型实现车辆区域检测框、可行驶区域和车道线分割图。本文我将介绍自动驾驶技术及其应用场景,并重点阐述了基于计算机视觉技术下的自动驾驶。自动驾驶技术是一种利用人工智能和…...

Stable Diffusion 系列教程 - 1 基础准备(针对新手)

使用SD有两种方式: 本地: 显卡要求:硬件环境推荐NVIDIA的具有8G显存的独立显卡,这个显存勉勉强强能摸到门槛。再往下的4G可能面临各种炸显存、炼丹失败、无法生成图片等各种问题。对于8G显存,1.0模型就不行࿰…...

听GPT 讲Rust源代码--src/tools(8)

File: rust/src/tools/rust-analyzer/crates/ide-assists/src/handlers/add_missing_match_arms.rs 在Rust源代码中,rust-analyzer是一个Rust编程语言的语言服务器。它提供了代码补全、代码重构和代码导航等功能来帮助开发者提高编码效率。 在rust-analyzer的代码目…...

Linux硬链接和软连接是什么?

在Linux操作系统中,文件管理是一个基本且重要的概念。其中,软链接(Symbolic Link)和硬链接(Hard Link)是文件系统中两种不同类型的链接方式,它们在文件管理和操作中扮演着重要的角色。软链接 软…...

LangChain 23 Agents中的Tools用于增强和扩展智能代理agent的功能

LangChain系列文章 LangChain 实现给动物取名字,LangChain 2模块化prompt template并用streamlit生成网站 实现给动物取名字LangChain 3使用Agent访问Wikipedia和llm-math计算狗的平均年龄LangChain 4用向量数据库Faiss存储,读取YouTube的视频文本搜索I…...

VS2015编译GDAL3.2.0+opencl+C#

参考借鉴https://www.cnblogs.com/litou/p/15004877.html 参考借鉴https://www.cnblogs.com/xiaowangba/p/6313903.html 参考借鉴gdal、proj、geos、sqlite等在VS2015下编译和配置_vs2015编译sqlite3-CSDN博客 参考借鉴Windows下GDAL3.1.2编译 (VS2015)_gdal windows编译-CS…...

linux之kylin系统nginx的安装

一、nginx的作用 1.可做高性能的web服务器 直接处理静态资源(HTML/CSS/图片等),响应速度远超传统服务器类似apache支持高并发连接 2.反向代理服务器 隐藏后端服务器IP地址,提高安全性 3.负载均衡服务器 支持多种策略分发流量…...

【杂谈】-递归进化:人工智能的自我改进与监管挑战

递归进化:人工智能的自我改进与监管挑战 文章目录 递归进化:人工智能的自我改进与监管挑战1、自我改进型人工智能的崛起2、人工智能如何挑战人类监管?3、确保人工智能受控的策略4、人类在人工智能发展中的角色5、平衡自主性与控制力6、总结与…...

测试markdown--肇兴

day1: 1、去程:7:04 --11:32高铁 高铁右转上售票大厅2楼,穿过候车厅下一楼,上大巴车 ¥10/人 **2、到达:**12点多到达寨子,买门票,美团/抖音:¥78人 3、中饭&a…...

【决胜公务员考试】求职OMG——见面课测验1

2025最新版!!!6.8截至答题,大家注意呀! 博主码字不易点个关注吧,祝期末顺利~~ 1.单选题(2分) 下列说法错误的是:( B ) A.选调生属于公务员系统 B.公务员属于事业编 C.选调生有基层锻炼的要求 D…...

学习STC51单片机32(芯片为STC89C52RCRC)OLED显示屏2

每日一言 今天的每一份坚持,都是在为未来积攒底气。 案例:OLED显示一个A 这边观察到一个点,怎么雪花了就是都是乱七八糟的占满了屏幕。。 解释 : 如果代码里信号切换太快(比如 SDA 刚变,SCL 立刻变&#…...

DeepSeek 技术赋能无人农场协同作业:用 AI 重构农田管理 “神经网”

目录 一、引言二、DeepSeek 技术大揭秘2.1 核心架构解析2.2 关键技术剖析 三、智能农业无人农场协同作业现状3.1 发展现状概述3.2 协同作业模式介绍 四、DeepSeek 的 “农场奇妙游”4.1 数据处理与分析4.2 作物生长监测与预测4.3 病虫害防治4.4 农机协同作业调度 五、实际案例大…...

Python网页自动化Selenium中文文档

1. 安装 1.1. 安装 Selenium Python bindings 提供了一个简单的API,让你使用Selenium WebDriver来编写功能/校验测试。 通过Selenium Python的API,你可以非常直观的使用Selenium WebDriver的所有功能。 Selenium Python bindings 使用非常简洁方便的A…...

客户案例 | 短视频点播企业海外视频加速与成本优化:MediaPackage+Cloudfront 技术重构实践

01技术背景与业务挑战 某短视频点播企业深耕国内用户市场,但其后台应用系统部署于东南亚印尼 IDC 机房。 随着业务规模扩大,传统架构已较难满足当前企业发展的需求,企业面临着三重挑战: ① 业务:国内用户访问海外服…...

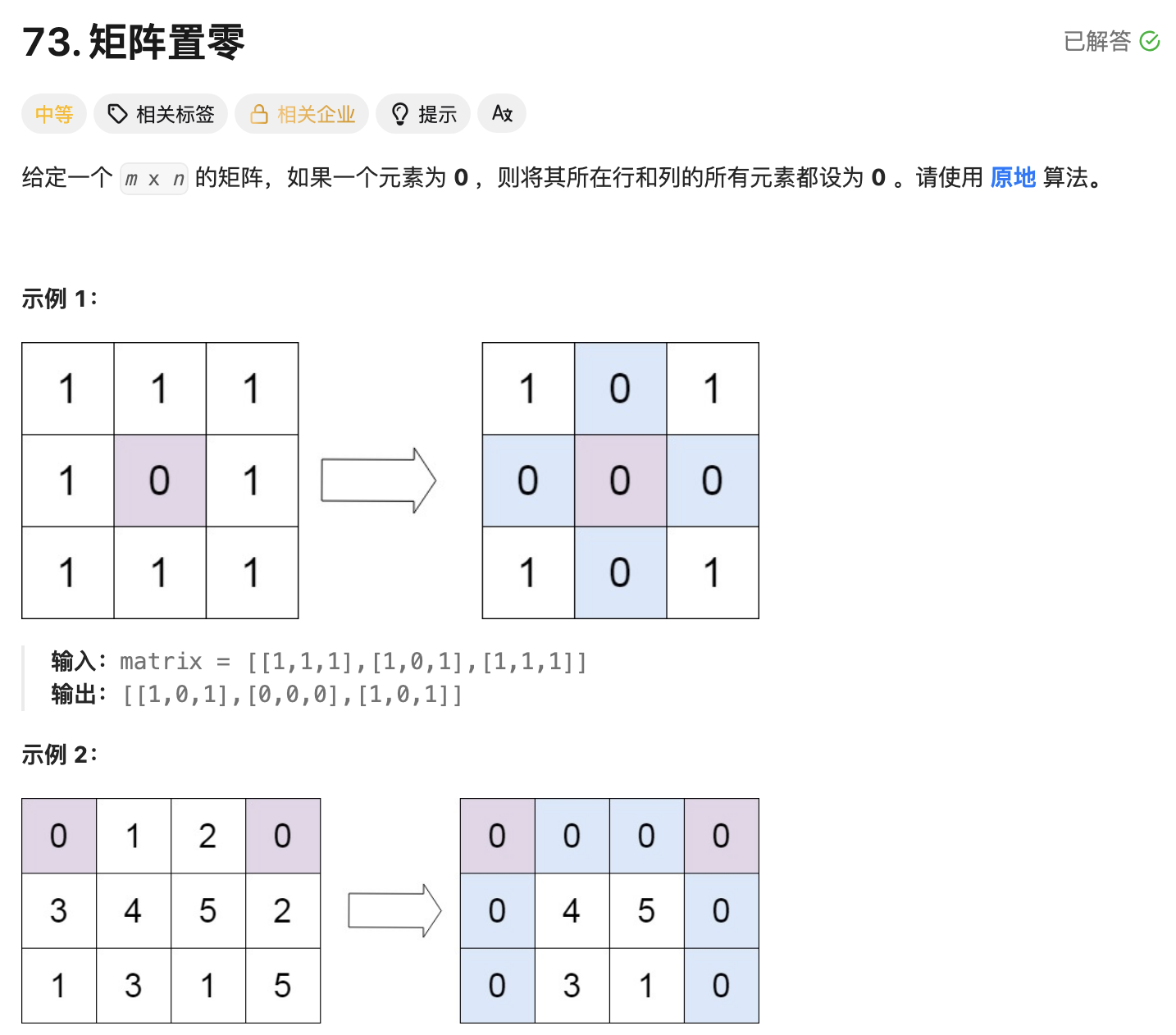

leetcode73-矩阵置零

leetcode 73 思路 记录 0 元素的位置:遍历整个矩阵,找出所有值为 0 的元素,并将它们的坐标记录在数组zeroPosition中置零操作:遍历记录的所有 0 元素位置,将每个位置对应的行和列的所有元素置为 0 具体步骤 初始化…...

Java多线程实现之Runnable接口深度解析

Java多线程实现之Runnable接口深度解析 一、Runnable接口概述1.1 接口定义1.2 与Thread类的关系1.3 使用Runnable接口的优势 二、Runnable接口的基本实现方式2.1 传统方式实现Runnable接口2.2 使用匿名内部类实现Runnable接口2.3 使用Lambda表达式实现Runnable接口 三、Runnabl…...