暑期实习准备——Verilog手撕代码(持续更新中。。。

暑期实习准备——手撕代码

- 牛客刷题笔记

- Verilog快速入门

- VL4 移位运算与乘法

- VL5 位拆分与运算

- VL6 多功能数据处理器

- VL8 使用generate…for语句简化代码

- VL9 使用子模块实现三输入数的大小比较

- VL11 4位数值比较器电路

- VL12 4bit超前进位加法器电路

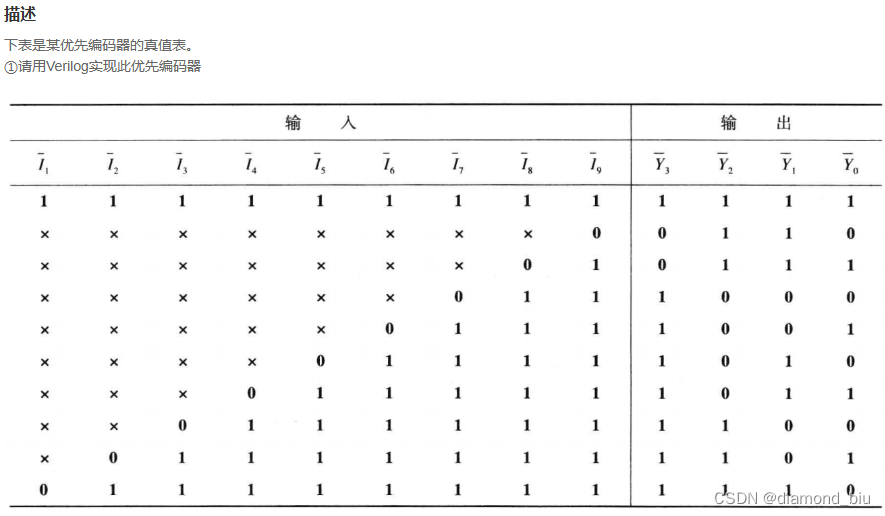

- VL13 优先编码器电路①

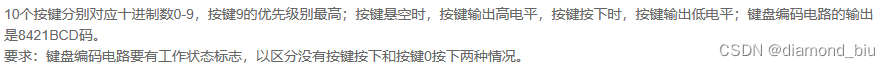

- VL14 用优先编码器①实现键盘编码电路

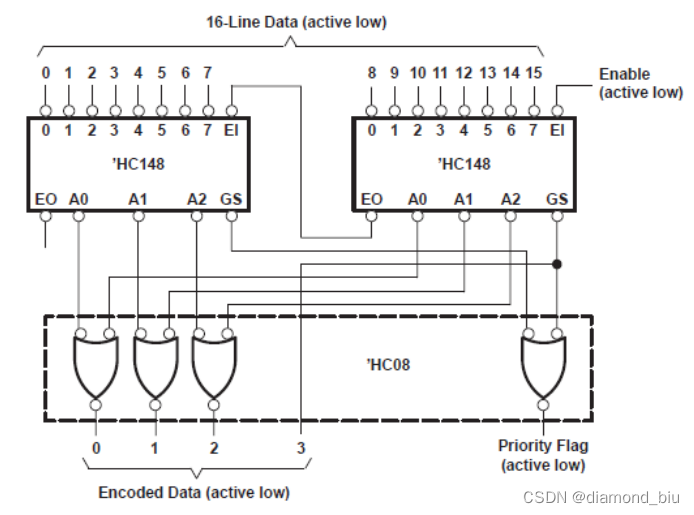

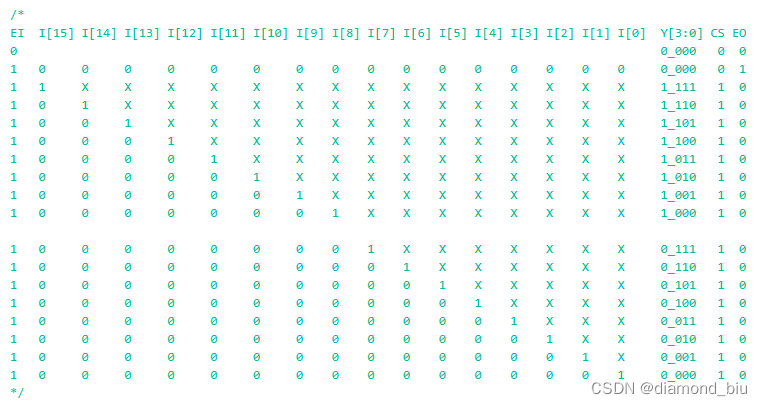

- VL16 使用8线-3线优先编码器Ⅰ实现16线-4线优先编码器

- Verilog进阶挑战

- Verilog企业真题

- 常见数字IC手撕代码

牛客刷题笔记

牛客Verilog题库

Verilog快速入门

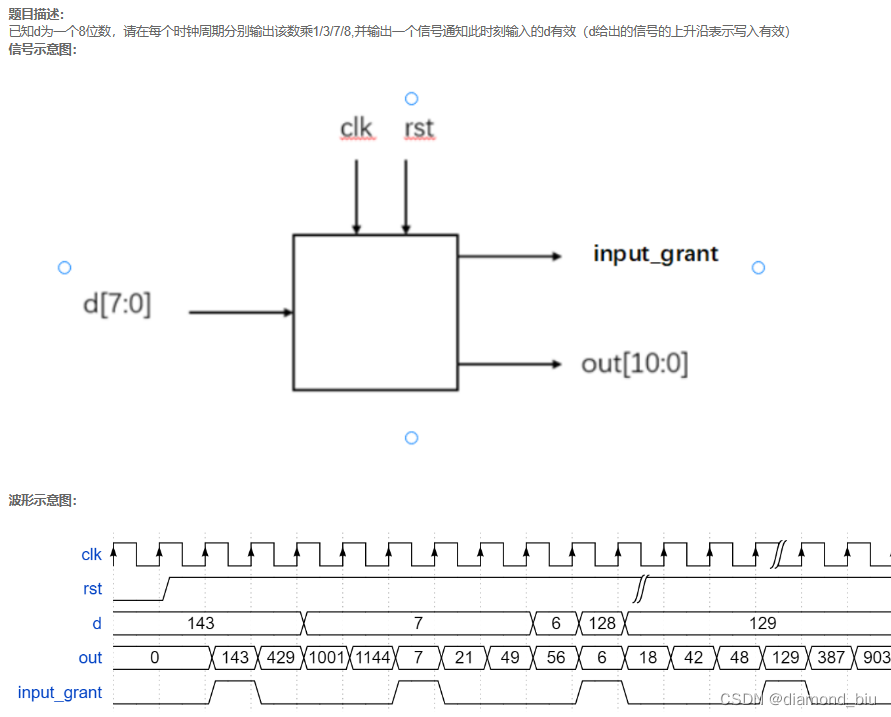

VL4 移位运算与乘法

- 要点1:题目用状态机实现,经典的两段式模板。

- 要点2:需要一个d_reg信号临时记录当前要加倍的d信号,这样才能保证d信号变化时,加倍的仍然是原本的d信号,注意d_reg<=d;赋值语句应该在11状态,即每一轮状态转换结束后,开启新一轮状态前。

- 要点3:always @ (posedge clk or negedge rst or current_state) 第二段的敏感事件表套模板的时候误删了current_state信号,导致所有的状态机状态转换被延长了一拍,因此这里的敏感时间表一定要将记住写current_state。

- 要点4:注意为状态机以及其他输出信号赋初始值。

- 要点5:1、3、7、8倍数通过移位运算和加运算实现,不需要乘法运算。

`timescale 1ns/1ns

module multi_sel(

input [7:0]d ,

input clk,

input rst,

output reg input_grant,

output reg [10:0]out

);

reg [1:0] current_state,next_state;

reg[7:0] d_reg;

//*************code***********//always @ (posedge clk or negedge rst) beginif(!rst) current_state<=2'b00;else current_state<=next_state;//非阻塞赋值

endalways @ (posedge clk or negedge rst or current_state) beginnext_state<=2'b00;if(!rst) begininput_grant<=1'b0;out<=11'b0;d_reg<=d;endelse begincase(current_state)2'b00:begininput_grant<=1'b1;out<=d_reg;next_state<=2'b01;end2'b01:begininput_grant<=1'b0;out<= d_reg + {2'b0, d_reg, 1'b0};next_state<=2'b10;end2'b10:begininput_grant<=1'b0;out<=d_reg + {2'b0, d_reg, 1'b0} + {1'b0 ,d_reg, 2'b00};next_state<=2'b11;end2'b11:begininput_grant<=1'b0;out<={d_reg, 3'b000};next_state<=2'b00;d_reg<=d;endendcaseend

end

//*************code***********//

endmodule

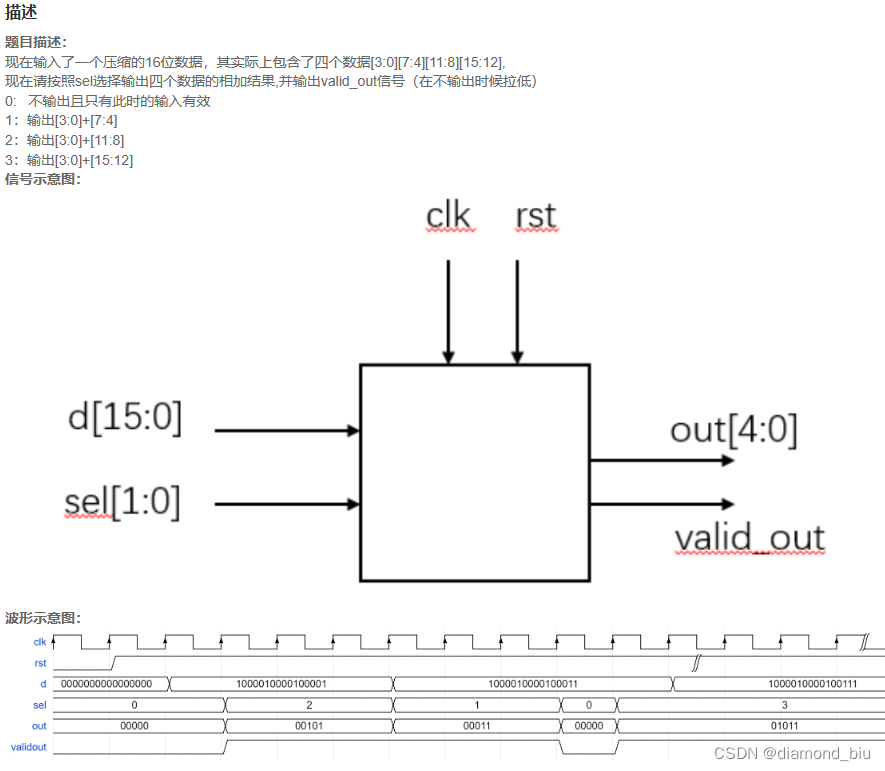

VL5 位拆分与运算

- 要点1:仔细读题,注意题目中提到的只有在sel=0时输入才有效,因此需要reg_d把输入d锁存。

- 要点2:仔细读题,还是要理解题目的意思。

`timescale 1ns/1nsmodule data_cal(

input clk,

input rst,

input [15:0]d,

input [1:0]sel,output reg [4:0]out,

output reg validout

);

//*************code***********//

reg [15:0] reg_d;always @ (posedge clk or rst or d) beginif(!rst) beginout<=5'b0;validout<=0;endelse begincase(sel)2'b00:begin out<=5'b0; validout<=0; reg_d<=d ;end2'b01:begin out<=reg_d[3:0]+reg_d[7:4]; validout<=1; end2'b10:begin out<=reg_d[3:0]+reg_d[11:8]; validout<=1; end2'b11:begin out<=reg_d[3:0]+reg_d[15:12]; validout<=1; endendcaseend

end

//*************code***********//

endmodule

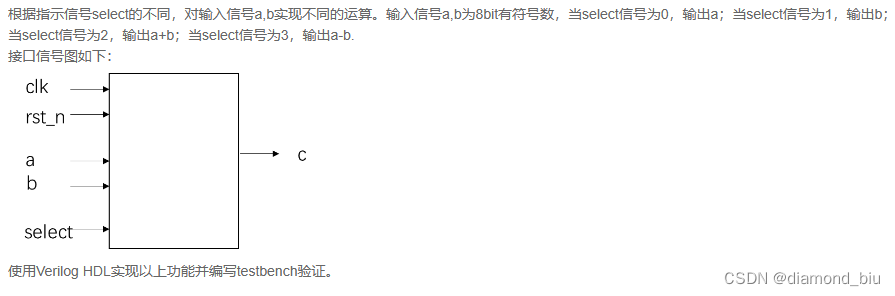

VL6 多功能数据处理器

- 要点1:有符号数以补码形式存储,可以直接进行加减运算。

- 要点2:

always @ (posedge clk or negedge rst_n)的写法是正确的,但有点疑惑是初始状态下就是低电平会不会触发,本题既然是正确的就说明初始低电平会触发。

always @ (posedge clk or rst_n)的写法是错误的,会在rst_n由0变为1时触发,但此时可能并非时钟上升沿,造成异常输出。

always @ (posedge clk)的写法会使得初始状态下输出信号处于无效状态,额外在always块前加上initial c<=9'b0;这样可以通过测试用例,但是initial语句不可综合,最好不要使用。

`timescale 1ns/1ns

module data_select(input clk,input rst_n,input signed[7:0]a,input signed[7:0]b,input [1:0]select,output reg signed [8:0]c

);always @ (posedge clk or negedge rst_n) beginif(!rst_n) beginc<=9'b0;endelse begincase(select)2'b00:begin c<=a; end2'b01:begin c<=b; end2'b10:begin c<=a+b; end2'b11:begin c<=a-b; endendcaseend

end

endmodule

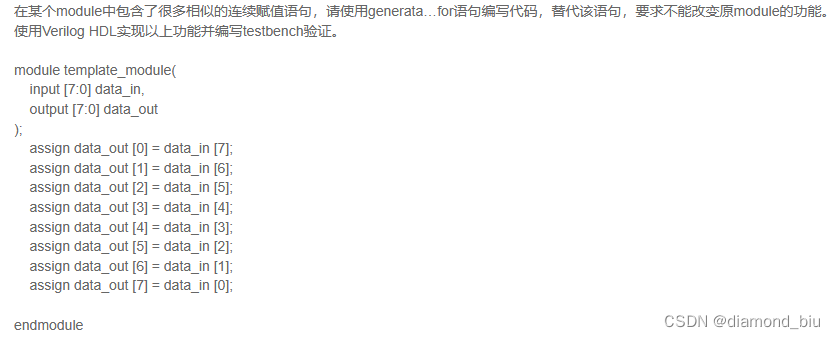

VL8 使用generate…for语句简化代码

- 要点1:必须使用

genvar声明循环变量。 - 要点2:

begin-end之间插入赋值语句,begin后面必须声明循环实例的名称。 - 要点3:

generate-for常用来简化assign的赋值,assign data_out[i]=data_in[7-i];展开后的8条assign语句是并行赋值的。如,在6线-64线、8线-256线译码器中可以用来简化代码。

`timescale 1ns/1ns

module gen_for_module( input [7:0] data_in,output [7:0] data_out

);genvar i;generate for(i=0;i<=7;i=i+1)begin:labelassign data_out[i]=data_in[7-i];endendgenerate

endmodule

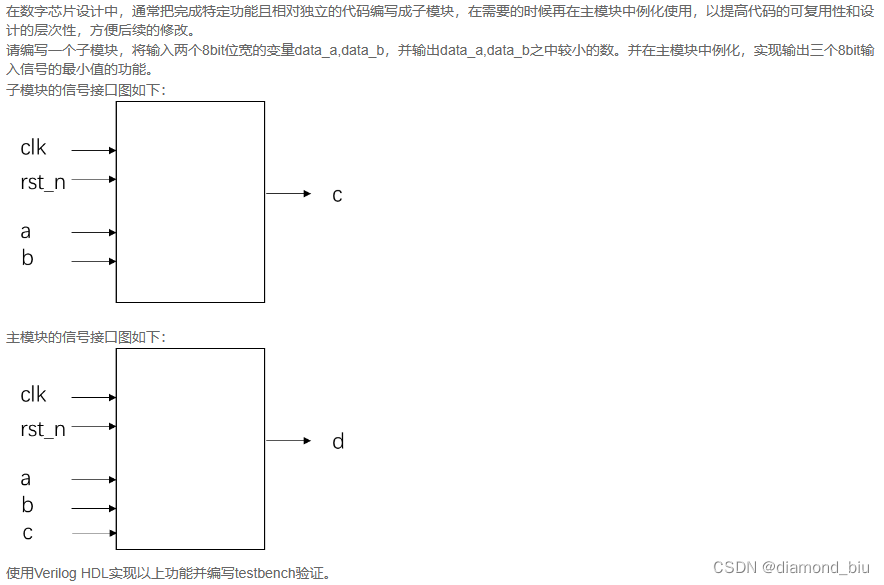

VL9 使用子模块实现三输入数的大小比较

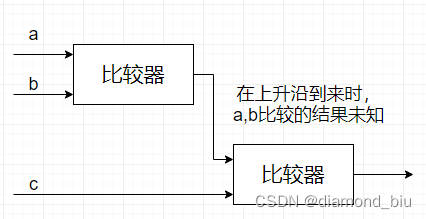

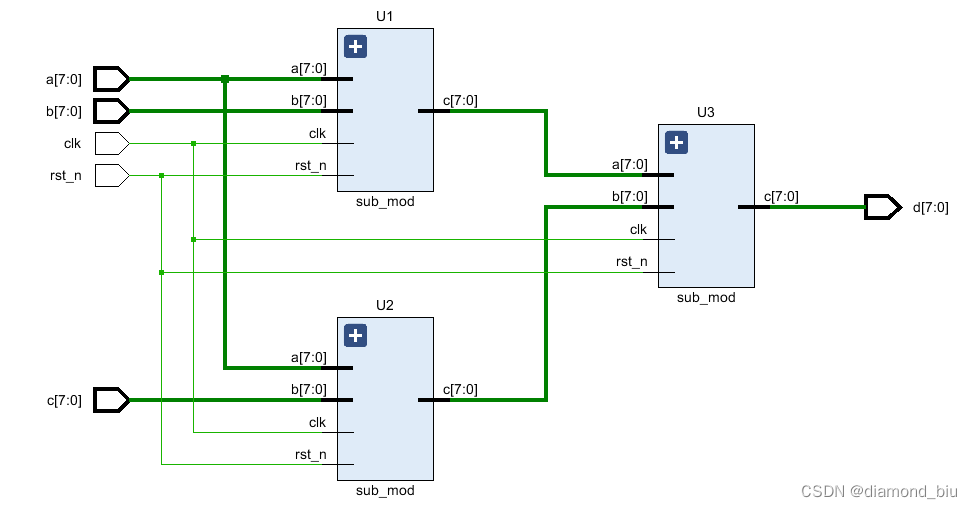

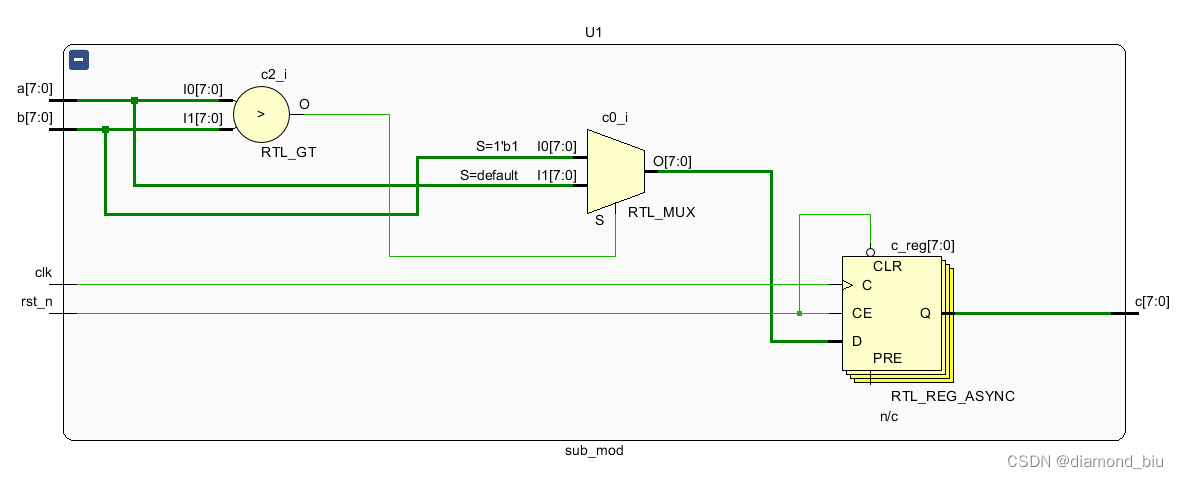

- 要点1:两个比较器会导致进入比较器的三个输入时间不同步,需要使用三个子模块才可以正确实现。

在第一个上升沿,ab进入第一个比较器,c进入第二个比较器。但是比较器输出是需要时间的,在第一个上升沿,c立刻进入第二个比较器,但ab比较器的输出会较晚的进入第二个比较器,这就造成了输入时间不同步,从而造成输出错误。

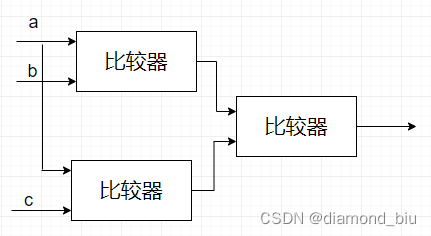

使用三个比较器将c延迟一拍,就可以让输入子模块的时间都相等,从而不会出现进入时间不同导致的错误。

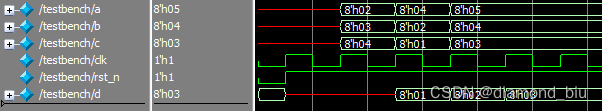

我们可以对波形进行分析来比较这两种写法的差别,testbench如下:

`timescale 1ns/1ns

module testbench();reg signed [7:0] a,b,c;reg clk,rst_n;wire [7:0]d;

main_mod dut(.clk(clk),.rst_n(rst_n),.a(a),.b(b),.c(c),.d(d)

);

always #5 clk = !clk;

initial beginclk=0;rst_n=0;#5 rst_n=1;#10 a=2;b=3;c=4;#10 a=4;b=2;c=1;#10 a=5;b=4;c=3;

end

endmodule

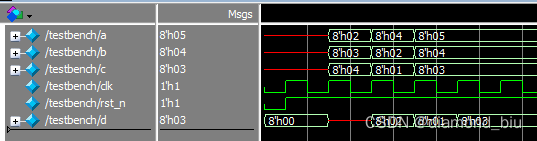

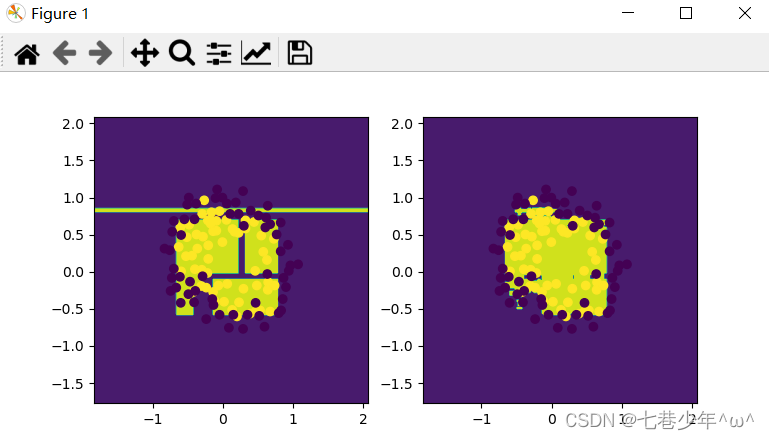

三个比较器的仿真波形如下。可以看到每一次比较的结果都在下一个时钟周期输出,分别为2,1,3。

二个比较器的仿真波形如下,此时比较结果为1,2,3,这是因为上一轮a,b的最小值实际上是与当前周期的c进行比较的,因此对于第一组输入,a和b的比较结果是2,2和下一组输入的c=1进行了比较,所以输出的最小值是1;同样第二组输出,a和b的比较结果是2,2和下一组输入的c=3进行了比较,所以输出为2;第二组输出,a和b的比较结果是4,4和下一组输入的c=3进行了比较,所以输出为3。

- 要点2:子模块中

c<=(a>b)?b:a;语句需要使用非阻塞赋值。

不知道为什么非阻塞不会报错,阻塞会报错显示有用例不通过。使用vivado综合出来的电路这两个是一样的。待解决!!!

但还是复习一下阻塞赋值和非阻塞赋值

非阻塞赋值b <= a;:非阻塞赋值中赋值并不是马上执行的,也就是说"always"块内的下一条语句执行后,b并不等于a,而是保持原来的值。"always"块结束后,才进行赋值。

阻塞赋值b=a;:方式是马上执行的。也就是说执行下一条语句时,b已等于a。

`timescale 1ns/1ns

module main_mod(input clk,input rst_n,input [7:0]a,input [7:0]b,input [7:0]c,output [7:0]d

);

wire [7:0] ab,ac;

sub_mod U1(.clk(clk),.rst_n(rst_n),.a(a),.b(b),.c(ab));

sub_mod U2(.clk(clk),.rst_n(rst_n),.a(a),.b(c),.c(ac));

sub_mod U3(.clk(clk),.rst_n(rst_n),.a(ab),.b(ac),.c(d));

endmodulemodule sub_mod(clk,rst_n,a,b,c);input clk,rst_n;input[7:0] a,b;output [7:0] c;reg[7:0]c;always@(posedge clk or negedge rst_n)beginif(~rst_n)c<=8'b0;else beginc<=(a>b)?b:a;endend

endmodule

VL11 4位数值比较器电路

要点1:题目中说要用门级描述完成,对于1bit数的比较对应的门运算如下,A>B对应~A&B,A<B对应A&~B,A=B对应~(A^B)。

`timescale 1ns/1nsmodule comparator_4(input [3:0] A ,input [3:0] B ,output wire Y2 , //A>Boutput wire Y1 , //A=Boutput wire Y0 //A<B

);assign Y2=(A[3]>B[3])|((A[3]==B[3])&(A[2]>B[2]))|((A[3]==B[3])&(A[2]==B[2])&(A[1]>B[1]))|((A[3]==B[3])&(A[2]==B[2])&(A[1]==B[1])&(A[0]>B[0]));

assign Y1=(A==B);

assign Y0=(A[3]<B[3])|((A[3]==B[3])&(A[2]<B[2]))|((A[3]==B[3])&(A[2]==B[2])&(A[1]<B[1]))|((A[3]==B[3])&(A[2]==B[2])&(A[1]==B[1])&(A[0]<B[0]));

endmodule

要点2:抽象描述可以写到直接比较A和B。

`timescale 1ns/1ns

module comparator_4(input [3:0] A ,input [3:0] B ,output wire Y2 , //A>Boutput wire Y1 , //A=Boutput wire Y0 //A<B

);

assign Y2=(A>B)?1:0;

assign Y1=(A==B)?1:0;

assign Y0=(A<B)?1:0;

endmodule

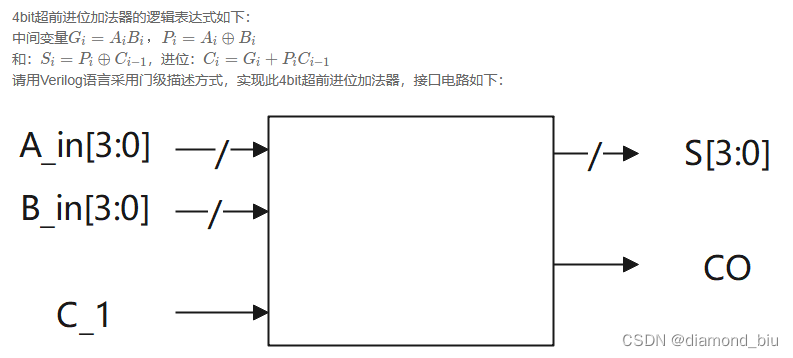

VL12 4bit超前进位加法器电路

加法器与半加器

超前进位加法器

1比特进位加法器的两种实现:

//实现1:逻辑代数

assign sum=a^b^cin;

assign cout=a&b|(cin&(a^b));或者assign cout=(a&b)|(a&cin)|(b&cin);

//实现2:抽象描述

assign {cout,sum}=a+b+cin;

assign cout=(a&b)|(a&cin)|(b&cin);很容易理解,即a,b,cin中任意两个或以上为1就进位。

assign cout=a&b|(cin&(a^b));可以理解为除了a,b为1的情况外,还有c为1同时 a和b中任意一个为1(a^b)。

多位数进位加法器

多位数进位加法器的实现有两种方式:串行进位加法器、超前进位加法器。

串行进位加法器就是将1比特加法器级联。

超前进位加法器是对串行全加器进行改良设计的并行加法器,以解决普通全加器串联互相进位产生的延迟。

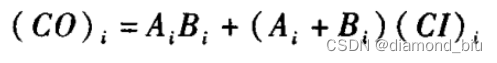

一位全加器的进位的运算逻辑(前面的式子是(A^B)这里是(A|B),对结果没有影响,|包含了^):

其中,令进位函数Gi = AiBi, 令进位传送函数Pi = Ai + Bi;

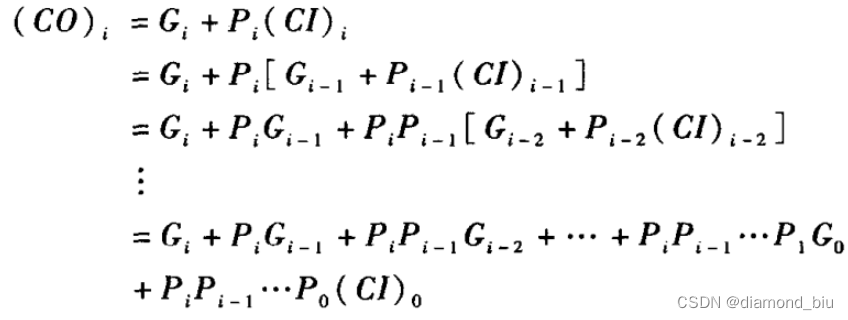

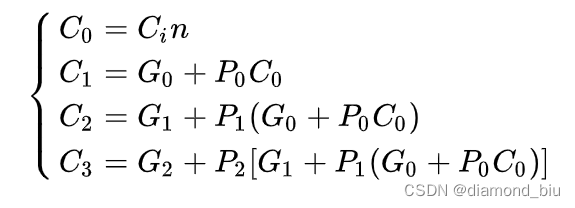

对于4比特超前进位加法器来说,进位输出如下:

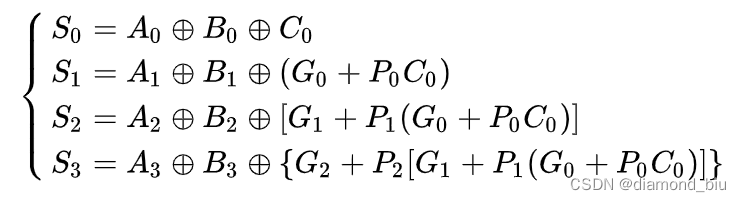

Si=Ai^Bi^(CI)i,对应的(CI)i=(CO)i-1,即Si=Ai^Bi^(CO)i-1。通过前面的推导已经得出了,可得:

- 要点1:需要明确4bit超前进位加法器的原理与推导过程,上一位运算的输出CO是下一位运算的输入CI,

COi=(Ai&Bi)|(CIi&(Ai|Bi))。 - 要点2:仿真自测时定义了一个8bit数num每个时钟周期累加1,将低4比特和高4比特赋值给A和B,需要注意的是给num赋初值!!!要不然仿真波形一片红!!!

`timescale 1ns/1nsmodule lca_4(input [3:0] A_in ,input [3:0] B_in ,input C_1 ,output wire CO ,output wire [3:0] S

);

wire[3:0] g,p,c;

assign p=A_in|B_in;

assign g=A_in&B_in;

assign c[0]=g[0]|(p[0]&C_1);

assign c[1]=g[1]|(p[1]&(g[0]|(p[0]&C_1)));

assign c[2]=g[2]|(p[2]&(g[1]|(p[1]&(g[0]|(p[0]&C_1)))));

assign c[3]=g[3]|(p[3]&(g[2]|(p[2]&(g[1]|(p[1]&(g[0]|(p[0]&C_1)))))));

assign CO=c[3];assign S=A_in^B_in^{c[2:0],C_1};

endmodule

测试代码:

`timescale 1ns/1ns

module testbench();

reg[3:0] A_in,B_in;

reg C_1;

wire CO;

wire[3:0] S;

reg[7:0] num;lca_4 U1(.A_in(A_in),.B_in(B_in),.C_1(C_1),.CO(CO),.S(S));

initial beginC_1=0;num=0;

end

always #10 begin num=num+1;A_in<=num[3:0];B_in<=num[7:4];

end

endmodule

VL13 优先编码器电路①

要点1:题目给的是I1-I9,注意顺序。

要点2:case、casez和casex三者都是可以综合的。case进行全等匹配,casez忽略?或z对应的位进行匹配,casex忽略x、?或z对应的位进行匹配。

`timescale 1ns/1ns

module encoder_0(input [8:0] I_n,output reg [3:0] Y_n

);

always@(I_n)begincasez(I_n)9'b111111111:Y_n<=4'b1111;9'b0????????:Y_n<=4'b0110;9'b10???????:Y_n<=4'b0111;9'b110??????:Y_n<=4'b1000;9'b1110?????:Y_n<=4'b1001;9'b11110????:Y_n<=4'b1010;9'b111110???:Y_n<=4'b1011;9'b1111110??:Y_n<=4'b1100;9'b11111110?:Y_n<=4'b1101;9'b111111110:Y_n<=4'b1110;endcase

end

endmodule

要点3:《CPU设计实战》这本书中提到在CPU设计中必须遵守的硬性规定是代码中禁止出现casez、casex,因此可以采用如下写法,看Y9~Y0中出现的第一个0的位置。

`timescale 1ns/1ns

module encoder_0(input [8:0] I_n,output [3:0] Y_n

);

assign Y_n=(~I_n[8])?4'b0110:(~I_n[7])?4'b0111:(~I_n[6])?4'b1000:(~I_n[5])?4'b1001:(~I_n[4])?4'b1010:(~I_n[3])?4'b1011:(~I_n[2])?4'b1100:(~I_n[1])?4'b1101:(~I_n[0])?4'b1110:4'b1111;

endmodule

VL14 用优先编码器①实现键盘编码电路

题目描述的不是很清楚。

要点1:GS:按下为1,不按为0,需要注意的是最后assign GS=(S_n==10'b1111111111)?1'b0:1'b1;并不能只判断S_n[0]==1,因为其他按键(9~1)被按下时S_n[0]也为0;

要点2:最终的输出需要对译码结果取反assign L=~Y_n;

`timescale 1ns/1nsmodule encoder_0(input [8:0] I_n ,output [3:0] Y_n

);

assign Y_n=(~I_n[8])?4'b0110:(~I_n[7])?4'b0111:(~I_n[6])?4'b1000:(~I_n[5])?4'b1001:(~I_n[4])?4'b1010:(~I_n[3])?4'b1011:(~I_n[2])?4'b1100:(~I_n[1])?4'b1101:(~I_n[0])?4'b1110:4'b1111;

endmodulemodule key_encoder(input [9:0] S_n , output wire[3:0] L ,output wire GS

);wire[3:0] Y_n;encoder_0 U1(.I_n(S_n[9:1]),.Y_n(Y_n));//GS:按下为1,不按为0assign GS=(S_n==10'b1111111111)?1'b0:1'b1;assign L=~Y_n;

endmodule

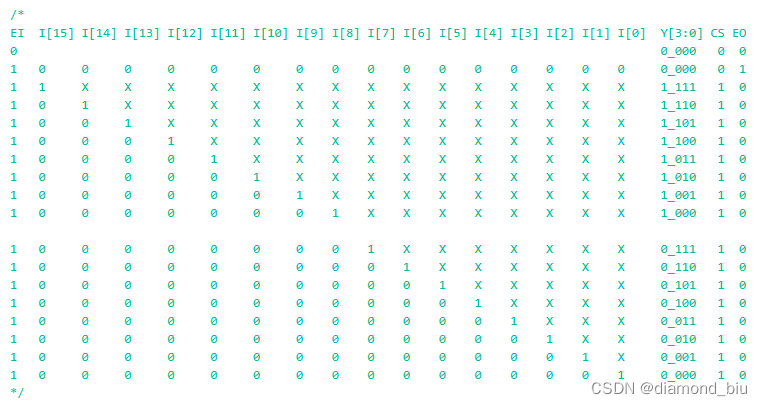

VL16 使用8线-3线优先编码器Ⅰ实现16线-4线优先编码器

要点1:编码的结果为000时,可能有三种情况,(1)译码器没有使能,不工作,此时GS=0;EO=0;(2)译码器再工作,但无输入,GS=0;EO=1;;(3)译码器在工作,且有输入,输入为0000_0001,GS=1;EO=0;;

要点2:参考SNx4HC148 8-Line to 3-Line Priority Encoders理解如何使用两个8-3译码器得到一个16-4译码器。实际就是将两个8-3译码器的EO与EI连接,输出取或运算作为译码结果的低3位I[2:0],高位译码器的GS作为译码结果I[3](1表示高位译码器在译码15~8,0表示在译码0~7)。最终的GS为GS1|GS2。

真值表如下:

`timescale 1ns/1ns

module encoder_83(input [7:0] I ,input EI ,output wire [2:0] Y ,output wire GS ,output wire EO

);

assign {Y,GS,EO}=(~EI)?5'b00000:I[7]?5'b11110:I[6]?5'b11010:I[5]?5'b10110:I[4]?5'b10010:I[3]?5'b01110:I[2]?5'b01010:I[1]?5'b00110:I[0]?5'b00010:5'b00001;

endmodulemodule encoder_164(input [15:0] A ,input EI ,output wire [3:0] L ,output wire GS ,output wire EO

);

wire GS1,GS2,EO1;

wire[2:0] L1,L2;

encoder_83 U1(.I(A[15:8]),.EI(EI),.Y(L1[2:0]),.GS(GS1),.EO(EO1));

encoder_83 U2(.I(A[7:0]),.EI(EO1),.Y(L2[2:0]),.GS(GS2),.EO(EO));

assign L={GS1,L1|L2};

assign GS=GS1|GS2;

endmodule

Verilog进阶挑战

Verilog企业真题

常见数字IC手撕代码

数字IC笔试面试题汇总

- 异步fifo。格雷码的镜像对称。格雷码和二进制的互相转换。

- 同步fifo。

- 除法器。

- Wallace乘法器。

- Booth乘法器。

- Booth+Wallace乘法器。

- 超前进位加法器。

- 边沿检测,输入消抖,毛刺消除。

- 异步复位同步释放。

- 三种计数器。二进制,移位,移位+反向。

- 无毛刺时钟切换。

- 串行-并行CRC。(ARM)。

- 线性反馈移位寄存器。

- 握手实现CDC。

- AXI-S接口,2T一次传输,1T一次传输,1T一次传输还要寄存器寄存。(Nvidia考题)Xilinx有例程。

- 其他简单功能的HDL实现以及状态转换图。(序列检测 ,回文序列检测(NVIDIA),奇、偶、半分频,小数分频,自动售货机)。

相关文章:

暑期实习准备——Verilog手撕代码(持续更新中。。。

暑期实习准备——手撕代码牛客刷题笔记Verilog快速入门VL4 移位运算与乘法VL5 位拆分与运算VL6 多功能数据处理器VL8 使用generate…for语句简化代码VL9 使用子模块实现三输入数的大小比较VL11 4位数值比较器电路VL12 4bit超前进位加法器电路VL13 优先编码器电路①VL14 用优先编…...

Qt音视频开发19-vlc内核各种事件通知

一、前言 对于使用第三方的sdk库做开发,除了基本的操作函数接口外,还希望通过事件机制拿到消息通知,比如当前播放进度、音量值变化、静音变化、文件长度、播放结束等,有了这些才是完整的播放功能,在vlc中要拿到各种事…...

Linux基础命令-nice调整进程的优先级

文章目录 Nice 命令介绍 语法格式 常用参数 参考实例 1 调整bash的优先级为-10 2 调整脚本的优先级为6 3 调整指令的优先级 4 默认使用nice命令调整优先级 命令总结 Nice 命令介绍 nice命令的主要功能是用于调整进程的优先级,合理分配系统资源。Linux系…...

函数)

解析C语言strcmp()函数

函数名: strcmp 头文件: <string.h> 函数原型: int strcmp(const char *str1,const char *str2); 功 能: 比较两个字符串的大小,区分大小写 参 数: str1和str2为要比较的字符串 返回值: str1 > str2 , 返回 1&…...

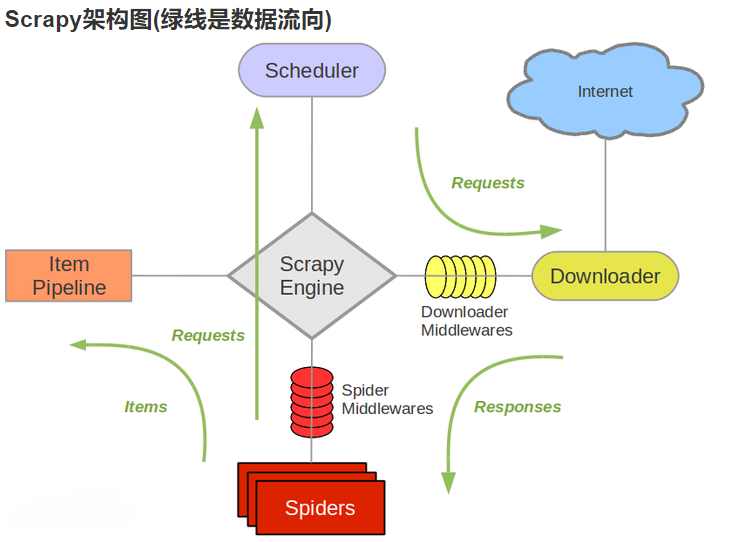

初识scrapy

认识scrapyscrapy是一个为了爬取网站数据,提取结构性数据而编写的应用框架,我们只需实现少量的代码,就能实现数据的快速抓取scrapy使用了Twisted异步网络架构,可以加快下载速度 pip install twisted安装:pip install s…...

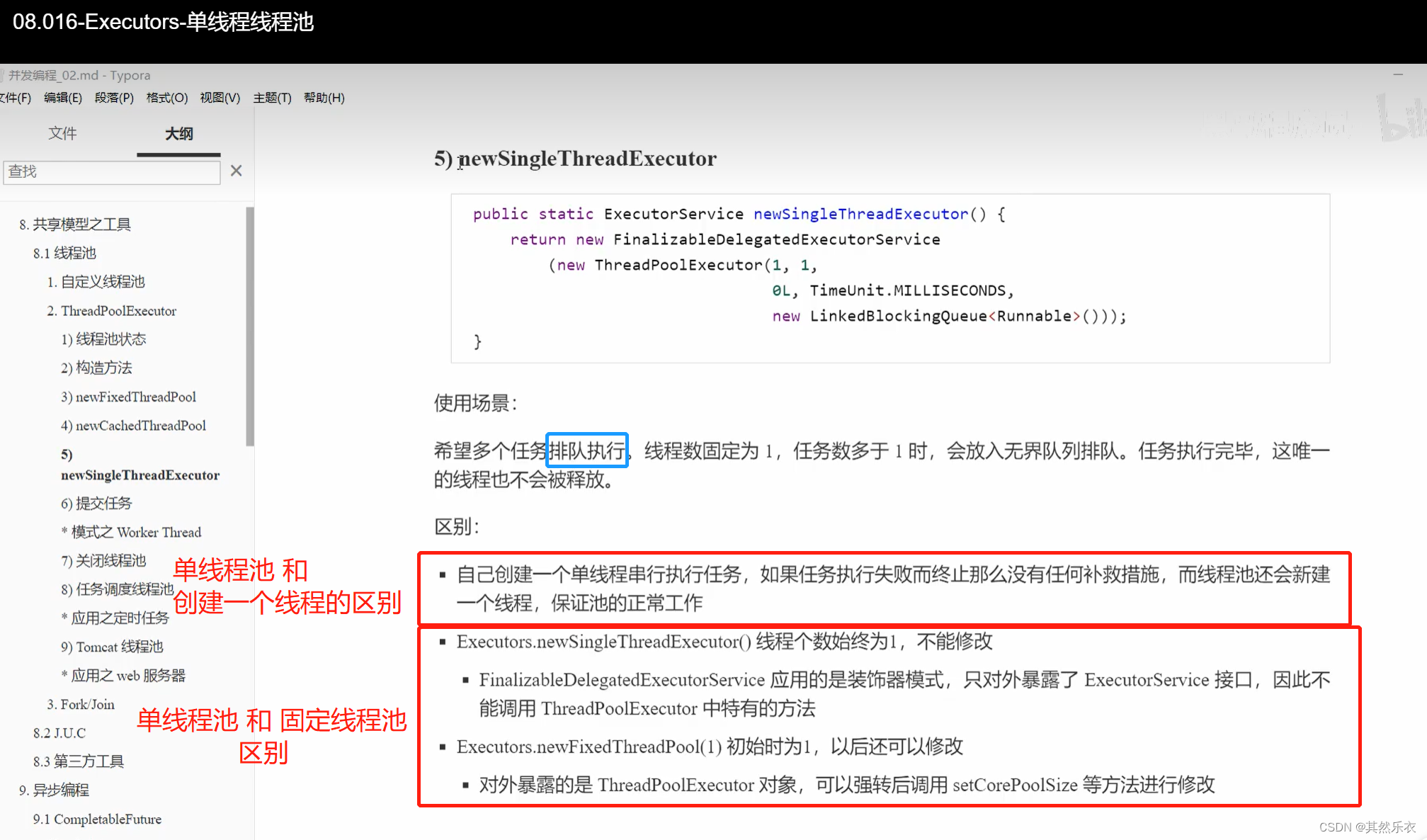

(JUC)核心线程 和 救急线程的区别;Executors-固定大小线程池单线程线程池

核心线程 和 救急线程的区别 救急线程是有个生存时间的,它执行完任务了,过了一段时间,没有新任务了,救急线程就会销毁掉,变成结束的状态 核心线程没有生存时间,它执行完任务后,它仍然会被保存…...

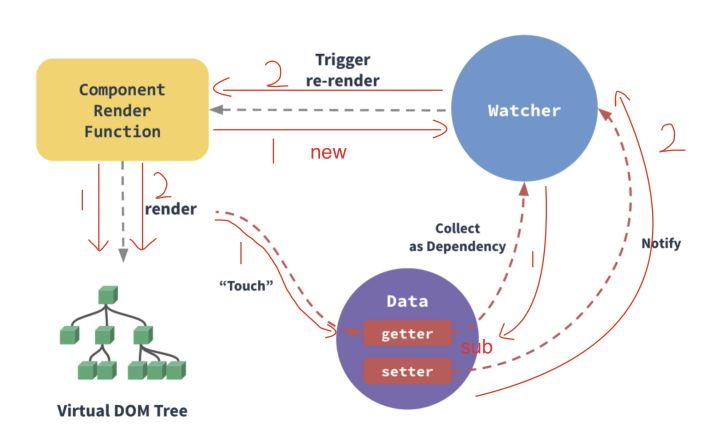

vue2的动画和过渡效果

文章目录过渡 & 动画Transition 组件基于 CSS 的过渡效果CSS 过渡类名 class为过渡效果命名CSS 过渡 transition实例1:实例2:CSS 动画自定义过渡的类名同时使用 transition 和 animation深层级过渡与显式过渡时长性能考量JavaScript 动画可复用过渡效…...

正数负数的取反运算推导过程

取反题目题目:数据常用位十进制数据举例 我们计算a 60的取反运算c~a 求c 引用的知识点知识点: 正数的反码 补码 都一样。 0的补码反码都一样 负数的反码,最高是标记符号位,其他位置1变0 1变0 负数的补码 反码1 步骤斜体样式本篇我们全用8位二…...

C语言 条件编译

目录 1. #if #elif #else #endif 2. #ifdef #else #endif 3. #ifndef #else #endif 4. 三者区别 根据不同情况编译不同代码、产生不同目标文件的机制,称为条件编译。 条件编译是预处理程序的功能,不是编译器的功能。 1. #if #elif #else #endif …...

Linux: ARM GIC只中断CPU 0问题分析

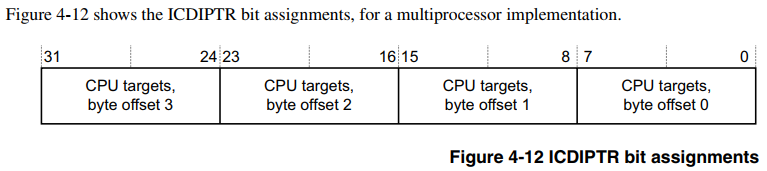

文章目录1. 前言2. 分析背景3. 问题4. 分析4.1 ARM GIC 中断芯片简介4.1.1 中断类型和分布4.1.2 拓扑结构4.2 问题根因4.2.1 设置GIC SPI 中断CPU亲和性4.2.2 GIC初始化:缺省的CPU亲和性4.2.2.1 boot CPU亲和性初始化流程4.2.2.1 其它非 boot CPU亲和性初始化流程5.…...

测试软件5

一 css基础 css定义:可以设置网页中的样式,外观,美化 css中文名字:级联样式表,层叠样式表,样式表 二 css基础语法 1.style标签写在title标签后面 2.选择器{属性名1:属性值1;属性名…...

前端JS内存管理

JS内存管理 内存原理: 任何变成语言在执行的时候都需要操作系统来分配内存,只是有些语言需要手动管理分配的内存有些语言有专门来管理内存的方式 如 JVM 了解以上的概念之后,我们再来了解一下大致的内存周期 分配需要的内存使用内存在不使用…...

第七章.集成学习(Ensemble Learning)—袋装(bagging),随机森林(Random Forest)

第七章.集成学习 (Ensemble Learning) 7.1 集成学习—袋装(bagging),随机森林(Random Forest) 集成学习就是组合多个学习器,最后得到一个更好的学习器。 1.常见的4种集成学习算法 个体学习器之间不存在强依赖关系,袋装(bagging)…...

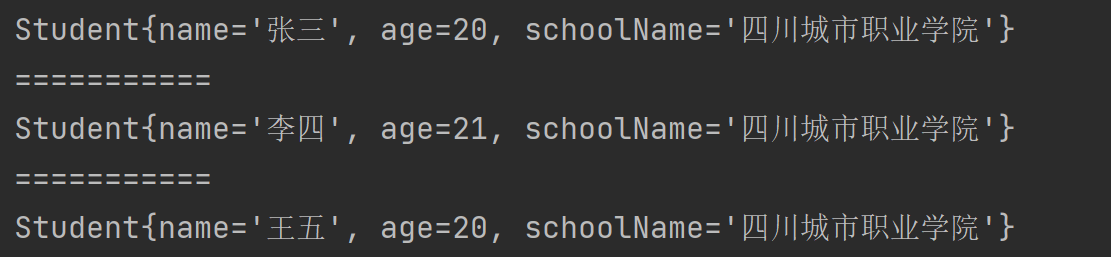

Java_面向对象

Java_面向对象 1.面向对象概述 面向对象是一种符合人类思想习惯的编程思想。显示生活中存在各种形态的不同事物,这些食物存在着各种各样的联系。在程序中使用对象来映射现实中的事物,使用对象的关系来描述事物之间的关系,这种思想就是面…...

【IoT】智能烟雾报警器

设计简介 硬件设计由AT89C51单片机、DS18B20温度传感器、4位共阳数码管、电源模块、报警模块、按键模块、MQ-2烟雾检测模块和ADC0832模数转换模块组成。 烟雾传感器MQ-2检测空气中的烟雾气体,通过ADC0832进行数据转换,经过单片机的运算处理后在数码管上…...

)

Python实现定时执行脚本(5)

前言 本文是该专栏的第17篇,后面会持续分享python的各种干货知识,值得关注。 笔者在前面有详细介绍过几种使用python实现定时执行任务的方法,可以说都是简单易上手的那种。而本文,再来详细介绍另外一种定时方法,那就是利用任务框架APScheduler(advanceded python schedu…...

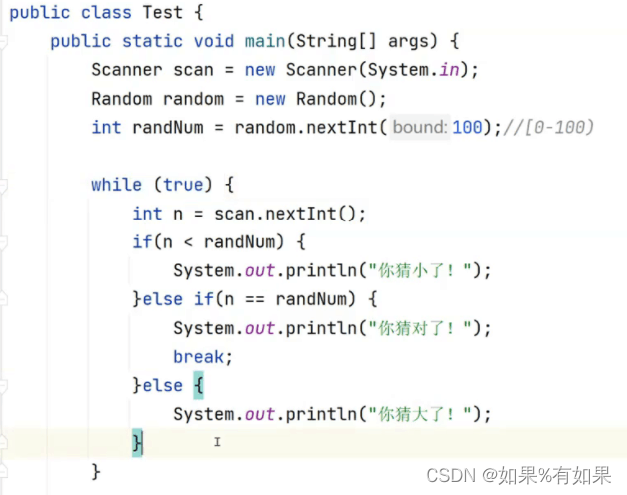

JavaSe第4次笔记

1.转义字符和编程语言无关。 2.斜杠(\)需要转义,反斜杠(/)不需要转义。 3.不能做switch的参数的数据类型:long float double boolean( String可以)。 4.输入的写法:Scanner(回车自动带头文件(import java.util.Scanner;)) Scanner scan …...

epoll机制

预备知识 文件描述符file descriptor 文件描述符是Linux系统中对文件、套接字等I/O资源的抽象,每个打开的文件或套接字都有一个唯一的文件描述符。应用程序可以使用文件描述符来读写文件或进行网络通信。 epoll允许程序监控多个文件描述符,以便在这些…...

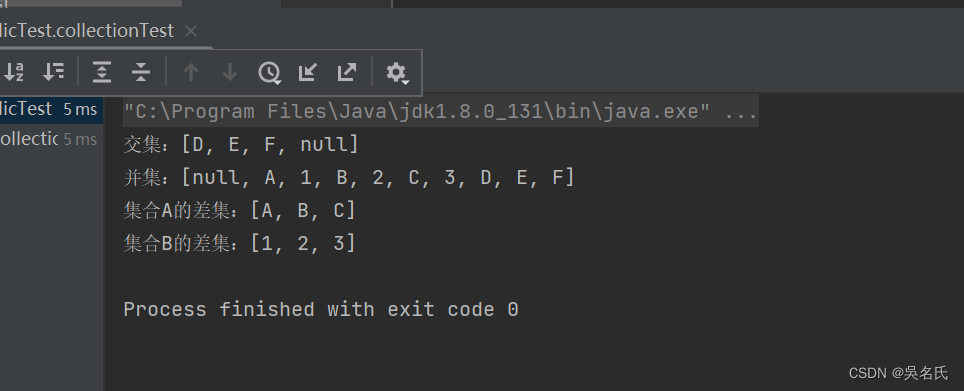

Java使用不同方式获取两个集合List的交集、补集、并集(相加)、差集(相减)

1 明确概念首先知道几个单词的意思:并集 union交集 intersection补集 complement析取 disjunction减去 subtract1.1 并集对于两个给定集合A、B,由两个集合所有元素构成的集合,叫做A和B的并集。记作:AUB 读作“A并B”例&#…...

【Android笔记80】Android之Retrofit适配器和文件上传下载

这篇文章,主要介绍Android之Retrofit适配器和文件上传下载。 目录 一、Retrofit适配器 1.1、Retrofit适配器 (1)引入RxJava依赖 (2)定义接口...

如何用QtScrcpy实现跨平台Android设备高效投屏与控制

如何用QtScrcpy实现跨平台Android设备高效投屏与控制 【免费下载链接】QtScrcpy Android实时投屏软件,此应用程序提供USB(或通过TCP/IP)连接的Android设备的显示和控制。它不需要任何root访问权限 项目地址: https://gitcode.com/barry-ran/QtScrcpy 在数字化…...

)

ROS Noetic下用Python脚本在Gazebo里动态生成障碍物(附完整代码和常见报错解决)

ROS Noetic下Python脚本动态生成Gazebo障碍物的工程实践 在机器人仿真测试中,动态生成环境障碍物是验证导航算法鲁棒性的关键手段。传统手动拖拽方式效率低下且难以复现特定测试场景,而通过编程控制Gazebo仿真环境则能实现测试流程的自动化与标准化。本文…...

3个关键步骤:如何用Bilibili-Evolved打造60fps流畅播放体验

3个关键步骤:如何用Bilibili-Evolved打造60fps流畅播放体验 【免费下载链接】Bilibili-Evolved 强大的哔哩哔哩增强脚本 项目地址: https://gitcode.com/gh_mirrors/bi/Bilibili-Evolved Bilibili-Evolved作为一款强大的哔哩哔哩增强脚本,为追求极…...

网络安全零基础入门:借助快马AI生成你的第一个防注入登录页面

作为一名刚接触网络安全的小白,我最近尝试用InsCode(快马)平台做了一个防注入的登录页面。整个过程比想象中简单很多,特别适合零基础入门。这里分享我的实践心得,希望能帮到同样想学习网络安全的朋友。 为什么选择登录页面作为切入点 登录功…...

阿里开源Z-Image镜像体验:ComfyUI可视化生成汉服美女实战

阿里开源Z-Image镜像体验:ComfyUI可视化生成汉服美女实战 1. 开篇:当汉服遇见AI绘画 想象一下,你只需要输入"一位穿着汉服的中国女性站在樱花树下",AI就能在几秒钟内生成一张细节精致的写实风格图像。这不再是科幻场景…...

Qt, C++数据类型扩展问题

Qt项目中ObjectDic类的类型扩展与代码优化 前言 在Qt项目开发中,我们经常会遇到需要处理不同类型数据的情况,尤其是当涉及到负数时,类型的选择就显得尤为重要。本文将详细介绍如何在Qt项目中扩展ObjectDic类的类型支持,从无符号整…...

比Jenkins轻量10倍!用Gitea Actions搭建内网自动化部署的完整踩坑记录

企业级内网CI/CD革命:Gitea Actions轻量化实战指南 在当今快节奏的软件开发环境中,持续集成与持续部署(CI/CD)已成为企业提升交付效率的关键。然而,传统解决方案如Jenkins往往伴随着沉重的资源消耗和复杂的配置流程,让许多中小团队…...

)

保姆级教程:将你的YOLOv8模型用Gradio部署到公网,并设置密码保护(避免临时链接失效)

从原型到生产:YOLOv8模型的安全部署与Gradio高级应用指南 当你的YOLOv8模型在本地运行良好,接下来最自然的想法就是把它分享给团队成员、客户或者进行小范围演示。Gradio提供的shareTrue参数看似简单,但背后隐藏着许多值得深入探讨的技术细节…...

MedGemma 1.5新手必看:从安装到问诊,完整使用流程详解

MedGemma 1.5新手必看:从安装到问诊,完整使用流程详解 你是否曾面对一份复杂的化验单,需要快速理解其临床意义?是否在深夜值班时,想快速确认某个药物的相互作用?或者,作为一名医学生࿰…...

效率倍增:基于快马平台集成最新openclaw构建自动化采集工具

最近在做一个数据采集项目时,发现手动写爬虫实在太费时间了。每次都要重复处理请求头、代理设置、数据清洗这些基础工作,效率特别低。后来发现了openclaw这个工具包的新版本,正好结合InsCode(快马)平台快速搭建了一个自动化采集工具ÿ…...