17 ABCD数码管显示与动态扫描原理

1. 驱动八位数码管循环点亮

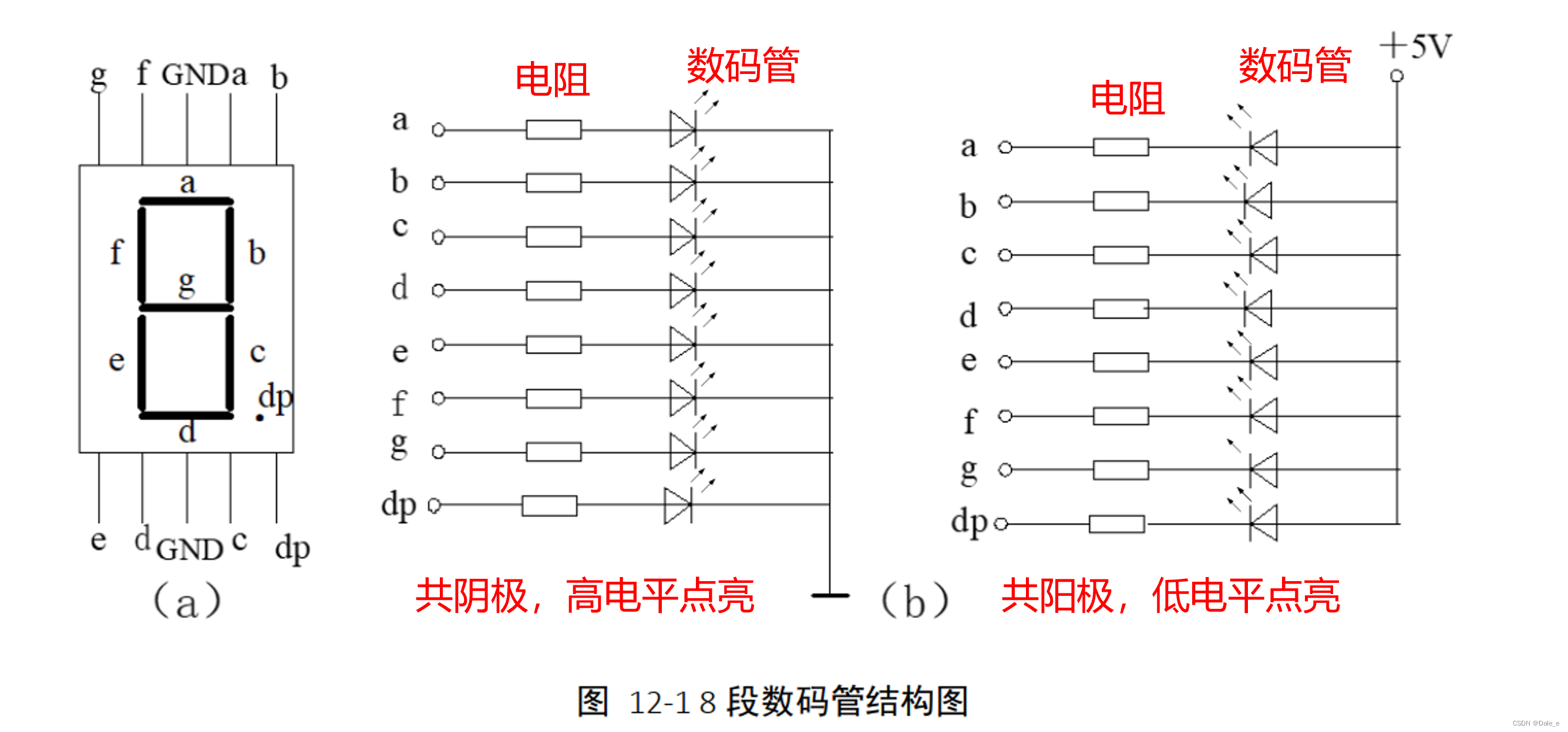

1.1 数码管结构图

数码管有两种结构,共阴极和共阳极,ACX720板上的是共阳极数码管,低电平点亮。

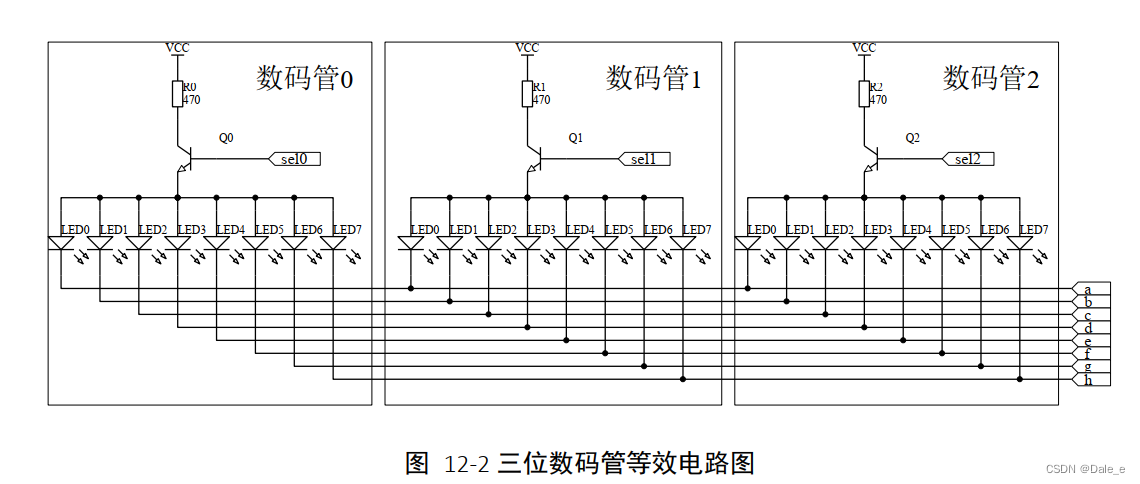

1.2 三位数码管等效电路图

为了节约I/O接口,各个数码管的各段发光管被连在一起,通过sel端口选择要发光的数码管。

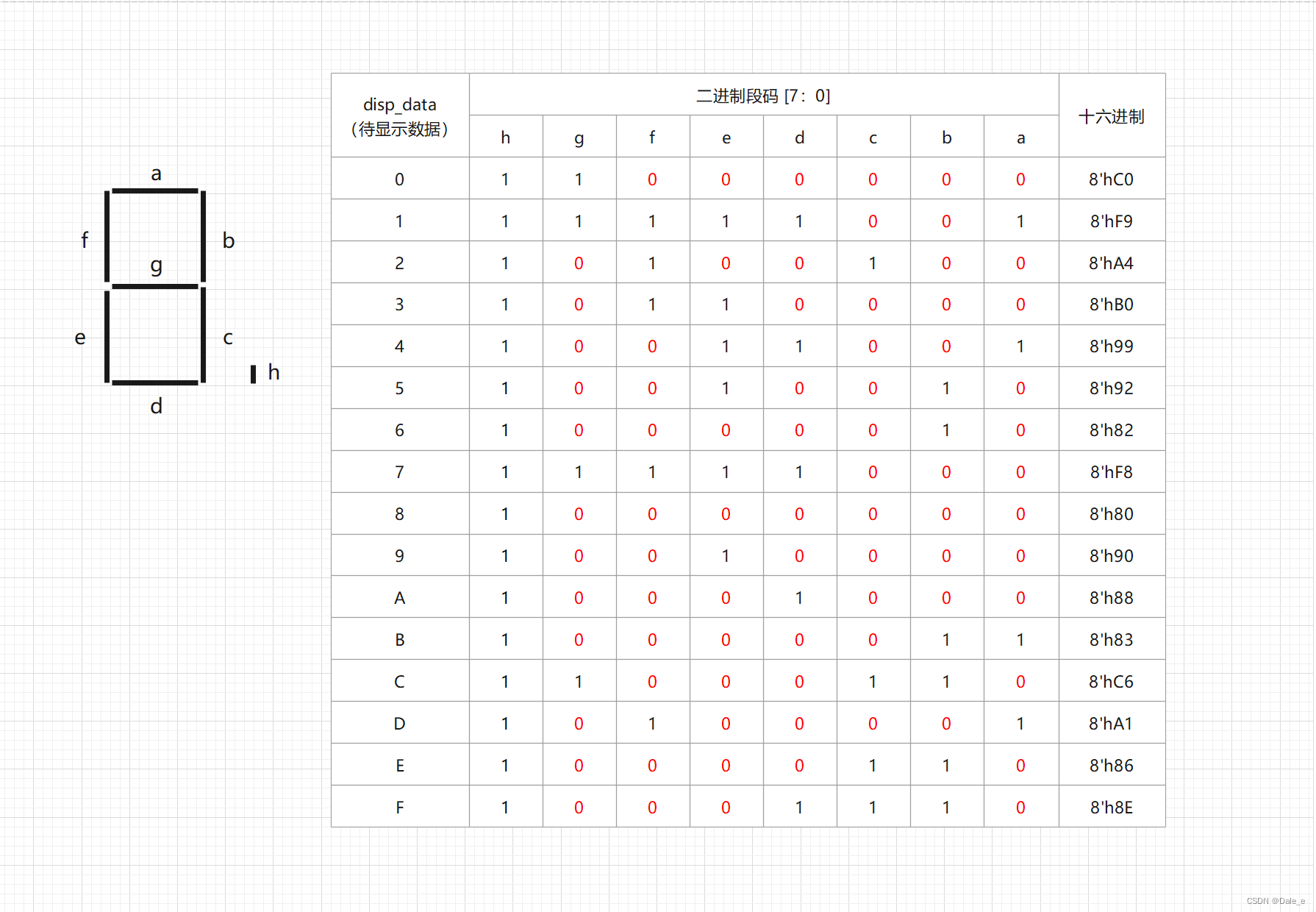

1.3 单个数码管发光的LUT(look up table)

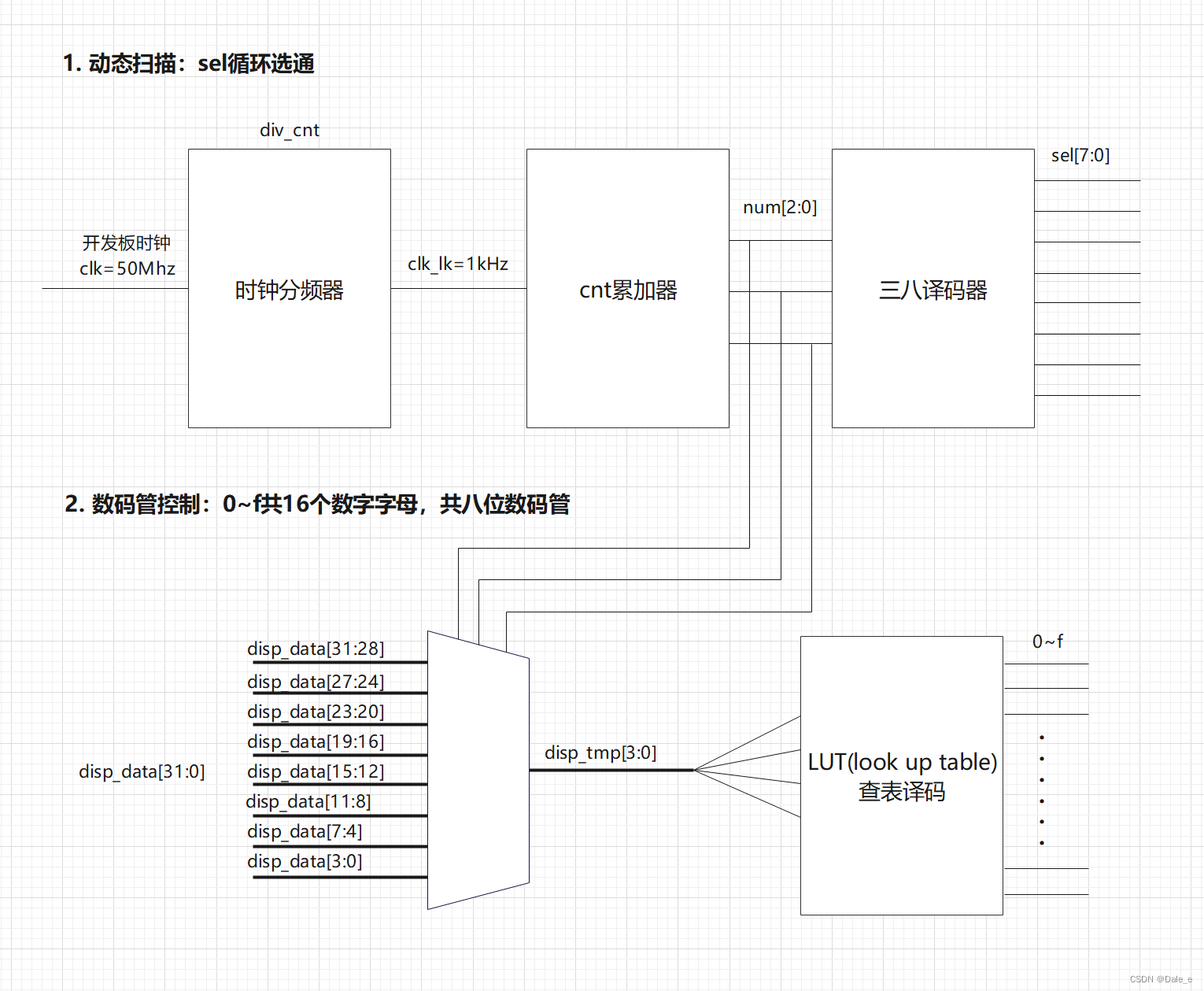

2. 数码管显示与动态扫描逻辑建模

3. 数码管显示与动态扫描的Verilog实现

3.1 不完善的设计代码版本

1. 设计代码

该设计代码有两个地方需要修改

- 分频时钟的使用不合理,在fpga设计中,一定要避免使用计数器(寄存器)分频得到的信号来作为时钟再去驱动其他的寄存器;推荐使用使能时钟,不要使用门控时钟。

- 在fpga设计中,推荐多使用时序逻辑而非组合逻辑。对于case语句,我们要将其放在always语句块中,在每个时钟沿下发生数据的变换。

module hex8(clk,rstn,disp_data,sel,led

);parameter times = 25000; // 0.5msinput clk;input rstn;input [31:0]disp_data;output reg [7:0] sel;output reg [7:0] led;reg [15:0]div_cnt;always@(posedge clk or negedge rstn)if(!rstn)div_cnt <= 0;else if(div_cnt >= times - 1)div_cnt <= 0;elsediv_cnt <= div_cnt + 1'd1;//分频时钟//用一个寄存器来模拟一个时钟去驱动其他寄存器会存在许多问题reg clk_lk;always@(posedge clk or negedge rstn)if(!rstn)clk_lk <= 0;else if(div_cnt == times - 1)clk_lk <= ~clk_lk;//cnt累加器reg [2:0] num_cnt; always@(posedge clk_lk or negedge rstn)if(!rstn)num_cnt <= 0;elsenum_cnt <= num_cnt + 1'd1;//三八译码器 always@(posedge clk_lk or negedge rstn)if(!rstn)sel <= 0;else case(num_cnt)0:sel = 8'b0000_0001;1:sel = 8'b0000_0010;2:sel = 8'b0000_0100;3:sel = 8'b0000_1000;4:sel = 8'b0001_0000;5:sel = 8'b0010_0000;6:sel = 8'b0100_0000;7:sel = 8'b1000_0000;endcase//八选一多路器reg [3:0]disp_tmp;always@(*)case(num_cnt)0:disp_tmp = disp_data[3:0];1:disp_tmp = disp_data[7:4];2:disp_tmp = disp_data[11:8];3:disp_tmp = disp_data[15:12];4:disp_tmp = disp_data[19:16];5:disp_tmp = disp_data[23:20];6:disp_tmp = disp_data[27:24];7:disp_tmp = disp_data[31:28];endcase//四十六译码器 always@(*)case(disp_tmp)0:led = 8'hc0;1:led = 8'hf9;2:led = 8'ha4;3:led = 8'hb0;4:led = 8'h99;5:led = 8'h92;6:led = 8'h82;7:led = 8'hf8;8:led = 8'h80;9:led = 8'h90;4'ha:led = 8'h88;4'hb:led = 8'h83;4'hc:led = 8'hc6;4'hd:led = 8'ha1;4'he:led = 8'h86;4'hf:led = 8'h8e; default:led = 8'hc0;endcaseendmodule

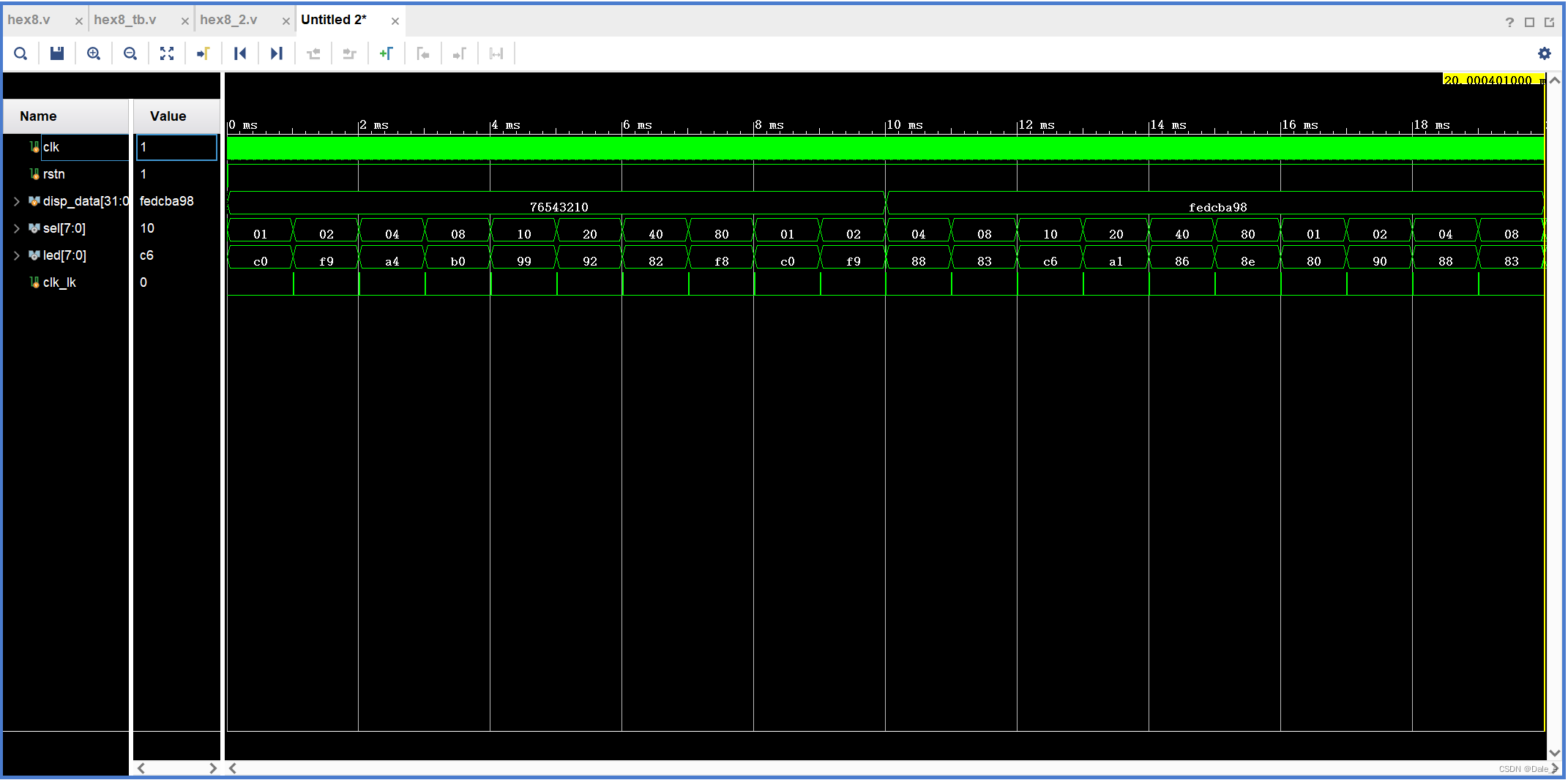

2. 仿真波形

3.1 修改分频时钟和case语句后的设计代码

1. 设计代码

module hex8_2(clk,rstn,disp_data,sel,led

);parameter times = 50000; // 1msinput clk;input rstn;input [31:0]disp_data;output reg [7:0] sel;output reg [7:0] led;reg [15:0]div_cnt;always@(posedge clk or negedge rstn)if(!rstn)div_cnt <= 0;else if(div_cnt >= times - 1)div_cnt <= 0;elsediv_cnt <= div_cnt + 1'd1;//使能时钟 reg clk_lk;always@(posedge clk or negedge rstn)if(!rstn)clk_lk <= 0;else if(div_cnt == times - 1)clk_lk <= 1'd1;elseclk_lk <= 0;//cnt累加器reg [2:0] num_cnt; always@(posedge clk_lk or negedge rstn)if(!rstn)num_cnt <= 0;else if(clk_lk == 1)num_cnt <= num_cnt + 1'd1;//三八译码器 always@(posedge clk or negedge rstn)if(!rstn)sel <= 0;else case(num_cnt)0:sel = 8'b0000_0001;1:sel = 8'b0000_0010;2:sel = 8'b0000_0100;3:sel = 8'b0000_1000;4:sel = 8'b0001_0000;5:sel = 8'b0010_0000;6:sel = 8'b0100_0000;7:sel = 8'b1000_0000;endcase//八选一多路器reg [3:0]disp_tmp;always@(posedge clk)case(num_cnt)0:disp_tmp = disp_data[3:0];1:disp_tmp = disp_data[7:4];2:disp_tmp = disp_data[11:8];3:disp_tmp = disp_data[15:12];4:disp_tmp = disp_data[19:16];5:disp_tmp = disp_data[23:20];6:disp_tmp = disp_data[27:24];7:disp_tmp = disp_data[31:28];endcase//四十六译码器 always@(posedge clk)case(disp_tmp)0:led = 8'hc0;1:led = 8'hf9;2:led = 8'ha4;3:led = 8'hb0;4:led = 8'h99;5:led = 8'h92;6:led = 8'h82;7:led = 8'hf8;8:led = 8'h80;9:led = 8'h90;4'ha:led = 8'h88;4'hb:led = 8'h83;4'hc:led = 8'hc6;4'hd:led = 8'ha1;4'he:led = 8'h86;4'hf:led = 8'h8e; default:led = 8'hc0;endcaseendmodule2.仿真代码

module hex8_2(clk,rstn,disp_data,sel,led

);parameter times = 50000; // 1msinput clk;input rstn;input [31:0]disp_data;output reg [7:0] sel;output reg [7:0] led;reg [15:0]div_cnt;always@(posedge clk or negedge rstn)if(!rstn)div_cnt <= 0;else if(div_cnt >= times - 1)div_cnt <= 0;elsediv_cnt <= div_cnt + 1'd1;//使能时钟 reg clk_lk;always@(posedge clk or negedge rstn)if(!rstn)clk_lk <= 0;else if(div_cnt == times - 1)clk_lk <= 1'd1;elseclk_lk <= 0;//cnt累加器reg [2:0] num_cnt; always@(posedge clk_lk or negedge rstn)if(!rstn)num_cnt <= 0;else if(clk_lk == 1)num_cnt <= num_cnt + 1'd1;//三八译码器 always@(posedge clk or negedge rstn)if(!rstn)sel <= 0;else case(num_cnt)0:sel = 8'b0000_0001;1:sel = 8'b0000_0010;2:sel = 8'b0000_0100;3:sel = 8'b0000_1000;4:sel = 8'b0001_0000;5:sel = 8'b0010_0000;6:sel = 8'b0100_0000;7:sel = 8'b1000_0000;endcase//八选一多路器reg [3:0]disp_tmp;always@(posedge clk)case(num_cnt)0:disp_tmp = disp_data[3:0];1:disp_tmp = disp_data[7:4];2:disp_tmp = disp_data[11:8];3:disp_tmp = disp_data[15:12];4:disp_tmp = disp_data[19:16];5:disp_tmp = disp_data[23:20];6:disp_tmp = disp_data[27:24];7:disp_tmp = disp_data[31:28];endcase//四十六译码器 always@(posedge clk)case(disp_tmp)0:led = 8'hc0;1:led = 8'hf9;2:led = 8'ha4;3:led = 8'hb0;4:led = 8'h99;5:led = 8'h92;6:led = 8'h82;7:led = 8'hf8;8:led = 8'h80;9:led = 8'h90;4'ha:led = 8'h88;4'hb:led = 8'h83;4'hc:led = 8'hc6;4'hd:led = 8'ha1;4'he:led = 8'h86;4'hf:led = 8'h8e; default:led = 8'hc0;endcaseendmodule3.仿真波形

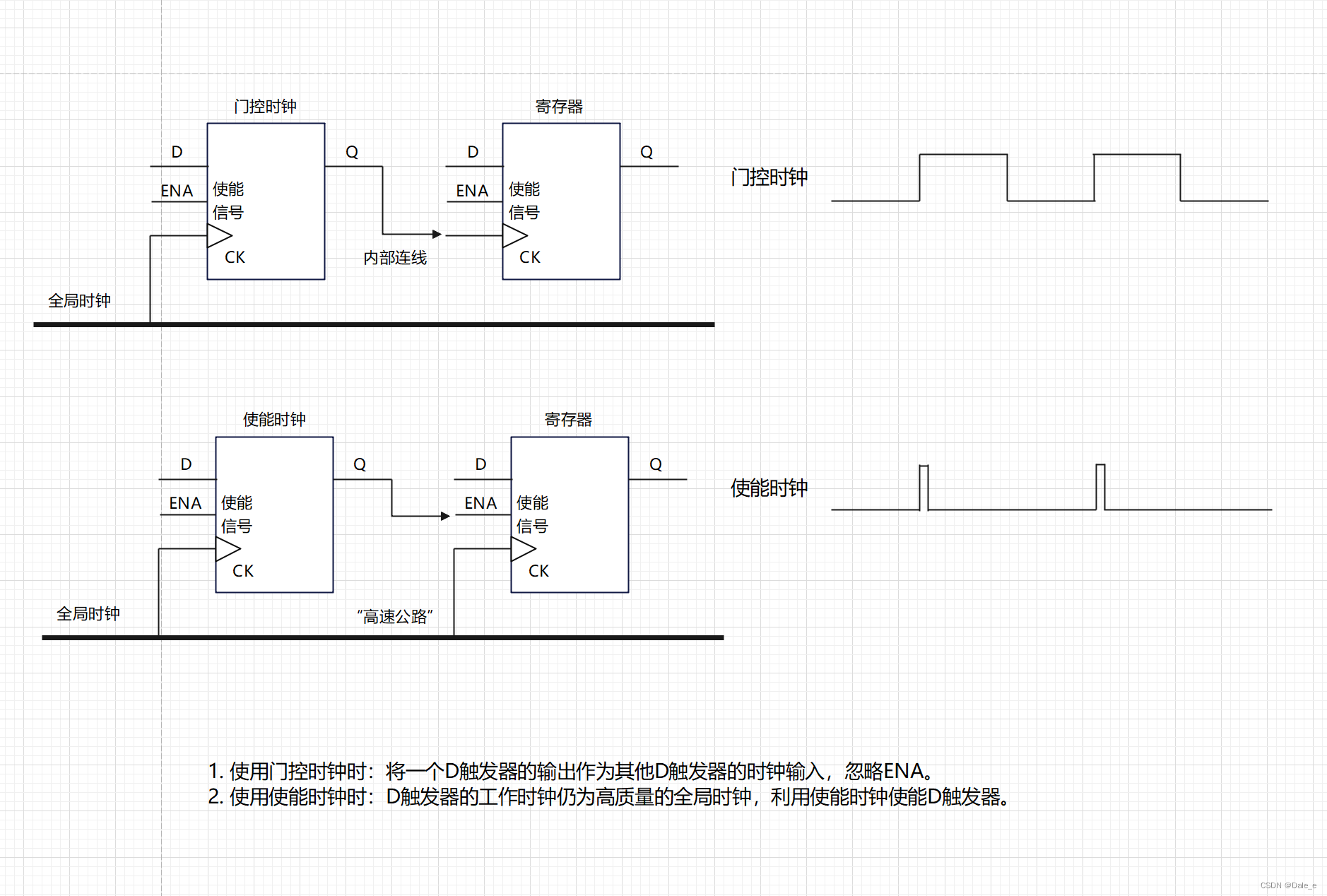

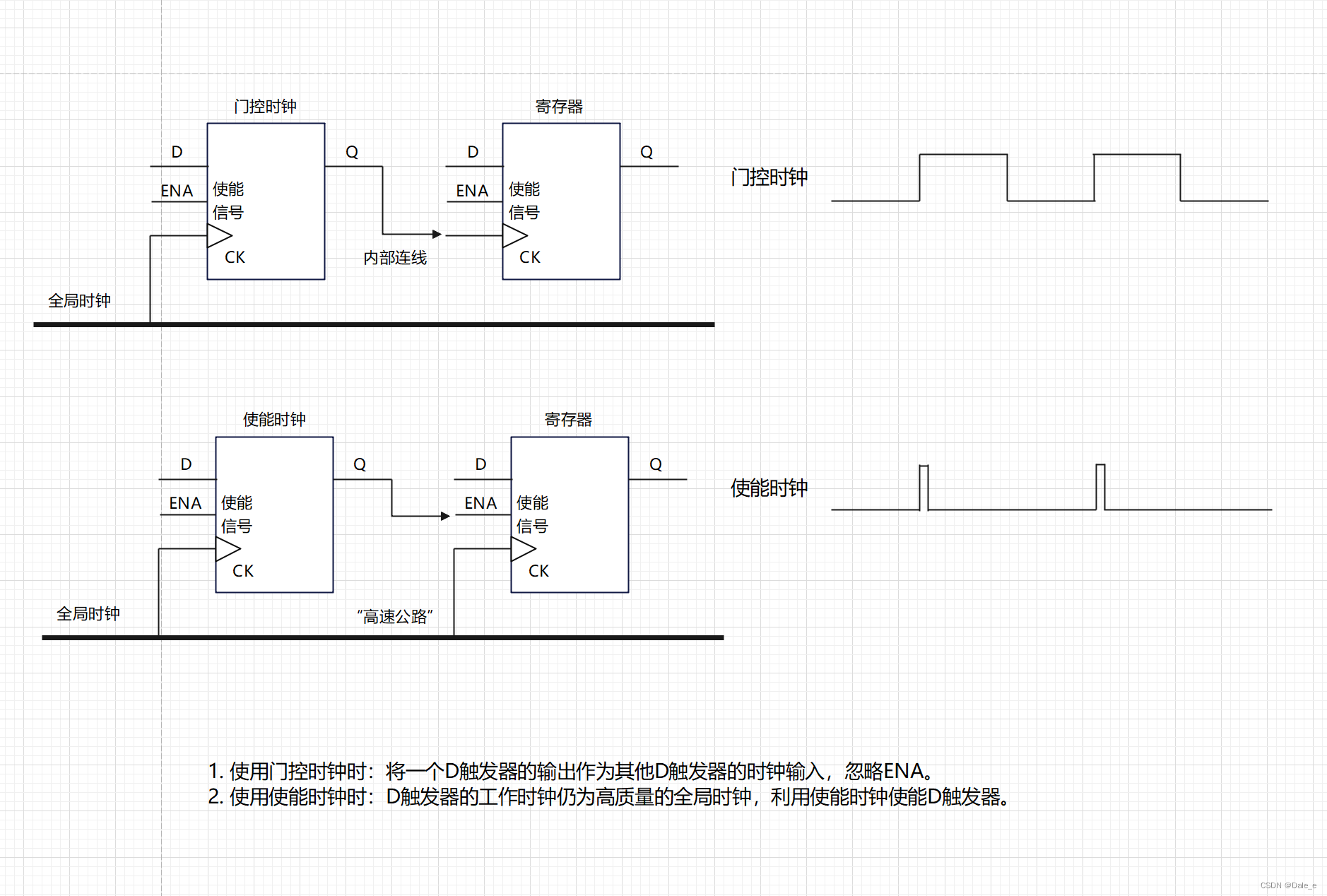

4. 使能时钟与门控时钟的原理和差异

1. 使能时钟和门控时钟

-

使用门控时钟时:将一个D触发器的输出作为其他D触发器的时钟输入,忽略ENA。

-

使用使能时钟时:D触发器的工作时钟仍为高质量的全局时钟,利用使能时钟使能D触发器。

2. 使用全局时钟的原因

- 全局时钟是一条“高速公路”,时钟信号到达各个寄存器的时间受连线距离影响比较小,而用寄存器产生的门控时钟,走的是内部连线,随着距离的延长,延迟增加明显,从而破环寄存器的建立保持时间。

- 使用寄存器传输时钟信号时,随着寄存器一级一级的传递,信号会出现波动,时钟信号的波形会越来越差(毛刺,波动等)

- 全局时钟有专门的晶体管来提高时钟的驱动能力,而寄存器产生的时钟会随着寄存器的传递,驱动能力越来越弱。

相关文章:

17 ABCD数码管显示与动态扫描原理

1. 驱动八位数码管循环点亮 1.1 数码管结构图 数码管有两种结构,共阴极和共阳极,ACX720板上的是共阳极数码管,低电平点亮。 1.2 三位数码管等效电路图 为了节约I/O接口,各个数码管的各段发光管被连在一起,通过sel端…...

【Zigbee课程设计系列文章】Zigbee开发环境搭建

【Zigbee课程设计系列文章】Zigbee开发环境搭建 前言IAR 下载安装Z-Stack协议栈安装 🎊项目专栏:【Zigbee课程设计系列文章】(附详细使用教程完整代码原理图完整课设报告) 前言 👑由于无线传感器网络(也即…...

[Linux开发工具]项目自动化构建工具-make/Makefile

📙 作者简介 :RO-BERRY 📗 学习方向:致力于C、C、数据结构、TCP/IP、数据库等等一系列知识 📒 日后方向 : 偏向于CPP开发以及大数据方向,欢迎各位关注,谢谢各位的支持 目录 1.背景2.依赖关系和依…...

PLC_博图系列☞参数实例

PLC_博图系列☞参数实例 文章目录 PLC_博图系列☞参数实例背景介绍参数实例参数实例的工作原理创建参数实例将实例作为参数传送 关键字: PLC、 西门子、 博图、 Siemens 、 参数实例 背景介绍 这是一篇关于PLC编程的文章,特别是关于西门子的博图软件…...

LLaMA 2 和 QianWen-14B

阿里云通义千问14B模型开源!性能超越Llama2等同等尺寸模型 - 科技新闻 - EDA365电子论坛网 LLaMA 2 的硬件要求: LLaMA 2 系列模型有不同的参数量版本,如7B、13B和70B等。对于不同大小的模型,其硬件需求也有所不同。以下是一些硬…...

浅谈Java常见设计模式及实例

前言 Java 中常用的设计模式有很多种,其实平常用到的还比较少,但是还是有必要了解一下,可以按照实际情况运用到我们的代码中。按照类型可以基本分解为,创建型模式、结构型模式和行为型模式。 创建型模式 (Creational Patterns) 1…...

-总体介绍)

【RISC-V DSP设计】基于CEVA DSP架构的指令集分析(一)-总体介绍

目录 一、引言 二、CEVA-BX1™ DSP Library 概述 三、CEVA-BX1™ DSP Library 功能与特点 四、CEVA-BX1™ DSP Library 优势 今天开始我们继续对CEVA DSP的架构和指令集进行分析,基于对CEVA DSP的分析和了解,后续可以进行基于RISC-V内核架构的DSP指令…...

Rust标量类型详解

在Rust中,数据类型分为标量类型和复合类型。本篇博客将重点介绍Rust的标量类型,其中包括整数类型、浮点类型、布尔类型以及字符类型。 整数类型 Rust提供了多种整数类型,分为带符号整数和无符号整数。带符号整数表示可以为正数、零或负数&a…...

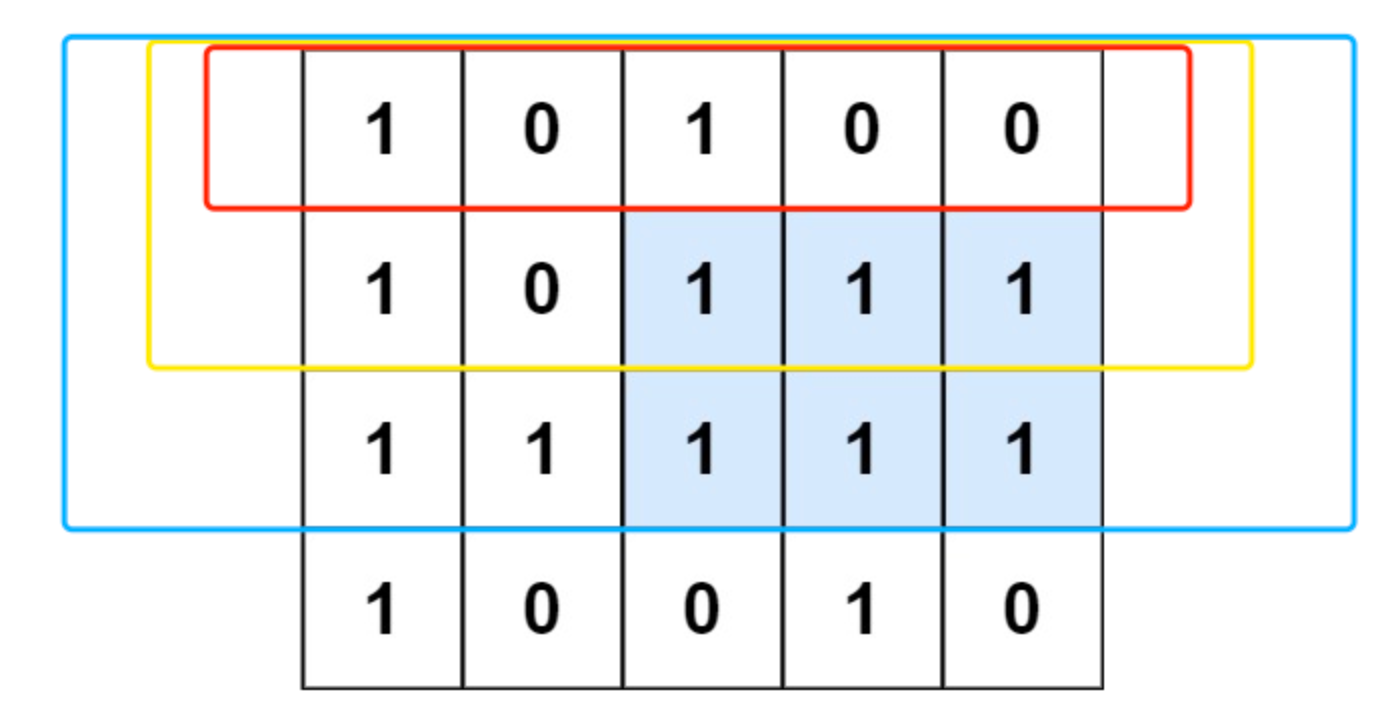

【双指针】【C++算法】1537. 最大得分

作者推荐 【深度优先搜索】【树】【图论】2973. 树中每个节点放置的金币数目 本文涉及知识点 双指针 LeetCoce 1537. 最大得分 你有两个 有序 且数组内元素互不相同的数组 nums1 和 nums2 。 一条 合法路径 定义如下: 选择数组 nums1 或者 nums2 开始遍历&…...

golang常用库之-操作数据库ORM:GORM 包介绍 | 一些 GORM 提示和注意事项

文章目录 golang操作数据库ORM:GORM 包介绍及实战一、什么是GORM 包二、GORM基本使用官方快速开始demo 一些 GORM 提示和注意事项 参考 golang操作数据库ORM:GORM 包介绍及实战 一、什么是GORM 包 官网:https://gorm.io/ github:…...

Stream流学习笔记

Stream流 创建流中间操作1、filter2、map3、distinct4、sorted5、limit6、skip7、flatMap 终结操作1、forEach2、count3、max&min4、collect5、查找与匹配 创建流 单例集合:集合对象.stream() List<Integer> list new ArrayList<>(); Stream<…...

单片机——FLASH(2)

文章目录 flash (stm32f40x 41x的内存映射中区域详解)flash写数据时 flash (stm32f40x 41x的内存映射中区域详解) Main memory 主存储区 放置代码和常数 System memory 系统存储区 方式bootloader代码 OTP区 一次性可编程区 选项…...

个体诊所门诊电子处方开单管理系统软件,配方模板病历模板设置一键导入操作教程

个体诊所门诊电子处方开单管理系统软件,配方模板病历模板设置一键导入操作教程 一、前言 以下操作教程以 佳易王诊所电子处方软件V17.2为例说明,最新版V17.3下载可以点击最下方官网卡片了解。 1、在现实生活中,医师开单可谓是争分夺秒&…...

ELAdmin 配置定时任务

定义方法 在自己的 Module 中写个要执行的方法。 比如获取微信公众号的 accessToken,每两个小时更新一次。这种的其实使用 Spring 的 Scheduled 更方便些,此处仅为演示。 package me.zhengjie.mp.task;import com.alibaba.fastjson.JSON; import lombo…...

【服务器部署】Docker环境的安装

基于CentOS系统的服务器环境下安装Docker环境,安装步骤参考官方指南:https://docs.docker.com/engine/install/centos/ 配置库 sudo yum install -y yum-utils sudo yum-config-manager --add-repo https://download.docker.com/linux/centos/docker-c…...

leetcode刷题--贪心算法

七. 贪心算法 文章目录 七. 贪心算法1. 605 种花问题2. 121 买卖股票的最佳时机3. 561 数组拆分4. 455 分发饼干5. 575 分糖果6. 135 分发糖果7. 409 最长回文串8. 621 任务调度器9. 179 最大数10. 56 合并区间11. 57 插入区间13. 452 用最少数量的箭引爆气球14. 435 无重叠区间…...

《Java 简易速速上手小册》第5章:Java 开发工具和框架(2024 最新版)

文章目录 5.1 Maven 和 Gradle - 构建你的堡垒5.1.1 基础知识5.1.2 重点案例:使用 Maven 构建一个简单的 Java 应用5.1.3 拓展案例 1:使用 Gradle 构建一个 Spring Boot 应用5.1.4 拓展案例 2:使用 Maven 管理多模块项目 5.2 Spring 框架 - 你…...

Python json解析

在Python中解析JSON(JavaScript Object Notation)非常简单,标准库中的json模块提供了必要的功能。JSON是一种轻量级的数据交换格式,易于人阅读和编写,同时也易于机器解析和生成。 以下是使用Python解析JSON的一些基本…...

[FFmpeg学习]从视频中获取图片

从视频中获取图片是一个比较直观的例子,这里从一个基础的例子来查看FFmpeg相关api的使用,从mp4文件中获取一帧图像,保存为jpeg格式图片,mp4文件比较好准备,一般手机录屏文件就是mp4格式。 原理还是比较清楚࿰…...

Redis集中管理Session和系统初始化参数详解

Redis 是一个开源的、基于内存的键值存储系统,通常用作数据库、缓存或消息传递系统。在 Web 应用程序中,Redis 常用于集中管理 Session 数据和系统初始化参数。 Redis 管理 Session Session 是 Web 应用程序中用于保持用户状态的一种机制…...

工业安全零事故的智能守护者:一体化AI智能安防平台

前言: 通过AI视觉技术,为船厂提供全面的安全监控解决方案,涵盖交通违规检测、起重机轨道安全、非法入侵检测、盗窃防范、安全规范执行监控等多个方面,能够实现对应负责人反馈机制,并最终实现数据的统计报表。提升船厂…...

Linux简单的操作

ls ls 查看当前目录 ll 查看详细内容 ls -a 查看所有的内容 ls --help 查看方法文档 pwd pwd 查看当前路径 cd cd 转路径 cd .. 转上一级路径 cd 名 转换路径 …...

全球首个30米分辨率湿地数据集(2000—2022)

数据简介 今天我们分享的数据是全球30米分辨率湿地数据集,包含8种湿地亚类,该数据以0.5X0.5的瓦片存储,我们整理了所有属于中国的瓦片名称与其对应省份,方便大家研究使用。 该数据集作为全球首个30米分辨率、覆盖2000–2022年时间…...

【AI学习】三、AI算法中的向量

在人工智能(AI)算法中,向量(Vector)是一种将现实世界中的数据(如图像、文本、音频等)转化为计算机可处理的数值型特征表示的工具。它是连接人类认知(如语义、视觉特征)与…...

BCS 2025|百度副总裁陈洋:智能体在安全领域的应用实践

6月5日,2025全球数字经济大会数字安全主论坛暨北京网络安全大会在国家会议中心隆重开幕。百度副总裁陈洋受邀出席,并作《智能体在安全领域的应用实践》主题演讲,分享了在智能体在安全领域的突破性实践。他指出,百度通过将安全能力…...

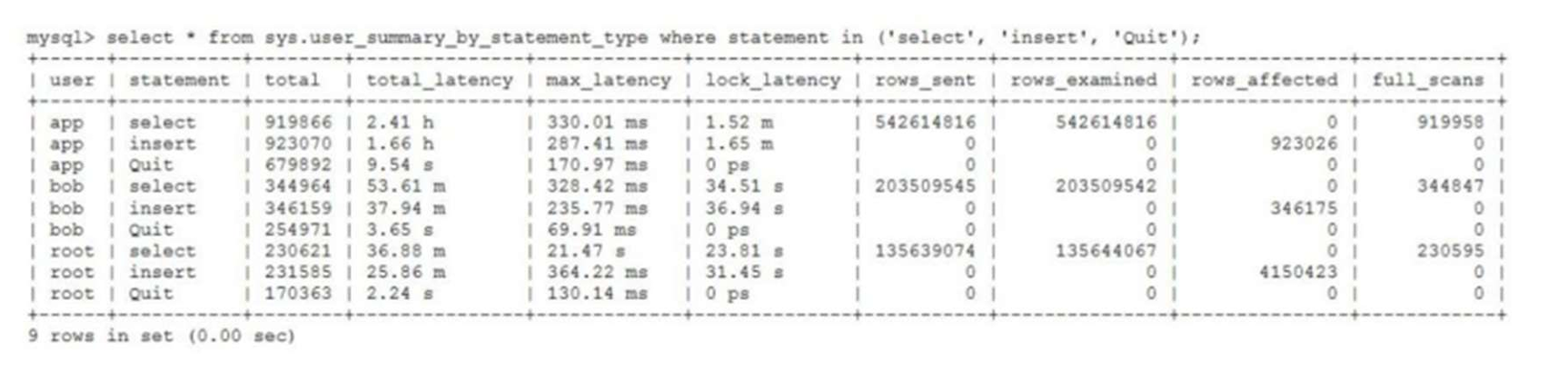

MySQL 8.0 OCP 英文题库解析(十三)

Oracle 为庆祝 MySQL 30 周年,截止到 2025.07.31 之前。所有人均可以免费考取原价245美元的MySQL OCP 认证。 从今天开始,将英文题库免费公布出来,并进行解析,帮助大家在一个月之内轻松通过OCP认证。 本期公布试题111~120 试题1…...

聊一聊接口测试的意义有哪些?

目录 一、隔离性 & 早期测试 二、保障系统集成质量 三、验证业务逻辑的核心层 四、提升测试效率与覆盖度 五、系统稳定性的守护者 六、驱动团队协作与契约管理 七、性能与扩展性的前置评估 八、持续交付的核心支撑 接口测试的意义可以从四个维度展开,首…...

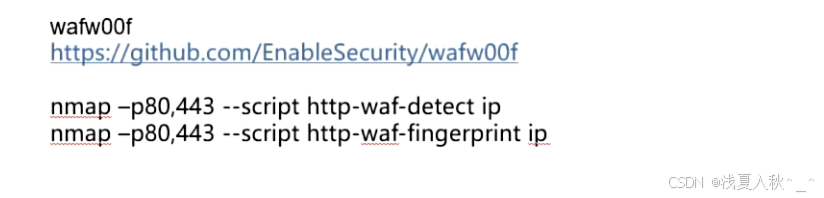

网站指纹识别

网站指纹识别 网站的最基本组成:服务器(操作系统)、中间件(web容器)、脚本语言、数据厍 为什么要了解这些?举个例子:发现了一个文件读取漏洞,我们需要读/etc/passwd,如…...

LINUX 69 FTP 客服管理系统 man 5 /etc/vsftpd/vsftpd.conf

FTP 客服管理系统 实现kefu123登录,不允许匿名访问,kefu只能访问/data/kefu目录,不能查看其他目录 创建账号密码 useradd kefu echo 123|passwd -stdin kefu [rootcode caozx26420]# echo 123|passwd --stdin kefu 更改用户 kefu 的密码…...

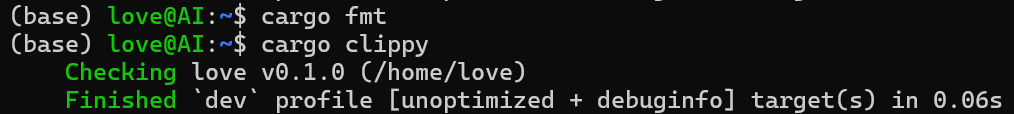

【笔记】WSL 中 Rust 安装与测试完整记录

#工作记录 WSL 中 Rust 安装与测试完整记录 1. 运行环境 系统:Ubuntu 24.04 LTS (WSL2)架构:x86_64 (GNU/Linux)Rust 版本:rustc 1.87.0 (2025-05-09)Cargo 版本:cargo 1.87.0 (2025-05-06) 2. 安装 Rust 2.1 使用 Rust 官方安…...