FPGA——三速自适应以太网设计(2)GMII与RGMII接口

FPGA——以太网设计(2)GMII与RGMII

- 基础知识

- (1)GMII

- (2)RGMII

- (3)IDDR

- GMII设计转RGMII接口

- 跨时钟传输模块

基础知识

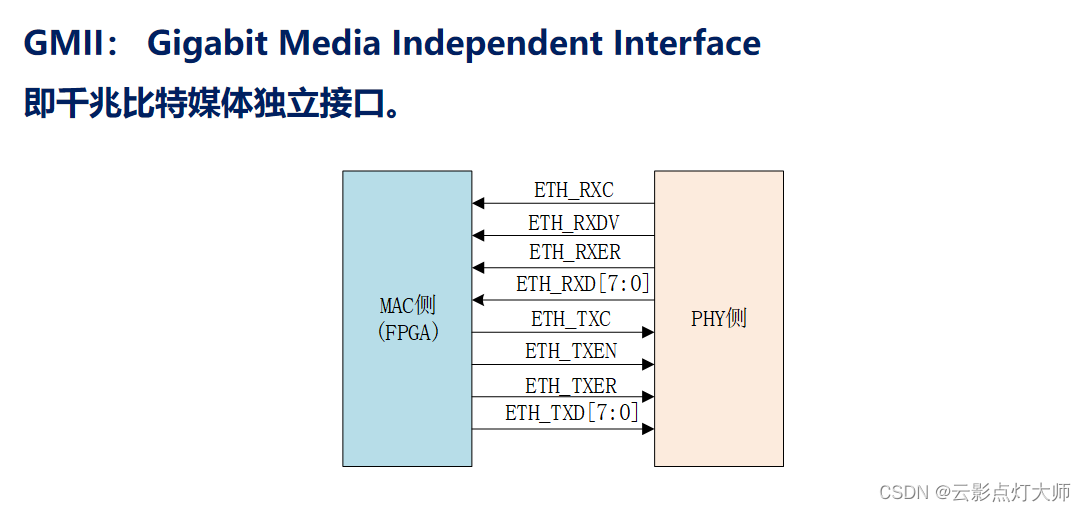

(1)GMII

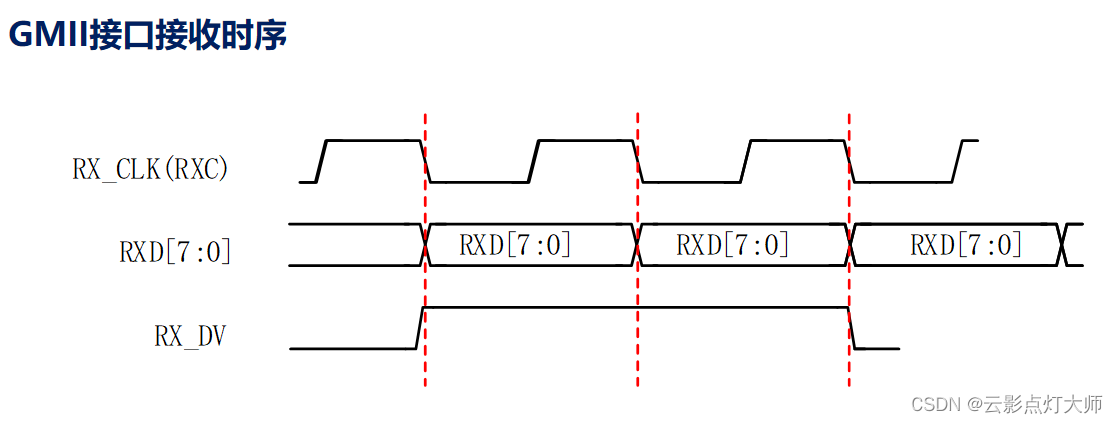

GMII:发送端时钟由MAC端提供

下降沿变化数据,上升沿采集数据

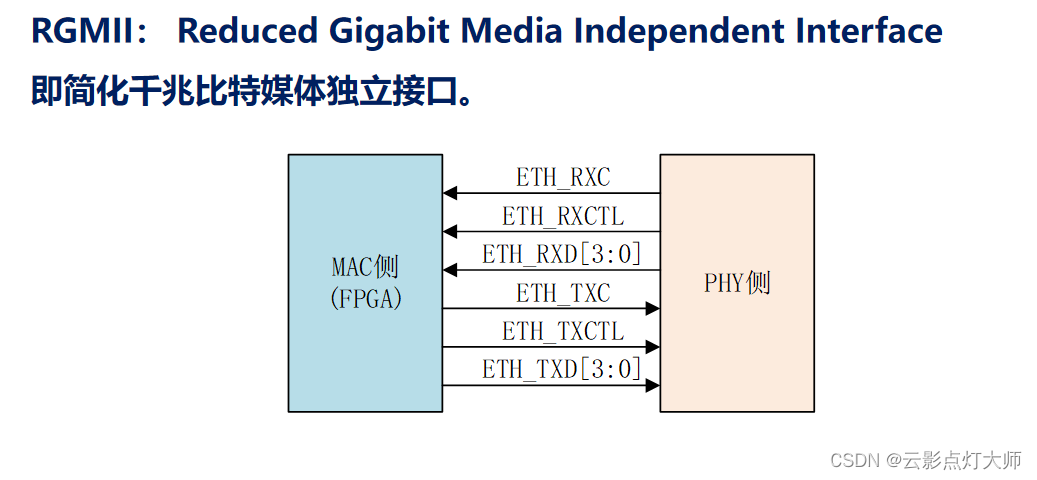

(2)RGMII

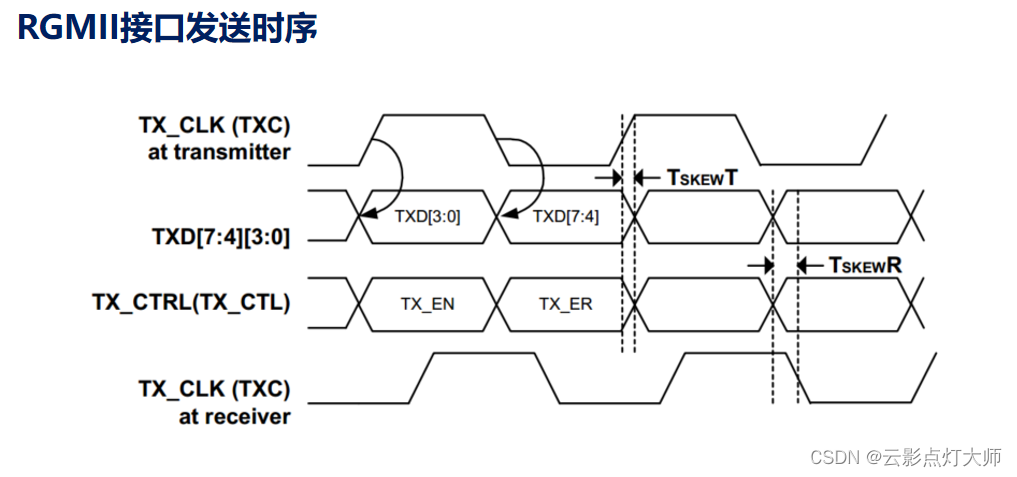

时钟是双沿采样

RGMII:ETH_RXCTL线同时表示有效和错误,有效和错误位相异或得到。

时钟偏移,方便采样

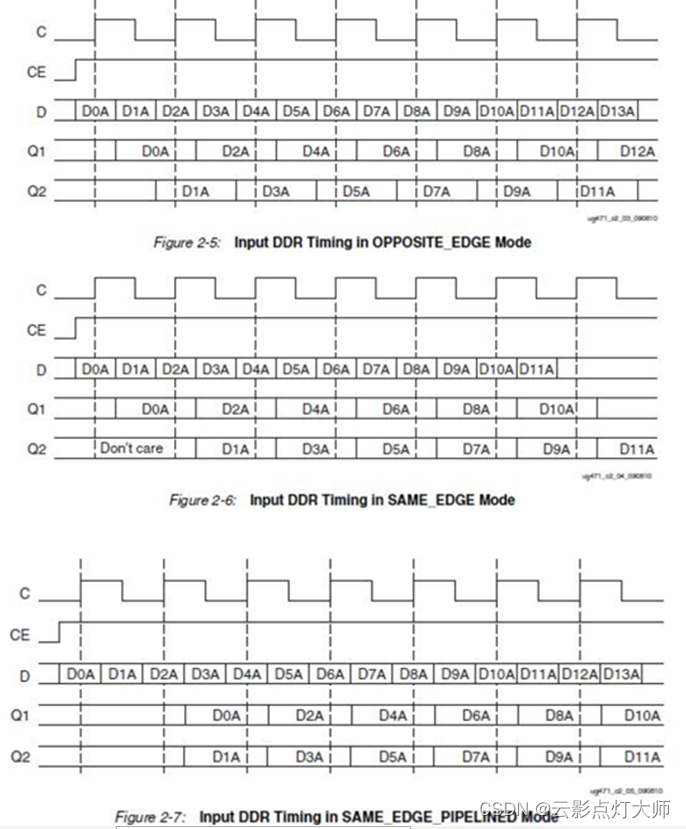

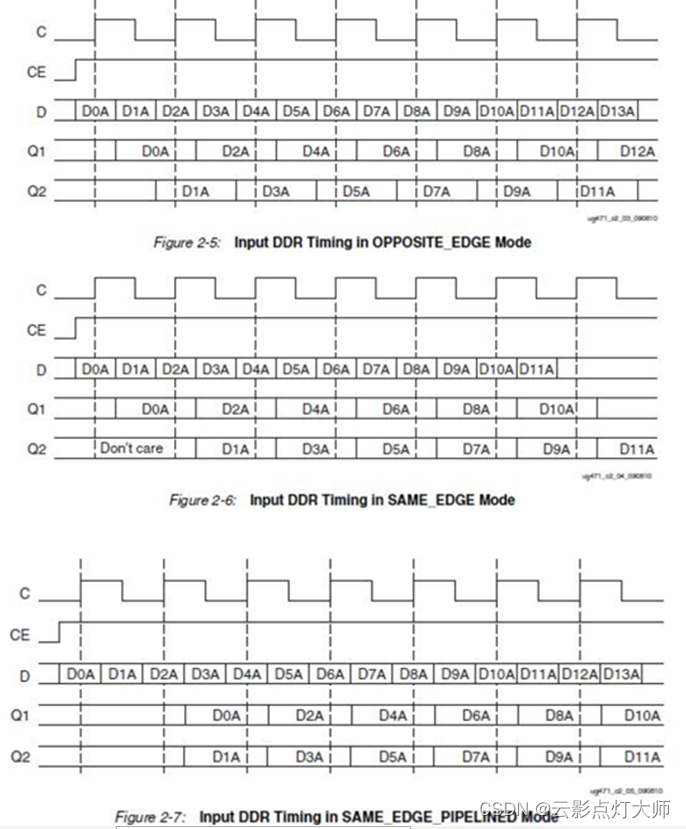

(3)IDDR

IDDR的三种模式

GMII设计转RGMII接口

千兆网:

输入和输出的时候,GMII的8位数据,先在时钟上升沿通过RGMII接口处理低四位,再在时钟的下降沿继续处理高四位。

百兆网:

只在时钟的上升沿通过RGMII接口处理低四位,下个时钟上升沿再处理高四位。所以在上升沿和下降沿都输入输出同一个数据就行。

module RGMII_Tri(/*--------rgmii port--------*/input i_rxc ,input [3 :0] i_rxd ,input i_rx_ctl ,output o_txc ,output [3 :0] o_txd ,output o_tx_ctl ,/*--------data port--------*/output o_rxc ,input [7 :0] i_send_data ,input i_send_valid ,output [7 :0] o_rec_data ,output o_rec_valid ,output o_rec_end ,output [1:0] o_speed ,output o_link

);reg [7 :0] ri_send_data =0 ;

reg ri_send_valid=0 ;

reg [7 :0] ro_rec_data = 0 ;

reg ro_rec_valid= 0 ;

reg ro_rec_end = 0 ;

reg r_cnt_10_100= 0 ;

reg r_tx_cnt_10_100 = 0 ;

reg [1 :0] ro_speed=0 ;

reg ro_link =0 ;

reg [1 :0] r_rec_valid=0 ;wire w_rxc_bufr ;

wire w_rxc_bufio ;

wire w_rxc_idelay ;

wire [3 :0] w_rxd_ibuf ;

wire w_rx_ctl_ibuf ;

(* mark_debug = "true" *)wire [7 :0] w_rec_data ;

(* mark_debug = "true" *)wire [1 :0] w_rec_valid ;

wire [3 :0] w_send_d1 ;

wire [3 :0] w_send_d2 ;

wire w_send_valid ;

wire i_speed1000 ;

wire w_txc ; assign w_txc = ~w_rxc_bufr;

assign o_rxc = w_rxc_bufr;

assign o_speed = ro_speed ;

assign o_link = ro_link ;

assign i_speed1000 = ro_speed == 2'b10 ? 1 : 0;

assign o_rec_data = ro_rec_data ;

assign o_rec_valid = ro_rec_valid;

assign o_rec_end = ro_rec_end ;OBUF #(.DRIVE (12 ), // Specify the output drive strength.IOSTANDARD ("DEFAULT" ), // Specify the output I/O standard.SLEW ("SLOW" ) // Specify the output slew rate

) OBUF_inst (.O (o_txc ), // Buffer output (connect directly to top-level port).I (w_txc ) // Buffer input

);// ODDR #(

// .DDR_CLK_EDGE ("OPPOSITE_EDGE" ), // "OPPOSITE_EDGE" or "SAME_EDGE"

// .INIT (1'b0 ), // Initial value of Q: 1'b0 or 1'b1

// .SRTYPE ("SYNC" ) // Set/Reset type: "SYNC" or "ASYNC"

// ) ODDR_inst (

// .Q (o_txc ), // 1-bit DDR output

// .C (w_rxc_bufr ), // 1-bit clock input

// .CE (1 ), // 1-bit clock enable input

// .D1 (0 ), // 1-bit data input (positive edge)

// .D2 (1 ), // 1-bit data input (negative edge)

// .R (0 ), // 1-bit reset

// .S (0 ) // 1-bit set

// );BUFIO BUFIO_inst (.O (w_rxc_bufio ),.I (i_rxc )

);BUFR #(.BUFR_DIVIDE ("BYPASS" ), .SIM_DEVICE ("7SERIES" )

)

BUFR_inst (.O (w_rxc_bufr ), .CE (1 ), .CLR (0 ), .I (i_rxc )

);// (* IODELAY_GROUP = "rgmii" *)

// IDELAYCTRL IDELAYCTRL_U0 (

// .RDY (RDY), // 1-bit output: Ready output

// .REFCLK (REFCLK), // 1-bit input: Reference clock input

// .RST (RST) // 1-bit input: Active high reset input

// );// (* IODELAY_GROUP = "rgmii" *)

// IDELAYE2 #(

// .CINVCTRL_SEL ("FALSE" ), // Enable dynamic clock inversion (FALSE, TRUE)

// .DELAY_SRC ("IDATAIN" ), // Delay input (IDATAIN, DATAIN)

// .HIGH_PERFORMANCE_MODE ("FALSE" ), // Reduced jitter ("TRUE"), Reduced power ("FALSE")

// .IDELAY_TYPE ("FIXED" ), // FIXED, VARIABLE, VAR_LOAD, VAR_LOAD_PIPE

// .IDELAY_VALUE (0 ), // Input delay tap setting (0-31) 0.15625

// .PIPE_SEL ("FALSE" ), // Select pipelined mode, FALSE, TRUE

// .REFCLK_FREQUENCY (200.0 ), // IDELAYCTRL clock input frequency in MHz (190.0-210.0, 290.0-310.0).

// .SIGNAL_PATTERN ("DATA" ) // DATA, CLOCK input signal

// )

// IDELAYE2_inst (

// .CNTVALUEOUT (), // 5-bit output: Counter value output

// .DATAOUT (w_rxc_idelay ), // 1-bit output: Delayed data output

// .C (), // 1-bit input: Clock input

// .CE (), // 1-bit input: Active high enable increment/decrement input

// .CINVCTRL (), // 1-bit input: Dynamic clock inversion input

// .CNTVALUEIN (), // 5-bit input: Counter value input

// .DATAIN (), // 1-bit input: Internal delay data input

// .IDATAIN (i_rxc ), // 1-bit input: Data input from the I/O

// .INC (), // 1-bit input: Increment / Decrement tap delay input

// .LD (), // 1-bit input: Load IDELAY_VALUE input

// .LDPIPEEN (), // 1-bit input: Enable PIPELINE register to load data input

// .REGRST () // 1-bit input: Active-high reset tap-delay input

// );genvar rxd_i;

generate for(rxd_i = 0 ;rxd_i < 4 ;rxd_i = rxd_i + 1)

beginIBUF #(.IBUF_LOW_PWR ("TRUE" ), .IOSTANDARD ("DEFAULT" )) IBUF_U (.O (w_rxd_ibuf[rxd_i] ), // Buffer output.I (i_rxd[rxd_i] ) // Buffer input (connect directly to top-level port));IDDR #(.DDR_CLK_EDGE ("SAME_EDGE_PIPELINED" ),.INIT_Q1 (1'b0 ),.INIT_Q2 (1'b0 ),.SRTYPE ("SYNC" ) ) IDDR_u0 ( .Q1 (w_rec_data[rxd_i] ), // 1-bit output for positive edge of clock .Q2 (w_rec_data[rxd_i +4] ), // 1-bit output for negative edge of clock.C (w_rxc_bufio ), .CE (1 ),.D (w_rxd_ibuf[rxd_i] ), .R (0 ), .S (0 ) );

end

endgenerateIBUF #(.IBUF_LOW_PWR ("TRUE" ), .IOSTANDARD ("DEFAULT" )

)

IBUF_U

( .O (w_rx_ctl_ibuf ), // Buffer output.I (i_rx_ctl ) // Buffer input (connect directly to top-level port)

);IDDR #(.DDR_CLK_EDGE ("SAME_EDGE_PIPELINED" ),.INIT_Q1 (1'b0 ),.INIT_Q2 (1'b0 ),.SRTYPE ("SYNC" )

)

IDDR_u0

( .Q1 (w_rec_valid[0] ), // 1-bit output for positive edge of clock .Q2 (w_rec_valid[1] ), // 1-bit output for negative edge of clock.C (w_rxc_bufio ), .CE (1 ),.D (w_rx_ctl_ibuf ), .R (0 ), .S (0 )

);always@(posedge w_rxc_bufr)

beginif(!i_speed1000 && (&w_rec_valid))r_cnt_10_100 <= r_cnt_10_100 + 1;else r_cnt_10_100 <= 'd0;

end always@(posedge w_rxc_bufr)

beginif(&w_rec_valid && i_speed1000)ro_rec_valid <= 'd1;else ro_rec_valid <= r_cnt_10_100;

endalways@(posedge w_rxc_bufr)

beginif(i_speed1000)ro_rec_data <= w_rec_data;else ro_rec_data <= {w_rec_data[3:0],ro_rec_data[7:4]};

endalways@(posedge w_rxc_bufr)

beginr_rec_valid <= w_rec_valid;

endalways@(posedge w_rxc_bufr)

beginif(!w_rec_valid && r_rec_valid)ro_rec_end <= 'd1;else ro_rec_end <= 'd0;

endalways@(posedge w_rxc_bufr)

beginif(w_rec_valid == 'd0) beginro_speed <= w_rec_data[2:1];ro_link <= w_rec_data[0];end else beginro_speed <= ro_speed;ro_link <= ro_link ;end

end/*---------rgmii send--------*/

always@(posedge w_rxc_bufr)

beginri_send_data <= i_send_data;ri_send_valid <= i_send_valid;

endalways@(posedge w_rxc_bufr)

beginif(i_send_valid)r_tx_cnt_10_100 <= r_tx_cnt_10_100 + 1;else r_tx_cnt_10_100 <= 'd0;

endgenvar txd_i;

generate for(txd_i = 0 ;txd_i < 4 ; txd_i = txd_i + 1)

beginassign w_send_d1[txd_i] = i_speed1000 ? i_send_data[txd_i] : r_tx_cnt_10_100 == 0 ? i_send_data[txd_i] : ri_send_data[txd_i + 4];assign w_send_d2[txd_i] = i_speed1000 ? i_send_data[txd_i + 4] : r_tx_cnt_10_100 == 0 ? i_send_data[txd_i] : ri_send_data[txd_i + 4];ODDR #(.DDR_CLK_EDGE ("OPPOSITE_EDGE" ),.INIT (1'b0 ),.SRTYPE ("SYNC" ) ) ODDR_u (.Q (o_txd[txd_i] ), .C (w_txc ),.CE (1 ),.D1 (w_send_d1[txd_i] ), .D2 (w_send_d2[txd_i] ), .R (0 ),.S (0 ) );

end

endgenerateassign w_send_valid = i_speed1000 ? i_send_valid : i_send_valid | ri_send_valid;ODDR#(.DDR_CLK_EDGE ("OPPOSITE_EDGE" ),.INIT (1'b0 ),.SRTYPE ("SYNC" )

)

ODDR_uu0

(.Q (o_tx_ctl ), .C (w_txc ),.CE (1 ),.D1 (w_send_valid ), .D2 (w_send_valid ), .R (0 ),.S (0 )

);endmodule跨时钟传输模块

module RGMII_RAM(input i_udp_stack_clk ,input [7 :0] i_GMII_data ,input i_GMII_valid ,output [7 :0] o_GMII_data ,output o_GMII_valid ,input i_rxc ,input i_speed1000 ,output [7 :0] o_send_data ,output o_send_valid ,input [7 :0] i_rec_data ,input i_rec_valid ,input i_rec_end

);/***************function**************//***************parameter*************//***************port******************/ /***************mechine***************//***************reg*******************/

reg [10:0] r_ram_addr_A=0 ;

reg [10:0] r_rec_len =0 ;

reg r_ram_en_B =0 ;

reg r_ram_en_B_1d=0 ;

reg r_ram_en_B_2d=0 ;

reg [10:0] r_ram_addr_B=0 ;

reg r_fifo_wr_en=0 ;

reg r_fifo_rd_en=0 ;

reg ri_rec_en =0 ;

reg r_read_run =0 ;

reg [10:0] r_read_cnt =0 ;

reg [7 :0] ro_GMII_data =0 ;

reg ro_GMII_valid=0 ;

reg [10:0] r_tx_ram_addr_A=10 ;

reg [10:0] r_tx_len=10 ;

reg r_tx_fifo_wren=0 ;

reg ri_GMII_valid=0 ;

reg r_tx_ram_en_B=0 ;

reg [10:0] r_tx_ram_addr_B=0 ;

reg r_tx_fifo_rden=0 ;

reg r_tx_read_run=0 ;

reg [10:0] r_tx_cnt =0 ;

reg [7 :0] ro_send_data =0 ;

reg ro_send_valid=0 ;

reg w_rxc=0 ;

reg ri_rec_end=0 ;

reg ro_send_valid_1d=0 ;/***************wire******************/

wire [7 :0] w_ram_dout_B ;

wire [10:0] w_fifo_dout ;

wire w_fifo_full ;

wire w_fifo_empty ;

wire [7 :0] w_tx_ram_dout ;

wire [10:0] w_tx_fifo_dout ;

wire w_tx_fifo_full ;

wire w_tx_fifo_empty ;/***************component*************/

RAM_8_1600 RAM_8_1600_U0 (.clka (i_rxc ), // input wire clka.ena (i_rec_valid ), // input wire ena.wea (i_rec_valid ), // input wire [0 : 0] wea.addra (r_ram_addr_A ), // input wire [10 : 0] addra.dina (i_rec_data ), // input wire [7 : 0] dina.douta ( ), // output wire [7 : 0] douta.clkb (i_udp_stack_clk), // input wire clkb.enb (r_ram_en_B ), // input wire enb.web (0 ), // input wire [0 : 0] web.addrb (r_ram_addr_B ), // input wire [10 : 0] addrb.dinb (0 ), // input wire [7 : 0] dinb.doutb (w_ram_dout_B ) // output wire [7 : 0] doutb

);FIFO_ASYNC_11_64 FIFO_ASYNC_11_64_u0 (.wr_clk (i_rxc ), // input wire wr_clk.rd_clk (i_udp_stack_clk), // input wire rd_clk.din (r_rec_len ), // input wire [10 : 0] din.wr_en (r_fifo_wr_en ), // input wire wr_en.rd_en (r_fifo_rd_en ), // input wire rd_en.dout (w_fifo_dout ), // output wire [10 : 0] dout.full (w_fifo_full ), // output wire full.empty (w_fifo_empty ) // output wire empty

);RAM_8_1600 RAM_8_1600_tx_U0 (.clka (i_udp_stack_clk ), // input wire clka.ena (i_GMII_valid ), // input wire ena.wea (i_GMII_valid ), // input wire [0 : 0] wea.addra (r_tx_ram_addr_A ), // input wire [10 : 0] addra.dina (i_GMII_data ), // input wire [7 : 0] dina.douta (), // output wire [7 : 0] douta.clkb (i_rxc ), // input wire clkb.enb (r_tx_ram_en_B ), // input wire enb.web (0 ), // input wire [0 : 0] web.addrb (r_tx_ram_addr_B ), // input wire [10 : 0] addrb.dinb (0 ), // input wire [7 : 0] dinb.doutb (w_tx_ram_dout ) // output wire [7 : 0] doutb

);FIFO_ASYNC_11_64 FIFO_ASYNC_11_64_tx_u0 (.wr_clk (i_udp_stack_clk ), // input wire wr_clk.rd_clk (i_rxc ), // input wire rd_clk.din (r_tx_len ), // input wire [10 : 0] din.wr_en (r_tx_fifo_wren ), // input wire wr_en.rd_en (r_tx_fifo_rden ), // input wire rd_en.dout (w_tx_fifo_dout ), // output wire [10 : 0] dout.full (w_tx_fifo_full ), // output wire full.empty (w_tx_fifo_empty ) // output wire empty

);/***************assign****************/

assign o_GMII_data = ro_GMII_data ;

assign o_GMII_valid = ro_GMII_valid ;

assign o_send_data = ro_send_data ;

assign o_send_valid = ro_send_valid_1d ;/***************always****************/

/*--------rgmii--------*/

always@(posedge i_rxc)

beginif(i_rec_valid)r_ram_addr_A <= r_ram_addr_A + 1;else if(i_rec_end)r_ram_addr_A <= 'd0;else r_ram_addr_A <= r_ram_addr_A;

endalways@(posedge i_rxc)

beginif(i_rec_valid)r_rec_len <= r_ram_addr_A + 1;else r_rec_len <= r_rec_len;

endalways@(posedge i_rxc)

beginri_rec_end <= i_rec_end;

endalways@(posedge i_rxc)

beginif(i_rec_end & !ri_rec_end)r_fifo_wr_en <= 'd1;else r_fifo_wr_en <= 'd0;

endalways@(posedge i_rxc)

beginif(r_tx_cnt == w_tx_fifo_dout)r_tx_read_run <= 'd0;else if(!w_tx_fifo_empty)r_tx_read_run <= 'd1;else r_tx_read_run <= r_tx_read_run;

endalways@(posedge i_rxc)

beginif(!r_tx_read_run && !w_tx_fifo_empty)r_tx_fifo_rden <= 'd1;else r_tx_fifo_rden <= 'd0;

endalways@(posedge i_rxc)

beginendalways@(posedge i_rxc)

beginif(i_speed1000)if(r_tx_cnt == w_tx_fifo_dout)r_tx_ram_en_B <= 'd0;else if(r_tx_fifo_rden)r_tx_ram_en_B <= 'd1;else r_tx_ram_en_B <= r_tx_ram_en_B;else if(r_tx_ram_en_B)r_tx_ram_en_B <= 'd0;else if(r_tx_fifo_rden || r_tx_read_run)r_tx_ram_en_B <= 'd1;else r_tx_ram_en_B <= 'd0;

endalways@(posedge i_rxc)

beginif(r_tx_ram_en_B)r_tx_ram_addr_B <= r_tx_ram_addr_B + 1;else r_tx_ram_addr_B <= 'd0;

endalways@(posedge i_rxc)

beginif(r_tx_ram_en_B)r_tx_cnt <= r_tx_cnt + 1;else r_tx_cnt <= 'd0;

endalways@(posedge i_rxc)

beginro_send_data <= w_tx_ram_dout;ro_send_valid <= r_tx_ram_en_B;

end

/*--------udp--------*/

always@(posedge i_udp_stack_clk)

beginif(r_read_cnt == w_fifo_dout)r_read_run <= 'd0;else if(!w_fifo_empty)r_read_run <= 'd1;else r_read_run <= r_read_run;

endalways@(posedge i_udp_stack_clk)

beginif(!r_read_run && !w_fifo_empty)r_fifo_rd_en <= 'd1;else r_fifo_rd_en <= 'd0;

endalways@(posedge i_udp_stack_clk)

beginif(r_read_cnt == w_fifo_dout) r_read_cnt <= 'd0;else if(r_ram_en_B) r_read_cnt <= r_read_cnt + 1;else r_read_cnt <= r_read_cnt;

endalways@(posedge i_udp_stack_clk)

beginif(r_read_cnt == w_fifo_dout)r_ram_en_B <= 'd0;else if(r_fifo_rd_en) r_ram_en_B <= 'd1;elser_ram_en_B <= r_ram_en_B;

endalways@(posedge i_udp_stack_clk)

beginif(r_ram_en_B)r_ram_addr_B <= r_ram_addr_B + 1;else r_ram_addr_B <= 'd0;

endalways@(posedge i_udp_stack_clk)

beginr_ram_en_B_1d <= r_ram_en_B;ro_GMII_data <= w_ram_dout_B;r_ram_en_B_2d <= r_ram_en_B_1d;

endalways@(posedge i_udp_stack_clk)

beginif(!r_ram_en_B & r_ram_en_B_1d)ro_GMII_valid <= 'd0;else if(r_ram_en_B_1d & !r_ram_en_B_2d)ro_GMII_valid <= 'd1;else ro_GMII_valid <= ro_GMII_valid;

endalways@(posedge i_udp_stack_clk)

beginif(i_GMII_valid)r_tx_ram_addr_A <= r_tx_ram_addr_A + 1;else r_tx_ram_addr_A <= 'd0;

endalways@(posedge i_udp_stack_clk)

beginif(i_GMII_valid)r_tx_len <= r_tx_ram_addr_A;else r_tx_len <= r_tx_len;

endalways@(posedge i_udp_stack_clk)

beginri_GMII_valid <= i_GMII_valid;ro_send_valid_1d <= ro_send_valid;

end always@(posedge i_udp_stack_clk)

beginif(!i_GMII_valid & ri_GMII_valid)r_tx_fifo_wren <= 'd1;else r_tx_fifo_wren <= 'd0;

endendmodule

有问题可以加企鹅群 658476482 交流

相关文章:

FPGA——三速自适应以太网设计(2)GMII与RGMII接口

FPGA——以太网设计(2)GMII与RGMII 基础知识(1)GMII(2)RGMII(3)IDDR GMII设计转RGMII接口跨时钟传输模块 基础知识 (1)GMII GMII:发送端时钟由MAC端提供 下…...

【校园导航小程序】2.0版本 静态/云开发项目 升级日志

演示视频 【校园导航小程序】2.0版本 静态/云开发项目 演示 首页 重做了首页,界面更加高效和美观 校园指南页 新增了 “校园指南” 功能,可以搜索和浏览校园生活指南 地图页 ①弃用路线规划插件,改用SDK开发包。可以无阻通过审核并发布…...

)

深入揭秘Lucene:全面解析其原理与应用场景(二)

本系列文章简介: 本系列文章将深入揭秘Lucene,全面解析其原理与应用场景。我们将从Lucene的基本概念和核心组件开始,逐步介绍Lucene的索引原理、搜索算法以及性能优化策略。通过阅读本文,读者将会对Lucene的工作原理有更深入的了解…...

Java中synchronized关键字、ReentrantLock、volatile关键字是如何实现线程同步的。

在Java中,synchronized关键字、ReentrantLock和volatile关键字这三个是编程中常用于实现线程同步的机制,下面结合代码详细说明一下这三个关键字的用法。 1. synchronized关键字: synchronized关键字是Java语言提供的内置锁机制,…...

路由拦截器

路由拦截可以分为几种不同的类型,每种类型都有其特定的作用和适用场景。以下是常见的几种路由拦截类型及其用途: 身份验证拦截器: 作用: 检查用户是否已经登录或具有有效的身份认证,并根据认证状态决定是否允许用户访问…...

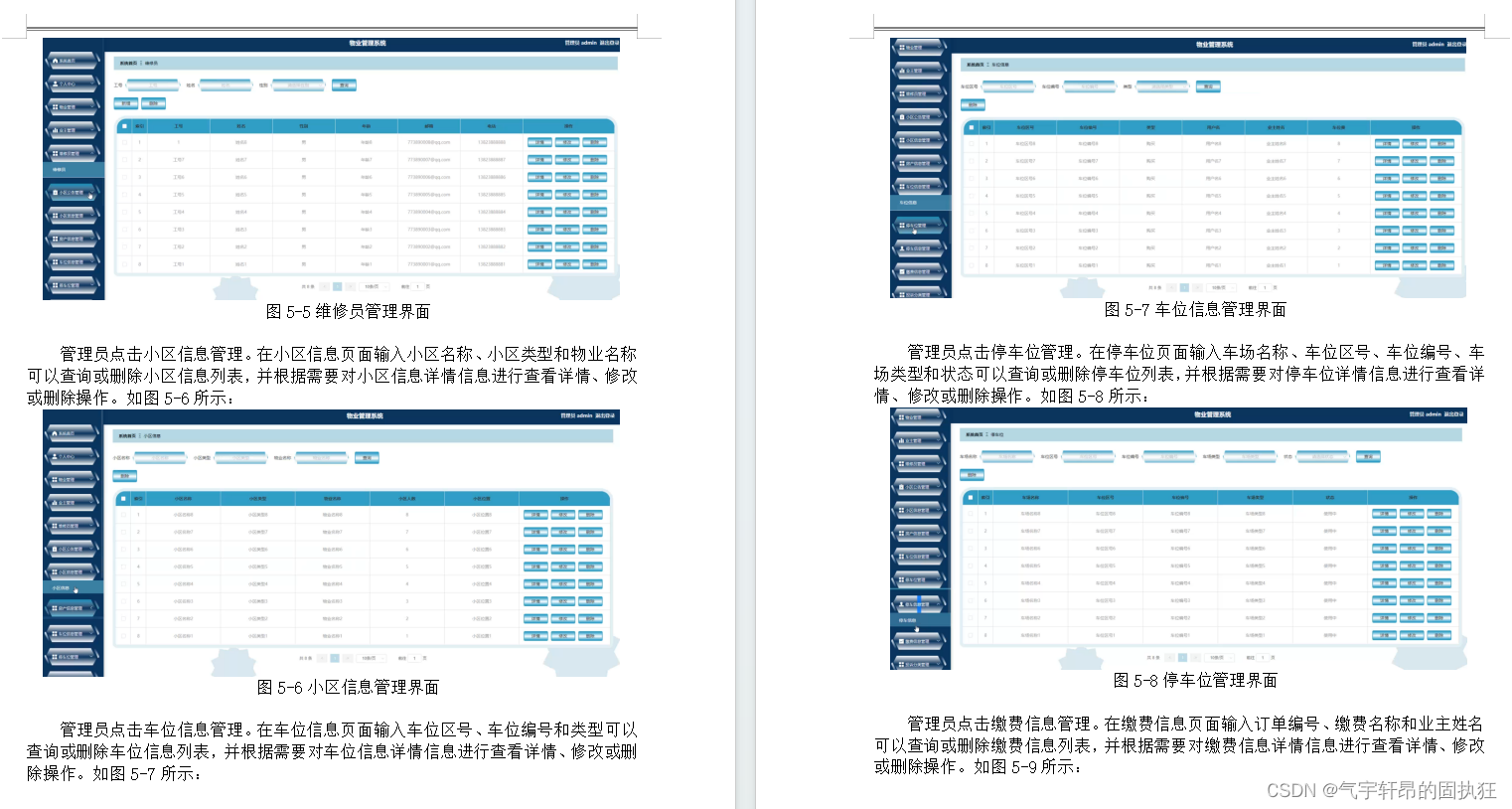

Springboot+vue的物业管理系统(有报告)。Javaee项目,springboot vue前后端分离项目。

演示视频: Springbootvue的物业管理系统(有报告)。Javaee项目,springboot vue前后端分离项目。 项目介绍: 本文设计了一个基于Springbootvue的物业管理系统,采用M(model)Vÿ…...

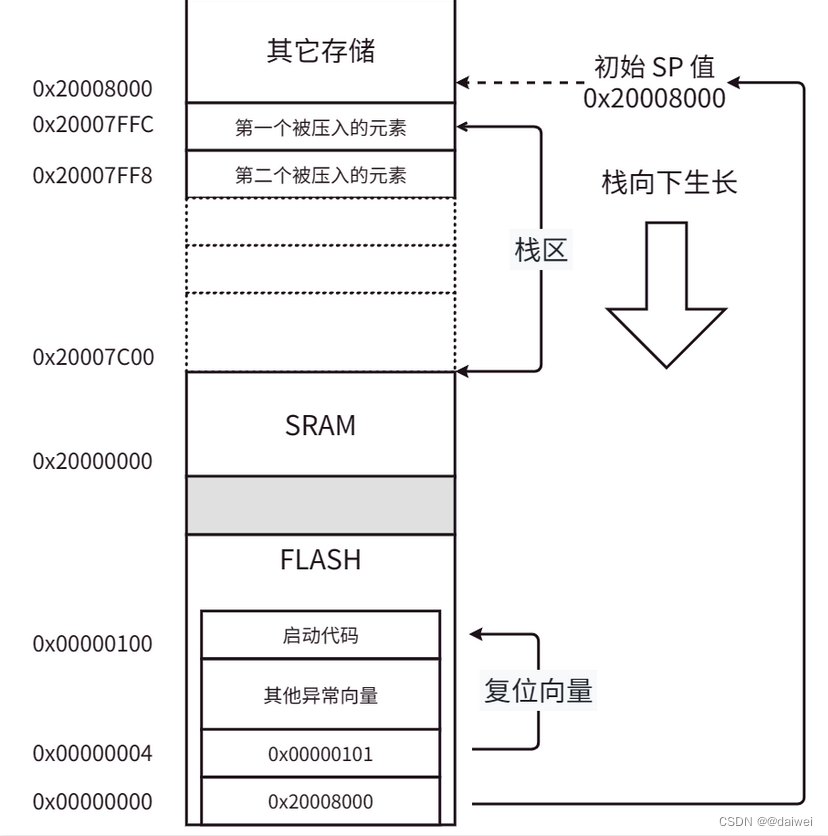

STM32的启动流程分析 和 一些底层控制的原理

阅读引言: 阅读本文之后, 你将对单片机, 甚至是嵌入式系统, 或者是传统的PC机系统的启动流程有一个大致的了解, 本文更加偏向于单片机的启动流程分析。 目录 一、基础知识 1.STM32系列的微控制器(mcu&…...

C#面:几种注释类型

三种常见的注释类型:单行注释、多行注释和 XML 注释。 单行注释: 以双斜线 // 开头,用于在一行中注释单个语句或代码块。单行注释会被编译器忽略,不会对程序的执行产生任何影响。 例如: // 这是一个单行注释 int a…...

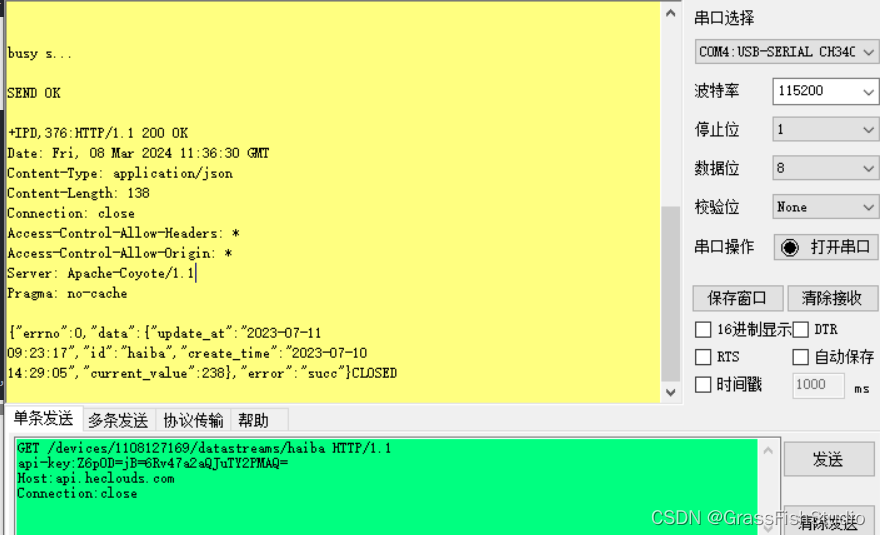

#onenet网络请求http(GET,POST)

参考博文: POST: https://blog.csdn.net/qq_43350239/article/details/104361153 POST请求(用串口助手测试): POST /devices/1105985351/datapoints HTTP/1.1 api-key:AdbrV5kCRsKsRCfjboYOCVcF9FY Host:api.heclouds.com Con…...

零基础学习JS--基础篇--索引集合类

数组是由名称和索引引用的值构成的有序列表。 JavaScript 中没有明确的数组数据类型。但是,你可以使用预定义的 Array 对象及其方法来处理应用程序中的数组。Array 对象具有以各种方式操作数组的方法,例如连接、反转和排序。它有一个用于确定数组长度的…...

【硬件工程师面经整理25_AD】

文章目录 1 AD设计电路全流程2 ad和cadence区别-逻辑上的区别 1 AD设计电路全流程 软件AD or 模拟数字? 软件AD:AD设计电路全流程包括以下步骤:选择AD库和添加、画原理图、PCB布局、PCB布线、PCB打样、PCB加工 模拟数字: 需求分…...

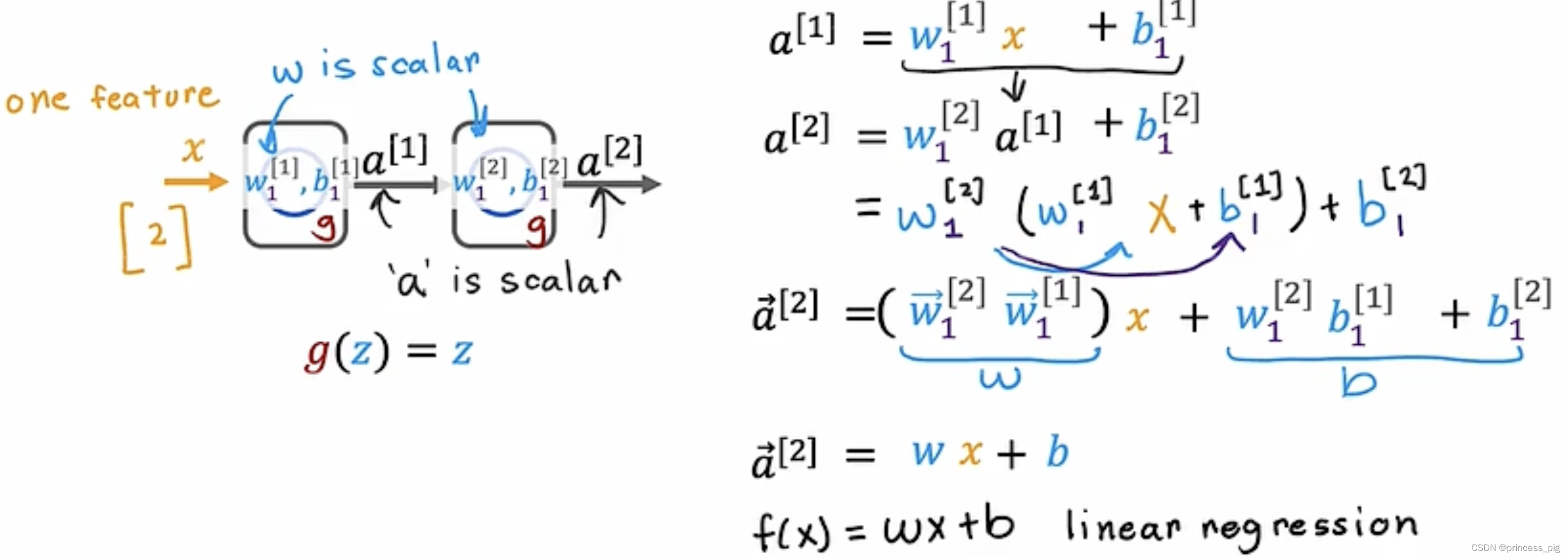

神经网络的矢量化,训练与激活函数

我们现在再回到我们的神经元部分,来看我们如何用python进行正向传递。 单层的正向传递: 我们回到我们的线性回归的函数。我们每个神经元通过上述的方法,就可以得到我们的激发值,从而可以继续进行下一层。 我们用这个方法就可以得…...

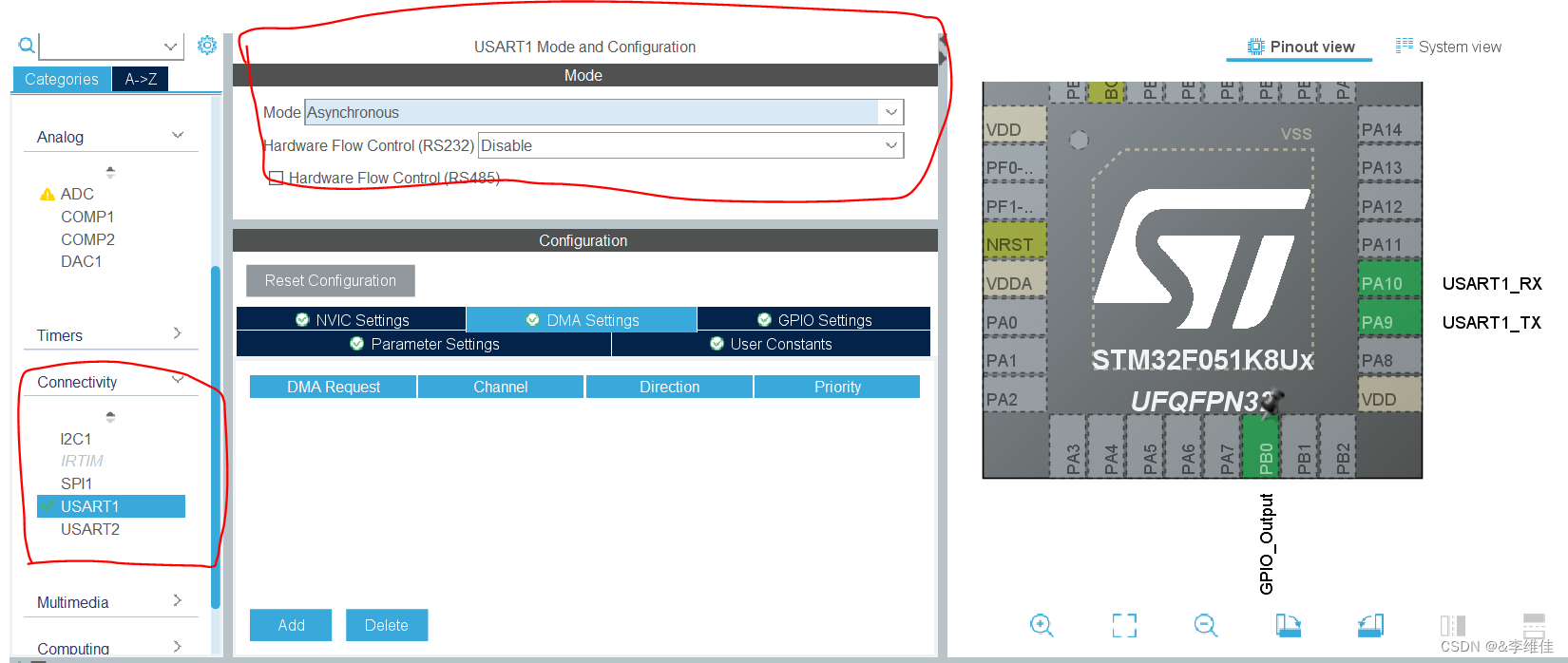

3.7号freeRtoS

1. 串口通信 配置串口为异步通信 设置波特率,数据位,校验位,停止位,数据的方向 同步通信 在同步通信中,数据的传输是在发送端和接收端之间通过一个共享的时钟信号进行同步的。这意味着发送端和接收端的时钟需要保持…...

瑞芯微 | I2S-音频基础 -1

最近调试音频驱动,顺便整理学习了一下i2s、alsa相关知识,整理成了几篇文章,后续会陆续更新。 喜欢嵌入式、Li怒晓得老铁可以关注一口君账号。 1. 音频常用术语 名称含义ADC(Analog to Digit Conversion)模拟信号转换…...

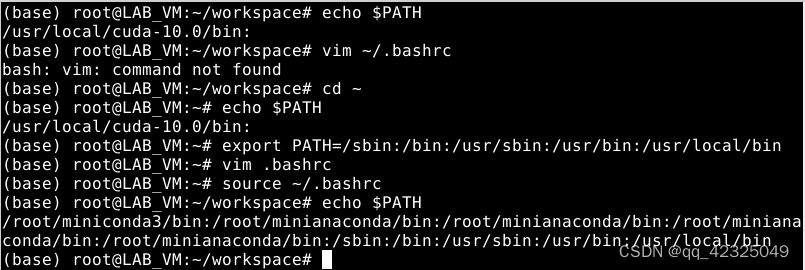

Linux配置.bashrc文件导致各种命令(vim、sudo)失效。

Linux配置.bashrc文件导致各种命令(vim、sudo)失效。 起因是 nvcc-V一直报错:-bash:nvcc: command not found 踩坑记录:上网一查说是没有配置cuda的环境变量。于是去修改了bashrc文件,在最下面…...

Visual Studio 2022 Version 17.9 新功能

Visual Studio 2022 v17.9 为广大 C 开发者引入了一系列好用的新功能和改进优化。 内存布局 现在,你可以使用【内存布局,Memory Layout】功能以可视化的方式来查看对象,结构体及联合体的内存布局信息,这可比以前需要手动查看内存…...

ArrayList 和 LinkedList 的区别

ArrayList ArrayList 是基于动态数组实现的, 它使用一块连续的内存空间来存储元素,因此访问元素的速度非常快(时间复杂度为 O(1)), 但是,在插入或删除元素时,如果位置不在数组末尾࿰…...

VGG16-CF-VGG11实验报告

说明:VGG16和CF-VGG11是论文《A 3D Fluorescence Classification and Component Prediction Method Based on VGG Convolutional Neural Network and PARAFAC Analysis Method》使用的两种主要模型。其对应代码仓库提供了实验使用的数据集、平行因子分析结果和CNN模型。论文和…...

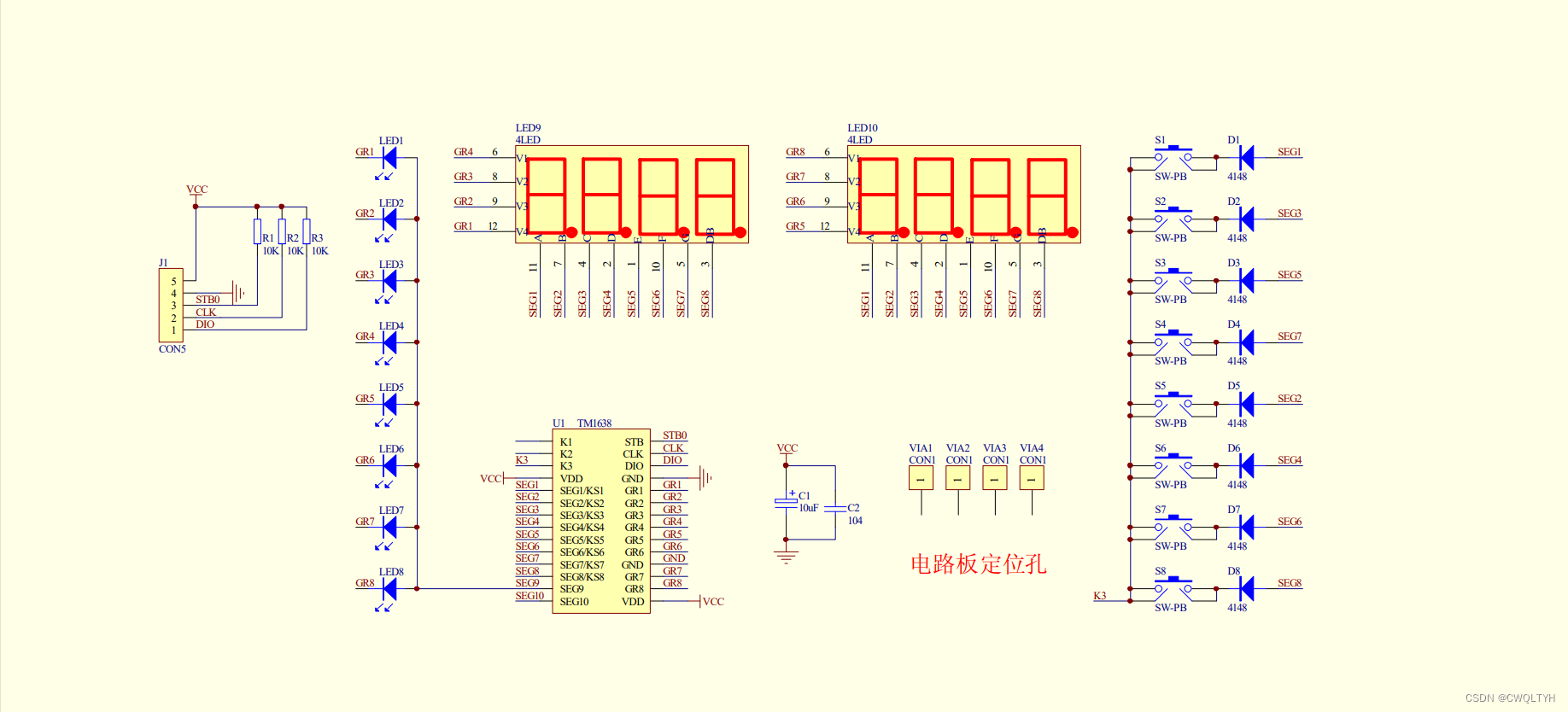

基于STC12C5A60S2系列1T 8051单片机的TM1638键盘数码管模块的按键扫描、数码管显示按键值、显示按键LED应用

基于STC12C5A60S2系列1T 8051单片机的TM1638键盘数码管模块的按键扫描、数码管显示按键值、显示按键LED应用 STC12C5A60S2系列1T 8051单片机管脚图STC12C5A60S2系列1T 8051单片机I/O口各种不同工作模式及配置STC12C5A60S2系列1T 8051单片机I/O口各种不同工作模式介绍TM1638键盘…...

uniapp使用华为云OBS进行上传

前言:无论是使用华为云还是阿里云,使用其产品的时候必须阅读文档 1、以华为云为例,刚接触此功能肯定是无从下手的情况,那么我们需要思考,我们使用该产品所用到的文档是什么 2、我们要使用obs 文件上传,肯…...

ES6从入门到精通:前言

ES6简介 ES6(ECMAScript 2015)是JavaScript语言的重大更新,引入了许多新特性,包括语法糖、新数据类型、模块化支持等,显著提升了开发效率和代码可维护性。 核心知识点概览 变量声明 let 和 const 取代 var…...

vue3 定时器-定义全局方法 vue+ts

1.创建ts文件 路径:src/utils/timer.ts 完整代码: import { onUnmounted } from vuetype TimerCallback (...args: any[]) > voidexport function useGlobalTimer() {const timers: Map<number, NodeJS.Timeout> new Map()// 创建定时器con…...

中关于正整数输入的校验规则)

Element Plus 表单(el-form)中关于正整数输入的校验规则

目录 1 单个正整数输入1.1 模板1.2 校验规则 2 两个正整数输入(联动)2.1 模板2.2 校验规则2.3 CSS 1 单个正整数输入 1.1 模板 <el-formref"formRef":model"formData":rules"formRules"label-width"150px"…...

AirSim/Cosys-AirSim 游戏开发(四)外部固定位置监控相机

这个博客介绍了如何通过 settings.json 文件添加一个无人机外的 固定位置监控相机,因为在使用过程中发现 Airsim 对外部监控相机的描述模糊,而 Cosys-Airsim 在官方文档中没有提供外部监控相机设置,最后在源码示例中找到了,所以感…...

Golang——7、包与接口详解

包与接口详解 1、Golang包详解1.1、Golang中包的定义和介绍1.2、Golang包管理工具go mod1.3、Golang中自定义包1.4、Golang中使用第三包1.5、init函数 2、接口详解2.1、接口的定义2.2、空接口2.3、类型断言2.4、结构体值接收者和指针接收者实现接口的区别2.5、一个结构体实现多…...

与文本切分器(Splitter)详解《二》)

LangChain 中的文档加载器(Loader)与文本切分器(Splitter)详解《二》

🧠 LangChain 中 TextSplitter 的使用详解:从基础到进阶(附代码) 一、前言 在处理大规模文本数据时,特别是在构建知识库或进行大模型训练与推理时,文本切分(Text Splitting) 是一个…...

【把数组变成一棵树】有序数组秒变平衡BST,原来可以这么优雅!

【把数组变成一棵树】有序数组秒变平衡BST,原来可以这么优雅! 🌱 前言:一棵树的浪漫,从数组开始说起 程序员的世界里,数组是最常见的基本结构之一,几乎每种语言、每种算法都少不了它。可你有没有想过,一组看似“线性排列”的有序数组,竟然可以**“长”成一棵平衡的二…...

向量几何的二元性:叉乘模长与内积投影的深层联系

在数学与物理的空间世界中,向量运算构成了理解几何结构的基石。叉乘(外积)与点积(内积)作为向量代数的两大支柱,表面上呈现出截然不同的几何意义与代数形式,却在深层次上揭示了向量间相互作用的…...

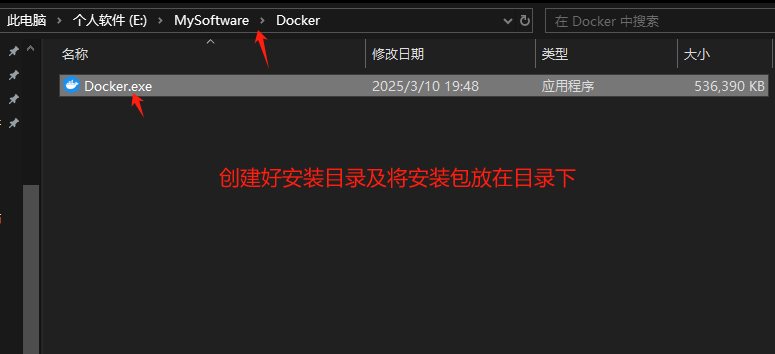

大模型——基于Docker+DeepSeek+Dify :搭建企业级本地私有化知识库超详细教程

基于Docker+DeepSeek+Dify :搭建企业级本地私有化知识库超详细教程 下载安装Docker Docker官网:https://www.docker.com/ 自定义Docker安装路径 Docker默认安装在C盘,大小大概2.9G,做这行最忌讳的就是安装软件全装C盘,所以我调整了下安装路径。 新建安装目录:E:\MyS…...

OpenGL-什么是软OpenGL/软渲染/软光栅?

软OpenGL(Software OpenGL)或者软渲染指完全通过CPU模拟实现的OpenGL渲染方式(包括几何处理、光栅化、着色等),不依赖GPU硬件加速。这种模式通常性能较低,但兼容性极强,常用于不支持硬件加速…...