【chatGPT】我:在Cadence Genus软件中,出现如下问题:......【4】

我

在Cadence Genus中,tcl代码为:foreach clk $clk_list{

set clkName [lindex $clk_list 0]

set targetFreq [lindex $clk_list 1]

set uncSynth [lindex $clk_list 4]

set clkPeriod [lindex “%.3f” [expr 1 / $targetFreq]]

…

}

以上代码出现如下错误:missing operand at @

in expression “1 / @”

([parsing expression “1/”)

invoked from within

“expr 1/$targetFreq”

ChatGPT

在你给出的 Tcl 代码片段中,有一个明显的逻辑错误。foreach 循环中的 clk 变量被假设为是一个列表,你想从中提取不同的元素。但实际上,循环的每次迭代中,clk 只是 clk_list 中的一个元素。因此,你应该在循环体内使用 clk 而不是 clk_list 来访问当前迭代的元素。

错误的根源在于 targetFreq 没有被正确设置。从你的代码来看,targetFreq 应该是 clk 列表的第二个元素 [lindex $clk 1]。但是,在 foreach 循环中你使用了 lindex $clk_list 1,这相当于试图在每次迭代中都获取 clk_list 第二个元素,这显然不符合逻辑,因为 targetFreq 应该是根据每个 clk 获取的。

另外,clkPeriod 的计算中,你试图格式化数字为一个特定的精度格式,但这样做的语法看起来也有些问题。你应该先计算出 clkPeriod,然后再格式化它。

这里是修改后的代码片段:

foreach clk $clk_list {set clkName [lindex $clk 0]set targetFreq [lindex $clk 1]set uncSynth [lindex $clk 4]set clkPeriod [expr {1.0 / $targetFreq}]set clkPeriod [format "%.3f" $clkPeriod]....

}

请注意,我在 expr 命令内使用了 {} 来确保变量 targetFreq 能正确展开,以及在计算 clkPeriod 后又使用了 format 命令来控制精度。这样,代码就应该能够正确运行,而不会遇到你提到的错误了。

我

在Cadence Genus中,出现如下错误该如何解决:error:option missing for SDC command. [SDC-203] [set_clock_uncertainty].

ChatGPT

在Cadence Genus中,遇到错误 “error:option missing for SDC command. [SDC-203] [set_clock_uncertainty]”,通常意味着SDC命令 set_clock_uncertainty 缺少了必要的参数或选项。在SDC(Synopsys Design Constraints)中设置时钟不确定性是为了在时序分析中考虑时钟信号之间的变化和偏差,这通常包括时钟偏斜和时钟抖动。

set_clock_uncertainty 命令通常需要至少两个参数:

- 不确定性的数值(如0.05表示50ps的不确定性)。

- 应用不确定性的时钟名称或者时钟对象。

命令的基本格式为:

set_clock_uncertainty <uncertainty_value> -from <source_clock> -to <destination_clock>

或者,如果不确定性值适用于时钟的所有路径,可以简写为:

set_clock_uncertainty <uncertainty_value> [get_clocks <clock_name>]

在你的具体情况下,这个错误可能是由于以下原因造成的:

- 未指定不确定性的数值。

- 没有指定

-from和/或-to选项以定义不确定性的来源和目的地时钟。 - 指定的时钟名字不存在或者不正确。

要解决这个问题,请检查你的 set_clock_uncertainty 命令,并确保提供了所有必要的参数。例如:

set_clock_uncertainty 0.05 -from clk1 -to clk2

上述命令为从 clk1 到 clk2 的时钟路径设置了50ps的不确定性。

如果你打算为同一时钟的所有路径设置不确定性,应该这样写:

set_clock_uncertainty 0.05 [get_clocks my_clock]

上述命令为 my_clock 时钟的所有路径设置了50ps的不确定性。

检查你的代码和上下文,确认你在使用此命令时提供了正确的参数和格式。如果问题仍然存在,你可能需要查看Genus的用户手册或寻求Cadence的技术支持以获取进一步的帮助。

我

在Cadence Genus中,tcl为:redirect -append ./acd.sdc { puts “set_clock_uncertainty 0.05 -setup [get_clocks $clkName]”},为什么在adc.sdc中却只添加了“set_clock_uncertainty 0.05 -setup ”字符串,而[get_clocks $clkName]没有添加进去。

ChatGPT

在你的 TCL 脚本中使用 redirect 命令来将输出重定向到 acd.sdc 文件,并且使用 puts 命令来将字符串写入该文件。问题出现在 puts 命令并不直接评估方括号内的 TCL 表达式。

这里有一个重要的点需要注意:redirect 命令捕获的是命令的输出,而不是对命令的求值。由于 [get_clocks $clkName] 在 puts 语句中是作为字符串传递的,所以 redirect 没有对其求值,因此 acd.sdc 文件中只写入了未经评估的字符串。

要解决这个问题,你需要在将字符串传递到 puts 之前先评估 [get_clocks $clkName]。这通常是通过将命令放在 set 中来完成,如下所示:

# 先求值 [get_clocks $clkName] 并将结果保存在变量中

set clocks [get_clocks $clkName]# 然后将完整的命令字符串包括求值的结果传递给 redirect 命令

redirect -append ./acd.sdc {puts "set_clock_uncertainty 0.05 -setup $clocks"

}

现在,[get_clocks $clkName] 会在 puts 命令执行之前被评估,输出的字符串会包括实际的时钟名称。

确保 $clkName 变量在你调用 get_clocks 命令之前已经被正确的设置,并且对应的时钟确实存在于设计中,否则 get_clocks 命令可能会返回空值或者错误。

我

仍然出现warning,could not find requested search value. [SDC-208] [get_clock]. the ‘get_clocks’ command cannot find any clocks named ‘LSI_CK’

ChatGPT

出现这个警告 “could not find requested search value. [SDC-208] [get_clock]. the ‘get_clocks’ command cannot find any clocks named ‘LSI_CK’” 通常意味着在设计中不存在名为 ‘LSI_CK’ 的时钟。这可能有几个原因:

- 时钟的名字有误。

- 时钟还没有被创建或者定义。

- 时钟名字的大小写不匹配(Tcl 是区分大小写的)。

- 在执行

get_clocks命令时,所提供的时钟名字变量clkName未被正确地赋值为 ‘LSI_CK’。

首先,请确认 ‘LSI_CK’ 是否是正确的时钟名称,以及它是否已经在设计当中被定义。你可以在 Genus 运行前或者相关的 SDC 文件中查找时钟定义的命令,通常是 create_clock。

如果时钟名字和大小写都没有问题,确认在你调用 get_clocks 之前 clkName 变量是否被正确设置。你可以通过打印 clkName 变量来检查它的值:

puts "clkName = $clkName"

如果变量值是正确的,并且确实存在一个相对应的时钟定义,那么 get_clocks 应该能找到时钟。如果没有找到,证明时钟可能根本就没有被定义。

在你的 TCL 脚本中,确保在执行任何依赖于时钟名的操作之前,先定义时钟。例如:

# 定义时钟

create_clock -name LSI_CK -period 10 [get_ports clk_port_name]# ... 其他设计步骤 ...# 然后设置时钟的不确定性

set clkName LSI_CK

set clocks [get_clocks $clkName]if {$clocks != ""} {redirect -append ./acd.sdc {puts "set_clock_uncertainty 0.05 -setup $clocks"}

} else {puts "Warning: Clock $clkName is not defined in the design."

}

上面的脚本段落首先定义了一个时钟,然后检查该时钟是否存在,如果存在就设置不确定性,并将其写入 acd.sdc 文件中。如果时钟不存在,它会打印一条警告信息。

我

在Cadence Genus中,tcl代码为:foreach clk $clk_list{

set clkName [lindex $clk 0]

set targetFreq [lindex $clk 1]

set uncSynth [lindex $clk 4]

set clkPeriod [lindex “%.3f” [expr 1 / $targetFreq]]

…

}

以上代码我有以下疑问:clk_list该如何设置,clkName 是IC_chip中的时钟pin脚还是CUCK模块中的输出接口?

ChatGPT

在 Cadence Genus 和类似的EDA(电子设计自动化)工具中,TCL 脚本被广泛用来自动化设计流程。在你提供的这段 TCL 代码中,foreach 循环被用于迭代一个名为 clk_list 的列表,从中提取每个时钟的信息,并对其进行处理。下面是你的疑问的一些澄清:

-

clk_list的设置:

clk_list应该是一个嵌套列表,其中每个子列表包含特定时钟的信息。子列表中的条目可能包括时钟的名称、目标频率、合成时的不确定性和其他相关参数。例如:set clk_list {{CLK1 100MHz 0.05ns} ;# 时钟名,目标频率,合成时的不确定性{CLK2 200MHz 0.04ns}{CLK3 300MHz 0.03ns}... }在这个例子中,

CLK1、CLK2和CLK3是时钟的名字,100MHz、200MHz和300MHz是它们的目标频率。 -

clkName的含义:

clkName是指列表中提取的当前时钟的名字。这个名字可以指代 IC 芯片中的实际时钟引脚或是设计中的一个逻辑信号,具体取决于设计中的时钟网络结构。在执行 TCL 脚本时,clkName可能代表:- 一个时钟源的引脚名称(例如,与 IC 芯片的物理时钟引脚相关联)。

- 一个时钟域的名称(例如,芯片中的某个模块或单元输出的时钟信号)。

在使用

get_clocks命令时,你需要确保提供的clkName是已经在设计中定义的时钟。通常,这个定义是通过create_clock命令提前完成的,而clkName应该与create_clock命令中定义的名字相匹配。

在你的设计中,你可能需要根据实际的情况来指定 clk_list。如果设计中包含多个时钟源,你需要按照设计的要求来配置每个时钟的参数。一旦 clk_list 被正确配置,你的 TCL 脚本将能迭代这个列表,并对每个时钟进行相应的操作。

我

如何提前在genus中create_clock,在genus进行综合的哪一步进行设定

ChatGPT

在 Cadence Genus 进行综合的过程中,create_clock 命令用于定义时钟源,这是设置设计约束的一个重要步骤。定义时钟源通常在综合流程的初期进行,确保在进行任何时序分析或优化之前,所有的时钟定义都已经到位。以下是如何在 Genus 综合流程中提前设置 create_clock 的简要指南:

1. 环境准备

确保你已经正确设置了 Genus 的环境,并且你有一个有效的设计(Verilog/VHDL 文件等)以及一个设计约束文件(通常是 SDC 格式文件)。

2. 创建 SDC 文件

在 SDC 文件中,你可以使用 create_clock 命令来定义时钟。SDC 文件是一种标准的设计约束格式,广泛用于指导综合和布局布线(P&R)工具。例如:

# 创建一个名为 CLK 的时钟,周期为 10ns

create_clock -name CLK -period 10 [get_ports clk_pin_name]

这里,[get_ports clk_pin_name] 指定了时钟信号的源端口,-period 10 定义了时钟周期为 10ns。

3. 在 Genus 中应用 SDC 约束

在启动 Genus 并读入你的设计后,你需要将 SDC 约束文件应用到当前设计。这可以通过在 Genus 的 TCL 控制台中运行以下命令完成:

read_sdc your_constraints.sdc

确保替换 your_constraints.sdc 为你的 SDC 文件的实际路径和名称。

4. 执行综合

一旦 SDC 文件被读取,你的设计约束(包括所有时钟定义)将应用于当前设计。此时,你可以继续在 Genus 中执行综合流程,如:

synthesize -to_mapped

或者使用其他相关命令,取决于你的具体需求和综合目标。

重要注意事项

- 早期定义时钟:通常,在综合流程的早期阶段定义时钟是很重要的,这样可以确保所有时序相关的优化和分析都能考虑到正确的时钟信息。

- 检查和调试:在综合之后,使用

report_timing和report_clocks等命令来验证时钟是否如你所预期的那样被正确定义和识别。 - 灵活性:在实际的项目中,可能需要根据综合结果和时序分析反馈来调整时钟定义或其他设计约束。

通过遵循上述步骤,你可以确保你的设计在 Cadence Genus 综合过程中具有正确的时钟定义,为达到设计目标和性能要求奠定基础。

我

在Cadence Genus中,加载sdc文件后,出现如下Error:A required object parameter could not be found. [TUI-61] [parse_options]. An object of type ‘port | pin’ name ‘’ could not be found.

ChatGPT

这个错误信息表明,在尝试加载 SDC (Synopsys Design Constraints) 文件时,Genus 在解析文件中的一条或多条指令时遇到了问题。具体来说,错误表明在某处需要一个类型为 ‘port | pin’ 的对象,但却找不到对应的对象名。这通常发生在使用了指向不存在的端口或引脚的约束命令时。以下是一些解决这个问题的建议步骤:

1. 检查 SDC 文件中的端口或引脚名称

- 确保 SDC 文件中引用的所有端口(

get_ports)或引脚(get_pins)名称与你的设计中实际的端口和引脚名称完全匹配。任何拼写错误或大小写不匹配都可能导致这个错误。 - 如果你的设计中更改了端口或引脚的名称,确保这些更改同样反映在 SDC 文件中。

2. 验证设计是否已正确读入

- 确保在尝试加载 SDC 文件前,你的设计已经被成功地读入到 Genus 中。如果设计没有被正确读入或者只是部分读入,那么 SDC 文件中的端口或引脚可能无法被正确识别。

- 使用 Genus 的 TCL 命令,如

report_design,来验证设计是否完整。

3. 使用报告命令识别问题

- 在 Genus 中,使用

report_ports命令来列出所有已识别的端口,检查是否所有预期的端口都已列出。 - 类似地,

report_pins可用于查看特定实例的引脚情况。

4. 分步加载 SDC 文件

- 如果 SDC 文件较大或包含多个复杂的约束,尝试分步加载 SDC 文件的不同部分,可以帮助你确定问题发生的确切位置。

- 将 SDC 文件分成几个部分,并逐一加载这些部分,直到发现导致错误的具体指令。

5. 检查 SDC 文件的结构和格式

- 确保 SDC 文件的语法正确。例如,使用

create_clock命令时,应确保所有必要的参数都已正确指定。 - 考虑使用文本编辑器的高亮功能或专用的 SDC 检查工具来帮助识别潜在的语法问题。

如果在完成这些步骤后问题仍然存在,可能需要更深入地检查设计文件和 SDC 文件,或者寻求来自 Cadence 支持社区或者是你所在组织的 CAD 工程师的帮助。

我

在Cadence Genus中,sdc文件中的get_ports和get_pins后面应该接什么形式的东西,请举例

ChatGPT

在 Cadence Genus 使用的 SDC (Synopsys Design Constraints) 文件中,get_ports 和 get_pins 命令用于选择特定的端口或引脚。这些命令后面应该接端口或引脚的名称,可以是单个名称,也可以是一个名称的列表,或者是匹配某种模式的通配符表达式。下面是一些例子:

使用 get_ports

- 选择单个端口:

get_ports clk

这里 clk 是端口的名称,此命令会选择名为 clk 的端口。

- 选择多个端口:

get_ports {clk rst button}

这里选择了三个端口:clk、rst 和 button。

- 使用通配符选择端口:

get_ports data*

这个命令会选择所有以 data 开头的端口。

- 使用正则表达式选择端口:

get_ports -regexp {^data[0-9]+$}

这里使用正则表达式选择所有以 data 开始,后面紧跟一组数字,并以这组数字结束的端口名称。

使用 get_pins

- 选择单个引脚:

get_pins U1/D

这里 U1 是实例的名称,D 是该实例上引脚的名称,此命令会选择 U1 实例上名为 D 的引脚。

- 选择多个引脚:

get_pins {U1/D U2/CLK U3/Q}

这里选择了三个引脚:U1 上的 D、U2 上的 CLK 和 U3 上的 Q。

- 使用通配符选择引脚:

get_pins U1/data*

这个命令会选择 U1 实例上所有以 data 开头的引脚。

- 选择特定类型的所有引脚(比如所有的输出引脚):

get_pins -filter {direction == "output"}

这里使用 -filter 选项来选择所有方向为输出的引脚。

在实际使用中,为了避免出错,你需要确保 SDC 文件中的端口和引脚名称与你的设计中定义的名称完全一致。任何不匹配都可以导致错误,这就是为什么你之前遇到了 A required object parameter could not be found 的错误。所以,在编写或修改 SDC 文件时,严格核对名称是非常关键的。

我

在Cadence Genus中,设置‘lp_insert_discretr_clock_gating_logic’root attribute 为true 和 false,有什么区别

ChatGPT

在 Cadence Genus 中,lp_insert_discrete_clock_gating_logic 是一个 root attribute,用于控制是否在综合过程中自动插入离散的时钟门控逻辑。通过设置这个属性,你可以影响设计的功耗优化策略,尤其是与时钟网络的功耗相关的部分。

-

当设置为

true时,Genus 会在综合过程中检测可以优化的时钟使能条件,并自动插入离散的时钟门控逻辑。这种方式可以减少时钟网络上的切换活动,从而减少整个设计的动态功耗。这对于功耗敏感的设计非常有用,因为它可以帮助实现更低的能耗。 -

当设置为

false时,Genus 不会自动插入离散的时钟门控逻辑。这意味着如果你的设计中需要时钟门控,你需要手动实现它,或依赖于设计中已经存在的门控逻辑。这个选项可能适用于那些对时钟门控有特定要求的设计,或者当设计者希望完全控制门控逻辑的实现方式时。

总的来说,这个属性的设置取决于你对设计的功耗优化要求。如果减少功耗是一个重要考虑,那么将此属性设置为 true 可能是一个好选择。然而,如果你需要更精细的控制或者对自动插入的门控逻辑有疑虑,那么保持它为 false 并手动管理时钟门控可能更适合你的需求。

请注意,在实际操作中,你可能还需要考虑其他 root attribute 和综合策略,以及它们如何相互影响,以达到最佳的功耗和性能平衡。在某些情况下,还需要进行多次迭代和综合,以及在后续的门级仿真中验证插入的时钟门控逻辑是否符合功能和时序要求。

我

数字ic设计中,.lef文件和.def文件的区别

ChatGPT

在数字集成电路设计流程中,.LEF(Library Exchange Format)文件和.DEF(Design Exchange Format)文件都发挥着重要角色。它们分别代表了不同的设计抽象级别,并被用于不同的设计阶段。下面是它们的主要区别:

.LEF 文件

-

LEF 是什么?

LEF 文件是一种用于在不同设计工具和数据库之间交换物理层级数据的格式。它通常包含了库单元(标准单元、宏单元、IP块等)的物理信息。 -

LEF 文件包含什么?

LEF 文件主要提供了单元的层次结构、外形尺寸、层信息、引脚位置、电源和地线分布等信息,但不包含具体的晶体管级细节或电路逻辑。 -

LEF 文件的用途:

LEF 文件用于布局阶段,它允许不同的设计团队在不暴露电气细节的情况下共享单元布局信息。这种格式可以用来执行布局规划、布局验证和芯片组装。

.DEF 文件

-

DEF 是什么?

DEF 文件是一个设计阶段的文件,它描述了特定芯片设计的布局信息。 -

DEF 文件包含什么?

DEF 文件包含实例放置位置、网线布线信息、设计的层次结构、版图区域、电源和地线布局、I/O位置等信息。 -

DEF 文件的用途:

DEF 文件通常用来在布局工具和布线工具之间传递信息,它包含了构建物理芯片所需的几乎所有信息,但不包括标准单元和宏单元的内部结构。

区别总结:

-

抽象级别不同:

LEF 是更高一级的抽象,提供单元的外部视图;DEF 是更加具体,描述了整个芯片的物理实现,包括所有单元的精确位置和布线。 -

信息内容不同:

LEF 关注单元的物理特性和接口定义;DEF 关注整个设计的物理布局,包括所有LEF中描述的单元如何在芯片上布局和互连。 -

使用阶段不同:

LEF 文件在芯片设计的早期被使用,主要用于库单元的布局规划;DEF 文件在设计流程的后期被使用,用于详细的版图布局和布线。

两者通常需要结合起来使用,LEF 文件为 DEF 文件提供了必要的单元信息,使得布局布线工具可以正确放置单元并进行互连布线,从而完成芯片的物理设计。

我

在Cadence Genus中,出现如下错误该如何解决:Error:linking to physical only cell only where timing library is absent. Paths that involve these cells are not timed.[CDFG-814]

ChatGPT

当在 Cadence Genus 综合工具中出现错误 “Error: linking to physical only cell only where timing library is absent. Paths that involve these cells are not timed. [CDFG-814]” 时,这通常表示设计中使用了一个仅具有物理信息但缺少时序信息的库单元。在综合过程中,Genus 需要这些时序信息来对路径进行时序分析和优化。

要解决这个错误,你可以采取以下步骤:

-

核实库文件:

确保你加载了包含所需时序信息的库文件。通常,这意味着需要一个有完整时序数据的.lib文件。检查你的搜索路径(search path)和库路径(library path)设置,确保 Genus 可以访问正确的标准单元库。 -

更新库文件路径:

如果库文件路径设置不正确,或者所引用的库文件不包含必要的时序信息,你需要更新你的库文件路径,以确保 Genus 可以找到并使用具有完整时序数据的库文件。 -

检查单元映射:

如果你在设计中使用了自定义单元或者第三方IP,确保这些单元已经正确地映射到了具有相应时序信息的标准库单元。在某些情况下,可能需要提供额外的映射文件来辅助这一过程。 -

联系库提供商:

如果问题出现在第三方提供的库单元,可以联系库提供商来获取具有时序信息的正确库文件。 -

检查综合脚本:

在你的综合脚本中,确保所有的库文件都已经被正确指定,没有遗漏,且顺序正确。一些综合脚本需要在特定的顺序中指定不同类型的库文件。 -

查看日志和报告:

详细审查 Genus 生成的日志文件和报告,有时候它们可以提供更多关于错误发生原因的线索。 -

清理工作目录:

有时候,之前的综合尝试可能会留下一些状态文件,这些文件可能会干扰新的综合尝试。清理或者重命名工作目录后重新综合可能有助于解决问题。 -

使用命令行选项:

一些情况下,Genus 的命令行选项可以用来指定对待缺少时序信息的单元的处理方式。查看 Genus 文档以获取可能的相关选项。

如果上述步骤都无法解决问题,可能需要与 Cadence 支持团队联系以获取更专业的帮助。在联系支持前,准备好所有相关的信息,包括你的综合脚本、日志文件、错误信息、使用的库文件版本和其他任何可能有助于问题诊断的数据。

我

在Cadence Genus中,rc.derate.sdc 是什么文件,主要约束哪方面的东西,为什么在最后进行优化前才进行读取约束

ChatGPT

在 Cadence Genus 这类综合工具中,rc.derate.sdc 是一个特定的约束文件,其名称通常是用户定义的,并不是 Genus 固有的命名。.sdc 代表 Synopsys Design Constraints,这是一个用于表达设计约束的文件格式,由 Synopsys 定义,并被业界广泛采用。

sdc 文件包含了对设计进行时序分析和优化所需的约束信息,如时钟定义、IO时序要求、set-up/hold 修正、假路径(false path)、多周期路径(multicycle path)等。

rc 通常是缩写,可能代表了 “resistance-capacitance”,这在时序分析中用来表示信号路径的电阻和电容。derate 这个词指的是降额,这是一种安全系数应用,用以考虑实际工作条件下对于设备性能的影响,比如温度、电压变化等。

rc.derate.sdc 中的约束可能专门用于调整这些条件对时序的影响。例如,可以通过指定不同的操作条件(如温度、电压)下的降额因子来调整组件的延迟和转换时间。这些修正因子通常基于实际硅片的测试数据或者是为了在边界情况下保守设计。

为什么在最后进行优化前才读取这些约束?通常,设计流程中会首先进行初始的综合步骤,不涉及所有详细的环境和工艺变化。随着设计的逐步成熟,会逐步引入更多的细节并加紧优化,因此在最终优化阶段读取更为精确且细致的derate约束是有意义的。这样可以确保时序分析和优化考虑到了最坏情况下的设备性能变化,为芯片带来良好的健壮性。

在实际应用中,应当根据设计要求和工艺条件,仔细选择合适的时机来应用这些降额约束。过早地引入可能会导致不必要的保守设计,影响性能;而过晚引入可能会导致设计无法满足要求。因此,何时读取这些约束需要根据设计的特定需求和设计流程策略来确定。

相关文章:

【chatGPT】我:在Cadence Genus软件中,出现如下问题:......【4】

我 在Cadence Genus中,tcl代码为:foreach clk $clk_list{ set clkName [lindex $clk_list 0] set targetFreq [lindex $clk_list 1] set uncSynth [lindex $clk_list 4] set clkPeriod [lindex “%.3f” [expr 1 / $targetFreq]] … } 以上代码出现如下…...

在JAVA中的应用)

单例模式(Singleton Pattern)在JAVA中的应用

在软件开发中,设计模式是解决特定问题的一种模板或者指南。它们是在多年的软件开发实践中总结出的有效方法。JAVA设计模式广泛应用于各种编程场景中,以提高代码的可读性、可维护性和扩展性。本文将介绍单例模式,这是一种常用的创建型设计模式…...

手把手教你创建新的OpenHarmony 三方库

创建新的三方库 创建 OpenHarmony 三方库,建议使用 Deveco Studio,并添加 ohpm 工具的环境变量到 PATH 环境变量。 创建方法 1:IDE 界面创建 在现有应用工程中,新创建 Module,选择"Static Library"模板&a…...

从零开始,如何成功进入IT行业?

0基础如何进入IT行业? 简介:对于没有任何相关背景知识的人来说,如何才能成功进入IT行业?是否有一些特定的方法或技巧可以帮助他们实现这一目标? 在当今数字化时代,IT行业无疑是一个充满活力和机遇的领域。…...

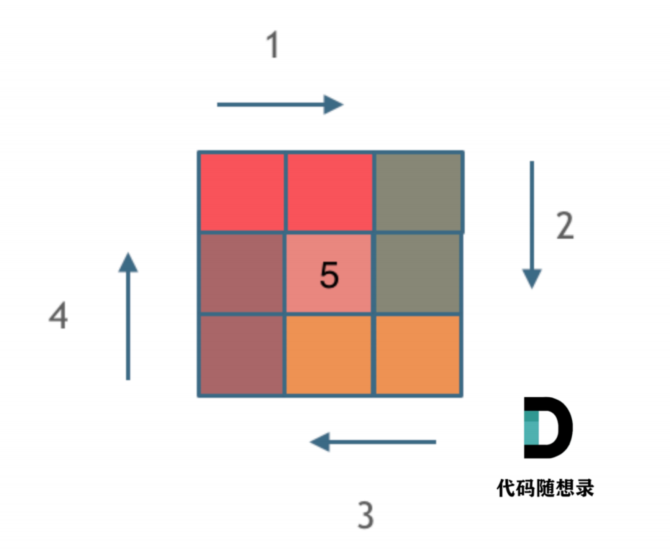

【数组】5螺旋矩阵

这里写自定义目录标题 一、题目二、解题精髓-循环不变量三、代码 一、题目 给定⼀个正整数 n,⽣成⼀个包含 1 到 n^2 所有元素,且元素按顺时针顺序螺旋排列的正⽅形矩阵。 示例: 输⼊: 3 输出: [ [ 1, 2, 3 ], [ 8, 9, 4 ], [ 7, 6, 5 ] ] 二、解题精髓…...

Sora视频生成模型:开启视频创作新纪元

随着人工智能技术的飞速发展,视频生成领域也迎来了前所未有的变革。Sora视频生成模型作为这一领域的佼佼者,凭借其卓越的性能和创新的应用场景,受到了广泛的关注与好评。本文将对Sora视频生成模型进行详细介绍,带您领略其魅力所在…...

OpenAI现已普遍提供带有视觉应用程序接口的GPT-4 Turbo

OpenAI宣布,其功能强大的GPT-4 Turbo with Vision模型现已通过公司的API全面推出,为企业和开发人员将高级语言和视觉功能集成到其应用程序中开辟了新的机会。 PS:使用Wildcard享受不受网络限制的API调用,详情查看教程 继去年 9 月…...

Swift中的元组属性

在Swift中,元组属性指的是一个元组作为结构体、类或枚举的属性。可以将一个元组作为属性来存储和访问多个值。 例如,考虑以下的Person类: class Person {var name: Stringvar age: Intvar address: (String, Int)init(name: String, age: I…...

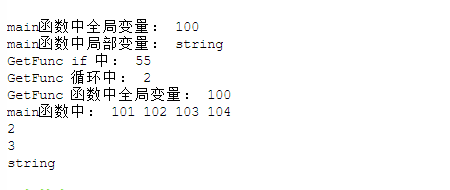

【go从入门到精通】作用域,包详解

作者简介: 高科,先后在 IBM PlatformComputing从事网格计算,淘米网,网易从事游戏服务器开发,拥有丰富的C,go等语言开发经验,mysql,mongo,redis等数据库,设计模…...

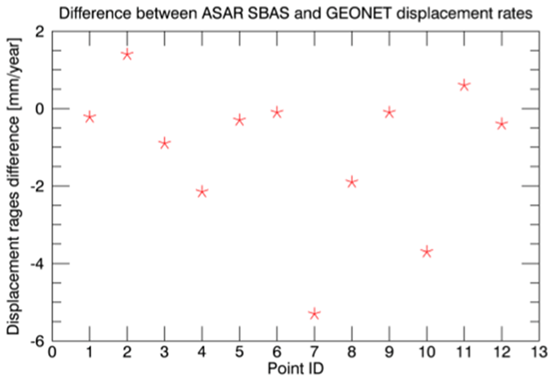

利用SARscape对日本填海造陆和天然气开采进行地表形变监测

日本千叶市,是日本南部重要的工业港市。位于西部的浦安市是一个典型的"填海造田"城市,东南部的东金区有一片天然气开采区域,本文利用SARscape,用干涉叠加的方法,即PS和SBAS,对这两个区域进行地表…...

“Python爬虫实战:高效获取网上公开美图“

如何通过Python创建一个简单的网络爬虫,以爬取网上的公开图片。网络爬虫是一种自动化工具,能够浏览互联网、下载内容并进行处理。请注意,爬取内容时应遵守相关网站的使用条款,尊重版权和隐私权。 ### 网络爬虫简介 网络爬虫&…...

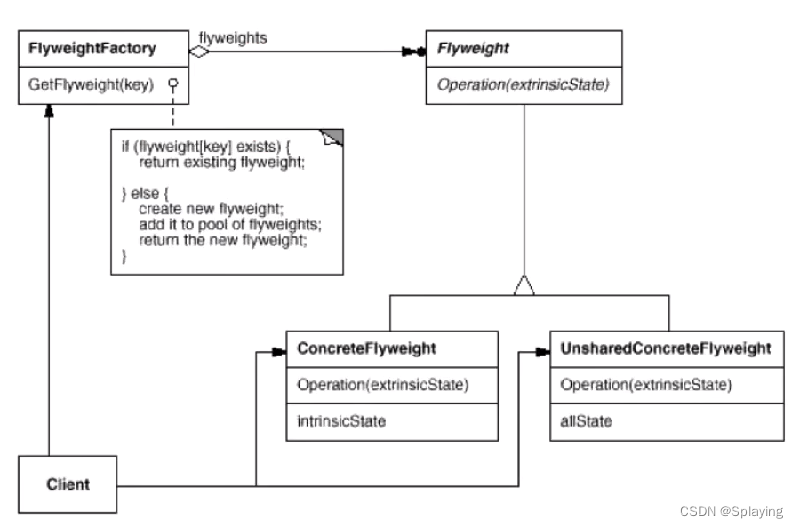

C++设计模式:享元模式(十一)

1、定义与动机 概述:享元模式和单例模式一样,都是为了解决程序的性能问题。面向对象很好地解决了"抽象"的问题,但是必不可免得要付出一定的代价。对于通常情况来讲,面向对象的成本大豆可以忽略不计。但是某些情况&#…...

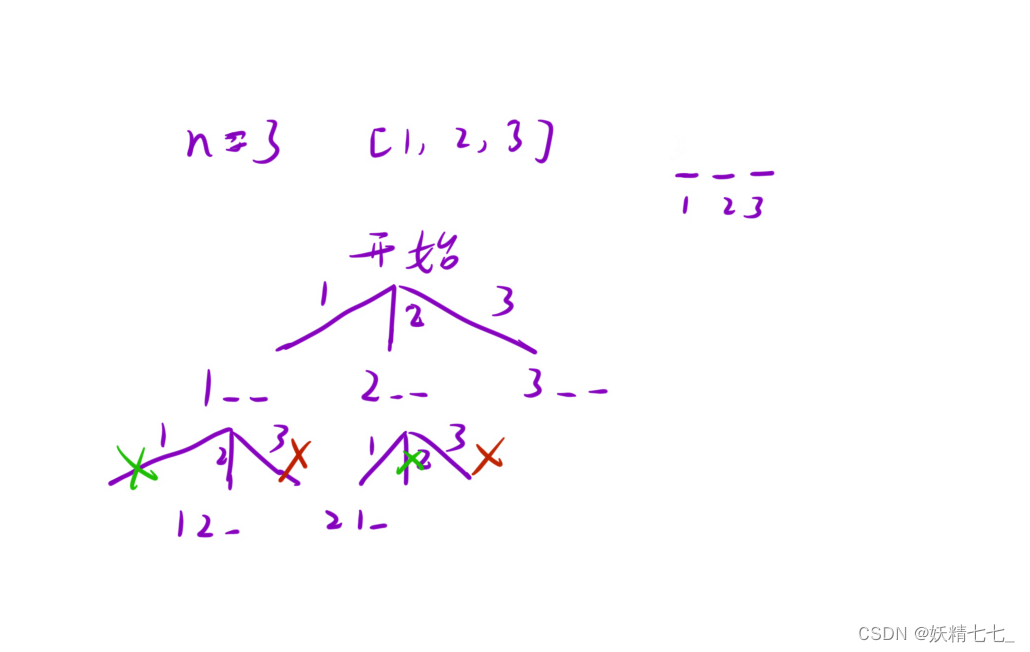

【三十六】【算法分析与设计】综合练习(3),39. 组合总和,784. 字母大小写全排列,526. 优美的排列

目录 39. 组合总和 对每一个位置进行枚举 枚举每一个数出现的次数 784. 字母大小写全排列 526. 优美的排列 结尾 39. 组合总和 给你一个 无重复元素 的整数数组 candidates 和一个目标整数 target ,找出 candidates 中可以使数字和为目标数 target 的 所有 不…...

——架构简介)

ARM Cordio WSF(一)——架构简介

1. 关于WSF WSF(wireless Software Foundation API),是一个RTOS抽象层。Wireless Software Foundation software service and porting layer,提供实时操作系统所需的基础服务,可基于不同平台进行实现,移植…...

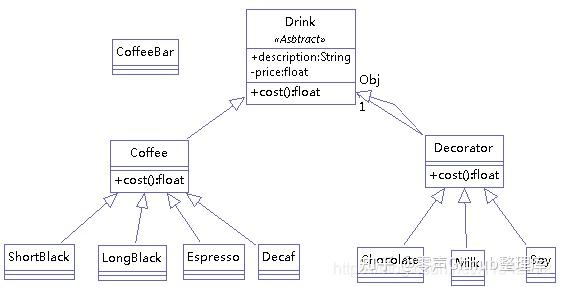

设计模式总结-装饰者模式

模式动机 一般有两种方式可以实现给一个类或对象增加行为: 继承机制,使用继承机制是给现有类添加功能的一种有效途径,通过继承一个现有类可以使得子类在拥有自身方法的同时还拥有父类的方法。但是这种方法是静态的,用户不能控制增…...

Stunnel网络加密服务

简介: Stunnel是一个用于创建SSL加密隧道的工具,针对本身无法进行TLS或SSL通信的客户端及服务器,Stunnel 可提供安全的加密连接。可以用于保护服务器之间的通信。您可以在每台服务器上安装Stunnel,并将其配置为在公网上加密传输数…...

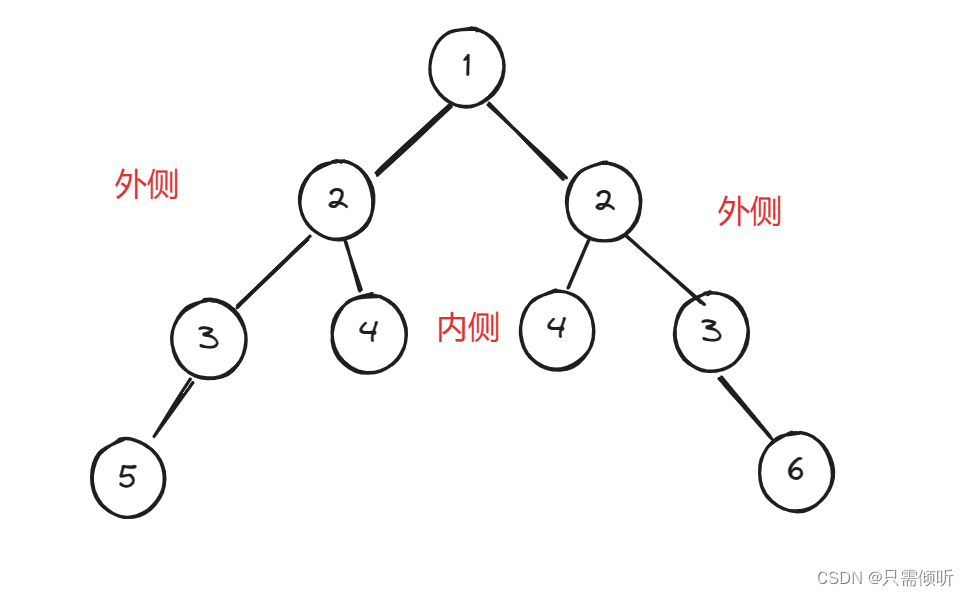

算法练习第16天|101. 对称二叉树

101. 对称二叉树 力扣链接https://leetcode.cn/problems/symmetric-tree/description/ 题目描述: 给你一个二叉树的根节点 root , 检查它是否轴对称。 示例 1: 输入:root [1,2,2,3,4,4,3] 输出:true示例 2&#x…...

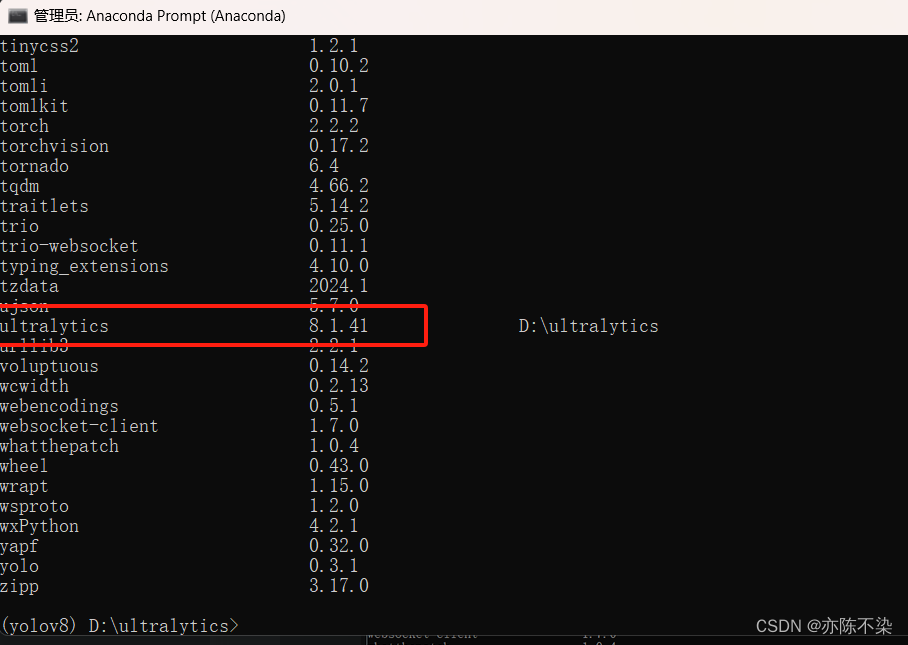

YOLOV8实战教程——最新安装(截至24.4)

前言:YOLOV8更新比较快,最近用的时候发现有些地方已经跟之前不一样,甚至安装都会出现差异,所以做一个最新版的 yolov8 安装教程 一、Github 或者 GitCode 搜索 ultralytics 下载源码包,下载后解压到你需要安装的位置…...

redis zremove删除不掉【bug】

redis zremove删除不掉【bug】 前言版权redis zremove删除不掉错误产生相关资源EldDataEchartsTestDataService 解决 最后 前言 2024-4-12 20:35:21 以下内容源自《【bug】》 仅供学习交流使用 版权 禁止其他平台发布时删除以下此话 本文首次发布于CSDN平台 作者是CSDN日星…...

对象的本地保存

对象的本地保存 对象的创建和保存 对象的特点: 对象“生活”在内存空间中,因此,程序一旦关闭,这些对象也都会被CLR的垃圾回收机制销毁。程序第二次运行时,对象会以“全新”的状态出现,无法保留上次对象的运行状态。…...

SkyWalking 10.2.0 SWCK 配置过程

SkyWalking 10.2.0 & SWCK 配置过程 skywalking oap-server & ui 使用Docker安装在K8S集群以外,K8S集群中的微服务使用initContainer按命名空间将skywalking-java-agent注入到业务容器中。 SWCK有整套的解决方案,全安装在K8S群集中。 具体可参…...

k8s从入门到放弃之Ingress七层负载

k8s从入门到放弃之Ingress七层负载 在Kubernetes(简称K8s)中,Ingress是一个API对象,它允许你定义如何从集群外部访问集群内部的服务。Ingress可以提供负载均衡、SSL终结和基于名称的虚拟主机等功能。通过Ingress,你可…...

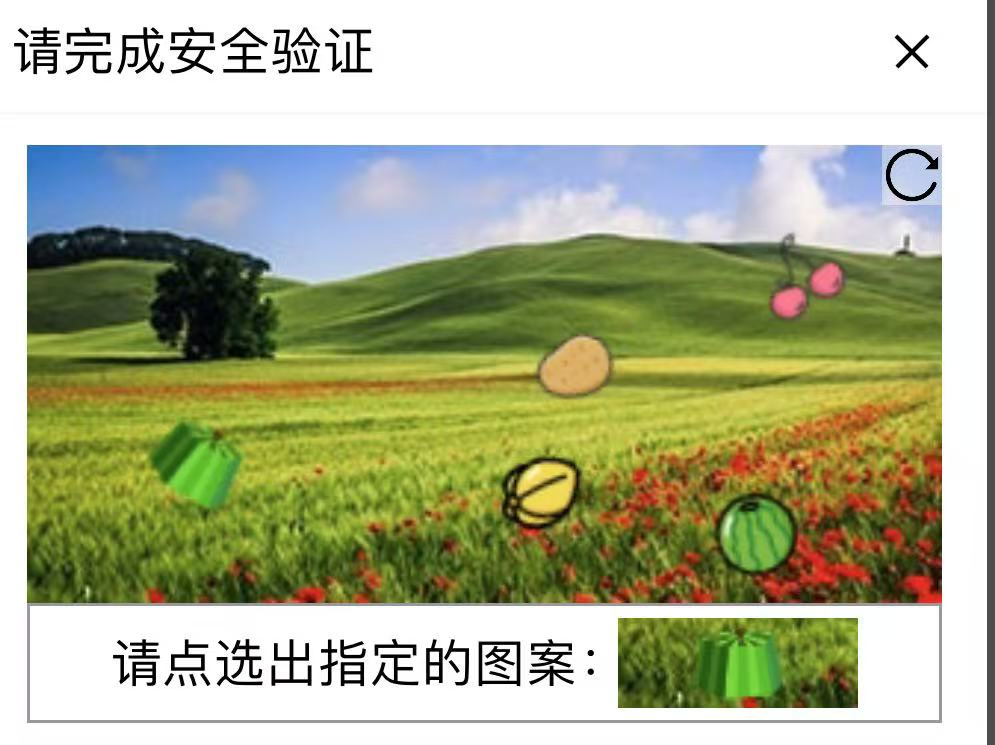

【配置 YOLOX 用于按目录分类的图片数据集】

现在的图标点选越来越多,如何一步解决,采用 YOLOX 目标检测模式则可以轻松解决 要在 YOLOX 中使用按目录分类的图片数据集(每个目录代表一个类别,目录下是该类别的所有图片),你需要进行以下配置步骤&#x…...

【JavaSE】绘图与事件入门学习笔记

-Java绘图坐标体系 坐标体系-介绍 坐标原点位于左上角,以像素为单位。 在Java坐标系中,第一个是x坐标,表示当前位置为水平方向,距离坐标原点x个像素;第二个是y坐标,表示当前位置为垂直方向,距离坐标原点y个像素。 坐标体系-像素 …...

)

C#学习第29天:表达式树(Expression Trees)

目录 什么是表达式树? 核心概念 1.表达式树的构建 2. 表达式树与Lambda表达式 3.解析和访问表达式树 4.动态条件查询 表达式树的优势 1.动态构建查询 2.LINQ 提供程序支持: 3.性能优化 4.元数据处理 5.代码转换和重写 适用场景 代码复杂性…...

Cilium动手实验室: 精通之旅---13.Cilium LoadBalancer IPAM and L2 Service Announcement

Cilium动手实验室: 精通之旅---13.Cilium LoadBalancer IPAM and L2 Service Announcement 1. LAB环境2. L2公告策略2.1 部署Death Star2.2 访问服务2.3 部署L2公告策略2.4 服务宣告 3. 可视化 ARP 流量3.1 部署新服务3.2 准备可视化3.3 再次请求 4. 自动IPAM4.1 IPAM Pool4.2 …...

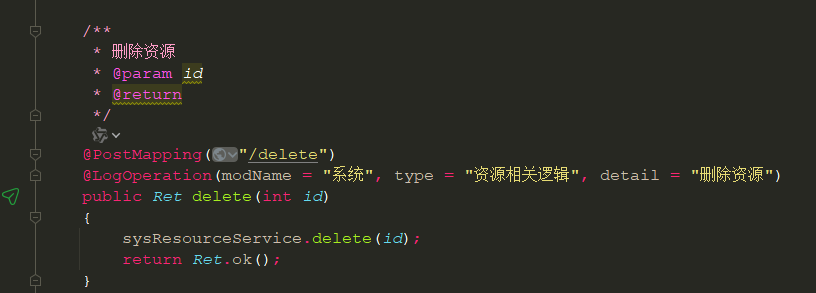

springboot 日志类切面,接口成功记录日志,失败不记录

springboot 日志类切面,接口成功记录日志,失败不记录 自定义一个注解方法 import java.lang.annotation.ElementType; import java.lang.annotation.Retention; import java.lang.annotation.RetentionPolicy; import java.lang.annotation.Target;/***…...

【FTP】ftp文件传输会丢包吗?批量几百个文件传输,有一些文件没有传输完整,如何解决?

FTP(File Transfer Protocol)本身是一个基于 TCP 的协议,理论上不会丢包。但 FTP 文件传输过程中仍可能出现文件不完整、丢失或损坏的情况,主要原因包括: ✅ 一、FTP传输可能“丢包”或文件不完整的原因 原因描述网络…...

Matlab实现任意伪彩色图像可视化显示

Matlab实现任意伪彩色图像可视化显示 1、灰度原始图像2、RGB彩色原始图像 在科研研究中,如何展示好看的实验结果图像非常重要!!! 1、灰度原始图像 灰度图像每个像素点只有一个数值,代表该点的亮度(或…...

SQL进阶之旅 Day 22:批处理与游标优化

【SQL进阶之旅 Day 22】批处理与游标优化 文章简述(300字左右) 在数据库开发中,面对大量数据的处理任务时,单条SQL语句往往无法满足性能需求。本篇文章聚焦“批处理与游标优化”,深入探讨如何通过批量操作和游标技术提…...