详解UART通信协议以及FPGA实现

文章目录

- 一、UART概述

- 二、UART协议帧格式

- 2.1 波特率

- 2.2 奇校验ODD

- 2.3 偶校验EVEN

- 三、UART接收器设计

- 3.1 接收时序图

- 3.2 Verilog代码

- 3.3 仿真文件测试

- 3.4 仿真结果

- 3.5 上版测试

- 四、UART发送器设计

- 4.1 发送时序图

- 4.2 Verilog代码

- 4.3 仿真文件测试

- 4.4 仿真结果

- 4.5 上板测试

- 五、UART回环测试

- 5.1 系统框图

- 5.2 Verilog代码

- 5.3 仿真文件测试

- 5.4 仿真结果

- 5.5 上板测试

- 六、参考

一、UART概述

从《浅谈UART,TTL,RS-232,RS-485的区别》这篇文章,我们知道了UART是一种串行、异步、全双工的通信协议,属于协议层;传输过程一般采用RS-232,RS-485电平标准,将所需传输的数据一位接一位地传输;整体传输框架如下:

串口通信由发送端和接收端构成,两根信号线实现,一根数据发送,一根数据接收。

二、UART协议帧格式

在串口通信过程中,数据接收与发送双方没有共享时钟,因此,双方必须协商好数据传输波特率。根据双方协议好的波特率,接收端即可对发送端的数据进行采样。整个传输流程如下:

- 传输线空闲时为高电平,然后拉低一个码元时间表示起始位

- 接着传输 8 个数据位,先传输低位,再传输高位

- 然后传输一个校验位,用来检测本次传输的数据是否正确

- 最后输出高电平表示停止位,可以是 1 位、1.5 位、2 位的高电平,并且进入空闲状态,等待下一次的数据传输

协议帧格式如下:

2.1 波特率

根据双方协议好的传输速率,接收端即可对发送端的数据进行采样。如果波特率为 9600也就是相当于每秒中划分成了 9600 等份的码元时间。常见的波特率标准为 300bps,600bps,800bps,9600bps,19200bps,38400bps,115200bps 等。通常对串口进行数据采样,采用更高频的时钟。

一个码元的计算方法:例如我们采样时钟为 50M ,所使用的波特率为 115200,传输 1个码元需要的时间( 1 / 115200 ) = 8680ns

2.2 奇校验ODD

使完整编码(有效位和校验位)中的 “1” 的个数为奇数个。如果原来信息中 1 的个数为奇数个,则校验位为 0,这样所有信息中1的个数还是奇数 ;如果原来信息中 1 的个数为偶数个,则校验位为 1,这样所有信息中1的个数还是奇数。

常见的串口通信格式是(8 位数据位+1 位奇数校验位)。以发送字符:10010101和11010101 为例

| 数据第0位 | 数据第1位 | 数据第2位 | 数据第3位 | 数据第4位 | 数据第5位 | 数据第6位 | 数据第7位 | 校验位 |

|---|---|---|---|---|---|---|---|---|

| 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 1 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 0 |

2.3 偶校验EVEN

使完整编码(有效位和校验位)中的 “1” 的个数为偶数个。如果原来信息中 1 的个数为奇数个,则校验位为 1,这样所有信息中1的个数还是偶数 ;如果原来信息中 1 的个数为偶数个,则校验位为 0,这样所有信息中1的个数还是偶数。

常见的串口通信格式是(8 位数据位+1 位奇数校验位)。以发送字符:10010101和11010101 为例

| 数据第0位 | 数据第1位 | 数据第2位 | 数据第3位 | 数据第4位 | 数据第5位 | 数据第6位 | 数据第7位 | 校验位 |

|---|---|---|---|---|---|---|---|---|

| 1 | 0 | 1 | 0 | 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 | 1 | 1 | 1 |

三、UART接收器设计

开发平台:vivado2021.1

开发芯片:xc7a100tfgg484-2

3.1 接收时序图

本次实现11500波特率,无奇偶校验位,时钟频率为50M,则每个码元计数次数为50000000/115200=434。时序图如下:

3.2 Verilog代码

`timescale 1ns/1ns

module uart_rx#

(parameter CLK_FREQ = 'd50_000_000, //时钟频率parameter UART_BPS = 'd115200 //波特率

)

(input clk , input rst_n , input rx , //uart_rxoutput reg [7:0] rx_data , //uart_rx_dataoutput reg rx_data_valid //uart_rx_data_valid

);localparam BAUD_CNT_MAX = CLK_FREQ/UART_BPS ;//一个码元的长度localparam BAUD_CNT_MAX_div2 = BAUD_CNT_MAX/2 ; reg rx_reg1 ;reg rx_reg2 ;reg rx_reg3 ;reg rx_flag ;reg [23:0] baud_cnt ;reg [3:0] bit_cnt ;reg bit_flag ;//打两拍,消除亚稳态

always @(posedge clk, negedge rst_n) beginif(rst_n == 1'b0)beginrx_reg1 <= 1'b1;rx_reg2 <= 1'b1;endelse beginrx_reg1 <= rx;rx_reg2 <= rx_reg1;end

end//再打一拍用于判断RX下降沿

always @(posedge clk, negedge rst_n) beginif(rst_n == 1'b0)rx_reg3 <= 1'b1;elserx_reg3 <= rx_reg2;end//接收范围

always @(posedge clk, negedge rst_n) beginif(rst_n == 1'b0)rx_flag <= 1'b0;else if (rx_reg3 == 1'b1 && rx_reg2 == 1'b0)rx_flag <= 1'b1;else if(bit_cnt == 'd8 && bit_flag ==1'b1)rx_flag <= 1'b0;elserx_flag <= rx_flag;

end//baud_cnt:波特率计数器计数,从 0 计数到 BAUD_CNT_MAX

always @(posedge clk, negedge rst_n) beginif(rst_n == 1'b0)baud_cnt <= 'd0;else if(baud_cnt == BAUD_CNT_MAX || rx_flag == 1'b0)baud_cnt <= 'd0;else if(rx_flag == 1'b1)baud_cnt <= baud_cnt + 1'b1;elsebaud_cnt <= baud_cnt;

end//bit_flag: baud_cnt 计数器计数到码元中间,时采样的数据最稳定

always @(posedge clk, negedge rst_n) beginif(rst_n == 1'b0)bit_flag <= 1'b0;else if(baud_cnt == BAUD_CNT_MAX_div2)bit_flag <= 1'b1;elsebit_flag <= 1'b0;end//bit_cnt:有效数据计数器, 8 个有效数据(不含起始位和停止位)

always @(posedge clk, negedge rst_n) beginif(rst_n == 1'b0)bit_cnt <= 'd0;else if(bit_cnt == 'd8 && bit_flag == 1'b1)bit_cnt <= 'd0;else if(bit_flag == 1'b1)bit_cnt <= bit_cnt + 1'b1;elsebit_cnt <= bit_cnt;

end//输出数据

always @(posedge clk, negedge rst_n) beginif(rst_n == 1'b0)rx_data <= 'd0;else if(bit_cnt >= 'd1 && bit_flag == 1'b1)rx_data <= {rx_reg3,rx_data [7:1]};elserx_data <= rx_data ;

end//输出数据有效信号,当接受完8个数据位后拉高

always @(posedge clk, negedge rst_n) beginif(rst_n == 1'b0)rx_data_valid <= 1'b0;else if(bit_cnt == 'd8 && bit_flag == 1'b1)rx_data_valid <= 1'b1;elserx_data_valid <= 1'b0;

endendmodule

3.3 仿真文件测试

这次仿真文件使用task任务来模拟uart发送数据

`timescale 1ns/1ns

module tb_uart_rx();reg clk ;reg rst_n ;reg rx ;wire [7:0] rx_data ;wire rx_data_valid ;initial beginclk = 0;rst_n = 0;rx = 1;#100rst_n = 1;end//调用task函数,连续发送八个数据initial begin#300tx_data(8'h6);tx_data(8'h6);tx_data(8'h1);tx_data(8'hA);tx_data(8'hB);tx_data(8'hC);tx_data(8'hD);tx_data(8'hE);tx_data(8'hF);end//定义task函数task tx_data(input [7:0] tx_data);integer i;for (i=0; i<10; i=i+1 ) begincase(i)0: rx <= 1'b0;1: rx <= tx_data[0];2: rx <= tx_data[1];3: rx <= tx_data[2];4: rx <= tx_data[3];5: rx <= tx_data[4];6: rx <= tx_data[5];7: rx <= tx_data[6];8: rx <= tx_data[7];9: rx <= 1'b1;endcase#(434*20);//每发送完一个bit数据后,延迟一个码元的时间endendtaskalways #10 clk = ~ clk;

uart_rx#(.CLK_FREQ ( 'd50_000_000 ),.UART_BPS ( 'd115200 )

)u1_uart_rx

(.clk ( clk ),.rst_n ( rst_n ),.rx ( rx ),.rx_data ( rx_data ),.rx_data_valid ( rx_data_valid )

);endmodule

3.4 仿真结果

由仿真结果可以看出,我们接收到的依次是(661ABCDEF)8个数据,和仿真文件给的一致。

3.5 上版测试

调用ila核,准备抓取rx_data,rx_data_valid信号。通过上位机发送数据,观察rx_data是否正确

上位机没发送数据时候,ila采集不到rx_data_valid信号拉高。

上位机发送一个9F时,ila采集到rx_data_valid信号拉高,并且输出rx_data为9F

四、UART发送器设计

4.1 发送时序图

4.2 Verilog代码

`timescale 1ns / 1ps

module uart_tx#

(parameter CLK_FREQ = 'd50_000_000, //时钟频率parameter UART_BPS = 'd115200 //波特率

)

(input clk ,input rst_n ,input [7:0] tx_data , //发送数据input tx_data_en , //发送数据有效信号output reg tx

);localparam BAUD_CNT_MAX = CLK_FREQ/UART_BPS;//待计数的码元周期最大值reg [7:0] tx_data_reg ;reg [23:0] baud_cnt ;reg [3:0] bit_cnt ;reg bit_flag ;reg tx_flag ;//将待发送的数据缓存起来

always @(posedge clk or negedge rst_n) beginif(rst_n == 1'b0)tx_data_reg <= 'd0;else if(tx_data_en == 1'b1)tx_data_reg <= tx_data;elsetx_data_reg <= tx_data_reg;

end//tx_flag拉高时刻

always @(posedge clk or negedge rst_n) beginif(rst_n == 1'b0)tx_flag <= 1'b0;else if(tx_data_en == 1'b1)tx_flag <= 1'b1;else if(bit_cnt == 'd9 && bit_flag == 1'b1)tx_flag <= 1'b0;elsetx_flag <= tx_flag;

end//baud_cnt 计数器

always @(posedge clk or negedge rst_n) beginif(rst_n == 1'b0)baud_cnt <= 'd0;else if(baud_cnt == BAUD_CNT_MAX)baud_cnt <= 'd0;else if(tx_flag == 1'b1)baud_cnt <= baud_cnt + 1'b1;elsebaud_cnt <= 'd0;

end

//bit_flag拉高时刻

always @(posedge clk or negedge rst_n) beginif(rst_n == 1'b0)bit_flag <= 1'b0;else if(baud_cnt == 'd1)bit_flag <= 1'b1;elsebit_flag <= 1'b0;

end//bit_cnt 计数器

always @(posedge clk or negedge rst_n) beginif(rst_n == 1'b0)bit_cnt <= 'd0;else if(bit_cnt == 'd9 && bit_flag == 1'b1)bit_cnt <= 'd0;else if(bit_flag == 1'b1)bit_cnt <= bit_cnt + 1'b1;elsebit_cnt <= bit_cnt;

end//移位data,由低到高发送至tx

always @(posedge clk or negedge rst_n) beginif(rst_n == 1'b0)tx <= 1'b1;else if(bit_flag == 1'b1)case(bit_cnt)0: tx <= 1'b0;1: tx <= tx_data_reg[0];2: tx <= tx_data_reg[1];3: tx <= tx_data_reg[2];4: tx <= tx_data_reg[3];5: tx <= tx_data_reg[4];6: tx <= tx_data_reg[5];7: tx <= tx_data_reg[6];8: tx <= tx_data_reg[7];9: tx <= 1'b1;default:tx <= 1'b1;endcase

endendmodule4.3 仿真文件测试

模拟两个数据(1A,3B)的输入,让tx模块发送

`timescale 1ns / 1ns

module tb_uart_tx();reg clk ;reg rst_n ;wire tx ;reg [7:0] tx_data ;reg tx_data_en ;initial beginclk = 0;rst_n = 0;tx_data = 8'd0;tx_data_en = 0;#100rst_n = 1;#300tx_data = 8'h1a;tx_data_en = 1;#20 tx_data_en = 0;#(434*20*10+100)//等待10个码元周期时间再等待100nstx_data = 8'h3b;tx_data_en = 1;#20 tx_data_en = 0;#(434*20*10+100)$stop;endalways #10 clk = ~clk;uart_tx#

(.CLK_FREQ ( 'd50_000_000 ),.UART_BPS ( 'd115200 )

)

u1_uart_tx

(.clk ( clk ),.rst_n ( rst_n ),.tx_data ( tx_data ),.tx_data_en ( tx_data_en ),.tx ( tx )

);endmodule4.4 仿真结果

因为发送数据是(1A:00011010)uart先发送起始位,再发送数据位从低到高,最后拉高一个停止位。理论上tx发送的顺序就是0_01011000_1

从仿真结果来看,tx线上的顺序和理论一致,3B数据同理。

4.5 上板测试

我们创建一个顶层,调用uart_tx模块,在顶层上输入一个数据,让发送模块发出,然后在上位机上接送,观察和我们发送的数据是否一致,代码如下:

`timescale 1ns / 1psmodule uart_top(input clk ,input rst_n ,output tx );reg [7:0] tx_data ;reg tx_data_en ;reg [1:0] cnt ;always @(posedge clk or negedge rst_n) beginif(rst_n == 1'b0)cnt <= 'd0;else if(cnt == 'd3)cnt <= cnt;else cnt <= cnt +1'b1;endalways @(posedge clk or negedge rst_n) beginif(rst_n == 1'b0)begintx_data <= 'd0;tx_data_en <= 1'b0;endelse if (cnt == 'd2)begintx_data <= 8'h6D;tx_data_en <= 1'b1;endelse begintx_data <= 'd0;tx_data_en <= 1'b0;endenduart_tx#

(.CLK_FREQ ( 'd50_000_000 ),.UART_BPS ( 'd115200 )

)

u_uart_tx

(.clk ( clk ),.rst_n ( rst_n ),.tx_data ( tx_data ),.tx_data_en ( tx_data_en ),.tx ( tx )

);endmodule

我们在顶层模块发送了一个 6D数据。

上板后,上位机收到了 6D数据

五、UART回环测试

5.1 系统框图

上面我们测试了UART发送和接收模块都正常,接下来我们将接收模块的输出信号接到发送模块的输入信号,在上位机上面发送数据和接收数据,看是否一致,系统框图如下:

5.2 Verilog代码

`timescale 1ns / 1psmodule uart_top(input clk ,input rst_n ,input rx ,output tx );wire [7:0] rx_data ;wire rx_data_valid ;uart_rx#

(.CLK_FREQ ( 'd50_000_000 ),.UART_BPS ( 'd115200 )

)

u_uart_rx(.clk ( clk ),.rst_n ( rst_n ),.rx ( rx ),.rx_data ( rx_data ),.rx_data_valid ( rx_data_valid )

);uart_tx#

(.CLK_FREQ ( 'd50_000_000 ),.UART_BPS ( 'd115200 )

)

u_uart_tx

(.clk ( clk ),.rst_n ( rst_n ),.tx_data ( rx_data ),.tx_data_en ( rx_data_valid ),.tx ( tx )

);endmodule5.3 仿真文件测试

我们依然用uart_rx里的测试代码,调用task函数,发送661abcdef

`timescale 1ns / 1ps

module tb_uart_top();reg clk ;reg rst_n ;reg rx ;wire tx ;initial beginclk = 0;rst_n = 0;rx = 1;#100rst_n = 1;end//调用task函数,连续发送八个数据initial begin#300tx_data(8'h6);tx_data(8'h6);tx_data(8'h1);tx_data(8'hA);tx_data(8'hB);tx_data(8'hC);tx_data(8'hD);tx_data(8'hE);tx_data(8'hF);end//定义task函数task tx_data(input [7:0] tx_data);integer i;for (i=0; i<10; i=i+1 ) begincase(i)0: rx <= 1'b0;1: rx <= tx_data[0];2: rx <= tx_data[1];3: rx <= tx_data[2];4: rx <= tx_data[3];5: rx <= tx_data[4];6: rx <= tx_data[5];7: rx <= tx_data[6];8: rx <= tx_data[7];9: rx <= 1'b1;endcase#(434*20);//每发送完一个bit数据后,延迟一个码元的时间endendtaskalways #10 clk =~clk;

uart_top u_uart_top(.clk ( clk ),.rst_n ( rst_n ),.rx ( rx ),.tx ( tx )

);endmodule5.4 仿真结果

可以看出接收后的数据和发送的数据没问题

5.5 上板测试

可以看到发送和接收都正常

六、参考

UART介绍

相关文章:

详解UART通信协议以及FPGA实现

文章目录 一、UART概述二、UART协议帧格式2.1 波特率2.2 奇校验ODD2.3 偶校验EVEN 三、UART接收器设计3.1 接收时序图3.2 Verilog代码3.3 仿真文件测试3.4 仿真结果3.5 上版测试 四、UART发送器设计4.1 发送时序图4.2 Verilog代码4.3 仿真文件测试4.4 仿真结果4.5 上板测试 五、…...

【算法】删除链表中重复元素

本题来源---《删除链表中重复元素》。 题目描述 给定一个已排序的链表的头 head , 删除所有重复的元素,使每个元素只出现一次 。返回已排序的链表 。 示例 1: 输入:head [1,1,2] 输出:[1,2]示例 2: 输入…...

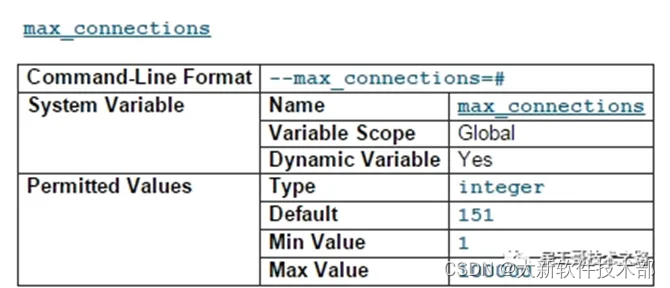

mysql防坑指南

1. MySQL连接数问题 MySQL里的max_connections参数代表mysql数据库的最大连接数,参数默认是151,显然不适用于生产,如果请求大于默认连接数,就会出现无法连接数据库的错误,会遇到too many connections的报错信息。 Mys…...

偏微分方程算法之混合边界差分

目录 一、研究对象 二、差分格式 2.1 向前欧拉格式 1. 中心差商 1.1.1 理论推导 1.1.2 算例实现 2. x0处向前差商,x1处向后差商 1.2.1 理论推导 1.2.2 算例实现 2.2 Crank-Nicolson格式 2.2.1 理论推导 2.2.2 算例实现 一、研究对象 这里我们以混合边界…...

中国八大古都,分别是哪8个?

中国历史上统一王朝或者在全局范围内看呈鼎立之势的大的政权的首都,称古都,又称都城、国都等,是古代王朝的政治中心,也是经济和文化中心。 1、西安 西安,古称长安,是中国历史上建都时间最长、建都朝代最多…...

财务信息化与财务软件有何区别与联系?

财务产品与财务信息化,两者究竟有何不同,又有何相通之处?或许,你心中也充满了这样的疑惑。那么,让我用一则小故事,为你揭晓其中的秘密。 想象这样一个场景,长尾狐狸,作为饭团公司的…...

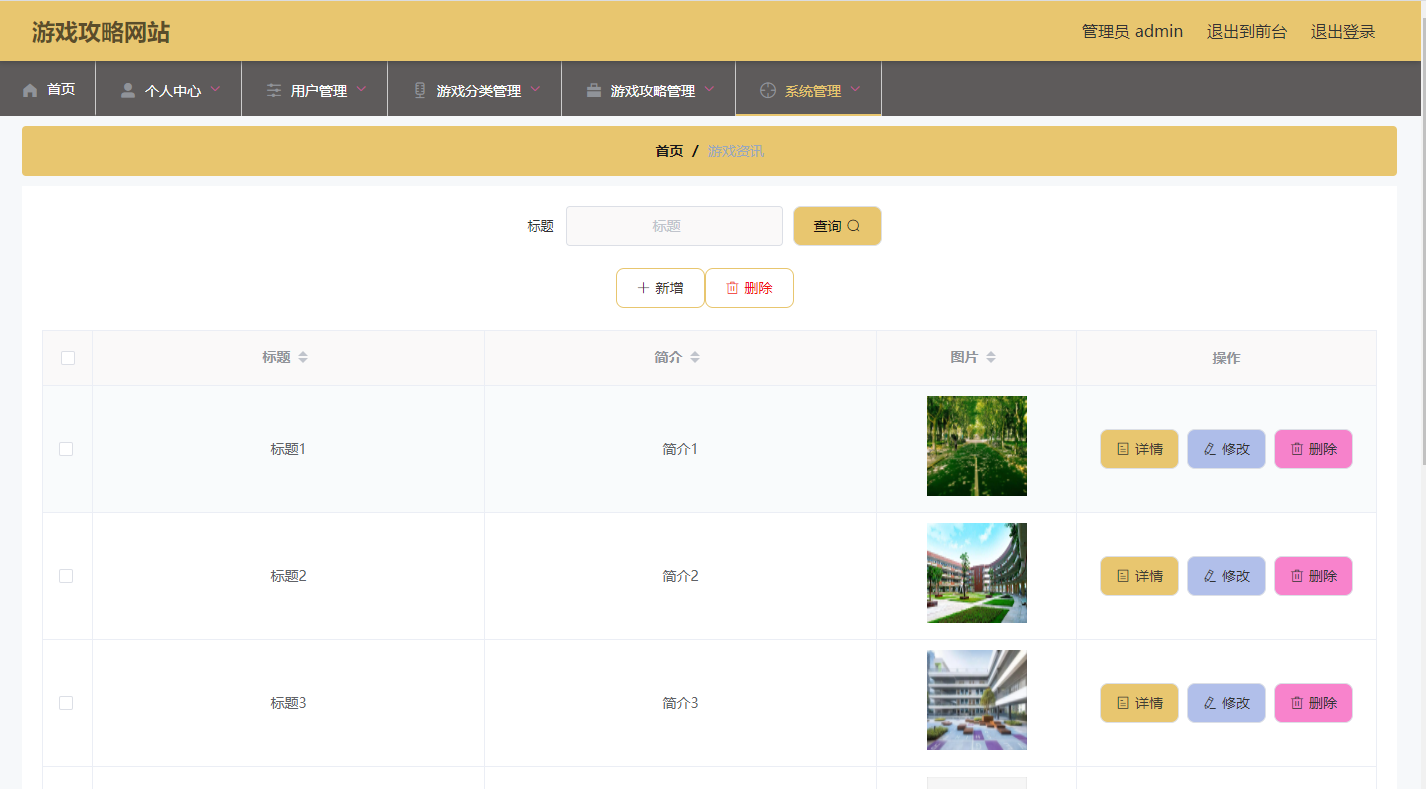

ssm052游戏攻略网站的设计与实现+vue

游戏攻略网站设计与实现 摘 要 现代经济快节奏发展以及不断完善升级的信息化技术,让传统数据信息的管理升级为软件存储,归纳,集中处理数据信息的管理方式。本游戏攻略网站就是在这样的大环境下诞生,其可以帮助管理者在短时间内处…...

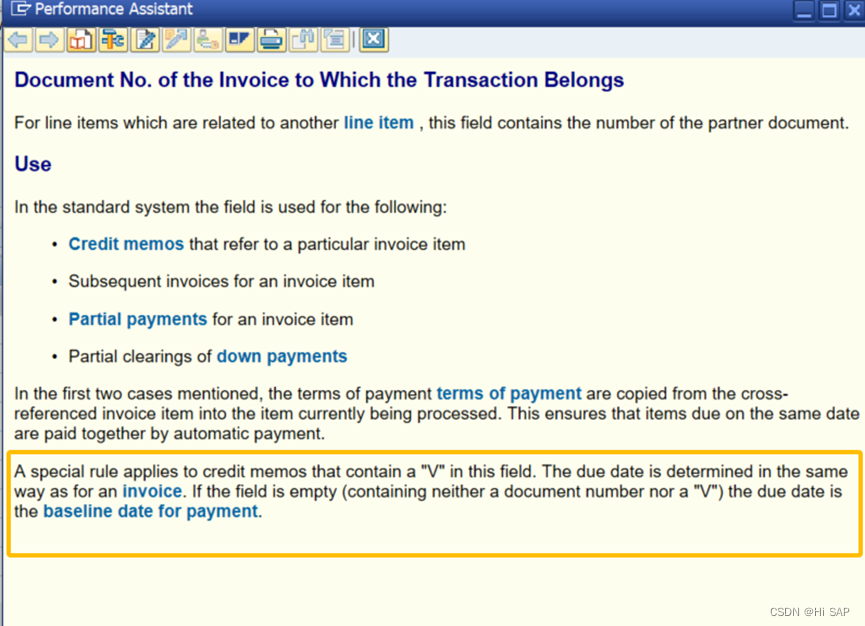

SAP Credit Memo 到期日设置技巧

当我们用FB60, MIRO或者FB70 记账vendor或者customer 的Credit Memo的时候,我们发现Credit Memo的Due Date不受付款条款的影响,默认为跟baseline date是同一天,并且无法手工更改,那么如果要设置到期日怎么操作呢? 首先…...

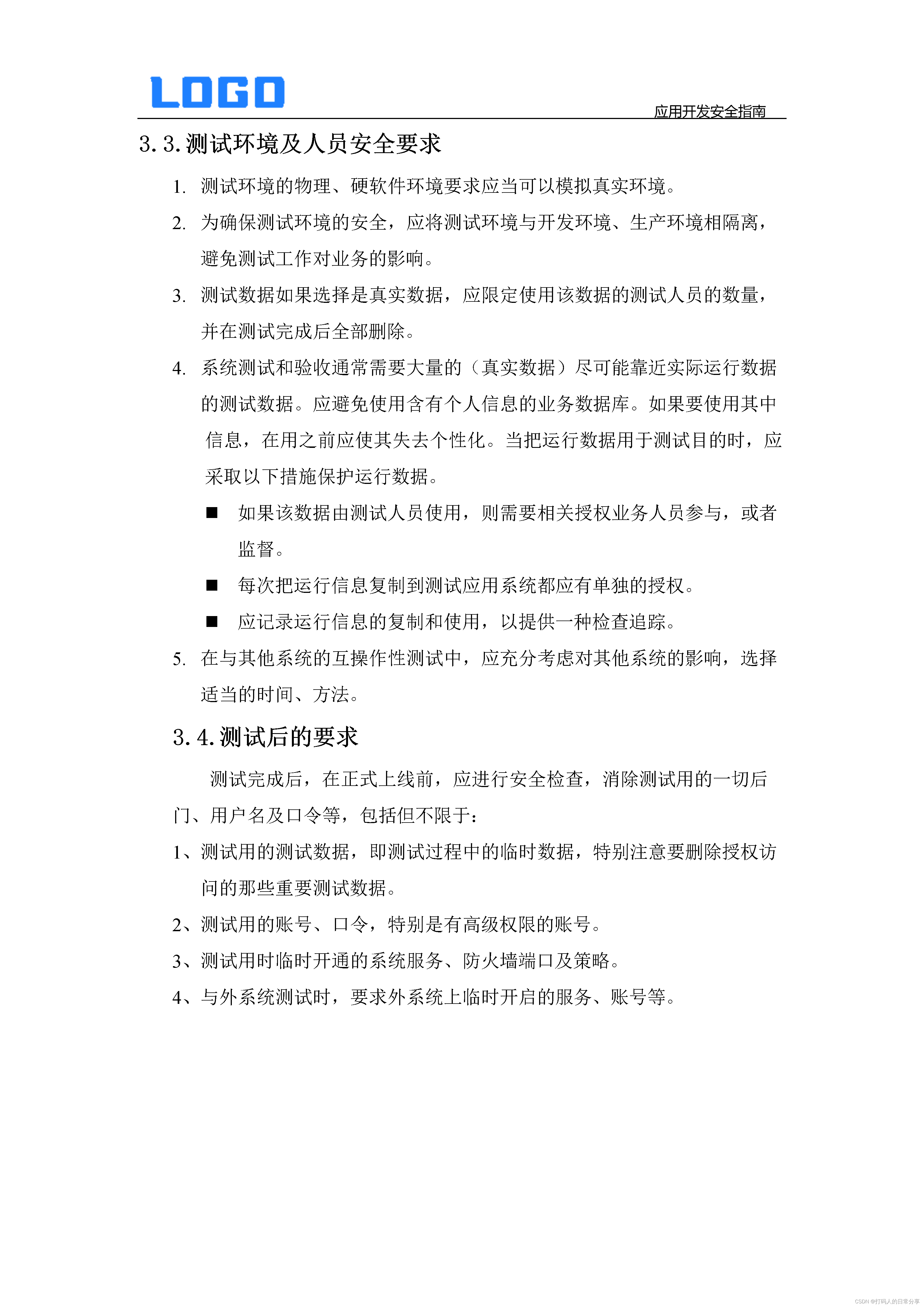

软件开发安全设计方案

2.1.应用系统架构安全设计要求 2.2.应用系统软件功能安全设计要求 2.3.应用系统存储安全设计要求 2.4.应用系统通讯安全设计要求 2.5.应用系统数据库安全设计要求 2.6.应用系统数据安全设计要求 软件开发全资料获取:软件开发全套资料_软件开发资料-CSDN博客https://…...

【Zabbix】zabbix 软件监控

使用zabbix监控系统查看服务器状态以及网站流量指标,利用监控系统的数据去了解上线发布的结果,和网站的健康状态 利用一个优秀的监控软件,我们可以: ●通过一个友好的界面进行浏览整个网站所有的服务器状态 ●可以在 Web 前端方便的查看监控…...

Vue Router 路由动态缓存组件

文章目录 一、简介基本用法生命周期钩子 二、定义是否缓存组件三、缓存组件1. 通过 :include 属性实现vue2.x中vue3.x中 2. 通过 v-slot 功能实现3. 通过 v-if 来实现 四、注意事项 一、简介 Vue Router 允许你缓存路由组件,这样在用户导航回之前的页面时ÿ…...

数据结构:线性表————单链表专题

🌈个人主页:小新_- 🎈个人座右铭:“成功者不是从不失败的人,而是从不放弃的人!”🎈 🎁欢迎各位→点赞👍 收藏⭐️ 留言📝 🏆所属专栏࿱…...

JMM中的内存屏障)

多线程(54)JMM中的内存屏障

Java内存模型(JMM)中的内存屏障是一种保证内存可见性、顺序性的底层机制。它们是一组指令,用于在多线程环境中确保内存操作的有序性和可见性。内存屏障主要分为四类:LoadLoad、StoreStore、LoadStore和StoreLoad。 内存屏障的类型…...

什么是流量清洗?

随着网络企业的迅速发展,越来越多的用户都开始关注关于网络流量的问题,同时,随着网络流量的增多,网络上也出现了大量的垃圾信息和恶意攻击,给网络带来了很大的困扰,而流量清洗则能够解决这个问题。 流量清洗…...

淘宝API(通过商品详情接口采集商品页面数据)请求说明文档|可接入测试key

淘宝商品详情数据接口(taobao.item_get)是天猫开放平台提供的一种API接口,旨在帮助开发者获取天猫平台上的商品详情信息。通过调用这个接口,开发者可以获取包括商品ID、标题、价格、库存量、图片等在内的详细数据,从而…...

示例说明闭包函数

示例说明闭包函数 闭包函数是指在一个函数内部定义另一个函数,并且内部函数可以访问外部函数的局部变量,即使外部函数已经执行完毕。 这种功能使得闭包函数可以捕获外部函数的状态,提供了一种保留局部变量值的方式。闭包函数在编程中常用于…...

【自媒体创作利器】AI白日梦+ChatGPT 三分钟生成爆款短视频

AI白日梦https://brmgo.com/signup?codey5no6idev 引言 随着人工智能(AI)技术的快速发展,AI在各个领域都展现出了强大的应用潜力。其中,自然语言处理技术的进步使得智能对话系统得以实现,而ChatGPT作为其中的代表之一…...

把握零碎时间,开启长期副业兼职之旅!在家也能轻松赚钱!

转眼间,2024年已悄然走过三分之一。这一年,外界环境似乎并不那么友好,但对我而言,我的月收入仍然相对稳定。我找到的副业让我每月能赚到3000元以上,这让我深感庆幸。 现实中,只依赖主业工资的日子确实艰辛…...

HarmonyOS开发实例:【数字管家app】

样例简介 数字管家场景需要手机端、设备端和服务端三方协同完成,本文档介绍的demo是数字管家大场景中的手机端应用;用户注册登录后可创建我的家庭并管理家庭成员;可以添加设备(包括智能台灯,智能窗帘,智能…...

人工智能_大模型033_LangChain003_记忆封装Memory上下文控制机制_LCEL表达式语言---人工智能工作笔记0168

## 三、记忆封装:Memory ### 3.1、对话上下文:ConversationBufferMemory from langchain.memory import ConversationBufferMemory, ConversationBufferWindowMemoryhistory = ConversationBufferMemory() history.save_context({"input": "你好啊"}…...

Qwen3-TTS快速体验:一键部署,输入文字即可生成10种语言语音

Qwen3-TTS快速体验:一键部署,输入文字即可生成10种语言语音 1. 从文字到语音,只需要几分钟 你有没有想过,把自己写的文字变成不同国家语言的语音,而且还能指定说话人的风格?比如让一个温柔的成年女性用中…...

Wishbone总线在嵌入式系统中的高效数据传输实践

1. Wishbone总线在嵌入式系统中的核心价值 第一次接触Wishbone总线是在2015年设计工业控制器的时候。当时我们需要在FPGA和多个传感器之间建立高速数据通道,尝试了几种总线方案后,最终被Wishbone的简洁高效所折服。这种开源总线协议虽然不如AXI、AHB等商…...

Windows系统下Xinference部署全攻略:从环境配置到模型启动

1. 为什么要在Windows上部署Xinference? 如果你正在Windows系统上尝试运行各种AI模型,可能会发现很多开源工具对Windows的支持并不友好。比如ollama虽然简单易用,但只能处理LLM和嵌入模型;vLLM干脆就不支持Windows平台。这时候Xi…...

用过才敢说 9个AI论文平台 全场景通用测评 从开题到毕业论文全搞定

在学术研究日益数字化的今天,AI写作工具已成为科研人员和高校学子不可或缺的助手。然而,面对市场上琳琅满目的平台,如何选择真正适合自己的工具成为一大难题。为此,我们基于2026年的实测数据与用户真实反馈,启动了本次…...

)

手把手教你用whip/whep协议实现ZLMediaKit的WebRTC拉流(2024最新版)

2024实战指南:基于WHIP/WHEP协议构建ZLMediaKit的WebRTC低延迟拉流系统 在实时音视频领域,WebRTC技术凭借其低延迟和点对点通信优势已成为行业标配。而WHIP/WHEP协议的出现,进一步简化了WebRTC与传统媒体服务器的集成流程。本文将深入探讨如何…...

)

闲鱼卖货4年从教师到自由职业,我把新手最想知道的30个问题整理出来了(干货版)

2026年了,做闲鱼的第4年。 4年前我在干嘛?还在学校上课,虽说这是体面的工作,但是心酸的累也只有自己知道。 做闲鱼4年了,从一个什么都不懂的小白,到卖出第一单,再到做成自己的店铺。 这些年我带过不少人上手, 有带娃的宝妈、有和我一样的打工人、也有想下班找点事做…...

摒弃有害厨具,京尚黑科技陶瓷锅,开启高端健康烹饪时代

健康生活,从选对一口锅开始。京尚纯陶瓷锅以天然无机材质为核心,坚守“零重金属、零有害析出”的安全底线,不含锰、铅、镉,不生锈、不串味、不腐蚀,完美替代有健康隐患的不锈钢与涂层锅,让烹饪回归纯粹与安…...

GitHub Linguist与编辑器集成:VSCode插件开发实例

GitHub Linguist与编辑器集成:VSCode插件开发实例 【免费下载链接】linguist Language Savant. If your repositorys language is being reported incorrectly, send us a pull request! 项目地址: https://gitcode.com/GitHub_Trending/li/linguist GitHub …...

2026 九大 AI 毕业论文格式排版工具实测:Paperxie 领衔,精准适配 4000 + 高校模板

paperxie-免费查重复率aigc检测/开题报告/毕业论文/智能排版/文献综述/aippthttps://www.paperxie.cn/format/typesettinghttps://www.paperxie.cn/format/typesetting 毕业季的收尾阶段,格式排版始终是本科生、研究生跨越毕业门槛的 “关键一关”。从字体行距的精准…...

SHT30温湿度传感器I²C驱动开发与嵌入式实践

1. SHT30数字温湿度传感器硬件与驱动实现详解1.1 器件选型与工程定位SHT30是 Sensirion 公司推出的高精度数字温湿度传感器,广泛应用于环境监测、工业控制、智能楼宇及消费电子等领域。其核心优势在于0.3℃的温度测量精度与2%RH的湿度测量精度,配合-40℃…...