FPGA之术语

FPGA之术语

- IOSTANDARD

- DIFF_SSTL12:

- LVCMOS33:

- sys_clk_p/n:

- rst_n:

- UART

- 时钟

- JTAG:

- GPIO

- ONFI

- PCIe

IOSTANDARD

在电子工程领域,DIFF_SSTL12和LVCMOS33是两种不同的电气标准,用于定义信号的电压级别和特性。

IOSTANDARD是一个在FPGA(现场可编程门阵列)设计中使用的术语,它指的是用于定义I/O(输入/输出)引脚电气特性的标准。这些标准确保了FPGA的I/O引脚能够与外部设备或电路兼容,并且可以按照预期的方式进行通信。

在FPGA设计中,不同的IOSTANDARD可以影响信号的电压水平、速度、驱动能力等。以下是一些常见的IOSTANDARD:

LVCMOS:

这是低电压互补金属氧化物半导体标准,用于定义3.3V或1.8V的单端I/O信号。

HSTL:

高速传输线标准,用于高速信号传输,通常用于1.5V或1.8V的I/O。

SSTL:

串行传输线标准,用于高速串行数据传输,通常与差分信号一起使用。

DIFF_SSTL:

差分版本的SSTL标准,用于高速差分信号传输。

LVDS:

低电压差分信号标准,用于长距离、高速数据传输。

Vivado:

Xilinx的Vivado设计套件中,IOSTANDARD属性可以指定在FPGA设计中使用的电气标准。

I/O Bank:

在FPGA中,I/O Bank是一组具有相同电气特性的I/O引脚。

I/O Constraints:

在FPGA设计中,I/O约束(Constraints)用于定义I/O引脚的电气特性,包括IOSTANDARD。

I/O Delay:

有时,IOSTANDARD的指定也与I/O延迟有关,用于同步信号。

I/O Buffer:

I/O Buffer是FPGA中用于驱动I/O引脚的电路,它可以根据IOSTANDARD进行配置。

在设计FPGA时,选择正确的IOSTANDARD对于确保设计的性能和可靠性至关重要。设计者需要根据外部设备的电气特性和设计要求来选择合适的IOSTANDARD。例如,如果设计需要与使用1.8V LVCMOS标准的外部设备通信,那么FPGA的相应I/O引脚也需要配置为1.8V LVCMOS IOSTANDARD。

DIFF_SSTL12:

DIFF代表差分信号,意味着数据通过一对互补的信号线传输,以减少噪声和提高信号完整性。

SSTL12是串行总线标准,其中"S"代表串行,"STL"代表串行总线逻辑,"12"表示电压级别,通常指的是1.2V的差分电压标准。

SSTL(Serial Source-Synchronous Interface Level)是一种串行接口标准,主要用于高速数据传输。

DIFF表示差分信号,即信号通过一对互补的信号线传输,这有助于减少噪声和提高信号的完整性。

"12"指的是信号的电压水平,表示在差分信号中,电压摆动(swing)从0V到1.2V。这种电压水平较低,有助于减少功耗和电磁干扰(EMI)。

LVCMOS33:

LVCMOS代表低电压互补金属氧化物半导体,这是一种常用的数字电路标准。

33表示电压级别,通常指的是3.3V的单端电压标准。

LVCMOS(Low Voltage CMOS)是一种低电压互补金属氧化物半导体标准,广泛用于数字电路。

"33"表示这种标准使用的电压水平为3.3V。LVCMOS33通常用于低速或中等速度的数字电路,因为它的电压水平较高,但功耗相对较大。

DIFF_SSTL12和LVCMOS33是两种不同的电气接口标准,它们定义了信号的电压水平和特性,通常用于高速数字电路的信号传输。下面是对这两种标准的详细比较:

电压水平:DIFF_SSTL12的电压水平较低(1.2V),而LVCMOS33的电压水平较高(3.3V)。

信号类型:DIFF_SSTL12使用差分信号,而LVCMOS33使用单端信号。

应用场景:DIFF_SSTL12更适合高速数据传输,因为它的差分特性有助于减少噪声和提高信号完整性。LVCMOS33则更适用于低速或中等速度的数字电路,因为它的电压水平较高,信号更容易被检测。

设计考虑:

在设计电路时,需要根据应用的具体需求选择合适的电气标准。例如,如果需要高速数据传输,可能会选择DIFF_SSTL12。如果对功耗要求不高,且电路速度不是主要考虑因素,可能会选择LVCMOS33。

兼容性:

在实际应用中,可能需要在不同的电气标准之间进行接口转换,例如使用电平转换器将LVCMOS33信号转换为DIFF_SSTL12信号,或者反之。

信号完整性:

差分信号(如DIFF_SSTL12)在长距离传输和高速应用中具有更好的信号完整性,因为它们对外部噪声的抵抗能力更强。

在电子设计中,选择不同的电气标准(如DIFF_SSTL12和LVCMOS33)通常基于以下几个考虑因素:

信号完整性: DIFF_SSTL12是一种差分信号标准,它提供了更好的信号完整性和抗干扰能力。差分信号可以减少电磁干扰(EMI)和信号退化,因为它们通过测量两个信号之间的电压差来确定信号状态,而不是每个信号的绝对电压。

速度: 差分信号通常用于高速数据传输,因为它们可以更快速地切换状态,并且信号传播延迟较小。SSTL12标准可能被设计用于高速信号传输,而LVCMOS33可能用于较低速度的信号。

功耗: LVCMOS33标准由于其较高的电压水平,可能在某些情况下提供更好的功耗效率,尤其是在不需要高速传输的场合。

兼容性: 设计者可能需要确保系统时钟与外部设备的接口兼容。如果外部设备使用LVCMOS33标准,那么使用rst_n作为低电平有效的复位信号可能更合适。

设计复杂性: 在某些情况下,使用LVCMOS33标准可能简化设计,因为这种标准在许多现有的电子系统中已经广泛使用,并且可能更容易与其他组件集成。

成本: 选择不同的电气标准可能会影响生产成本。在某些情况下,使用LVCMOS33可能更经济,因为它可能需要更少的定制化设计。

系统要求: 系统设计可能要求某些信号使用特定的电气标准以满足特定的性能或功能需求。

信号类型: sys_clk_p/n作为系统时钟信号,使用差分信号可以提供更准确的同步,而rst_n作为复位信号,可能不需要高速传输,因此使用LVCMOS33标准可能足够。

安全和可靠性: 在某些应用中,使用差分信号可以提高系统的可靠性和安全性,因为它们对噪声的抵抗能力更强。

技术规范: 不同的信号可能遵循不同的技术规范或行业标准,这可能要求使用特定的电气标准。

综上所述,选择DIFF_SSTL12作为系统时钟信号的电气标准,以及LVCMOS33作为复位信号的电气标准,是基于多种设计考虑和技术要求的结果。

sys_clk_p/n:

这些通常指的是系统时钟的正相(sys_clk_p)和负相(sys_clk_n)输入。在差分信号中,它们一起工作以提供精确的时钟信号。

系统时钟的正相(sys_clk_p)和负相(sys_clk_n)是差分信号传输中的两个互补的信号。差分信号传输是一种在电子通信中广泛使用的技术,它通过使用成对的信号线来传输信息,其中一个信号线表示正相,另一个表示负相。

set_property PACKAGE_PIN AL8 [get_ports sys_clk_p] #这行代码为sys_clk_p(可能代表系统时钟的正相位)指定了物理引脚位置AL8。set_property是Tcl中用于设置属性的命令,PACKAGE_PIN属性指定了FPGA封装中引脚的物理位置。

set_property IOSTANDARD DIFF_SSTL12 [get_ports sys_clk_p] #此行设置了sys_clk_p的输入/输出标准为DIFF_SSTL12,这是一种差分信号标准,适用于高速或高稳定性的时钟信号。

set_property IOSTANDARD DIFF_SSTL12 [get_ports sys_clk_n] #这行代码为sys_clk_n(可能代表系统时钟的负相位)设置了相同的差分信号标准DIFF_SSTL12。

sys_clk_p/n作为系统时钟信号,使用差分信号可以提供更准确的同步,而rst_n作为复位信号,可能不需要高速传输,因此使用LVCMOS33标准可能足够。

下面是一些关于这两个信号的详细说明:

差分信号:

差分信号传输可以提高信号的完整性和抗干扰能力。由于信号是通过一对互补的信号线传输的,因此它们之间的电压差代表了实际的信号状态。

sys_clk_p:

正相信号通常标记为sys_clk_p,它代表了时钟信号的高电平部分。在数字电路中,高电平通常与逻辑"1"相对应。

sys_clk_n:

负相信号通常标记为sys_clk_n,它代表了时钟信号的低电平部分。在数字电路中,低电平通常与逻辑"0"相对应。

时钟信号的作用:

系统时钟是同步数字电路操作的基准信号。它为电路中的逻辑门和寄存器提供同步脉冲,确保数据在正确的时刻被读取或写入。

差分时钟的优势:

使用差分时钟可以减少电磁干扰(EMI)和信号退化,因为信号的完整性不受外部噪声的影响。差分信号的接收端通过比较两个信号线的电压差来确定信号状态,而不是单独测量每个信号线的绝对电压。

应用场景:

差分时钟信号在高速数据传输和长距离通信中尤为重要,例如在高速串行通信接口(如PCIe、SATA、USB等)中。

信号完整性:

在设计高速电路时,信号完整性是一个关键考虑因素。差分信号有助于减少信号的时延和失真,从而确保数据传输的准确性。

差分时钟信号是现代电子设计中的一个重要组成部分,特别是在需要高速和高可靠性的系统中。

rst_n:

这是复位信号,其中"n"代表它是低电平有效的,意味着当信号为低电平时,系统或设备会进行复位。

set_property PACKAGE_PIN AN12 [get_ports rst_n] #这行代码为复位信号rst_n(低电平有效的复位信号)指定了物理引脚位置AN12。

set_property IOSTANDARD LVCMOS33 [get_ports rst_n] #此行为rst_n设置了输入/输出标准为LVCMOS33,这是一种低电压互补金属氧化物半导体标准,适用于3.3V的工作电压。

UART

UART,即通用异步接收/发送装置(Universal Asynchronous Receiver/Transmitter),是一种串行通信协议和设备,用于计算机和电子设备之间的数据传输。以下是UART的一些关键特性和功能:

异步通信:

UART使用异步通信方式,这意味着发送和接收设备不需要共享一个时钟信号来同步数据传输。

数据传输速率:

数据传输速率由波特率(Baud Rate)决定,这是每秒传输的比特数。常见的波特率有9600、19200、38400、115200等。

串行数据:

UART通过串行方式传输数据,即每次传输一个比特。

数据帧:

数据通常以帧的形式传输,一个数据帧包括起始位、数据位、奇偶校验位(可选)和停止位。

起始位:

每个数据帧开始时,UART发送一个起始位,通常为0。

数据位:

数据位是传输数据的核心部分,常见的数据位长度有7位、8位等。

奇偶校验位:

可选的奇偶校验位用于错误检测,可以是奇校验或偶校验。

停止位:

数据帧传输结束后,UART发送一个或两个停止位,通常为1,用于标识数据帧的结束。

全双工通信:

UART支持全双工通信,即可以同时发送和接收数据。

连接方式:

UART通常通过串行接口,如RS-232、RS-485等,连接到其他设备。

应用场景:

UART广泛应用于计算机、微控制器、调制解调器、传感器等设备的数据通信。

硬件实现:

UART可以作为独立芯片或集成在微控制器、FPGA等设备中。

软件配置:

UART的波特率、数据位、停止位和奇偶校验等参数通常可以通过软件配置。

中断和DMA:

许多微控制器中的UART模块支持中断和直接内存访问(DMA),以提高数据传输的效率和灵活性。

UART是一种非常基本但广泛使用的串行通信协议,适用于各种低速到中等速度的数据传输应用。

set_property PACKAGE_PIN D11 [get_ports {uart_rx}]

set_property IOSTANDARD LVCMOS33 [get_ports {uart_rx}]set_property PACKAGE_PIN D10 [get_ports {uart_tx}]

set_property IOSTANDARD LVCMOS33 [get_ports {uart_tx}]

这些命令用于设置FPGA引脚的属性。Tcl是一种脚本语言,常用于自动化设计流程和配置FPGA。下面是对这些命令的解释:

set_property: 这是一个Tcl命令,用于设置FPGA设计中的属性。

PACKAGE_PIN: 这个属性指定了FPGA芯片上的物理引脚。在这个例子中,D11和D10是FPGA芯片上的引脚编号。

get_ports {uart_rx} 和 get_ports {uart_tx}: 这些是Tcl命令,用于获取名为uart_rx和uart_tx的端口。uart_rx通常代表UART(通用异步接收/发送装置)接收端口,而uart_tx代表UART发送端口。

IOSTANDARD: 这个属性定义了FPGA引脚的电气标准。在这个例子中,LVCMOS33被设置为uart_rx和uart_tx端口的电气标准。

LVCMOS33: 这是一个电气标准,表示低电压互补金属氧化物半导体,33表示3.3V的逻辑电平。这通常用于低速或中等速度的数字信号。

这些命令的作用是将FPGA设计中的UART接收和发送端口分别映射到物理引脚D11和D10上,并且指定这两个引脚使用LVCMOS33电气标准。这样配置后,设计中的UART通信就可以通过这些特定的引脚与外部设备进行交互。

在实际的FPGA设计过程中,这样的脚本可以帮助自动化引脚分配和电气配置,确保设计满足特定的硬件要求和接口标准。

时钟

create_clock -period 20.000 -name clk -waveform {0.000 10.000} [get_ports clk]

set_property C_CLK_INPUT_FREQ_HZ 300000000 [get_debug_cores dbg_hub]

set_property C_ENABLE_CLK_DIVIDER false [get_debug_cores dbg_hub]

set_property C_USER_SCAN_CHAIN 1 [get_debug_cores dbg_hub]

connect_debug_port dbg_hub/clk [get_nets clk_IBUF_BUFG]

create_clock:

这个命令用于创建一个新的时钟定义。它指定了时钟的周期(以纳秒为单位)和时钟的波形(上升沿和下降沿的时间)。

-period 20.000: 表示时钟周期为20纳秒,即50MHz的频率。

-name clk: 给创建的时钟定义命名为clk。

-waveform {0.000 10.000}: 定义时钟的波形,0.000表示时钟开始时为0,10.000表示时钟在10纳秒后变为1。

[get_ports clk]:

这个命令获取名为clk的端口,并将创建的时钟定义应用到这个端口上。

set_property C_CLK_INPUT_FREQ_HZ 300000000 [get_debug_cores dbg_hub]:

这个命令为调试核心dbg_hub设置了时钟输入频率的属性,这里是300MHz。

set_property C_ENABLE_CLK_DIVIDER false [get_debug_cores dbg_hub]:

这个命令设置调试核心dbg_hub的时钟分频器属性为false,表示不启用时钟分频。

set_property C_USER_SCAN_CHAIN 1 [get_debug_cores dbg_hub]:

这个命令设置调试核心dbg_hub的用户扫描链属性为1,这可能与测试或调试配置有关。

connect_debug_port dbg_hub/clk [get_nets clk_IBUF_BUFG]:

这个命令将调试核心dbg_hub的时钟端口clk连接到名为clk_IBUF_BUFG的网络。这通常意味着将外部时钟信号通过一个输入缓冲器(IBUF)和一个全局时钟缓冲器(BUFG)连接到调试核心。

这些命令通常用于FPGA设计中的时钟管理和调试接口配置,确保设计满足特定的时钟要求和调试需求。通过这些设置,设计者可以精确控制时钟信号的频率和相位,以及如何将时钟信号连接到FPGA的调试逻辑。

JTAG:

JTAG是联合测试行动组的缩写,是一种标准的测试接口,用于对电子设备进行测试和编程。TAG是一种用于测试印刷电路板上芯片之间连接的标准,也用于芯片内部的编程和调试。JTAG接口允许对芯片进行在线测试(例如边界扫描测试)和固件更新。

用途:JTAG主要用于设备制造和维修期间的故障诊断、调试以及固件更新。

GPIO

GPIO是通用输入输出的缩写,指的是可以配置为输入或输出的数字信号引脚。GPIO是微控制器、微处理器或FPGA等数字电路中的一种通用引脚,可以被程序设置为输入或输出。GPIO用于各种简单的输入输出功能,如读取按钮状态、控制LED等。

用途:GPIO非常灵活,用于基本的数字信号操作。

ONFI

ONFI是开放NAND闪存接口的缩写,是一个行业标准,定义了NAND闪存的接口规范。ONFI是一种为NAND闪存芯片定义的标准接口。它由多个大型半导体公司共同开发,旨在标准化NAND闪存的接口,以确保不同厂商的产品之间的互操作性。

用途:ONFI使得系统设计者可以不受供应商限制地选择NAND闪存芯片,因为符合ONFI标准的芯片能保证相互兼容。

PCIe

PCIe是周边组件互连快速总线的缩写,是一种高速串行输入/输出总线标准,用于计算机硬件设备之间的连接。PCIe是一种高速串行计算机扩展总线标准,用于连接主板的中央处理单元与扩展卡及其他设备。PCIe提供比旧的并行PCI总线更高的基带带宽和更低的引脚计数。

用途:PCIe广泛应用于高性能数据传输需求的设备,如显卡、固态硬盘、网络卡等。

相关文章:

FPGA之术语

FPGA之术语 IOSTANDARDDIFF_SSTL12:LVCMOS33:sys_clk_p/n:rst_n:UART时钟JTAG:GPIOONFIPCIe IOSTANDARD 在电子工程领域,DIFF_SSTL12和LVCMOS33是两种不同的电气标准,用于定义信号的电压级别和特性。 IOSTANDARD是一个在FPGA(现场可编程门阵…...

WPF透明置顶窗口wine适配穿透问题解决

一、透明窗口全屏时,鼠标不穿透 问题描述 我有一个透明窗口,它是一个全屏置顶窗口,窗口里面有一个工具条,可以通过鼠标拖动工具条的位置,程序启动后,在不点击工具条的时候,鼠标是可以穿透的&a…...

方法的使用)

浅析Kafka Streams中KTable.aggregate()方法的使用

KTable.aggregate() 方法是 Apache Kafka Streams API 中用于对流数据进行状态化聚合的核心方法之一。这个方法允许你根据一个键值(通常是<K,V>类型)的流数据,应用一个初始值和一个聚合函数,来累积和更新一个状态࿰…...

java word转pdf、word中关键字位置插入图片 工具类

java word转pdf、word中关键字位置插入图片 工具类 1.pom依赖 <dependency><groupId>org.apache.poi</groupId><artifactId>poi</artifactId><version>3.15</version></dependency><dependency><groupId>org.apa…...

jail内部ubuntu apt升级失败问题解决

在FreeBSD jail 里安装启动Ubuntu jammy系统,每次装好执行jexec ubjammy sh进入Ubuntu系统后,执行apt update报错。 这个问题困惑了好久,突然有一天仔细去看报错信息,查看了(man 5 apt.conf) ,才搞定问题。简单来说就是…...

迎接AI新时代:GPT-5的技术飞跃与未来展望

引言 随着人工智能技术的迅猛发展,大语言模型在过去几年取得了显著进步。OpenAI最新的声明表明,GPT-5将在一年半后发布,并将带来从高中生智力水平到博士生智力水平的飞跃。这一突破引起了科技界和公众的广泛关注。本文将从技术突破预测、智能…...

Snap Video:用于文本到视频合成的扩展时空变换器

图像生成模型的质量和多功能性的显著提升,研究界开始将其应用于视频生成领域。但是视频内容高度冗余,直接将图像模型技术应用于视频生成可能会降低运动的保真度和视觉质量,并影响可扩展性。来自 Snap 的研究团队及其合作者提出了 "Snap …...

实验8 视图创建与管理实验

一、实验目的 理解视图的概念。掌握创建、更改、删除视图的方法。掌握使用视图来访问数据的方法。 二、实验内容 在job数据库中,有聘任人员信息表:Work_lnfo表,其表结构如下表所示: 其中表中练习数据如下: 1.‘张明…...

C++ 开源库

1 PDFium PDFium 是一个开源的 PDF 渲染和处理库,最初由 Foxit Software 开发,并于2014年捐赠给了 Chromium 项目。PDFium 旨在为各种应用程序提供高效、灵活的 PDF 渲染和操作功能。 2 代码地址 https://github.com/chromium/pdfium 主要特性 渲染…...

LabVIEW滤波器性能研究

为了研究滤波器的滤波性能,采用LabVIEW设计了一套滤波器性能研究系统。该系统通过LabVIEW中的波形生成函数,输出幅值及频率可调的正弦波和白噪声两种信号,并将白噪声与正弦波叠加,再通过滤波器输出纯净的正弦波信号。系统通过FFT&…...

『C++成长记』vector模拟实现

🔥博客主页:小王又困了 📚系列专栏:C 🌟人之为学,不日近则日退 ❤️感谢大家点赞👍收藏⭐评论✍️ 目录 一、存储结构 二、默认成员函数 📒2.1构造函数 📒2.2拷贝…...

【Mac】Charles for Mac(HTTP协议抓包工具)及同类型软件介绍

软件介绍 Charles for Mac 是一款功能强大的网络调试工具,主要用于HTTP代理/HTTP监视器。以下是它的一些主要特点和功能: 1.HTTP代理:Charles 可以作为HTTP代理服务器,允许你查看客户端和服务器之间的所有HTTP和SSL/TLS通信。 …...

LVS集群及其它的NAT模式

1.lvs集群作用:是linux的内核层面实现负载均衡的软件;将多个后端服务器组成一个高可用、高性能的服务器的集群,通过负载均衡的算法将客户端的请求分发到后端的服务器上,通过这种方式实现高可用和负载均衡。 2.集群和分布式&#…...

【RNN练习】天气预测

🍨 本文为🔗365天深度学习训练营 中的学习记录博客🍖 原作者:K同学啊 一、环境及数据准备 1. 我的环境 语言环境:Python3.11.9编译器:Jupyter notebook深度学习框架:TensorFlow 2.15.0 2. 导…...

prompt第四讲-fewshot

文章目录 前提回顾FewShotPromptTemplateforamt格式化 前提回顾 前面已经实现了一个翻译助手了[prompt第三讲-PromptTemplate],prompt模板设计中,有说明、案例、和实际的问题 # -*- coding: utf-8 -*- """ Time : 2024/7/8 …...

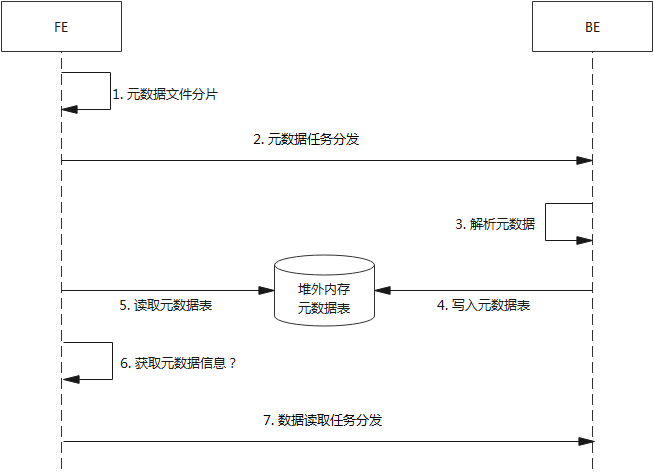

StarRocks分布式元数据源码解析

1. 支持元数据表 https://github.com/StarRocks/starrocks/pull/44276/files 核心类:LogicalIcebergMetadataTable,Iceberg元数据表,将元数据的各个字段做成表的列,后期可以通过sql操作从元数据获取字段,这个表的组成…...

阅读笔记——《Fuzz4All: Universal Fuzzing with Large Language Models》

【参考文献】Xia C S, Paltenghi M, Le Tian J, et al. Fuzz4all: Universal fuzzing with large language models[C]//Proceedings of the IEEE/ACM 46th International Conference on Software Engineering. 2024: 1-13.【注】本文仅为作者个人学习笔记,如有冒犯&…...

【C++】使用gtest做单元测试框架写单元测试

本文主要介绍在将gtest框架引入到项目里过程中遇到的问题。 我的需求如下: 用CMake构建项目。我要写一些测试程序验证某些功能,但是不想每一个测试都新建一个main函数。 因为新建一个main函数就要在CMakeList.txt里增加一个project,非常不方便。 于是我搜了下,C++里有没…...

Java类与对象

类是对现实世界中实体的抽象,是对一类事物的描述。 类的属性位置在类的内部、方法的外部。 类的属性描述一个类的一些可描述的特性,比如人的姓名、年龄、性别等。 [public] [abstract|final] class 类名 [extends父类] [implements接口列表] { 属性声…...

xlwings 链接到 指定sheet 从别的 excel 复制 sheet 到指定 sheet

重点 可以参考 宏录制 cell sheet.range(G4)cell.api.Hyperlinks.Add(Anchorcell.api, Address"", SubAddress"001-000-02301!A1")def deal_excel(self):with xw.App(visibleTrue) as app:wb app.books.open(self.summary_path, update_linksFalse)sheet…...

测试微信模版消息推送

进入“开发接口管理”--“公众平台测试账号”,无需申请公众账号、可在测试账号中体验并测试微信公众平台所有高级接口。 获取access_token: 自定义模版消息: 关注测试号:扫二维码关注测试号。 发送模版消息: import requests da…...

内存分配函数malloc kmalloc vmalloc

内存分配函数malloc kmalloc vmalloc malloc实现步骤: 1)请求大小调整:首先,malloc 需要调整用户请求的大小,以适应内部数据结构(例如,可能需要存储额外的元数据)。通常,这包括对齐调整,确保分配的内存地址满足特定硬件要求(如对齐到8字节或16字节边界)。 2)空闲…...

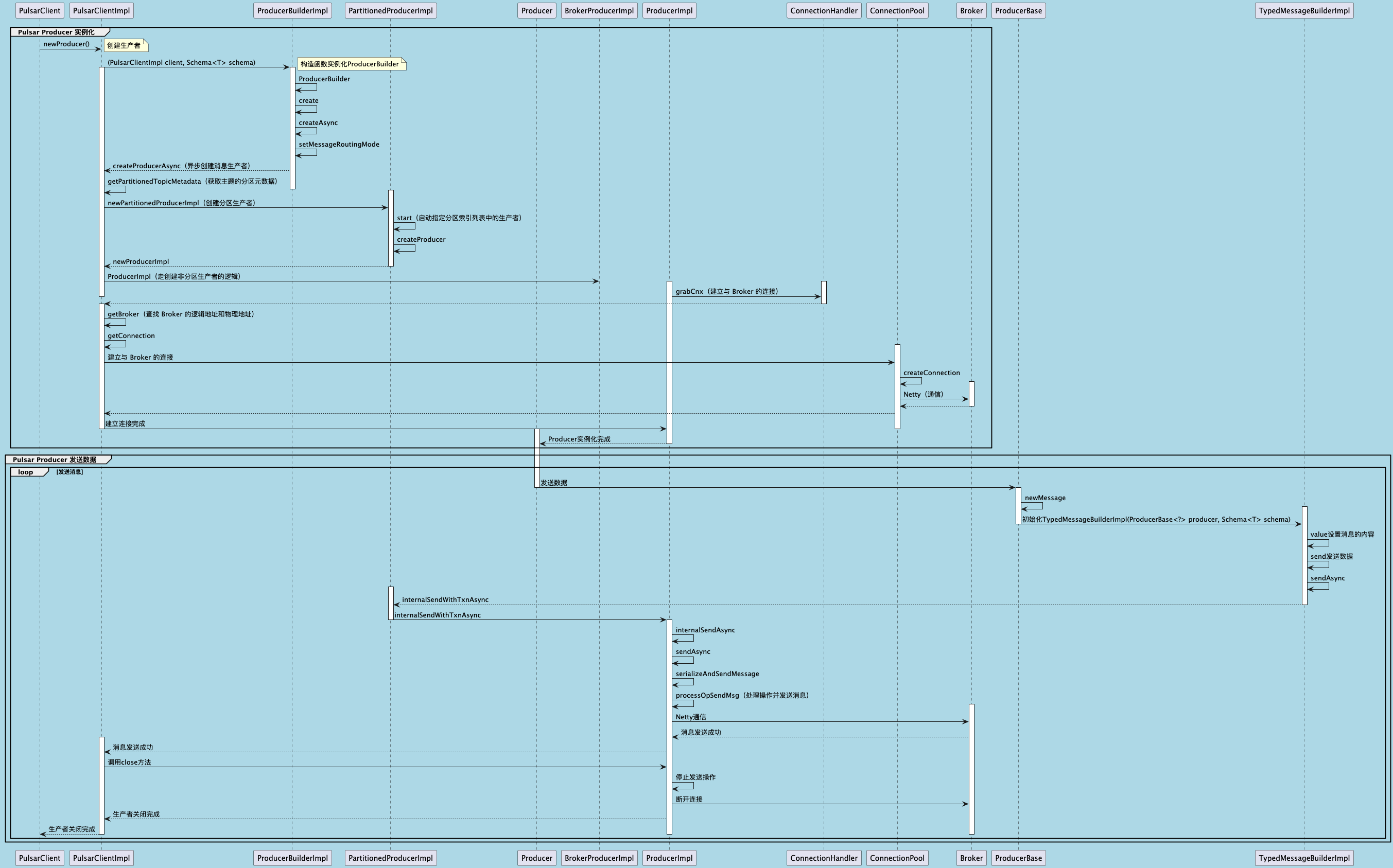

聊聊 Pulsar:Producer 源码解析

一、前言 Apache Pulsar 是一个企业级的开源分布式消息传递平台,以其高性能、可扩展性和存储计算分离架构在消息队列和流处理领域独树一帜。在 Pulsar 的核心架构中,Producer(生产者) 是连接客户端应用与消息队列的第一步。生产者…...

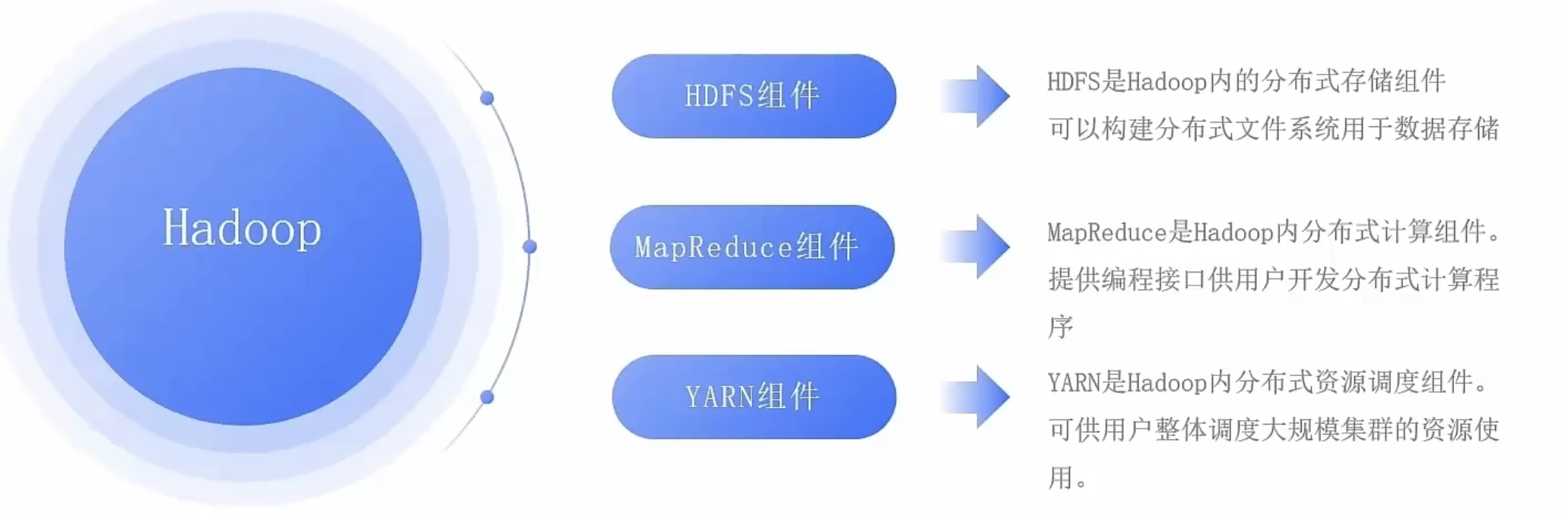

大数据零基础学习day1之环境准备和大数据初步理解

学习大数据会使用到多台Linux服务器。 一、环境准备 1、VMware 基于VMware构建Linux虚拟机 是大数据从业者或者IT从业者的必备技能之一也是成本低廉的方案 所以VMware虚拟机方案是必须要学习的。 (1)设置网关 打开VMware虚拟机,点击编辑…...

c#开发AI模型对话

AI模型 前面已经介绍了一般AI模型本地部署,直接调用现成的模型数据。这里主要讲述讲接口集成到我们自己的程序中使用方式。 微软提供了ML.NET来开发和使用AI模型,但是目前国内可能使用不多,至少实践例子很少看见。开发训练模型就不介绍了&am…...

智能仓储的未来:自动化、AI与数据分析如何重塑物流中心

当仓库学会“思考”,物流的终极形态正在诞生 想象这样的场景: 凌晨3点,某物流中心灯火通明却空无一人。AGV机器人集群根据实时订单动态规划路径;AI视觉系统在0.1秒内扫描包裹信息;数字孪生平台正模拟次日峰值流量压力…...

论文笔记——相干体技术在裂缝预测中的应用研究

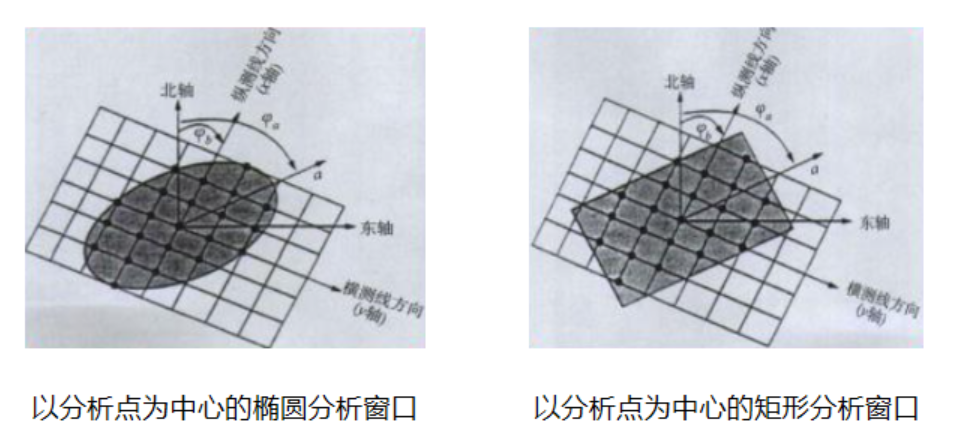

目录 相关地震知识补充地震数据的认识地震几何属性 相干体算法定义基本原理第一代相干体技术:基于互相关的相干体技术(Correlation)第二代相干体技术:基于相似的相干体技术(Semblance)基于多道相似的相干体…...

【Android】Android 开发 ADB 常用指令

查看当前连接的设备 adb devices 连接设备 adb connect 设备IP 断开已连接的设备 adb disconnect 设备IP 安装应用 adb install 安装包的路径 卸载应用 adb uninstall 应用包名 查看已安装的应用包名 adb shell pm list packages 查看已安装的第三方应用包名 adb shell pm list…...

R 语言科研绘图第 55 期 --- 网络图-聚类

在发表科研论文的过程中,科研绘图是必不可少的,一张好看的图形会是文章很大的加分项。 为了便于使用,本系列文章介绍的所有绘图都已收录到了 sciRplot 项目中,获取方式: R 语言科研绘图模板 --- sciRplothttps://mp.…...

)

uniapp 集成腾讯云 IM 富媒体消息(地理位置/文件)

UniApp 集成腾讯云 IM 富媒体消息全攻略(地理位置/文件) 一、功能实现原理 腾讯云 IM 通过 消息扩展机制 支持富媒体类型,核心实现方式: 标准消息类型:直接使用 SDK 内置类型(文件、图片等)自…...