Xilinx FPGA DDR4 接口的 PCB 准则

目录

1. 简介

1.1 FPGA-MIG 与 DDR4 介绍

1.2 DDR4 信号介绍

1.2.1 Clock Signals

1.2.2 Address and Command Signals

1.2.3 Control Signals

1.2.4 Data Signals

1.2.5 Other Signals

2. 通用存储器布线准则

3. Xilinx FPGA-MIG 的 PCB 准则

3.1 引脚配置

3.1.1 Bank/Byte Planner

3.1.2 Signal Group

3.1.3 自动分配信号组

3.1.4 DRC 检查

3.1.5 引脚交换

3.1.5.1 DQS/DQ/DM 位置

3.1.5.2 成对使用x4组件

3.1.5.3 数据字节通道

3.1.5.4 地址/控制信号

3.1.5.5 RDIMMs和UDIMMs

3.1.5.6 VRP 引脚

3.1.5.7 时钟引脚

3.1.5.8 reset_n 引脚

3.1.5.9 Bank 共享

3.1.5.10 Column要求

3.1.5.11 SLR 要求

3.1.5.12 接口上限

3.1.5.13 不允许跳过 Bank

3.1.5.14 GCIO 引脚

3.1.5.15 VREF 引脚

3.1.5.16 相同类型 Bank

3.1.5.17 PAR 引脚

3.1.5.18 sys_rst_n 引脚

3.1.6 引脚分配示例

3.2 《UG575》Pinouts

3.2.1 FFVB676 Bank Diagram

3.2.2 Multi−Function I/O Pins

3.2.3 Pinout Files

3.3 布线准则

3.3.1 Fly-by(飞跃式)

3.3.2 Clamshell(贝壳式)

4. 总结

5. 参考资料

1. 简介

1.1 FPGA-MIG 与 DDR4 介绍

DDR4

DDR 的全称是 DDR SDRAM(Double Data Rate Synchronous Dynamic Random Access Memory),即双倍数据传输率的同步动态随机存取存储器。

- DDR - 即双倍的意思。DDR 内存采用了双倍数据传输率的技术,即在每个时钟周期内可以传输两次数据,相比于传统的 SDRAM,DDR 内存的数据传输速度是提升了一倍的。

- Synchronous - 表示内存与系统时钟同步工作,数据传输在时钟的控制下进行。

- Dynamic - 表示内存是动态随机存取存储器,需要定期刷新以保持数据的存储状态。与之相对的是静态存储器(SRAM),SRAM 速度更快、功耗更高,但相对稳定且不需要定期刷新。

- RAM - 随机存取存储器,其对立面是 Sequential Access Memory(顺序存取存储器),包括:磁带、光盘、磁盘。

FPGA-MIG

Memory Controller - 控制器接受来自用户接口的突发事务,并生成与 SDRAM 之间的事务。控制器负责处理 SDRAM 的时序参数和刷新。它合并写入和读取事务,以减少在转换总线时涉及的死周期数量。控制器还重新排序命令,以改善数据总线到SDRAM的利用率。

Physical Layer - 物理层为 SDRAM 提供高速接口。该层包括 FPGA 内的硬块和软件块校准逻辑,以确保硬块与 SDRAM 接口的时序最佳。

Application Interface - 用户接口层为应用程序提供类似 FIFO 的简单接口。数据被缓冲,读取的数据按照请求顺序呈现。

1.2 DDR4 信号介绍

1.2.1 Clock Signals

ck_t, ck_c - 差分时钟

1.2.2 Address and Command Signals

a[17,13:0] - 地址输入

ras_n/a[16] - 行地址选通,地址位 16

cas_n/a[15] - 列地址选通,地址位 15

we_n/a[14] - 写入使能,地址位 14

bg[1:0] - Bank 组输入

ba[1:0] - Bank 地址输入

act_n - Activation command input(激活命令输入)

par - Command and address parity input(命令和地址奇偶校验输入)

1.2.3 Control Signals

cke - 时钟使能

cs_n[3:0] - 芯片选择

odt - On-die termination enable

reset_n

1.2.4 Data Signals

dq[79:0] - 数据输入/输出

dqs_t/dqs_c[9:0] - Data strobe (differential),数据选通 (差分)

dm_n/dbi_n - Data mask and data bus inversion(数据掩码和数据总线反转)

1.2.5 Other Signals

TEN - Test connectivity mode. CMOS level. Connect 500Ω resistor to ground at memory devices。测试连接模式。 CMOS 级别。将 500Ω 电阻连接到位于存储器器件处的接地。

alert_n

VRP (PL) - 240Ω to GND

ZQ (PS) - 240Ω to GND

2. 通用存储器布线准则

1. 判定信号走线长度时,请在布线约束内包含封装延迟。如可设置封装延迟的最小值和最大值,请使用最小值与最大值之间的中段值。

2. 总线内的最短信号和最长信号必须在列示的规范范围内。

3. 总线中最长地址信号与最短地址之间的延迟之差不得超过 2ps。

4. DDR4 组件接口的 CK 到 DQS 规范范围很大。目的是为了确保在所有存储器器件上从器件链的首个器件到最后一个器件间实现适当的写平衡。

5. 对于飞越式布线,可将地址信号、命令信号和控制信号布线于不同层级上,但建议尽可能少用此方法。请勿将任一信号布线在 2 个以上层级上,这样可最大限度减少可能导致串扰问题的感应环路。任何跨信号层的过孔都需在50 mil 周边范围存储器在 1 个接地过孔。

3. Xilinx FPGA-MIG 的 PCB 准则

3.1 引脚配置

3.1.1 Bank/Byte Planner

如果设计中存在 UltraScale 架构的 Memory IP,则包含启动内存 Bank/Byte 规划工具。

Memory Bank/Byte Planner

3.1.2 Signal Group

点击 Show Signal Group 按钮,以在 Signal Groups 对话框中显示每个 Memory IP 的信号组列表。

Signal Group 显示当前配置的 DDR 所有的信号线。

3.1.3 自动分配信号组

3.1.4 DRC 检查

在分配或修改管脚分配后,必须运行 DRC 检查。

运行 DRC 是管脚规划中最关键的步骤之一。DRC 会根据一套特定的设计规则检查(称为规则集)来检查当前设计,并报告任何错误或违规情况。

在 I/O Planning 期间,Vivado 执行基本检查以确保合法的引脚布局。然而,完整的签名 DRC 只在Vivado 实施期间运行。因此,需要通过 Vivado 实施来确保最终合法的引脚布局。

交互式 I/O Placement Routines,在引脚放置期间检查常见的错误情况。可以在 General tab of the Package window 的常规标签中使用 Autocheck I/O Placement 复选框来开启或关闭此功能。

当启用自动检查时,该工具不允许在会引起设计问题的引脚上放置 I/O 端口。在 Place I/O Ports Sequentially 模式下,如果尝试在有问题的引脚上放置一个I/O端口,会出现一个工具提示,描述为什么 I/O 端口不能被放置。

默认情况下,交互式DRC是启用的。

3.1.5 引脚交换

字节组,包含数据字节组和地址/控制字节组。

- 字节组内可自由交换:

-

数据字节组、地址/控制字节组内的引脚可以自由交换。即,同一字节组内的任何引脚可以相互交换位置,但有一个例外:DQS 必须位于其所在 nibble 的专用 DQS 上。

-

- 字节组间交换:

- 数据字节组、地址/控制字节组之间可以交换。

- 地址/控制字节组的交换:

- 地址/控制字节组内的引脚不仅可以在自己的组内自由交换,还可以与其他地址/控制字节组之间交换。

- 除了上述允许的交换之外,不允许进行其他任何形式的 pin swapping。

3.1.5.1 DQS/DQ/DM 位置

1). 使用x8或x16组件的设计 - dqs必须位于以“U”(N6和N7)指定的上部nibble中的专用字节时钟对上。 与dqs相关的dq必须位于除N1和N12引脚之外的任何其他引脚上的相同字节通道上。

2). 使用x4组件的设计 - dqs必须位于nibble中的专用dqs对上(在下部nibble中的N0和N1,在上部nibble中的N6和N7)。 与dqs相关的dq必须位于除引脚N12(上部nibble)之外的任何其他引脚上的相同nibble中。

3). 如果使用dm,必须将其放置在与相应dqs对应的字节通道的引脚N0上。 当dm被禁用时,引脚N0可以用于dq,但不能用于地址/控制信号。 当不使用dm时,引脚N0不能用于地址/控制(除了reset#引脚)。注意:x4设备不支持dm。

4). 如果未使用dm,则必须在PCB上将其拉低。 用于这一目的的典型值等于DQ线传输阻抗,例如40或50Ω。 请咨询内存供应商以获得他们的具体建议。 如果未适当拉低,则可能导致不可预测的故障。

3.1.5.2 成对使用x4组件

x4组件必须成对使用。 不允许使用奇数个x4组件。 数据字节的上半字节和下半字节都必须由一个x4 dq/dqs组占用。

3.1.5.3 数据字节通道

带有dqs的字节通道被视为数据字节通道(Data Byte Lanes)。 引脚N1和N12可以在数据字节通道中用于地址/控制。 如果数据字节位于与其余地址/控制引脚相同的存储器bank中,请参阅3.1.5.4。

3.1.5.4 地址/控制信号

地址/控制信号可以位于地址/控制字节通道中的任何13个引脚中。 地址/控制信号必须包含在同一个存储器bank中。

3.1.5.5 RDIMMs和UDIMMs

对于RDIMMs和UDIMMs的双插槽配置:cs、odt、cke和ck端口宽度加倍。 有关信号的确切映射,请参阅DIMM配置。

3.1.5.6 VRP 引脚

- 每个I/O bank需要一个VRP引脚:每个I/O bank都需要一个VRP引脚,并且DCI(数字校准接口)是接口所必需的。

- 输入和输出bank都需要VRP引脚:不仅包含输入的I/O bank需要VRP引脚,只有输出的I/O bank也需要VRP引脚。这是因为地址/控制信号使用SSTL15_DCI/SSTL135_DCI标准,以实现受控输出阻抗。

- 允许DCI级联:当选择DCI级联时,VRP引脚可以作为普通I/O使用。

- 遵循UG571中的DCI规则:必须遵循UltraScale™架构SelectIO™资源用户指南(UG571)中的所有DCI规则。

3.1.5.7 时钟引脚

时钟(ck)对必须位于地址/控制字节通道中的任何PN对中。

3.1.5.8 reset_n 引脚

reset_n 可以位于任何引脚,只要满足一般互连时序要求,并且 I/O 标准必须是SSTL15。 重置DRAM 应该被拉低,以便在上电期间保持低电平。 当dm被禁用时,重置引脚可以分配给数据字节通道的第N0引脚或该字节通道的任何其他空闲引脚,只要不违反其他规则。

3.1.5.9 Bank 共享

Bank 可以在两个控制器之间共享。

1). 每个字节通道专用于特定的控制器(除了reset_n)。

2). 来自一个控制器的字节通道不能放置在另一个控制器内。 例如,对于控制器A和B,“AABB”是允许的,而“ABAB”是不允许的。

3.1.5.10 Column要求

内存接口使用的所有I/O bank必须位于同一列(column)中。

3.1.5.11 SLR 要求

内存接口使用的所有I/O bank必须位于SSI技术设备的同一列的同一SLR中。

SLR(Super Logic Region):是 SSI 技术设备中的一个逻辑区域。每个SLR可以看作是一个独立的小规模FPGA。多个SLR通过一个被动的硅中介层(Interposer)连接在一起。

SSI(Stacked Silicon Interconnect):堆叠硅互连技术,它允许将多个SLR组件安装在一个被动的硅中介层上。相比传统设备,SSI技术使得Xilinx能够构建更大规模的FPGA设备。所有用于内存接口的I/O bank必须位于同一列的同一个SLR中。这是为了确保信号传输的效率和一致性。

3.1.5.12 接口上限

接口的最大高度为五个连续的bank。 支持的最大接口宽度为80位。 组件的最大限制为九个,此限制仅适用于组件,而不适用于DIMMs。

3.1.5.13 不允许跳过 Bank

- 不能跳过bank连接:例如,如果你有bank 64、65、66、67,你不能跳过bank 65直接连接bank 64和bank 66。

- 连续连接:所有需要连接的I/O bank必须是连续的,没有中间空缺的bank。

这个规则确保了信号传输的完整性,避免了由于跳过bank而可能引起的信号完整性问题。

3.1.5.14 GCIO 引脚

接口中 MMCM 的输入时钟必须来自用于内存接口的 I/O column 中的 GCIO pair。

3.1.5.15 VREF 引脚

有专用的 VREF 引脚, 可以使用内部或外部VREF。 如果不使用外部VREF,则必须通过UltraScale™ Architecture SelectIO™资源用户指南(UG571)中指定的电阻值将VREF引脚拉到地。 这些引脚必须根据使用的标准进行适当连接。

3.1.5.16 相同类型 Bank

接口必须包含在相同类型的 I/O bank(高范围或高性能)中。 不允许混合不同类型的 bank,除了第7步中提到的 reset_n 和第12步中提到的输入时钟之外。

3.1.5.17 PAR 引脚

对于DDR3 RDIMMs,par引脚是必需的。

3.1.5.18 sys_rst_n 引脚

如果字节用于内存 I/O,则系统复位引脚(sys_rst_n)不得分配给 N0 和 N6 引脚。

3.1.6 引脚分配示例

Byte Lane View of Bank on FPGA Die for x8 and x16 Support

| I/O Type | Byte Lane | Pin Number | Signal Name |

| - | T0U | N12 | - |

| N | T0U | N11 | DQ[7:0] |

| P | T0U | N10 | DQ[7:0] |

| N | T0U | N9 | DQ[7:0] |

| P | T0U | N8 | DQ[7:0] |

| DQSCC-N | T0U | N7 | DQS0_N |

| DQSCC-P | T0U | N6 | DQS0_P |

| N | T0L | N5 | DQ[7:0] |

| P | T0L | N4 | DQ[7:0] |

| N | T0L | N3 | DQ[7:0] |

| P | T0L | N2 | DQ[7:0] |

| DQSCC-N | T0L | N1 | - |

| DQSCC-P | T0L | N0 | DM0 |

3.2 《UG575》Pinouts

《UltraScale(+) FPGAs Packaging and Pinouts Product Specification UG (UG575)》

3.2.1 FFVB676 Bank Diagram

FFVB676 (XCKU3P and XCKU5P)

3.2.2 Multi−Function I/O Pins

3.2.3 Pinout Files

UltraScale and UltraScale+ Package Device Pinout Files![]() https://www.xilinx.com/support/package-pinout-files/ultrascale-pkgs.html

https://www.xilinx.com/support/package-pinout-files/ultrascale-pkgs.html

T - Tile,拼块,通常指的是一个逻辑单元的集合,这些单元在物理上相邻并且在功能上相关。

命名规则:

# 差分

IO_L[1-24][P/N]_T[0-3 ] [U/L]_N[0-12]_ [multi-function]_[bank number]# 单端

IO_T[0-3 ][U/L]_N[0-12]_[multi-function]_[bank number]- 大多数用户 I/O 引脚都支持差分信号并且可以成对实现。

- IO表示用户I/O引脚。

- L[1-24] 表示 I/O 引脚是差分对。没有L表示 I/O 引脚是单端的。

- T[0-3][U/L] 表示为引脚分配的字节组和该组内的半字节位置(上部或下部)。

- N[0-12] 其字节组内 I/O 的数量。

- [multi-function] 表示该引脚可以提供的其他功能。

- [bank number] 表示为用户 I/O 引脚分配的 Bank。

AD[0-15][P/N]

系统监视器差分辅助模拟输入0-15。

GC or HDGC

每个组中有四个全局时钟 (GC) 引脚对。 HDGC 引脚可以直接访问全局时钟缓冲区。 GC 引脚可以直接访问位于同一 I/O Bank 的时钟管理块 (CMT) 中的全局时钟缓冲器、MMCM 和 PLL。 GC 和 HDGC 输入提供对内部全局和区域时钟资源的专用高速访问。 GC 和 HDGC 输入使用专用路由,并且必须用于时钟输入,其中各种时钟功能的时序是必需的。 GC 或 HDGC 引脚在不用作输入时钟时可被视为用户 I/O。

DBC or QBC

字节通道时钟(DBC 和 QBC)输入引脚对是直接将源同步时钟驱动到 I/O Bank 中位片的时钟输入。在内存应用中,这些也称为 DQS。

PERSTN[0-1]

PCI Express 集成块的默认复位引脚位置。

3.3 布线准则

3.3.1 Fly-by(飞跃式)

飞越式拓扑是将所有存储器器件都包含在单一层级内,通常采用直插方式,布线更便于且提供最佳信号完整性,但可能占用较多开发板空间。

3.3.2 Clamshell(贝壳式)

贝壳拓扑具有开发板占用空间更小等优势,但存储器器件封装管脚位置不对称可能导致布线拥挤,增加串扰风险,因为接地回路过孔少且走线更长。

4. 总结

本文档提供了关于FPGA-MIG和DDR4内存的详细介绍,包括其工作原理、关键信号、以及与之相关的PCB设计准则。DDR4作为目前广泛使用的内存技术,其特点包括高速数据传输和同步工作机制,而FPGA-MIG则为这些内存提供了高效的控制和接口,确保数据传输的稳定性和高效性。文档还详细讨论了DDR4的信号类型,包括时钟信号、地址和命令信号以及数据信号等,这对于理解DDR4的工作机制至关重要。在PCB设计方面,本文档提供了关于如何布线和引脚分配的准则,旨在帮助设计师优化内存与FPGA之间的连接,以及提高整体系统的性能和可靠性。通过遵循这些准则,可以在设计高性能电子系统时,确保内存接口的稳定性和效率。

5. 参考资料

1. UG583 - 《UltraScale 架构 PCB 设计》

UltraScale Architecture PCB Design User Guide (UG583)![]() https://docs.amd.com/r/en-US/ug583-ultrascale-pcb-design/UltraScale-Architecture-PCB-Design-User-Guide

https://docs.amd.com/r/en-US/ug583-ultrascale-pcb-design/UltraScale-Architecture-PCB-Design-User-Guide

2. PG150 - 《基于UltraScale架构的FPGA存储IP产品指南》

UltraScale Architecture-Based FPGAs Memory IP Product Guide (PG150)![]() https://docs.amd.com/v/u/en-US/pg150-ultrascale-memory-ip3. UG899 -《I/O 和时钟规划》

https://docs.amd.com/v/u/en-US/pg150-ultrascale-memory-ip3. UG899 -《I/O 和时钟规划》

Vivado Design Suite User Guide: I/O and Clock Planning (UG899)![]() https://docs.amd.com/r/en-US/ug899-vivado-io-clock-planning/Introduction4. UG575 - 《Packaging and Pinouts》

https://docs.amd.com/r/en-US/ug899-vivado-io-clock-planning/Introduction4. UG575 - 《Packaging and Pinouts》

Us(+) FPGAs Packaging and Pinouts Product Specification UG (UG575)![]() https://0x04.net/~mwk/xidocs/ug/ug575-ultrascale-pkg-pinout.pdf5. UG571 - 《UltraScale Architecture SelectIO Resources》

https://0x04.net/~mwk/xidocs/ug/ug575-ultrascale-pkg-pinout.pdf5. UG571 - 《UltraScale Architecture SelectIO Resources》

UltraScale Architecture SelectIO Resources User Guide (UG571)![]() https://docs.amd.com/r/en-US/ug571-ultrascale-selectio/I/O-Tile-Overview

https://docs.amd.com/r/en-US/ug571-ultrascale-selectio/I/O-Tile-Overview

相关文章:

Xilinx FPGA DDR4 接口的 PCB 准则

目录 1. 简介 1.1 FPGA-MIG 与 DDR4 介绍 1.2 DDR4 信号介绍 1.2.1 Clock Signals 1.2.2 Address and Command Signals 1.2.3 Control Signals 1.2.4 Data Signals 1.2.5 Other Signals 2. 通用存储器布线准则 3. Xilinx FPGA-MIG 的 PCB 准则 3.1 引脚配置 3.1.1 …...

神经网络 | Transformer 基本原理

目录 1 为什么使用 Transformer?2 Attention 注意力机制2.1 什么是 Q、K、V 矩阵?2.2 Attention Value 计算流程2.3 Self-Attention 自注意力机制2.3 Multi-Head Attention 多头注意力机制 3 Transformer 模型架构3.1 Positional Encoding 位置编…...

浅析 VO、DTO、DO、PO 的概念

文章目录 I 浅析 VO、DTO、DO、PO1.1 概念1.2 模型1.3 VO与DTO的区别I 浅析 VO、DTO、DO、PO 1.1 概念 VO(View Object) 视图对象,用于展示层,它的作用是把某个指定页面(或组件)的所有数据封装起来。DTO(Data Transfer Object): 数据传输对象,这个概念来源于J2EE的设…...

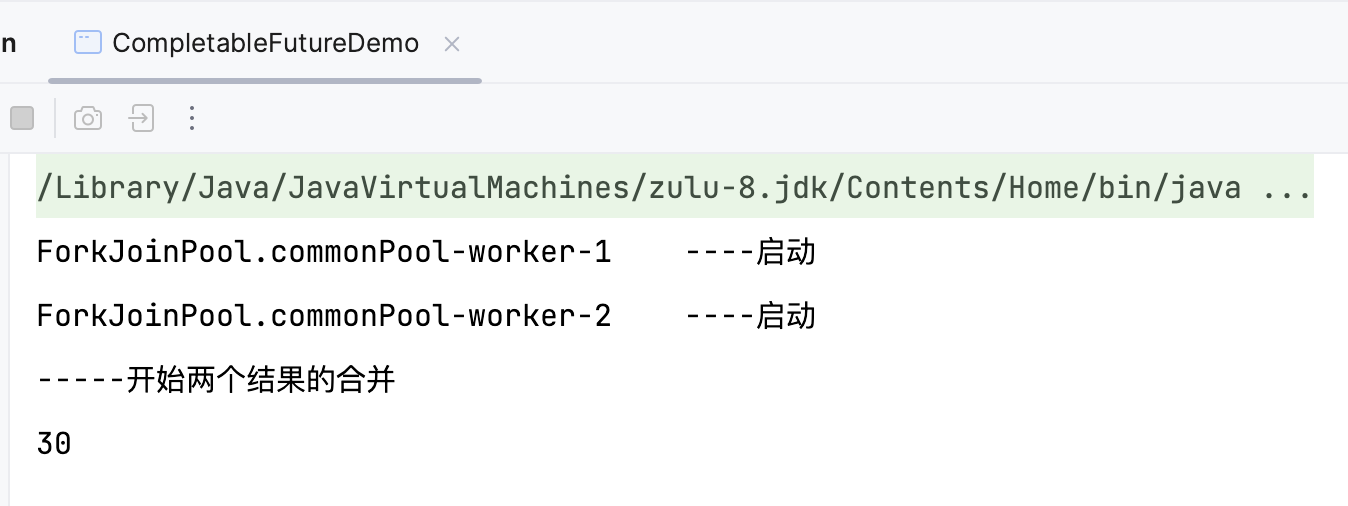

7.8 CompletableFuture

Future 接口理论知识复习 Future 接口(FutureTask 实现类)定义了操作异步任务执行的一些方法,如获取异步任务的执行结果、取消任务的执行、判断任务是否被取消、判断任务执行是否完毕等。 比如主线程让一个子线程去执行任务,子线…...

iPad锁屏密码忘记怎么办?有什么方法可以解锁?

当我们在日常使用iPad时,偶尔可能会遇到忘记锁屏密码的尴尬情况。这时,不必过于担心,因为有多种方法可以帮助您解锁iPad。接下来,小编将为您详细介绍这些解决方案。 一、使用iCloud的“查找我的iPhone”功能 如果你曾经启用了“查…...

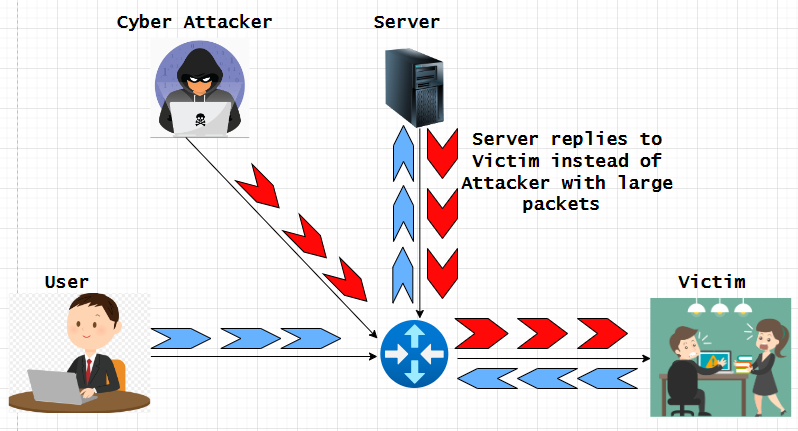

了解并缓解 IP 欺骗攻击

欺骗是黑客用来未经授权访问计算机或网络的一种网络攻击,IP 欺骗是其他欺骗方法中最常见的欺骗类型。通过 IP 欺骗,攻击者可以隐藏 IP 数据包的真实来源,使攻击来源难以知晓。一旦访问网络或设备/主机,网络犯罪分子通常会挖掘其中…...

java LogUtil输出日志打日志的class文件内具体方法和行号

最近琢磨怎么把日志打的更清晰,方便查找问题,又不需要在每个class内都创建Logger对象,还带上不同的颜色做区分,简直不要太爽。利用堆栈的方向顺序拿到日志的class问题。看效果,直接上代码。 1、demo test 2、输出效果…...

02. Hibernate 初体验之持久化对象

1. 前言 本节课程让我们一起体验 Hibernate 的魅力!编写第一个基于 Hibernate 的实例程序。 在本节课程中,你将学到 : Hibernate 的版本发展史;持久化对象的特点。 为了更好地讲解这个内容,这个初体验案例分上下 2…...

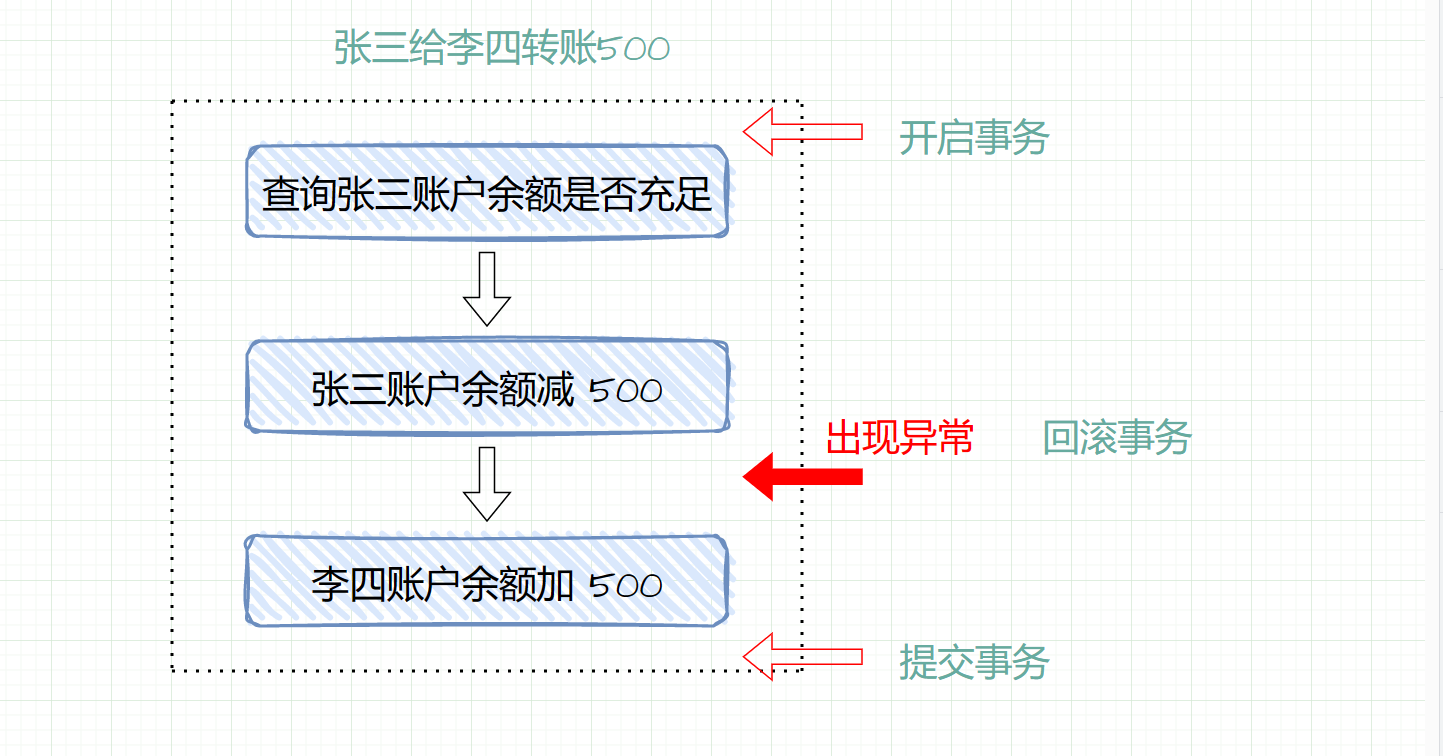

MySQL超详细学习教程,2023年硬核学习路线

文章目录 前言1. 数据库的相关概念1.1 数据1.2 数据库1.3 数据库管理系统1.4 数据库系统1.5 SQL 2. MySQL数据库2.1 MySQL安装2.2 MySQL配置2.2.1 添加环境变量2.2.2 新建配置文件2.2.3 初始化MySQL2.2.4 注册MySQL服务2.2.5 启动MySQL服务 2.3 MySQL登录和退出2.4 MySQL卸载2.…...

初识SpringBoot

1.Maven Maven是⼀个项⽬管理⼯具, 通过pom.xml⽂件的配置获取jar包,⽽不⽤⼿动去添加jar包 主要功能 项⽬构建管理依赖 构建Maven项目 1.1项目构建 Maven 提供了标准的,跨平台(Linux, Windows, MacOS等)的⾃动化项⽬构建⽅式 当我们开发了⼀个项⽬之后, 代…...

Qt之元对象系统

Qt的元对象系统提供了信号和槽机制(用于对象间的通信)、运行时类型信息和动态属性系统。 元对象系统基于三个要素: 1、QObject类为那些可以利用元对象系统的对象提供了一个基类。 2、在类声明中使用Q_OBJECT宏用于启用元对象特性,…...

Provider(1)- 什么是AudioBufferProvider

什么是AudioBufferProvider? 顾名思义,Audio音频数据缓冲提供,就是提供音频数据的缓冲类,而且这个AudioBufferProvider派生出许多子类,每个子类有不同的用途,至关重要;那它在Android哪个地方使…...

加密与安全_密钥体系的三个核心目标之完整性解决方案

文章目录 Pre机密性完整性1. 哈希函数(Hash Function)定义特征常见算法应用散列函数常用场景散列函数无法解决的问题 2. 消息认证码(MAC)概述定义常见算法工作原理如何使用 MACMAC 的问题 不可否认性数字签名(Digital …...

【C++】:继承[下篇](友元静态成员菱形继承菱形虚拟继承)

目录 一,继承与友元二,继承与静态成员三,复杂的菱形继承及菱形虚拟继承四,继承的总结和反思 点击跳转上一篇文章: 【C】:继承(定义&&赋值兼容转换&&作用域&&派生类的默认成员函数…...

昇思25天学习打卡营第13天|基于MindNLP+MusicGen生成自己的个性化音乐

关于MindNLP MindNLP是一个依赖昇思MindSpore向上生长的NLP(自然语言处理)框架,旨在利用MindSpore的优势特性,如函数式融合编程、动态图功能、数据处理引擎等,致力于提供高效、易用的NLP解决方案。通过全面拥抱Huggin…...

nigix的下载使用

1、官网:https://nginx.org/en/download.html 双击打开 nginx的默认端口是80 配置文件 默认访问页面 在目录下新建pages,放入图片 在浏览器中输入地址进行访问 可以在电脑中配置本地域名 Windows设置本地DNS域名解析hosts文件配置 文件地址…...

)

nginx+lua 实现URL重定向(根据传入的参数条件)

程序版本说明 程序版本URLnginx1.27.0https://nginx.org/download/nginx-1.27.0.tar.gzngx_devel_kitv0.3.3https://github.com/simpl/ngx_devel_kit/archive/v0.3.3.tar.gzluajitv2.1https://github.com/openresty/luajit2/archive/refs/tags/v2.1-20240626.tar.gzlua-nginx-m…...

算法学习笔记(8.4)-完全背包问题

目录 Question: 图例: 动态规划思路 2 代码实现: 3 空间优化: 代码实现: 下面是0-1背包和完全背包具体的例题: 代码实现: 图例: 空间优化代码示例 Question: 给定n个物品…...

陈述)

C++catch (...)陈述

catch (...)陈述 例外处理可以有多个catch,如果catch后的小括弧里面放...,就表示不限型态种类的任何例外。 举例如下 #include <iostream>int main() {int i -1;try {if (i > 0) {throw 0;}throw 2.0;}catch (const int e) {std::cout <…...

Redis实践

Redis实践 使用复杂度高的命令 如果在使用Redis时,发现访问延迟突然增大,如何进行排查? 首先,第一步,建议你去查看一下Redis的慢日志。Redis提供了慢日志命令的统计功能,我们通过以下设置,就…...

铭豹扩展坞 USB转网口 突然无法识别解决方法

当 USB 转网口扩展坞在一台笔记本上无法识别,但在其他电脑上正常工作时,问题通常出在笔记本自身或其与扩展坞的兼容性上。以下是系统化的定位思路和排查步骤,帮助你快速找到故障原因: 背景: 一个M-pard(铭豹)扩展坞的网卡突然无法识别了,扩展出来的三个USB接口正常。…...

vscode里如何用git

打开vs终端执行如下: 1 初始化 Git 仓库(如果尚未初始化) git init 2 添加文件到 Git 仓库 git add . 3 使用 git commit 命令来提交你的更改。确保在提交时加上一个有用的消息。 git commit -m "备注信息" 4 …...

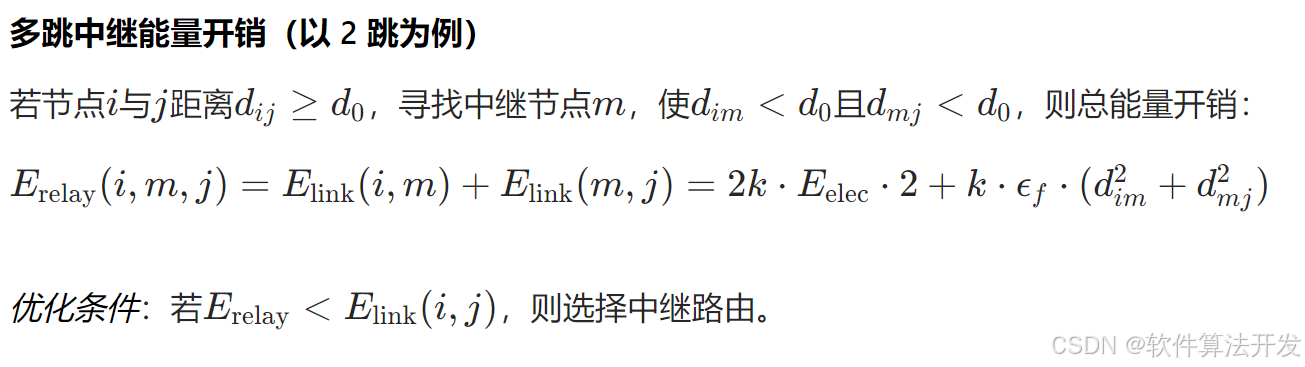

基于距离变化能量开销动态调整的WSN低功耗拓扑控制开销算法matlab仿真

目录 1.程序功能描述 2.测试软件版本以及运行结果展示 3.核心程序 4.算法仿真参数 5.算法理论概述 6.参考文献 7.完整程序 1.程序功能描述 通过动态调整节点通信的能量开销,平衡网络负载,延长WSN生命周期。具体通过建立基于距离的能量消耗模型&am…...

【Oracle】分区表

个人主页:Guiat 归属专栏:Oracle 文章目录 1. 分区表基础概述1.1 分区表的概念与优势1.2 分区类型概览1.3 分区表的工作原理 2. 范围分区 (RANGE Partitioning)2.1 基础范围分区2.1.1 按日期范围分区2.1.2 按数值范围分区 2.2 间隔分区 (INTERVAL Partit…...

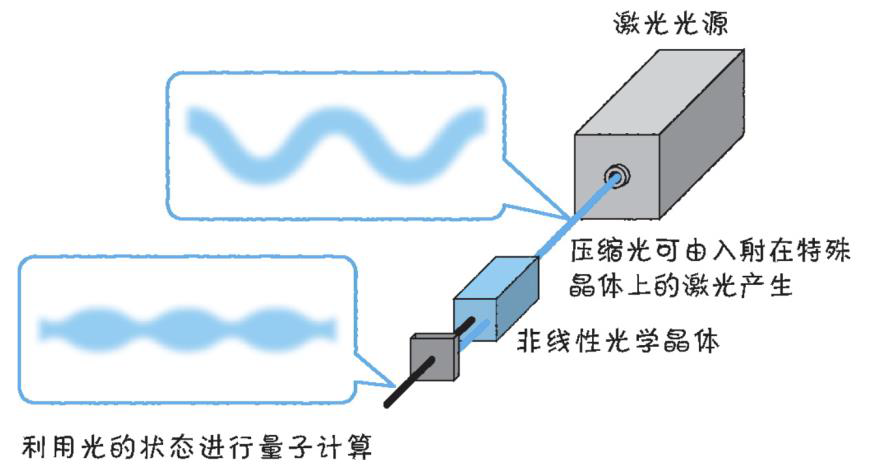

以光量子为例,详解量子获取方式

光量子技术获取量子比特可在室温下进行。该方式有望通过与名为硅光子学(silicon photonics)的光波导(optical waveguide)芯片制造技术和光纤等光通信技术相结合来实现量子计算机。量子力学中,光既是波又是粒子。光子本…...

在Ubuntu24上采用Wine打开SourceInsight

1. 安装wine sudo apt install wine 2. 安装32位库支持,SourceInsight是32位程序 sudo dpkg --add-architecture i386 sudo apt update sudo apt install wine32:i386 3. 验证安装 wine --version 4. 安装必要的字体和库(解决显示问题) sudo apt install fonts-wqy…...

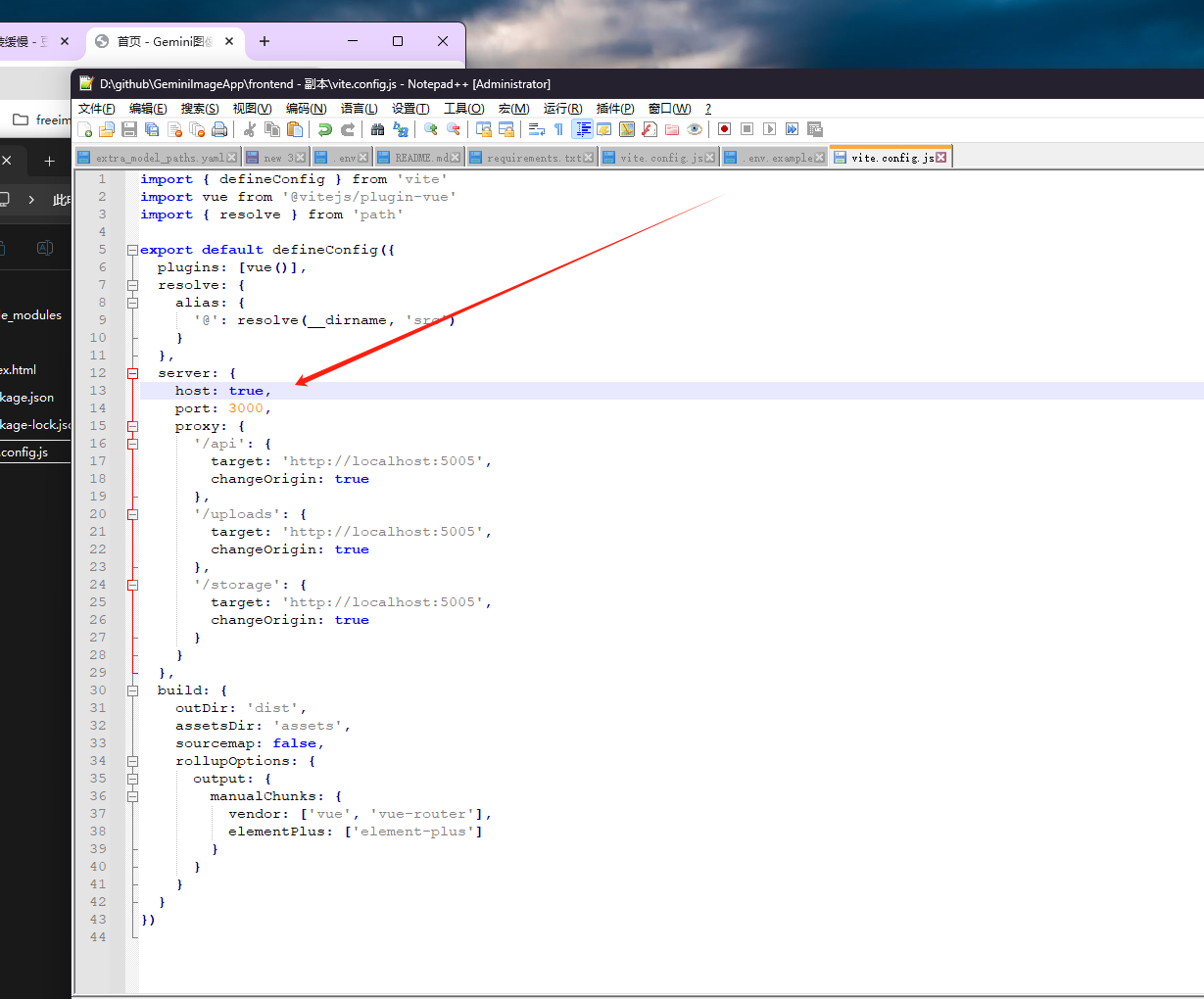

推荐 github 项目:GeminiImageApp(图片生成方向,可以做一定的素材)

推荐 github 项目:GeminiImageApp(图片生成方向,可以做一定的素材) 这个项目能干嘛? 使用 gemini 2.0 的 api 和 google 其他的 api 来做衍生处理 简化和优化了文生图和图生图的行为(我的最主要) 并且有一些目标检测和切割(我用不到) 视频和 imagefx 因为没 a…...

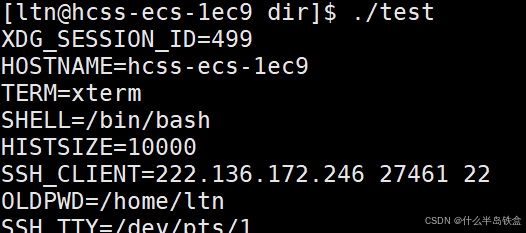

【Linux系统】Linux环境变量:系统配置的隐形指挥官

。# Linux系列 文章目录 前言一、环境变量的概念二、常见的环境变量三、环境变量特点及其相关指令3.1 环境变量的全局性3.2、环境变量的生命周期 四、环境变量的组织方式五、C语言对环境变量的操作5.1 设置环境变量:setenv5.2 删除环境变量:unsetenv5.3 遍历所有环境…...

uniapp 小程序 学习(一)

利用Hbuilder 创建项目 运行到内置浏览器看效果 下载微信小程序 安装到Hbuilder 下载地址 :开发者工具默认安装 设置服务端口号 在Hbuilder中设置微信小程序 配置 找到运行设置,将微信开发者工具放入到Hbuilder中, 打开后出现 如下 bug 解…...

redis和redission的区别

Redis 和 Redisson 是两个密切相关但又本质不同的技术,它们扮演着完全不同的角色: Redis: 内存数据库/数据结构存储 本质: 它是一个开源的、高性能的、基于内存的 键值存储数据库。它也可以将数据持久化到磁盘。 核心功能: 提供丰…...