Artix7系列FPGA实现SDI视频编解码+UDP以太网传输,基于GTP高速接口,提供工程源码和技术支持

目录

- 1、前言

- 工程概述

- 免责声明

- 2、相关方案推荐

- 本博已有的 SDI 编解码方案

- 本博已有的以太网方案

- 本博已有的FPGA图像缩放方案

- 本方案的缩放应用

- 本方案在Xilinx--Kintex系列FPGA上的应用

- 本方案在Xilinx--Zynq系列FPGA上的应用

- 3、详细设计方案

- 设计原理框图

- SDI 输入设备

- Gv8601a 均衡器

- GTP 高速接口-->解串与串化

- SMPTE SD/HD/3G SDI IP核

- BT1120转RGB

- 纯Verilog图像缩放模块详解

- 纯Verilog图像缩放模块使用

- 图像缓存

- UDP协议栈

- UDP视频发送

- UDP协议栈数据发送

- MAC数据缓冲FIFO组

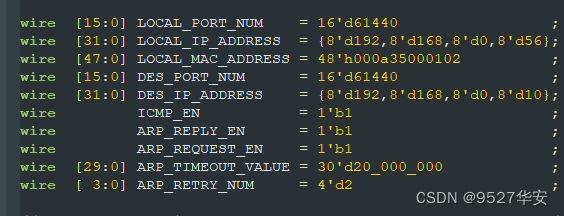

- IP地址、端口号的修改

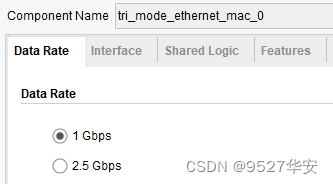

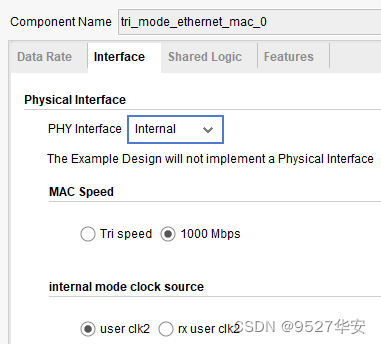

- 以太网网口输出方案-->Tri Mode Ethernet MAC

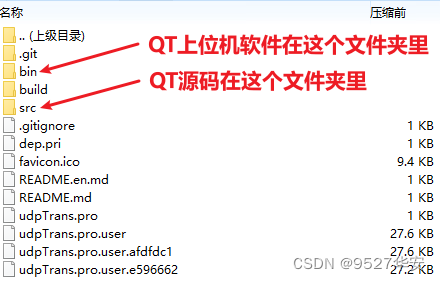

- QT上位机和源码

- 工程源码架构

- 4、工程源码1详解-->PHY芯片以太网输出方案

- 5、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 6、上板调试验证

- 准备工作

- 输出视频演示

- 7、福利:工程代码的获取

Artix7系列FPGA实现SDI视频编解码+UDP以太网传输,基于GTP高速接口,提供工程源码和技术支持

1、前言

目前FPGA实现SDI视频编解码有两种方案:一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971接收器直接将SDI解码为并行的YCrCb422,GS2972发送器直接将并行的YCrCb422编码为SDI视频,缺点是成本较高,可以百度一下GS2971和GS2972的价格;另一种方案是使用FPGA逻辑资源部实现SDI编解码,利用Xilinx系列FPGA的GTP/GTX资源实现解串,利用Xilinx系列FPGA的SMPTE SDI资源实现SDI编解码,优点是合理利用了FPGA资源,GTP/GTX资源不用白不用,缺点是操作难度大一些,对FPGA开发者的技术水平要求较高。有意思的是,这两种方案在本博这里都有对应的解决方案,包括硬件的FPGA开发板、工程源码等等。

工程概述

本设计基于Xilinx的Artix7系列FPGA开发板实现SDI视频编解码+图像缩放+UDP以太网传输,输入源为一个3G-SDI相机或者HDMI转3G-SDI盒子,也可以使用HD-SDI或者SD-SDI相机,因为本设计是三种SDI视频自适应的;同轴的SDI视频通过同轴线连接到FPGA开发板的BNC座子,然后同轴视频经过板载的Gv8601a芯片实现单端转差分和均衡EQ的功能;然后差分SDI视频信号进入FPGA内部的GTP高速资源,实现数据高速串行到并行的转换,本博称之为解串;解串后的并行视频再送入Xilinx系列FPGA特有的SMPTE SD/HD/3G SDI IP核,进行SDI视频解码操作并输出BT1120视频,至此,SDI视频解码操作已经完成,可以进行常规的图像处理操作了;

本设计的目的是做图像缩放后再以UDP以太网输出解码的SDI视频,针对目前市面上的主流项目需求,本博设计了基于传统PHY芯片(B50610)的以太网输出方式;首先对解码BT1120视频进行转RGB和图像缓存操作和图像缩放操作;图像缩放方案采用纯verilog方案将输入的1920x1080视频缩放为1280x720;再使用BT1120转RGB模块实现视频格式转换;再使用本博常用的FDMA图像缓存架构实现图像3帧缓存,缓存介质为板载的DDR3;图像从DDR3读出后,进入UDP视频发送模块,对视频进行自定义协议编码;然后送入UDP协议栈进行UDP以太网帧格式编码;然后输出给MAC层,再输出给物理层,最后通过网线输出给PC上位机;PC端上位机(QT)接收网络视频并显示图像;本博客提供1套工程源码,详情如下:

工程源码1

开发板FPGA型号为Xilinx–>Xilinx-Artix7-100T–xc7a100tfgg484-2;输入视频为3G-SDI相机或者HDMI转3G-SDI盒子,输入分辨率为1920x1080@60Hz,输入视频经过板载的Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过GTP将SDI视频解串为并行数据;再经过SMPTE SDI IP核将SDI解码BT1120数据;再经过BT1120转RGB模块将BT1120转换为RGB888视频;再经过自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为1280x720;再经过自研的FDMA图像缓存方案将视频写入DDR3做三帧缓存;再经过UDP视频发送模块,对视频进行自定义协议编码;再经过UDP协议栈进行UDP以太网帧格式编码;再经过Xilinx官方的Tri Mode Ethernet MAC实现MAC数据发送,输出RGMII接口数据;再经过板载的B50610芯片后以RJ45网口输出;PC端运行QT上位机实时接收视频数据并显示出来;该工程适用于SDI转网络(PHY芯片方案)输出场景;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

本博已有的 SDI 编解码方案

我的博客主页开设有SDI视频专栏,里面全是FPGA编解码SDI的工程源码及博客介绍;既有基于GS2971/GS2972的SDI编解码,也有基于GTP/GTX资源的SDI编解码;既有HD-SDI、3G-SDI,也有6G-SDI、12G-SDI等;专栏地址链接如下:

点击直接前往

本博已有的以太网方案

目前我这里有大量UDP协议的工程源码,包括UDP数据回环,视频传输,AD采集传输等,也有TCP协议的工程,对网络通信有需求的兄弟可以去看看,以下是专栏地址:

直接点击前往

本博已有的FPGA图像缩放方案

我的主页目前有FPGA图像缩放专栏,改专栏收录了我目前手里已有的FPGA图像缩放方案,从实现方式分类有基于HSL实现的图像缩放、基于纯verilog代码实现的图像缩放;从应用上分为单路视频图像缩放、多路视频图像缩放、多路视频图像缩放拼接;从输入视频分类可分为OV5640摄像头视频缩放、SDI视频缩放、MIPI视频缩放等等;以下是专栏地址:

点击直接前往

本方案的缩放应用

本方案有缩放版本的应用,只做SDI视频编解码,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

本方案在Xilinx–Kintex系列FPGA上的应用

本方案在Xilinx–Kintex系列FPGA上的也有应用,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

本方案在Xilinx–Zynq系列FPGA上的应用

本方案在Xilinx–Zynq系列FPGA上的也有应用,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

3、详细设计方案

设计原理框图

设计原理框图如下:

SDI 输入设备

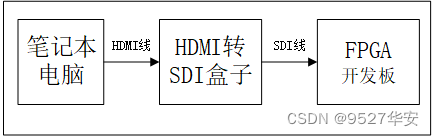

SDI 输入设备可以是SDI相机,代码兼容HD/SD/3G-SDI三种模式;SDI相机相对比较贵,预算有限的朋友可以考虑用HDMI转SDI盒子模拟SDI相机,这种盒子某宝一百块左右;当使用HDMI转SDI盒子时,输入源可以用笔记本电脑,即用笔记本电脑通过HDMI线连接到HDMI转SDI盒子的HDMI输入接口,再用SDI线连接HDMI转SDI盒子的SDI输出接口到FPGA开发板,如下:

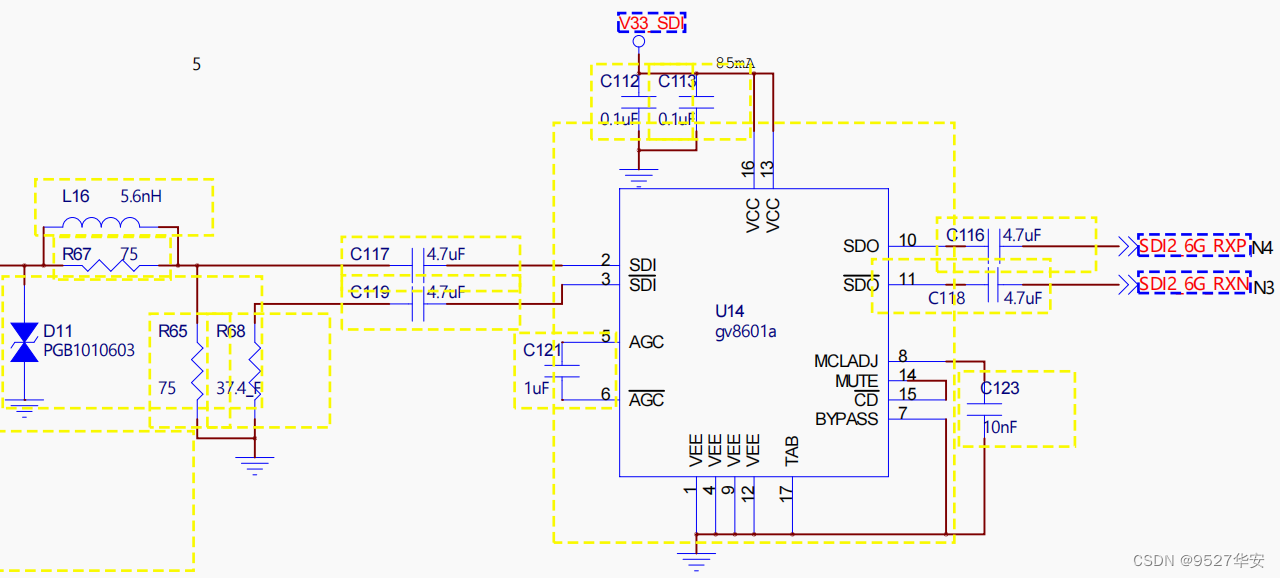

Gv8601a 均衡器

Gv8601a芯片实现单端转差分和均衡EQ的功能,这里选用Gv8601a是因为借鉴了了Xilinx官方的方案,当然也可以用其他型号器件。Gv8601a均衡器原理图如下:

GTP 高速接口–>解串与串化

本设计使用Xilinx特有的GTP高速信号处理资源实现SDI差分视频信号的解串与串化,对于SDI视频接收而言,GTP起到解串的作用,即将输入的高速串行的差分信号解为并行的数字信号;对于SDI视频发送而言,GTP起到串化的作用,即将输入的并行的数字信号串化为高速串行的差分信号;GTP的使用一般需要例化GTP IP核,通过vivado的UI界面进行配置,但本设计需要对SD-SDI、HD-SDI、3G-SDI视频进行自动识别和自适应处理,所以需要使得GTP具有动态改变线速率的功能,该功能可通过DRP接口配置,也可通过GTP的rate接口配置,所以不能使用vivado的UI界面进行配置,而是直接例化GTP的GTPE2_CHANNEL和GTPE2_COMMON源语直接使用GTP资源;此外,为了动态配置GTP线速率,还需要GTP控制模块,该模块参考了Xilinx的官方设计方案,具有动态监测SDI模式,动态配置DRP等功能;该方案参考了Xilinx官方的设计;GTP 解串与串化模块代码架构如下:

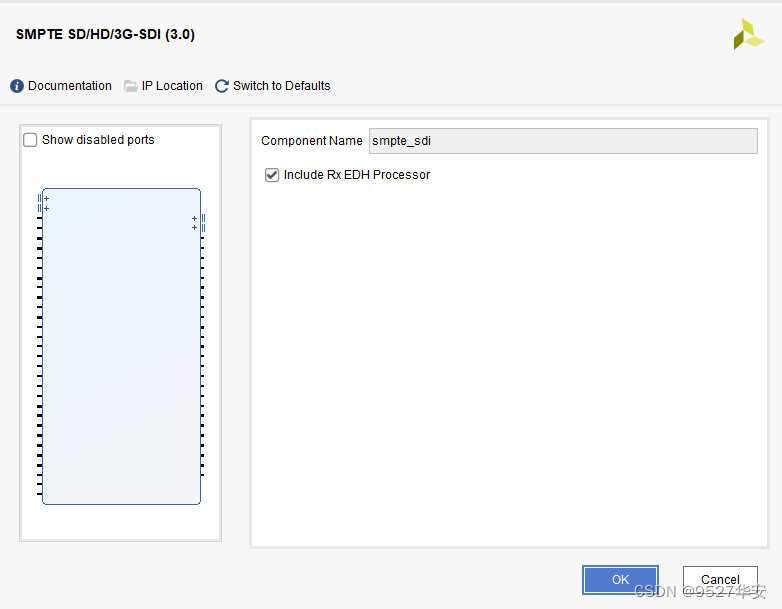

SMPTE SD/HD/3G SDI IP核

SMPTE SD/HD/3G SDI IP核是Xilinx系列FPGA特有的用于SDI视频编解码的IP,该IP配置使用非常简单,vivado的UI界面如下:

SMPTE SD/HD/3G SDI IP核必须与GTP配合才能使用,对于SDI视频接收而言,该IP接收来自于GTP的数据,然后将SDI视频解码为BT1120视频输出,对于SDI视频发送而言,该IP接收来自于用户侧的的BT1120视频数据,然后将BT1120视频编码为SDI视频输出;该方案参考了Xilinx官方的设计;SMPTE SD/HD/3G SDI IP核代码架构如下:

BT1120转RGB

BT1120转RGB模块的作用是将SMPTE SD/HD/3G SDI IP核解码输出的BT1120视频转换为RGB888视频,它由BT1120转CEA861模块、YUV422转YUV444模块、YUV444转RGB888三个模块组成,该方案参考了Xilinx官方的设计;BT1120转RGB模块代码架构如下:

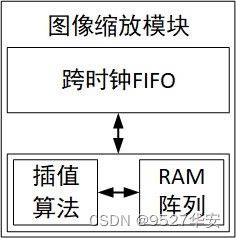

纯Verilog图像缩放模块详解

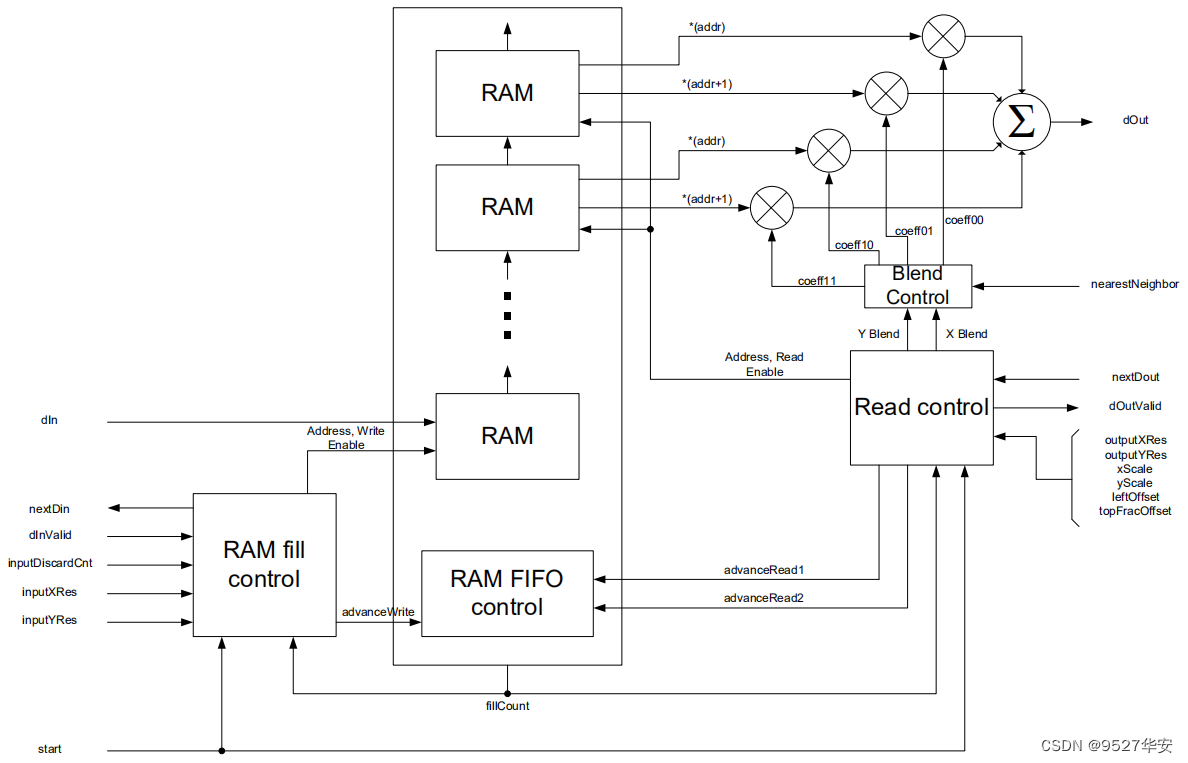

工程源码1、2的图像缩放模块使用纯Verilog方案,功能框图如下,由跨时钟FIFO、插值+RAM阵列构成,跨时钟FIFO的目的是解决跨时钟域的问题,比如从低分辨率视频放大到高分辨率视频时,像素时钟必然需要变大,这是就需要异步FIFO了,插值算法和RAM阵列具体负责图像缩放算法层面的实现;

插值算法和RAM阵列以ram和fifo为核心进行数据缓存和插值实现,设计架构如下:

图像缩放模块代码架构如下:模块的例化请参考工程源码的顶层代码;

图像缩放模块FIFO的选择可以调用工程对应的vivado工具自带的FIFO IP核,也可以使用纯verilog实现的FIFO,可通过接口参数选择,图像缩放模块顶层接口如下:

module helai_video_scale #(//---------------------------Parameters----------------------------------------parameter FIFO_TYPE = "xilinx", // "xilinx" for xilinx-fifo ; "verilog" for verilog-fifoparameter DATA_WIDTH = 8 , //Width of input/output dataparameter CHANNELS = 1 , //Number of channels of DATA_WIDTH, for color imagesparameter INPUT_X_RES_WIDTH = 11 //Widths of input/output resolution control signals

)(input i_reset_n , // 输入--低电平复位信号input [INPUT_X_RES_WIDTH-1:0] i_src_video_width , // 输入视频--即缩放前视频的宽度input [INPUT_X_RES_WIDTH-1:0] i_src_video_height, // 输入视频--即缩放前视频的高度input [INPUT_X_RES_WIDTH-1:0] i_des_video_width , // 输出视频--即缩后前视频的宽度input [INPUT_X_RES_WIDTH-1:0] i_des_video_height, // 输出视频--即缩后前视频的高度input i_src_video_pclk , // 输入视频--即缩前视频的像素时钟input i_src_video_vs , // 输入视频--即缩前视频的场同步信号,必须为高电平有效input i_src_video_de , // 输入视频--即缩前视频的数据有效信号,必须为高电平有效input [DATA_WIDTH*CHANNELS-1:0] i_src_video_pixel , // 输入视频--即缩前视频的像素数据input i_des_video_pclk , // 输出视频--即缩后视频的像素时钟,一般为写入DDR缓存的时钟output o_des_video_vs , // 输出视频--即缩后视频的场同步信号,高电平有效output o_des_video_de , // 输出视频--即缩后视频的数据有效信号,高电平有效output [DATA_WIDTH*CHANNELS-1:0] o_des_video_pixel // 输出视频--即缩后视频的像素数据

);

FIFO_TYPE选择原则如下:

1:总体原则,选择"xilinx"好处大于选择"verilog";

2:当你的FPGA逻辑资源不足时,请选"xilinx";

3:当你图像缩放的视频分辨率较大时,请选"xilinx";

4:当你的FPGA没有FIFO IP或者FIFO IP快用完了,请选"verilog";

5:当你向自学一下异步FIFO时,,请选"verilog";

6:不同FPGA型号对应的工程FIFO_TYPE参数不一样,但选择原则一样,具体参考代码;

2种插值算法的整合与选择

本设计将常用的双线性插值和邻域插值算法融合为一个代码中,通过输入参数选择某一种算法;

具体选择参数如下:

input wire i_scaler_type //0-->bilinear;1-->neighbor

通过输入i_scaler_type 的值即可选择;

输入0选择双线性插值算法;

输入1选择邻域插值算法;

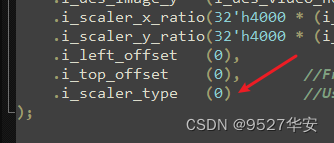

代码里的配置如下:

纯Verilog图像缩放模块使用

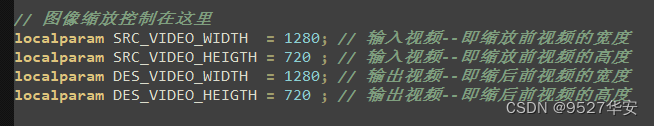

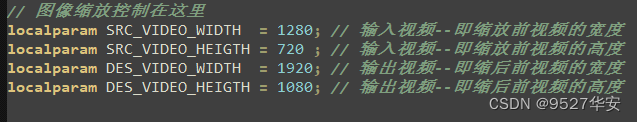

图像缩放模块使用非常简单,顶层代码里设置了四个参数,举例如下:

上图视频通过图像缩放模块但不进行缩放操作,旨在掌握图像缩放模块的用法;如果需要将图像放大到1080P,则修改为如下:

当然,需要修改的不仅仅这一个地方,FDMA的配置也需要相应修改,详情请参考代码,但我想要证明的是,图像缩放模块使用非常简单,你都不需要知道它内部具体怎么实现的,上手就能用;

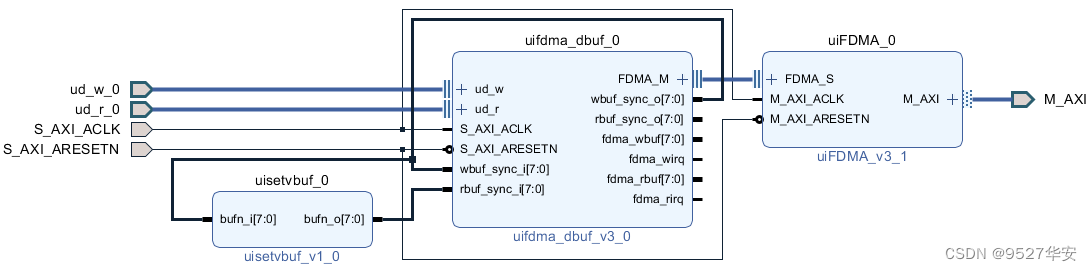

图像缓存

使用本博常用的的FDMA图像缓存架构;缓存介质为DDR3;FDMA图像缓存架构由FDMA、FDMA控制器、缓存帧选择器构成;图像缓存使用Xilinx vivado的Block Design设计,如下图:

关于FDMA更详细的介绍,请参考我之前的博客,博文链接如下:

点击直接前往

需要注意的是,为了适应UDP视频传输,这里的FDMA已被我修改,和以往版本不同,具体参考代码;

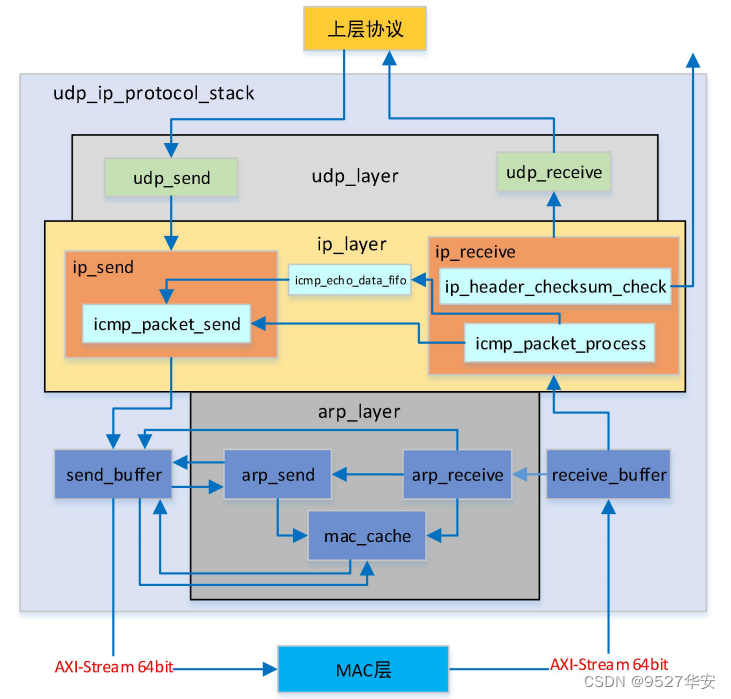

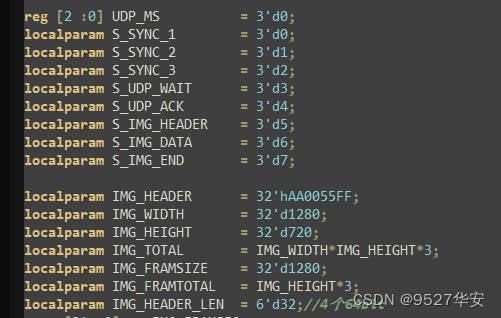

UDP协议栈

本UDP协议栈使用UDP协议栈网表文件,该协议栈目前并不开源,只提供网表文件,虽看不见源码但可正常实现UDP通信,但不影响使用,该协议栈带有用户接口,使得用户无需关心复杂的UDP协议而只需关心简单的用户接口时序即可操作UDP收发,非常简单;协议栈架构如下:

协议栈性能表现如下:

1:支持 UDP 接收校验和检验功能,暂不支持 UDP 发送校验和生成;

2:支持 IP 首部校验和的生成和校验,同时支持 ICMP 协议中的 PING 功能,可接收并响应同一个子网内部设备的 PING 请求;

3:可自动发起或响应同一个子网内设备的 ARP 请求,ARP 收发完全自适应。ARP 表可保存同一个子网内部256 个 IP 和 MAC 地址对;

4:支持 ARP 超时机制,可检测所需发送数据包的目的 IP 地址是否可达;

5:协议栈发送带宽利用率可达 93%,高发送带宽下,内部仲裁机制保证 PING 和 ARP 功能不受任何影响;

6:发送过程不会造成丢包;

7:提供64bit位宽AXI4-Stream形式的MAC接口,可与Xilinx官方的千兆以太网IP核Tri Mode Ethernet MAC,以及万兆以太网 IP 核 10 Gigabit Ethernet Subsystem、10 Gigabit Ethernet MAC 配合使用;

有了此协议栈,我们无需关心复杂的UDP协议的实现了,直接调用接口即可使用。。。

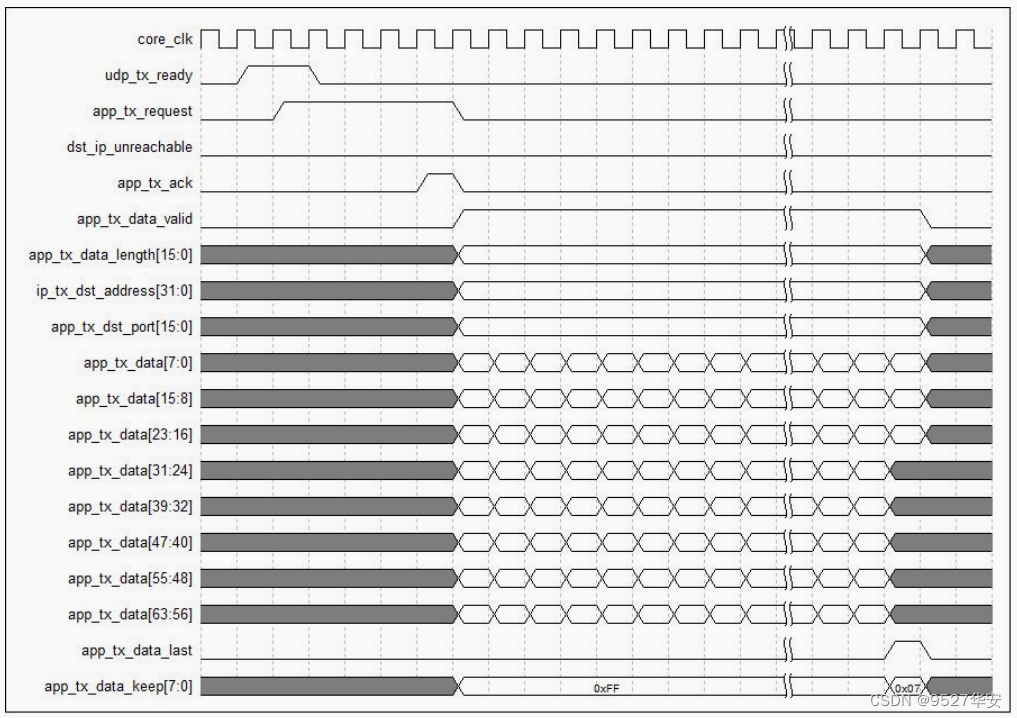

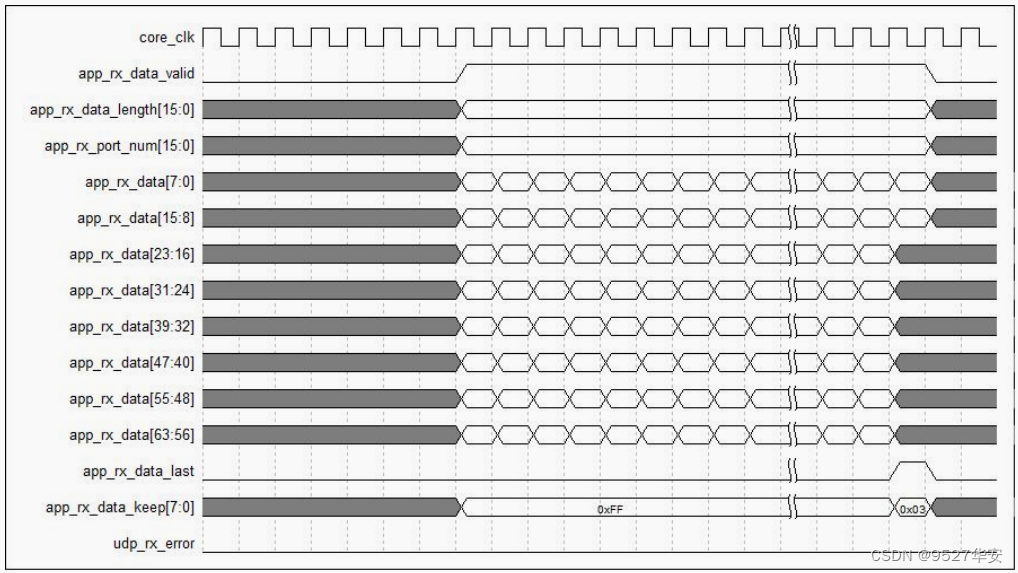

本UDP协议栈用户接口发送时序如下:

本UDP协议栈用户接口接收时序如下:

UDP视频发送

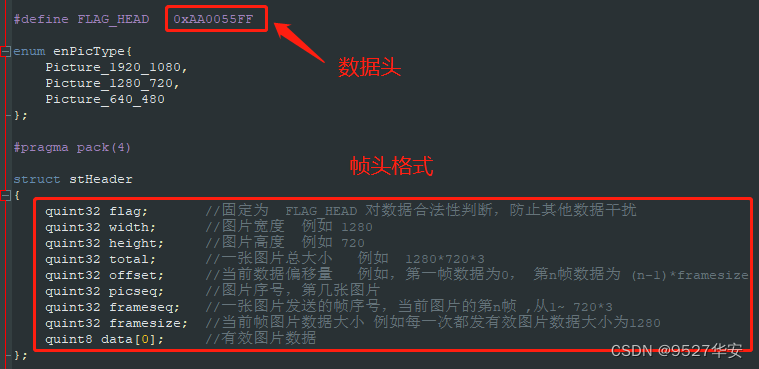

UDP视频发送实现UDP视频数据的组包,UDP数据发送必须与QT上位机的接受程序一致,上位机定义的UDP帧格式包括帧头个UDP数据,帧头定义如下:

FPGA端的UDP数据组包代码必须与上图的数据帧格式对应,否则QT无法解析,代码中定义了数据组包状态机以及数据帧,如下:

另外,由于UDP发送是64位数据位宽,而图像像素数据是24bit位宽,所以必须将UDP数据重新组合,以保证像素数据的对齐,这部分是整个工程的难点,也是所有FPGA做UDP数据传输的难点;

UDP协议栈数据发送

UDP协议栈具有发送和接收功能,但这里仅用到了发送,此部分代码架构如下:

UDP协议栈代码组我已经做好,用户可直接拿去使用;

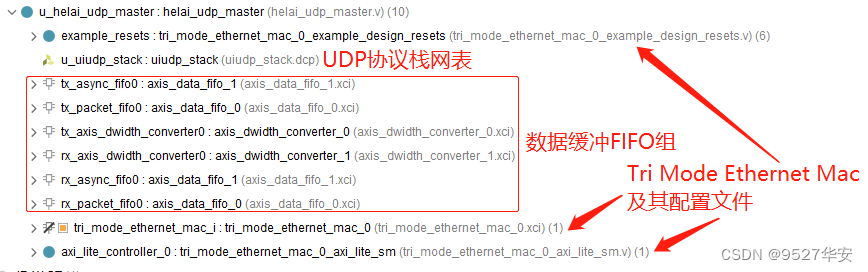

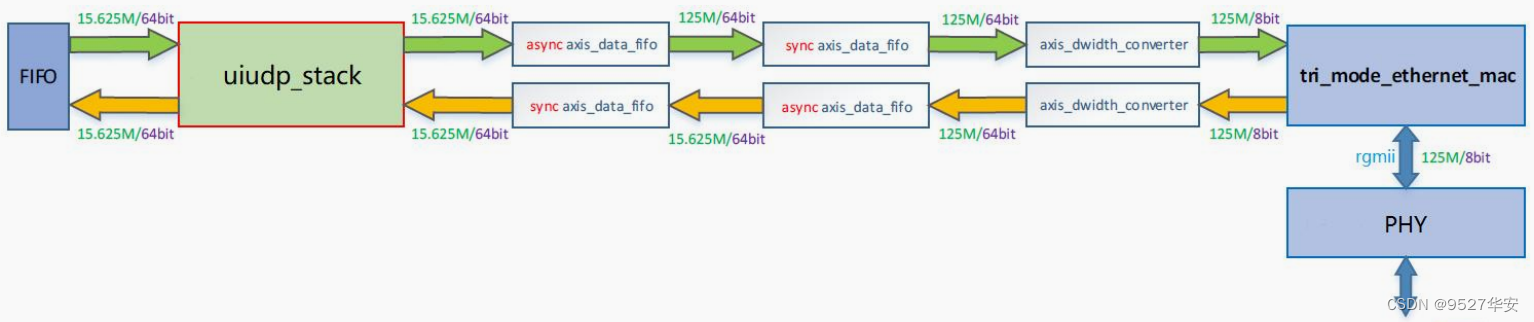

MAC数据缓冲FIFO组

这里对代码中用到的数据缓冲FIFO组做如下解释:

由于 UDP IP 协议栈的 AXI-Stream 数据接口位宽为 64bit,而 Tri Mode Ethernet MAC 的 AXI-Stream数据接口位宽为 8bit。因此,要将 UDP IP 协议栈与 Tri Mode Ethernet MAC 之间通过 AXI-Stream 接口互联,需要进行时钟域和数据位宽的转换。实现方案如下图所示:

收发路径(本设计只用到了发送)都使用了2个AXI-Stream DATA FIFO,通过其中1个FIFO实现异步时钟域的转换,1个FIFO实

现数据缓冲和同步Packet mode功能;由于千兆速率下Tri Mode Ethernet MAC的AXI-Stream数据接口同步时钟信号为125MHz,此时,UDP协议栈64bit的AXI-Stream数据接口同步时钟信号应该为125MHz/(64/8)=15.625MHz,因此,异步

AXI-Stream DATA FIFO两端的时钟分别为125MHz(8bit),15.625MHz(64bit);UDP IP协议栈的AXI-Stream接口经过FIFO时钟域转换后,还需要进行数据数据位宽转换,数据位宽的转换通过AXI4-Stream Data Width Converter完成,在接收路径中,进行 8bit 到 64bit 的转换;在发送路径中,进行 64bit 到 8bit 的转换;

IP地址、端口号的修改

UDP协议栈留出了IP地址、端口号的修改端口供用户自由修改,位置如下:

以太网网口输出方案–>Tri Mode Ethernet MAC

PHY芯片网络输出架构以Tri Mode Ethernet MAC为核心,以PHY芯片为载体,优点是FPGA逻辑设计较为简单,缺点是硬件设计较为复杂,硬件成本会相应提高;本设计采用B50610芯片,工作于延时模式,RGMII接口;关于该方案的以太网输出详细设计文档,请参考我之前的博客,博客链接如下:

直接点击前往

Tri Mode Ethernet MAC主要是为了适配PHY芯片,因为后者的输入接口是GMII,而Tri Mode Ethernet MAC的输入接口是AXIS,输出接口是GMII,Tri Mode Ethernet MAC配置如下:

提供Tri Mode Ethernet MAC使用教程和移植教程,如下:

QT上位机和源码

PC端接收网络视频,并运行QT上位机接收显示视频;我们提供和UDP通信协议相匹配的QT抓图显示上位机及其源代码,目录如下:

我们的QT目前仅支持1280x720分辨率的视频抓图显示,但同时预留了1080P接口,对QT开发感兴趣的朋友可以尝试修改代码以适应1080P,因为QT在这里只是验证工具,不是本工程的重点,所以不再过多赘述;

工程源码架构

本博客提供1套工程源码,vivado Block Design设计如下,其他工程与之类似,Block Design设计为图像缓存架构的部分:

工程源码1工程源码架构如下:

4、工程源码1详解–>PHY芯片以太网输出方案

开发板FPGA型号:Xilinx-Artix7-100T–xc7a100tfgg484-2;

开发环境:Vivado2019.1;

输入:3G-SDI相机或HDMI转SDI盒子,分辨率1920x1080@60Hz;

输出:RJ45网口,分辨率1280x720@60Hz;

SDI视频解串方案:Xilinx–GTP高速接口解串;

SDI视频解码方案:Xilinx–SMPTE SD/HD/3G SDI解码;

图像缩放方案:自研纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到1280x720;

图像缓存方案:自研FDMA方案;

图像缓存介质:DDR3;

以太网输出方案:PHY芯片以太网输出;

PHY芯片:B50610,延时模式,RGMII接口;

PC端接收方案:QT上位机;

工程作用:此工程目的是让读者掌握Xilinx–Artix7低端系列FPGA实现SDI转网口的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

5、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

6、上板调试验证

准备工作

需要准备的器材如下:

FPGA开发板;

SDI摄像头或HDMI转SDI盒子;

网线;

我的开发板了连接如下:

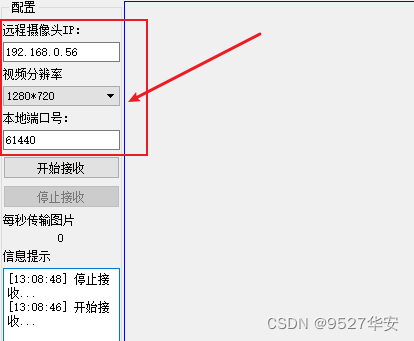

QT上位机配置如下:

输出视频演示

以工程1,3G-SDI输入图像缩放转网络输出为例,输出如下:

3G-SDI输入图像缩放转网络输出

7、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务:

相关文章:

Artix7系列FPGA实现SDI视频编解码+UDP以太网传输,基于GTP高速接口,提供工程源码和技术支持

目录 1、前言工程概述免责声明 2、相关方案推荐本博已有的 SDI 编解码方案本博已有的以太网方案本博已有的FPGA图像缩放方案本方案的缩放应用本方案在Xilinx--Kintex系列FPGA上的应用本方案在Xilinx--Zynq系列FPGA上的应用 3、详细设计方案设计原理框图SDI 输入设备Gv8601a 均衡…...

加拿大上市药品查询-加拿大药品数据库

在加拿大,药品的安全性、有效性和质量是受到严格监管的。根据《食品药品法案》的规定,所有药品制造商必须提供充分的科学证据,证明其产品的安全性和有效性。为此,加拿大卫生部建立了一个全面的药品数据库 (DPD) &#…...

qt自定义控件(QLabel)

先创建自定义控件类painter_label 1.自定义类必须给基类传入父窗口指针 2.重写控件中的方法 3.在UI中创建一个QLabel,右键“提升为”,输入类名...

阿里云国际站:海外视频安全的DRM加密

随着科技的进步,视频以直播或录播的形式陆续开展海外市场,从而也衍生出内容安全的问题,阿里云在这方面提供了完善的内容安全保护机制,适用于不同的场景,如在视频安全提供DRM加密。 由图可以了解到阿里云保护直播安全的…...

【Apache Doris】周FAQ集锦:第 15 期

【Apache Doris】周FAQ集锦:第 15 期 SQL问题数据操作问题运维常见问题其它问题关于社区 欢迎查阅本周的 Apache Doris 社区 FAQ 栏目! 在这个栏目中,每周将筛选社区反馈的热门问题和话题,重点回答并进行深入探讨。旨在为广大用户…...

verilog实现ram16*8 (vivado)

module ram_16x2 (input clk, // 时钟信号input we, // 写使能input en, // 使能信号input [3:0] addr, // 地址线input [1:0] datain, // 输入数据线output reg [1:0] dataout // 输出数据线 );// 定义存储器数组reg [1:0] mem [15:0];always (posedge…...

框架使用及下载

Bootstrap5 安装使用 | 菜鸟教程 (runoob.com) https://github.com/twbs/bootstrap/releases/download/v5.1.3/bootstrap-5.1.3-dist.zip(下载链接) Staticfile CDN(html的所有框架合集) 直接在w3cschool里面看参考文件进行搜索自…...

通用图形处理器设计GPGPU基础与架构(四)

一、前言 本文将介绍GPGPU中线程束的调度方案、记分牌方案和线程块的分配与调度方案。 二、线程束调度 在计算机中有很多资源,既可以是虚拟的计算资源,如线程、进程或数据流,也可以是硬件资源,如处理器、网络连接或 ALU 单元。调…...

会Excel就会sql?

如果你熟悉Excel,理解SQL(结构化查询语言,Structured Query Language)会相对容易,因为它们在某些功能上有着相似之处。SQL主要用于管理和操作数据库中的数据,而Excel则是电子表格软件,用于数据的组织、分析和可视化。下面我会用Excel的视角来帮你理解SQL的基本概念。 数…...

MyBatis-Plus的几种常见用法

MyBatis-Plus 提供了丰富的高级用法,可以简化开发,提高效率。以下是一些常见的可能会被忽略的用法示例。 1. 乐观锁 乐观锁用于避免在并发环境下数据更新冲突。MyBatis-Plus 通过注解和版本字段实现乐观锁。 示例: 在实体类中添加版本字段…...

【LeetCode】day15:110 - 平衡二叉树, 257 - 二叉树的所有路径, 404 - 左叶子之和, 222 - 完全二叉树的节点个数

LeetCode 代码随想录跟练 Day15 110.平衡二叉树257.二叉树的所有路径404.左叶子之和222.完全二叉树的节点个数 110.平衡二叉树 题目描述: 给定一个二叉树,判断它是否是 平衡二叉树 平衡二叉树的定义是,对于树中的每个节点,其左右…...

【网络安全的神秘世界】Error:Archives directory /var/cache/apt/archives/partial is missing.

🌝博客主页:泥菩萨 💖专栏:Linux探索之旅 | 网络安全的神秘世界 | 专接本 | 每天学会一个渗透测试工具 ✨问题描述 在kali中想要安装beef-xss软件包时,发生如下报错: Error: Archives directory /var/cac…...

网络编程中的TCP和UDP

什么是TCP协议 TCP( Transmission control protocol )即传输控制协议,是一种面向连接、可靠的数据传输协议,它是为了在不可靠的互联网上提供可靠的端到端字节流而专门设计的一个传输协议。 面向连接 :数据传输之前客户端和服务器端必须建立连…...

模型)

基于python的时空地理加权回归(GTWR)模型

一、时空地理加权回归(GTWR)模型 时空地理加权回归(GTWR)模型是由美国科罗拉多州立大学的Andy Liaw、Stanley A. Fiel和Michael E. Bock于2008年提出的一种高级空间统计分析方法。它是在传统地理加权回归(GWR…...

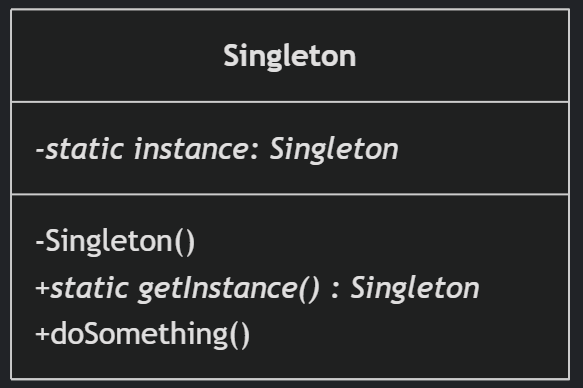

什么是单例模式,有哪些应用?

目录 一、定义 二、应用场景 三、6种实现方式 1、懒汉式,线程不安全。 2、懒汉式,线程安全 3、双检锁/双重校验锁(DCL,即 double-checked locking) 4、静态内部类方式-------只适用于静态域 5、饿汉式 6、枚举…...

adb命令操作手机各种开关

打开iqoo手机热点设置 adb shell am start -n com.android.settings/com.android.settings.Settings$\VivoTetherSettingsActivity蓝牙模块 检查蓝牙状态的ADB命令 检查蓝牙开关状态 adb shell settings get global bluetooth_on开启和关闭蓝牙 使用Intent操作蓝牙…...

【分布式存储系统HDFS】架构和使用

分布式存储系统HDFS:架构和使用 目录 引言HDFS简介HDFS的架构 NameNodeDataNodeSecondary NameNode HDFS的工作原理 数据读写流程数据冗余与恢复 HDFS的安装和配置 环境准备HDFS安装步骤HDFS配置文件启动HDFS HDFS的使用 基本命令HDFS Shell操作Java API操作 HDFS…...

Linux 实验一Linux系统安装

一、实验日期与地址 1、实验日期:2024年 2 月28 日 2、实验地址:S1-504 二、实验目的 1、掌握VMware Workstation建立虚拟机 2、掌握虚拟机环境下安装Centos 7 三、实验环境 VMware Workstation、Centos 7 四、实验内容 1、安装VMware Workstat…...

【人工智能】深度剖析AI伦理:强化隐私防线,推动算法公平性的核心议题

文章目录 🍊1 人工智能兴起背后的伦理及道德风险1.1 算法偏见与歧视1.2 数据隐私侵权1.3 透明度受限1.4 决策失衡1.5 AI生成内容的危险性 🍊2 建构AIGC伦理观:实现人机共创的永续提升2.1 技术手段与伦理预防2.2 即时警告与紧急关停措施2.3 法…...

如何解决微服务下引起的 分布式事务问题

一、什么是分布式事务? 虽然叫分布式事务,但不是一定是分布式部署的服务之间才会产生分布式事务。不是在同一个服务或同一个数据库架构下,产生的事务,也就是分布式事务。 跨数据源的分布式事务 跨服务的分布式事务 二、解决方…...

linux之kylin系统nginx的安装

一、nginx的作用 1.可做高性能的web服务器 直接处理静态资源(HTML/CSS/图片等),响应速度远超传统服务器类似apache支持高并发连接 2.反向代理服务器 隐藏后端服务器IP地址,提高安全性 3.负载均衡服务器 支持多种策略分发流量…...

macOS多出来了:Google云端硬盘、YouTube、表格、幻灯片、Gmail、Google文档等应用

文章目录 问题现象问题原因解决办法 问题现象 macOS启动台(Launchpad)多出来了:Google云端硬盘、YouTube、表格、幻灯片、Gmail、Google文档等应用。 问题原因 很明显,都是Google家的办公全家桶。这些应用并不是通过独立安装的…...

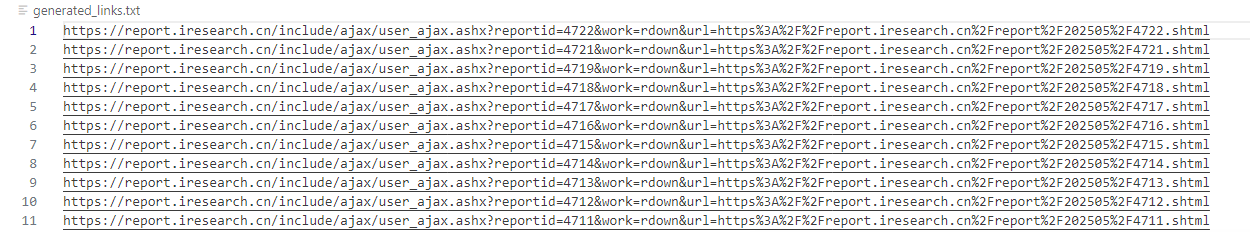

selenium学习实战【Python爬虫】

selenium学习实战【Python爬虫】 文章目录 selenium学习实战【Python爬虫】一、声明二、学习目标三、安装依赖3.1 安装selenium库3.2 安装浏览器驱动3.2.1 查看Edge版本3.2.2 驱动安装 四、代码讲解4.1 配置浏览器4.2 加载更多4.3 寻找内容4.4 完整代码 五、报告文件爬取5.1 提…...

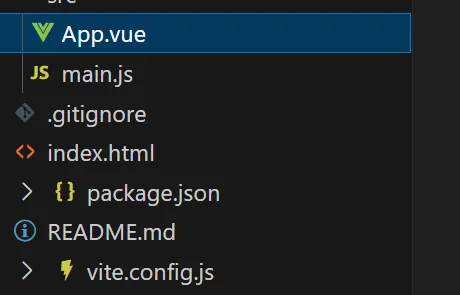

springboot整合VUE之在线教育管理系统简介

可以学习到的技能 学会常用技术栈的使用 独立开发项目 学会前端的开发流程 学会后端的开发流程 学会数据库的设计 学会前后端接口调用方式 学会多模块之间的关联 学会数据的处理 适用人群 在校学生,小白用户,想学习知识的 有点基础,想要通过项…...

Linux nano命令的基本使用

参考资料 GNU nanoを使いこなすnano基础 目录 一. 简介二. 文件打开2.1 普通方式打开文件2.2 只读方式打开文件 三. 文件查看3.1 打开文件时,显示行号3.2 翻页查看 四. 文件编辑4.1 Ctrl K 复制 和 Ctrl U 粘贴4.2 Alt/Esc U 撤回 五. 文件保存与退出5.1 Ctrl …...

4. TypeScript 类型推断与类型组合

一、类型推断 (一) 什么是类型推断 TypeScript 的类型推断会根据变量、函数返回值、对象和数组的赋值和使用方式,自动确定它们的类型。 这一特性减少了显式类型注解的需要,在保持类型安全的同时简化了代码。通过分析上下文和初始值,TypeSc…...

(一)单例模式

一、前言 单例模式属于六大创建型模式,即在软件设计过程中,主要关注创建对象的结果,并不关心创建对象的过程及细节。创建型设计模式将类对象的实例化过程进行抽象化接口设计,从而隐藏了类对象的实例是如何被创建的,封装了软件系统使用的具体对象类型。 六大创建型模式包括…...

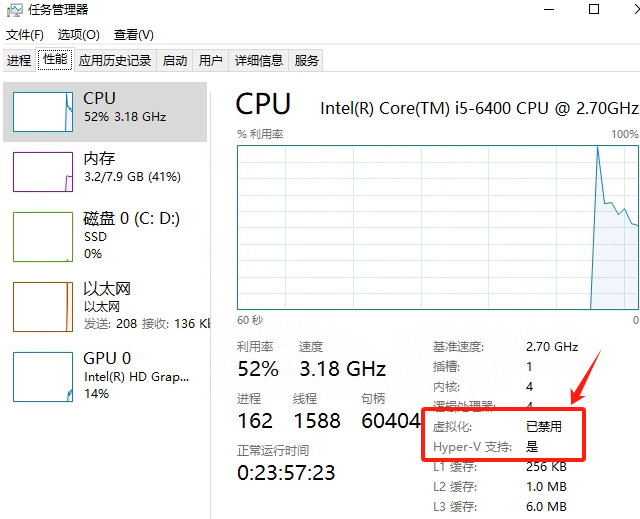

Windows电脑能装鸿蒙吗_Windows电脑体验鸿蒙电脑操作系统教程

鸿蒙电脑版操作系统来了,很多小伙伴想体验鸿蒙电脑版操作系统,可惜,鸿蒙系统并不支持你正在使用的传统的电脑来安装。不过可以通过可以使用华为官方提供的虚拟机,来体验大家心心念念的鸿蒙系统啦!注意:虚拟…...

TCP/IP 网络编程 | 服务端 客户端的封装

设计模式 文章目录 设计模式一、socket.h 接口(interface)二、socket.cpp 实现(implementation)三、server.cpp 使用封装(main 函数)四、client.cpp 使用封装(main 函数)五、退出方法…...

【笔记】AI Agent 项目 SUNA 部署 之 Docker 构建记录

#工作记录 构建过程记录 Microsoft Windows [Version 10.0.27871.1000] (c) Microsoft Corporation. All rights reserved.(suna-py3.12) F:\PythonProjects\suna>python setup.py --admin███████╗██╗ ██╗███╗ ██╗ █████╗ ██╔════╝…...