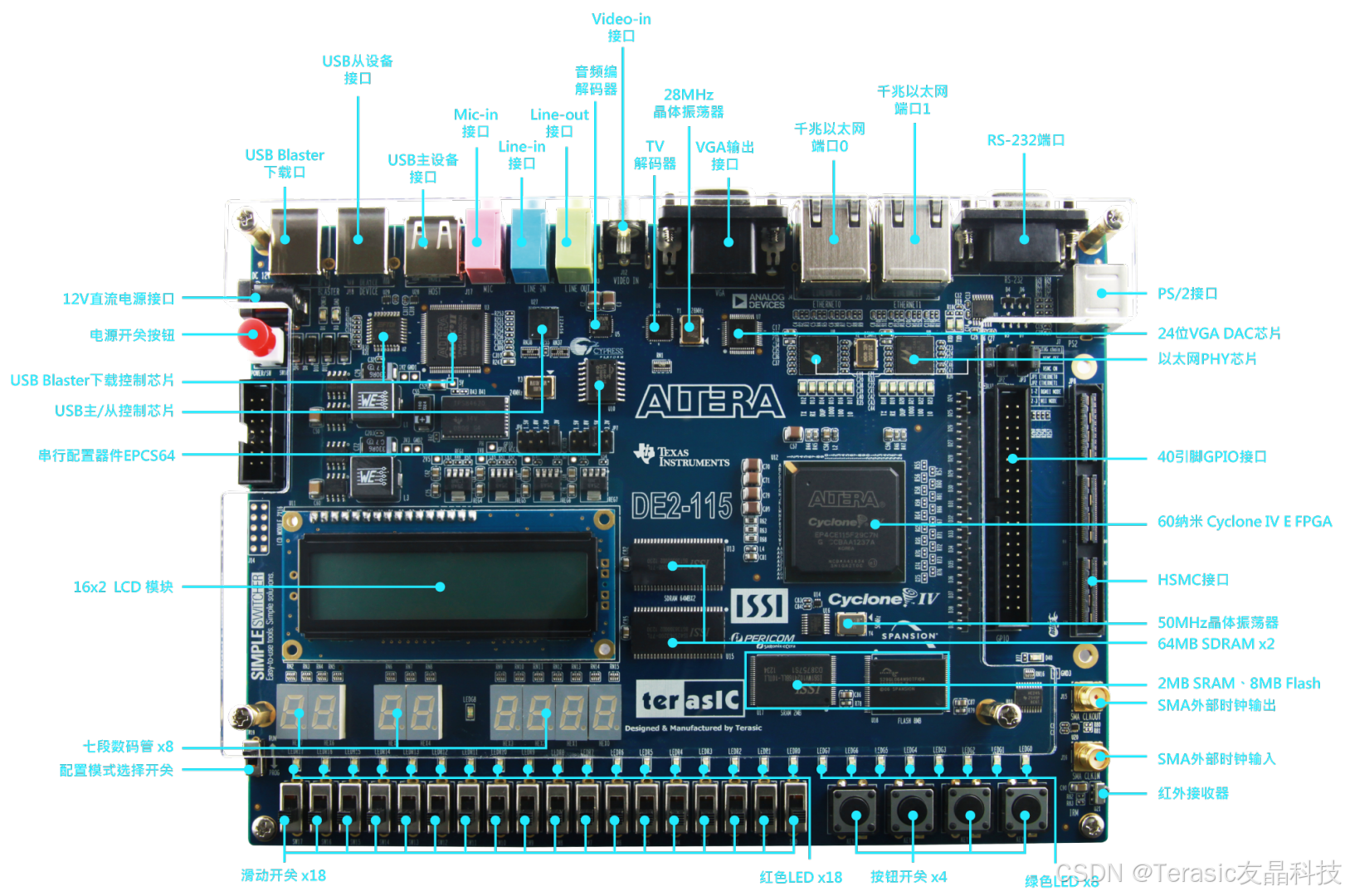

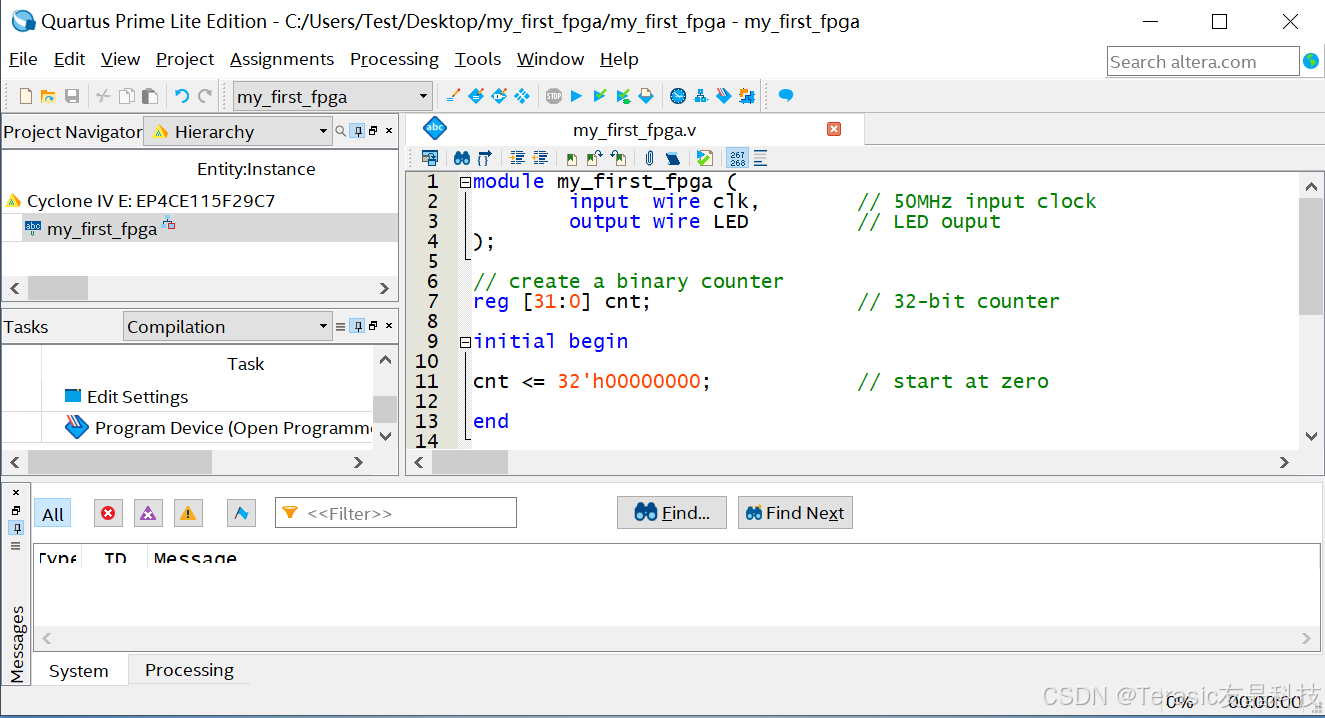

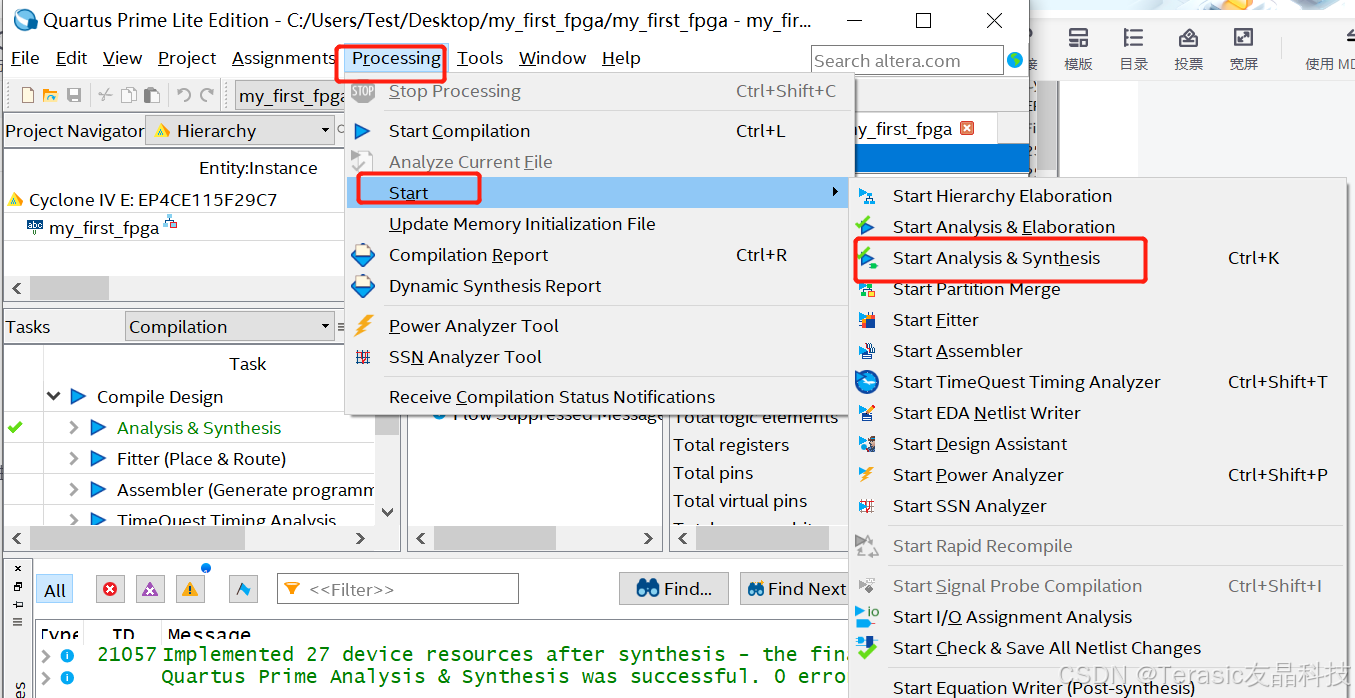

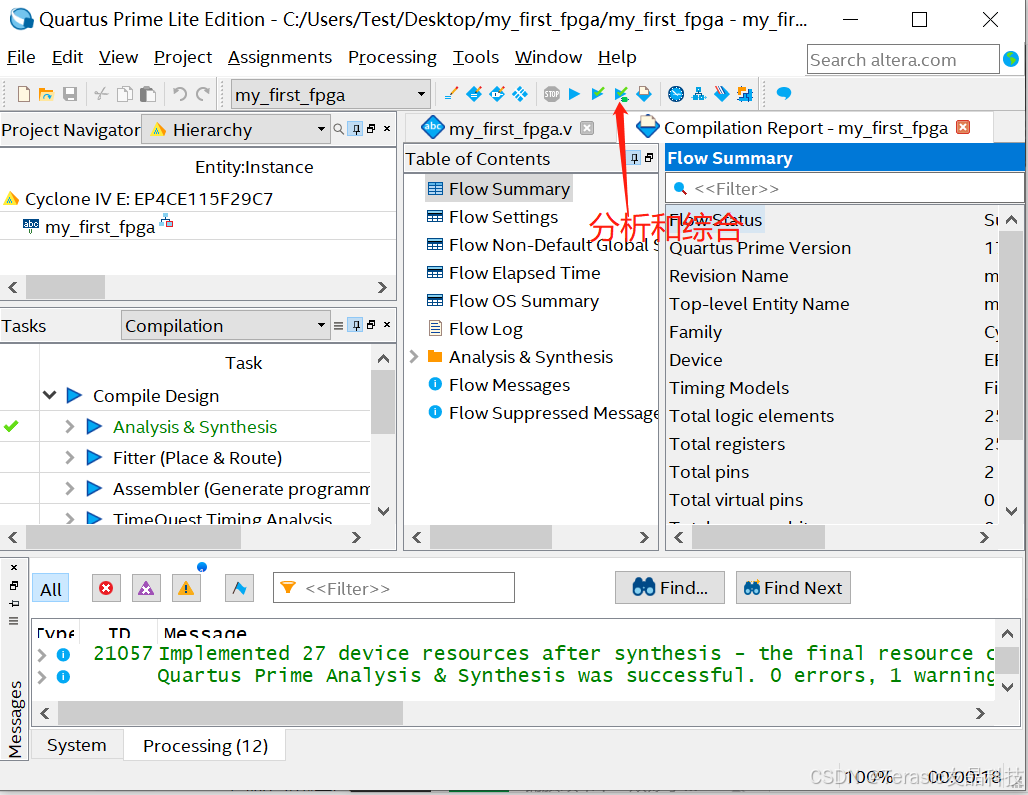

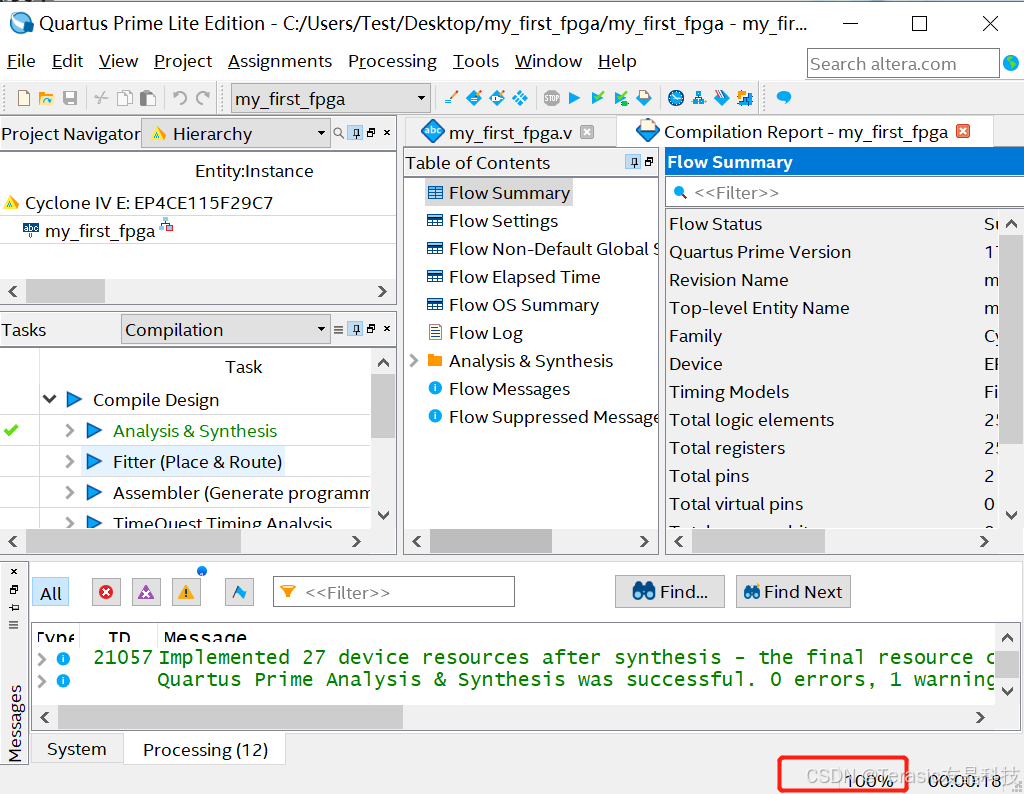

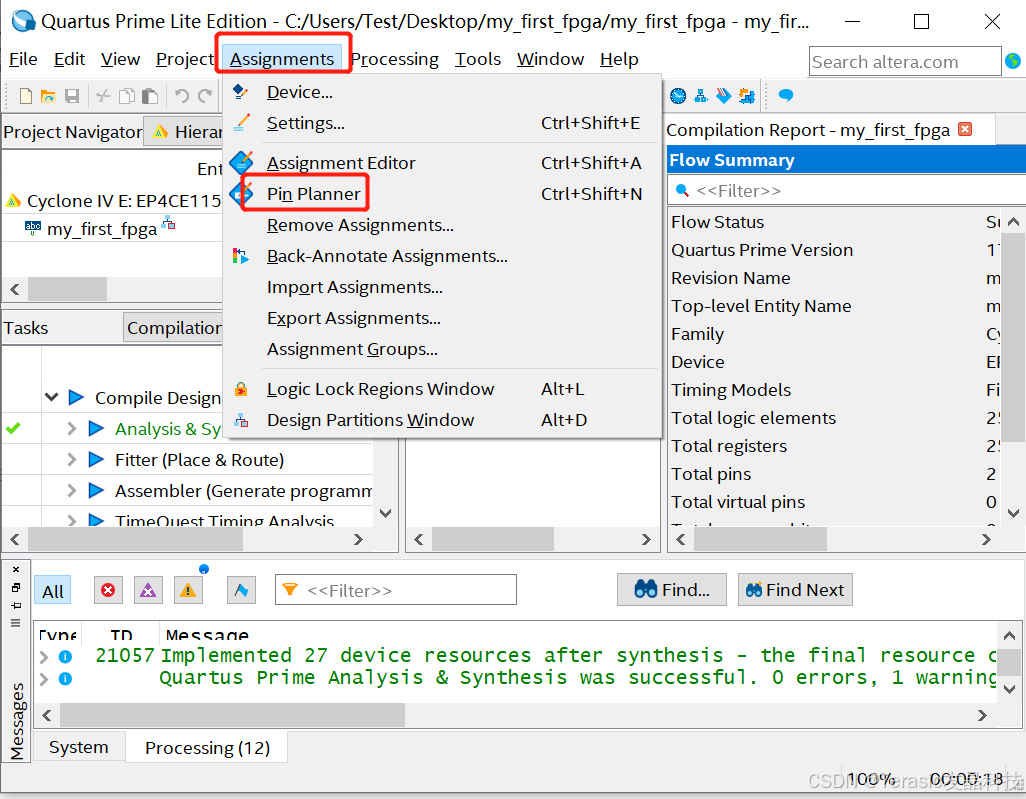

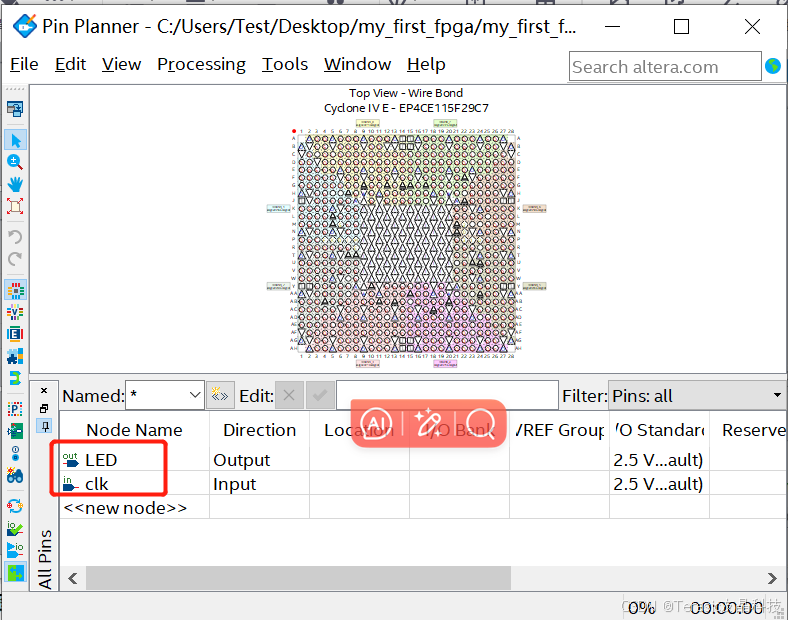

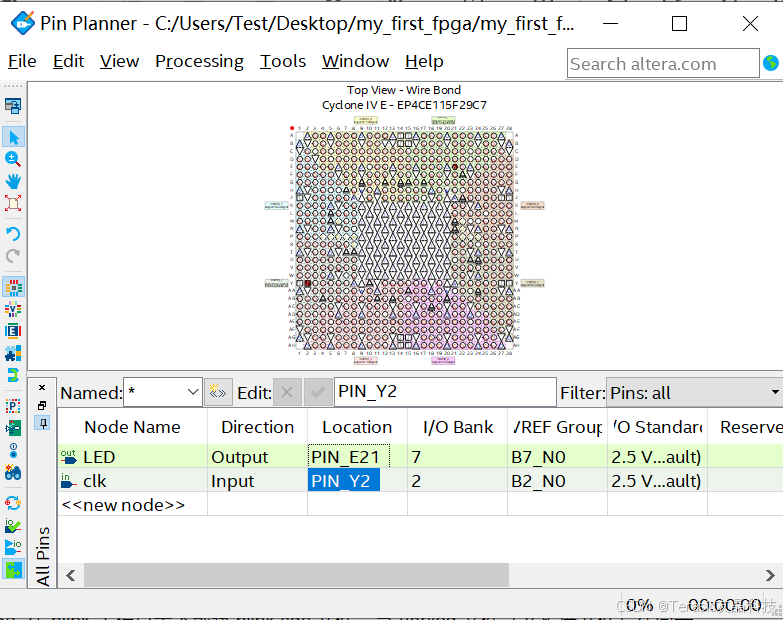

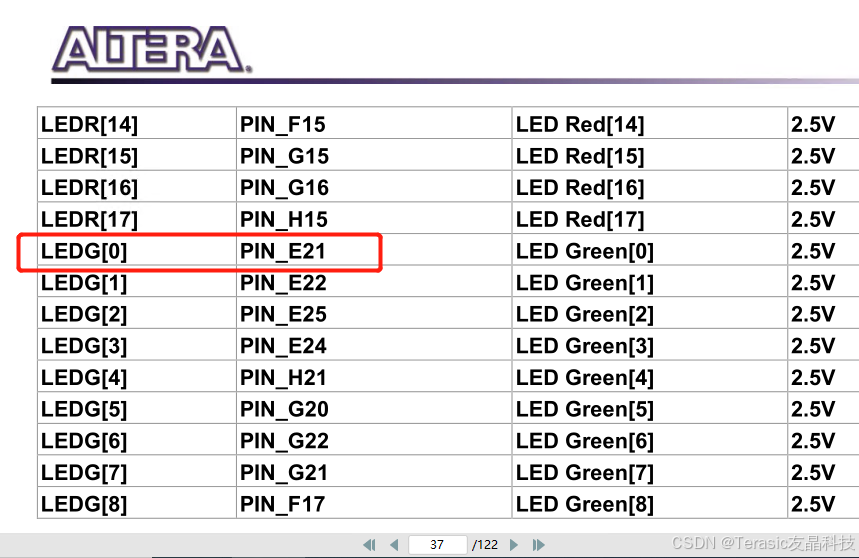

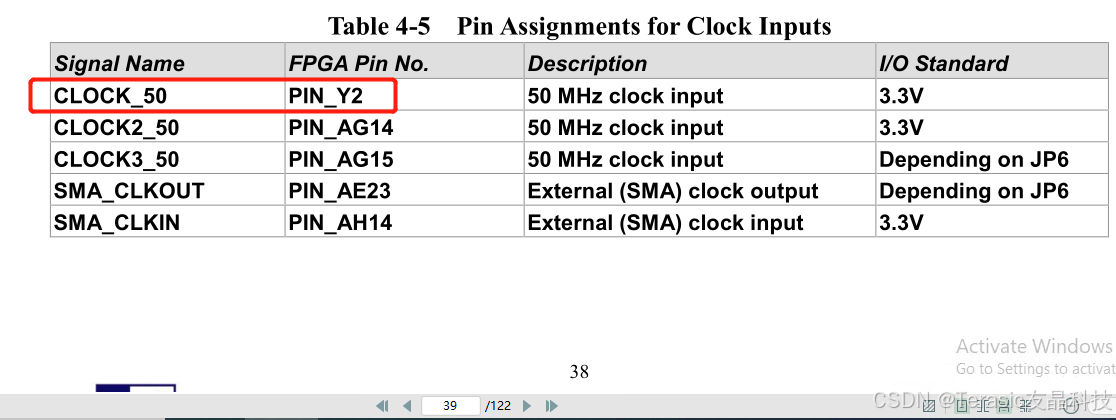

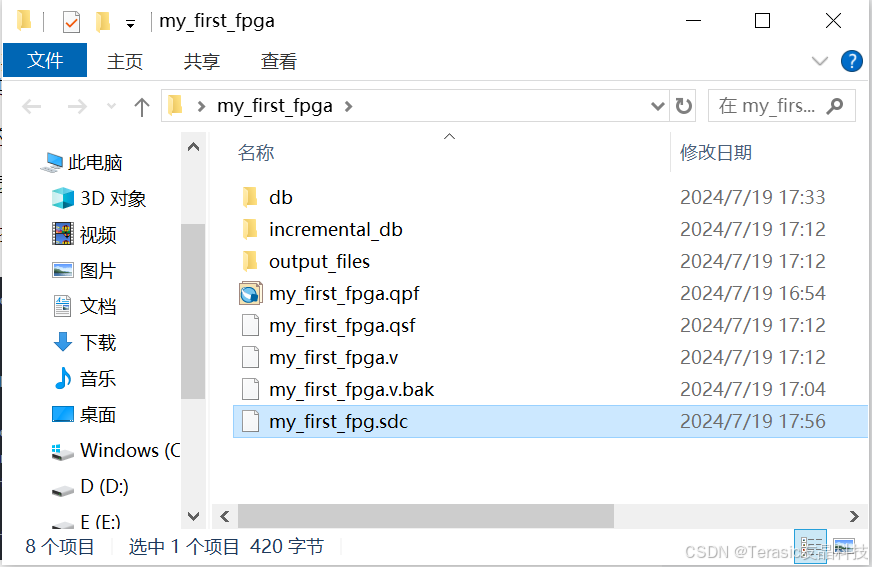

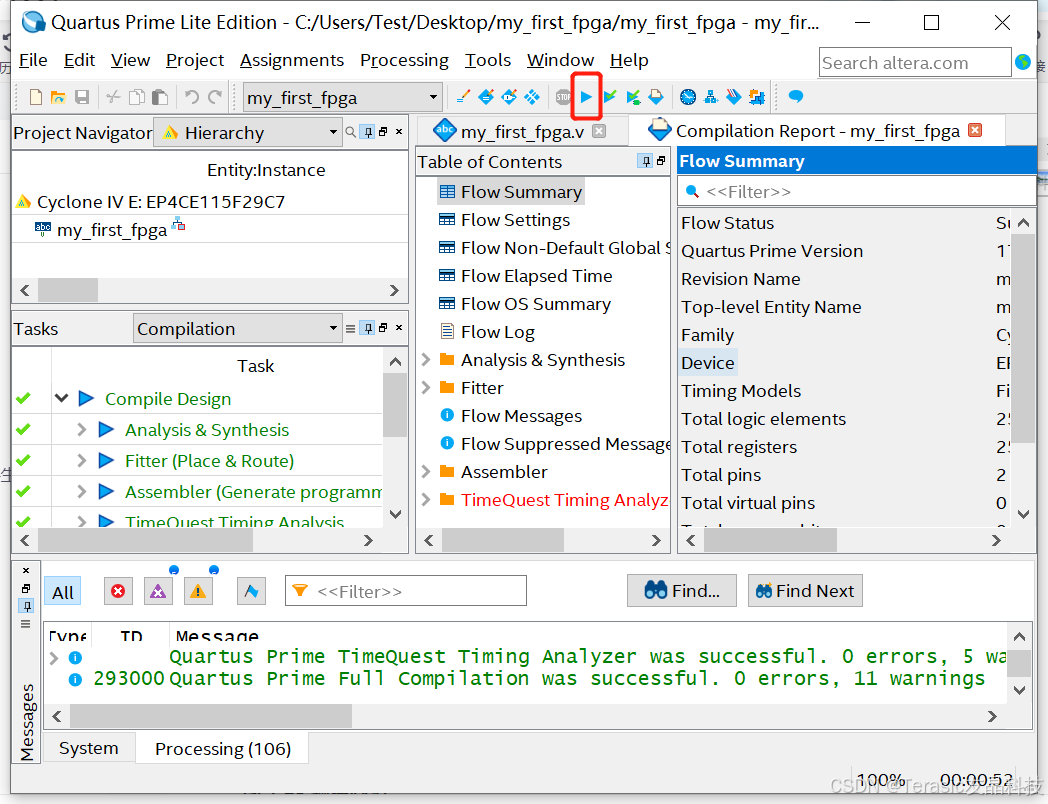

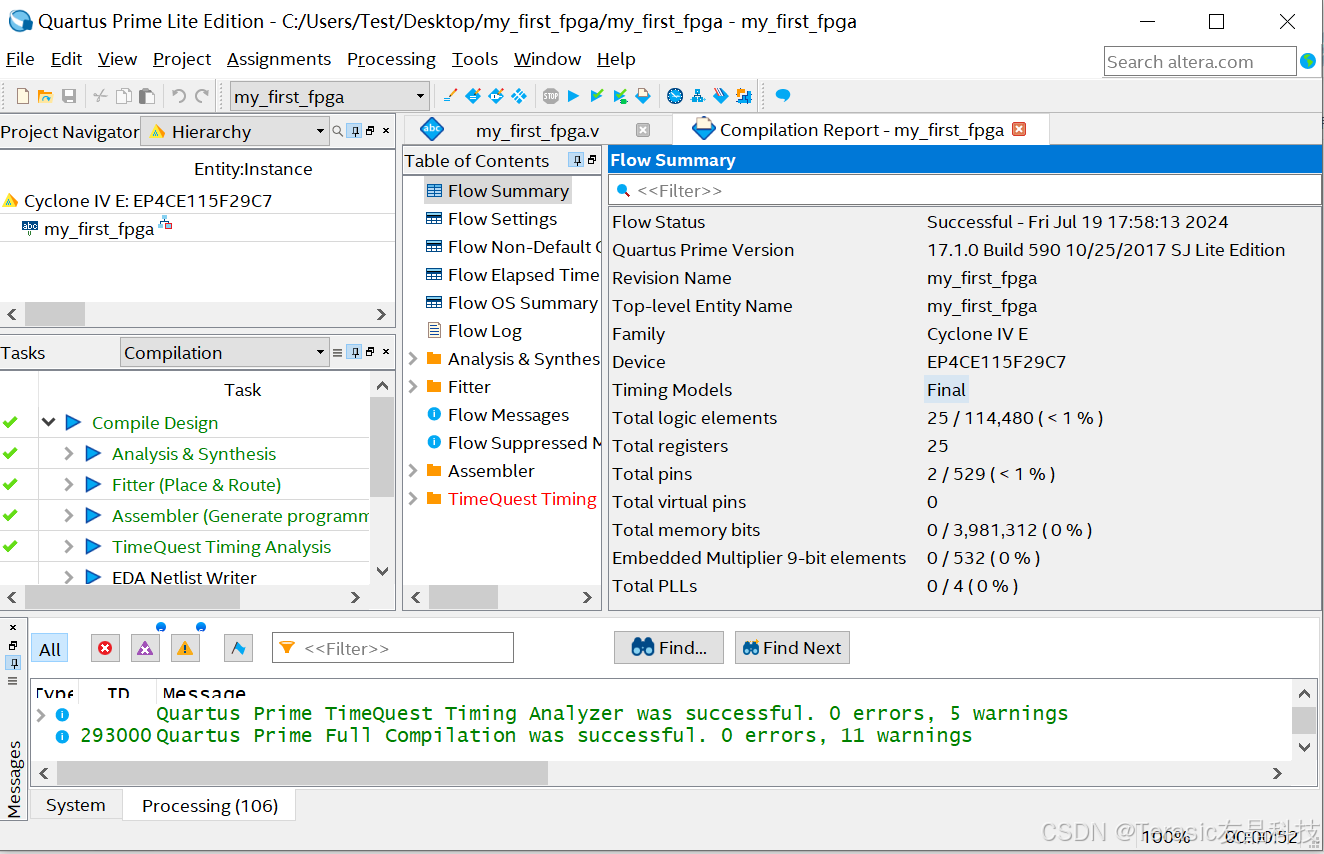

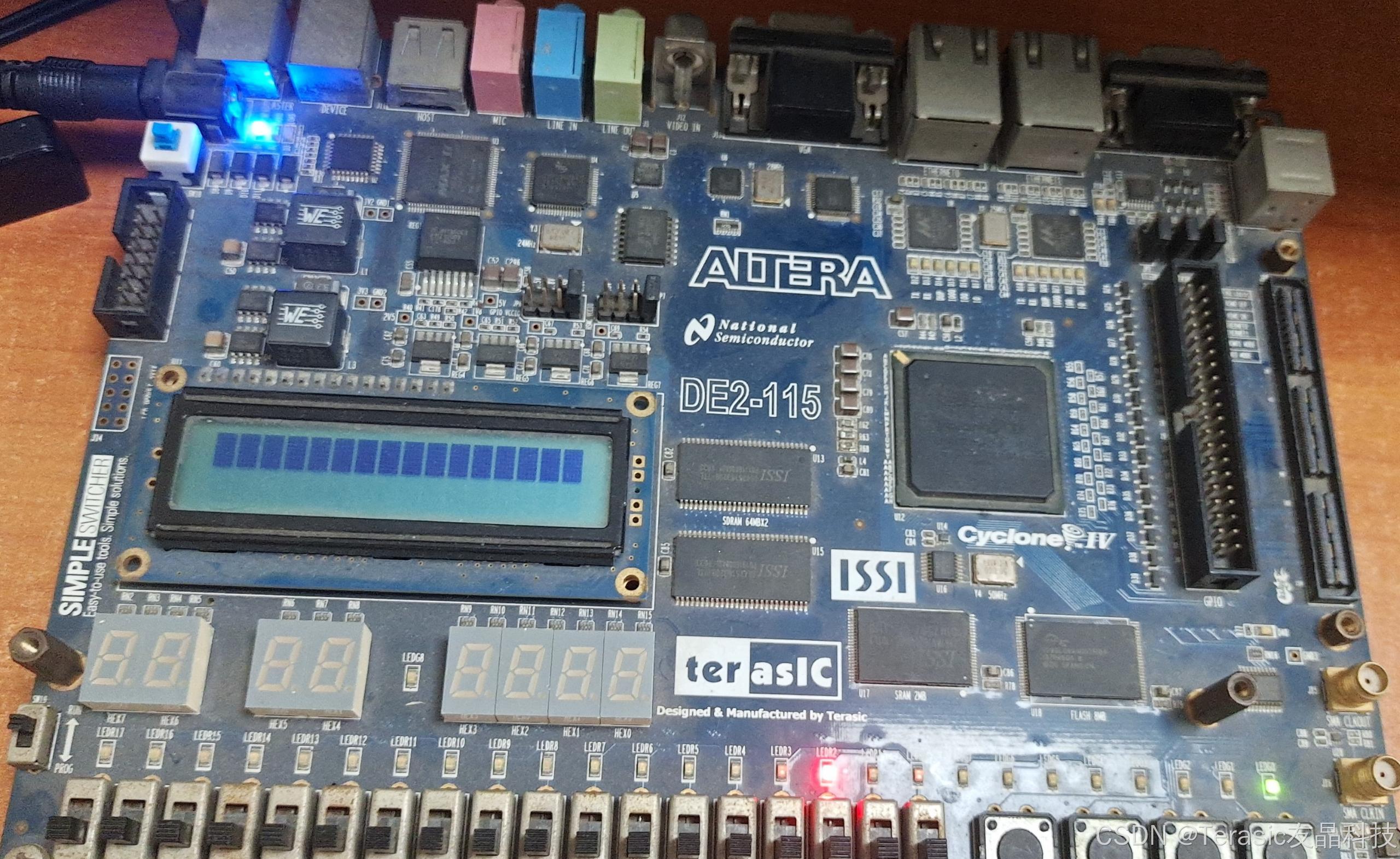

【入门教程一】基于DE2-115的My First FPGA 工程

module my_first_fpga(input wire clk, // 50MHz input clockoutput wire LED // LED ouput

);// create a binary counter

reg [31:0] cnt; // 32-bit counterinitial begincnt <= 32'h00000000; // start at zeroendalways @(posedge clk) begincnt <= cnt + 1; // count upend//assign LED to 25th bit of the counter to blink the LED at a few Hz

assign LED = cnt[24];endmodule

# inform quartus that the clk port brings a 50MHz clock into our design so

# that timing closure on our design can be analyzedcreate_clock -name clk -period "50MHz" [get_ports clk]# inform quartus that the LED output port has no critical timing requirements

# its a single output port driving an LED, there are no timing relationships

# that are critical for thisset_false_path -from * -to [get_ports LED]

1. // create module

2. module blink(

3. input wire clk, // 50MHz input clock

4. output wire [7:0] LED // array of 8 LEDs

5. );

6.

7. // create a binary counter

8. reg [31:0] cnt; //32 bit counter

9.

10. initial begin

11.

12. cnt <= 32’h00000000; // start count at zero

13.

14. end

15.

16. always @(posedge clk) begin

17.

18. cnt <= cnt+1; // count up

19.

20. end

21.

22. //assign LEDs to bits 28 through 21 of the counter

23.

24. assign LED = cnt[28:21];

25.

26. endmodule相关文章:

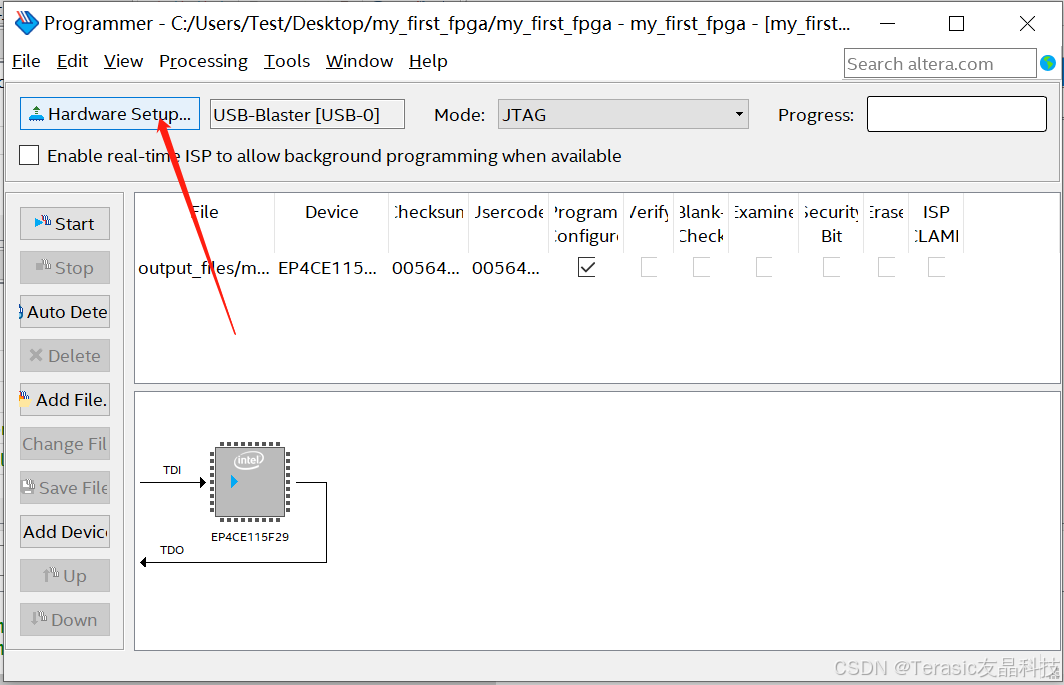

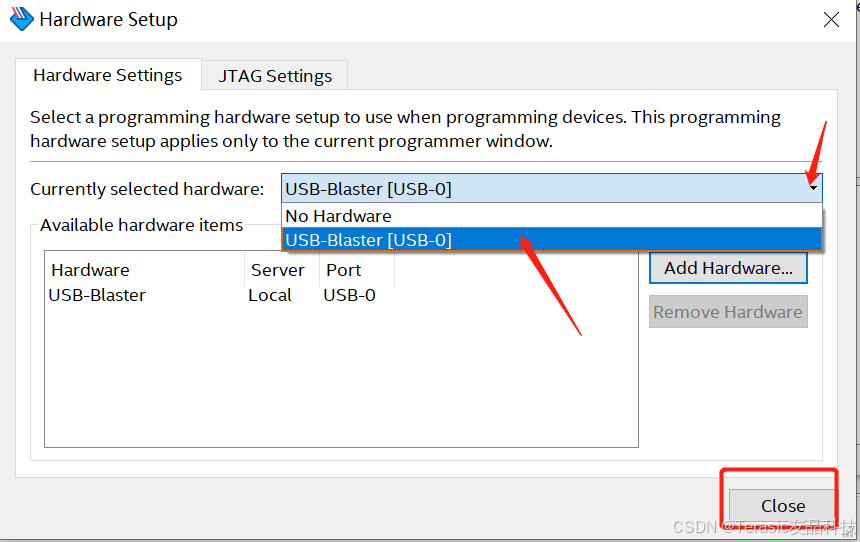

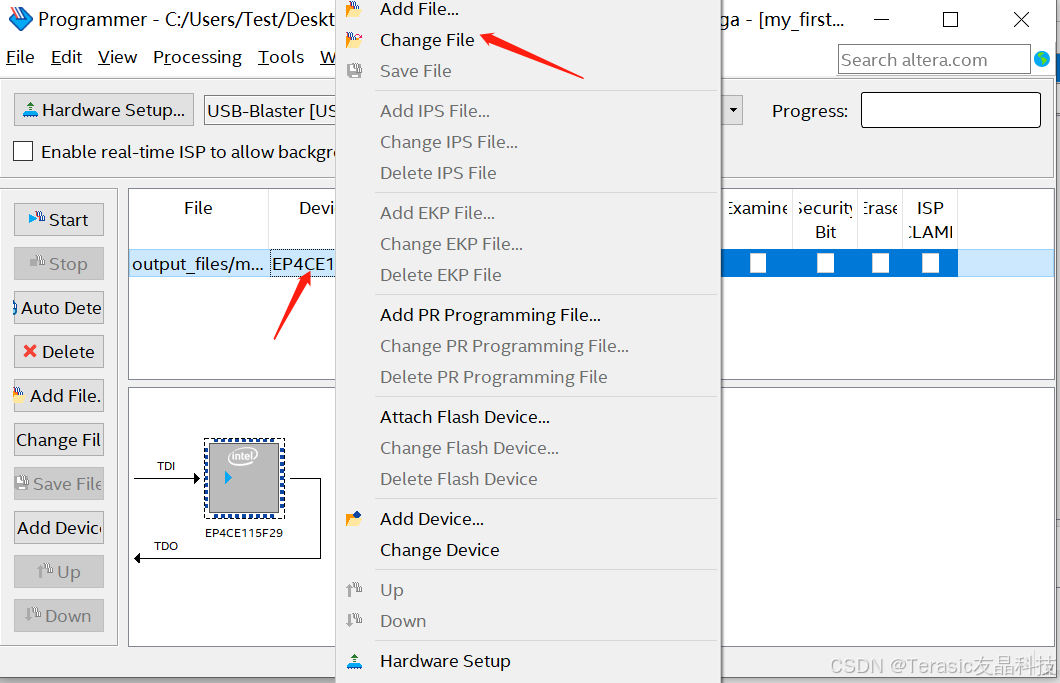

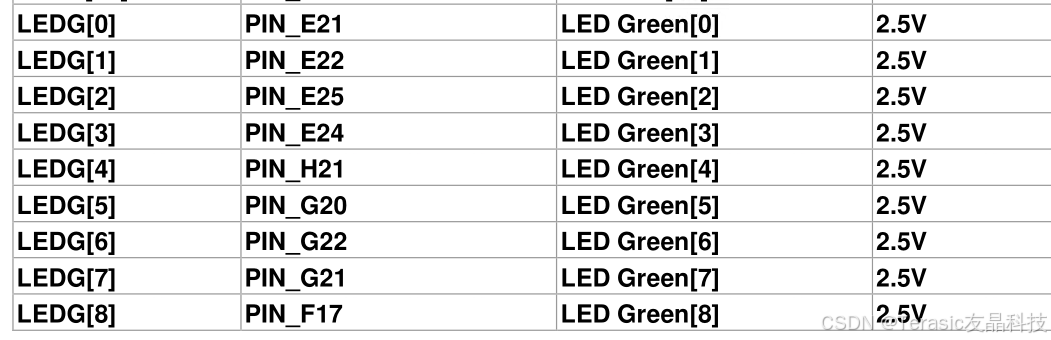

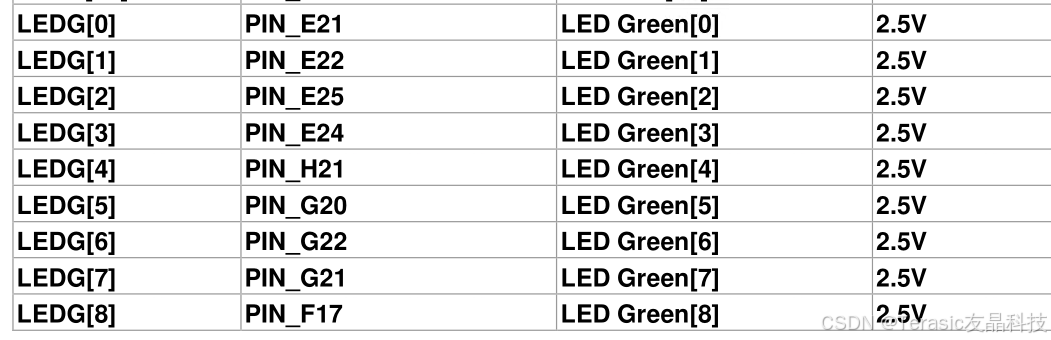

【入门教程一】基于DE2-115的My First FPGA 工程

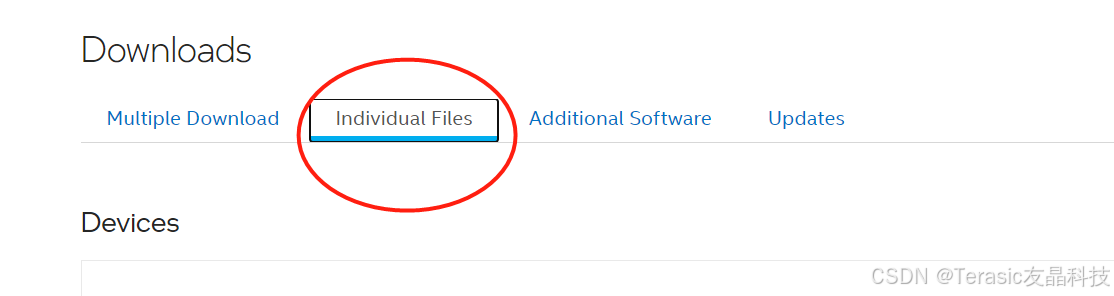

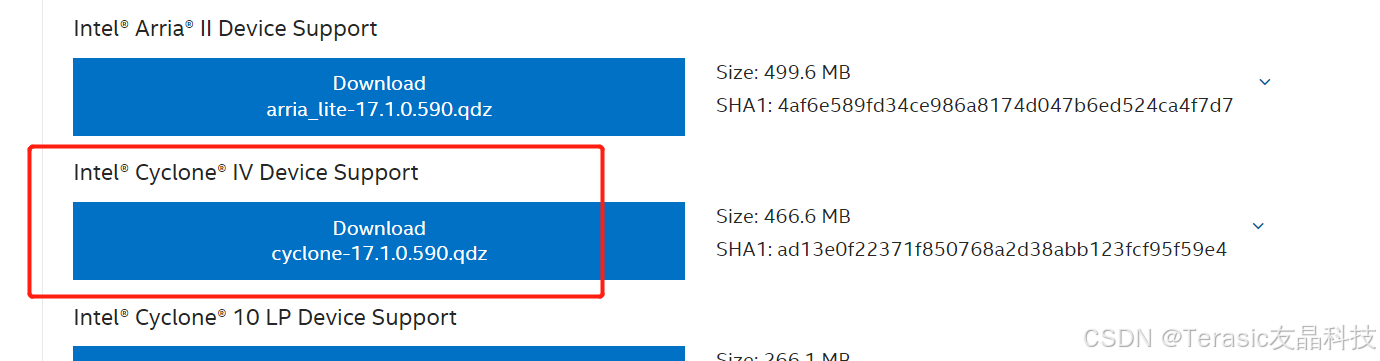

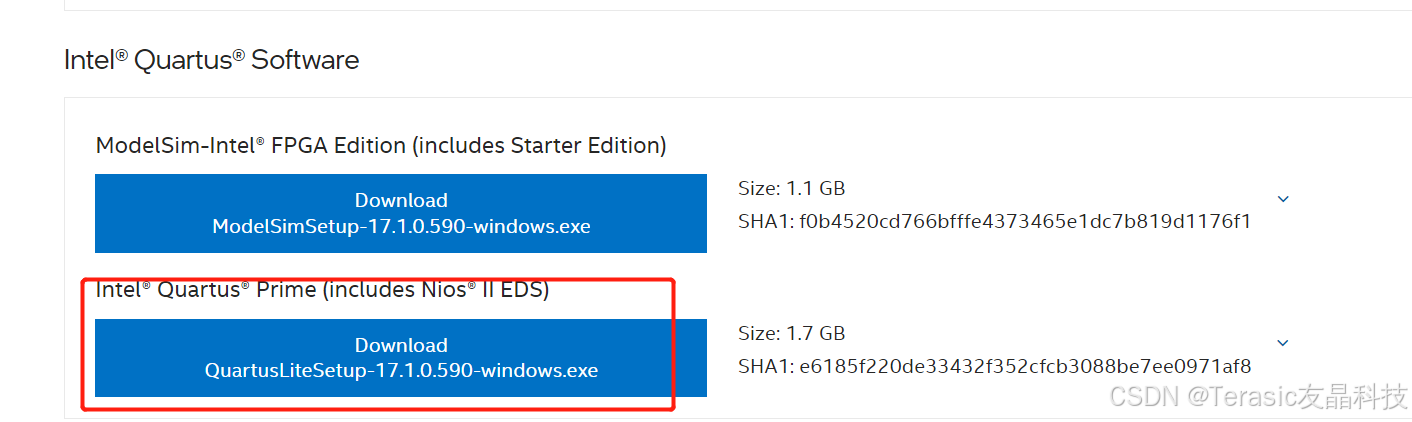

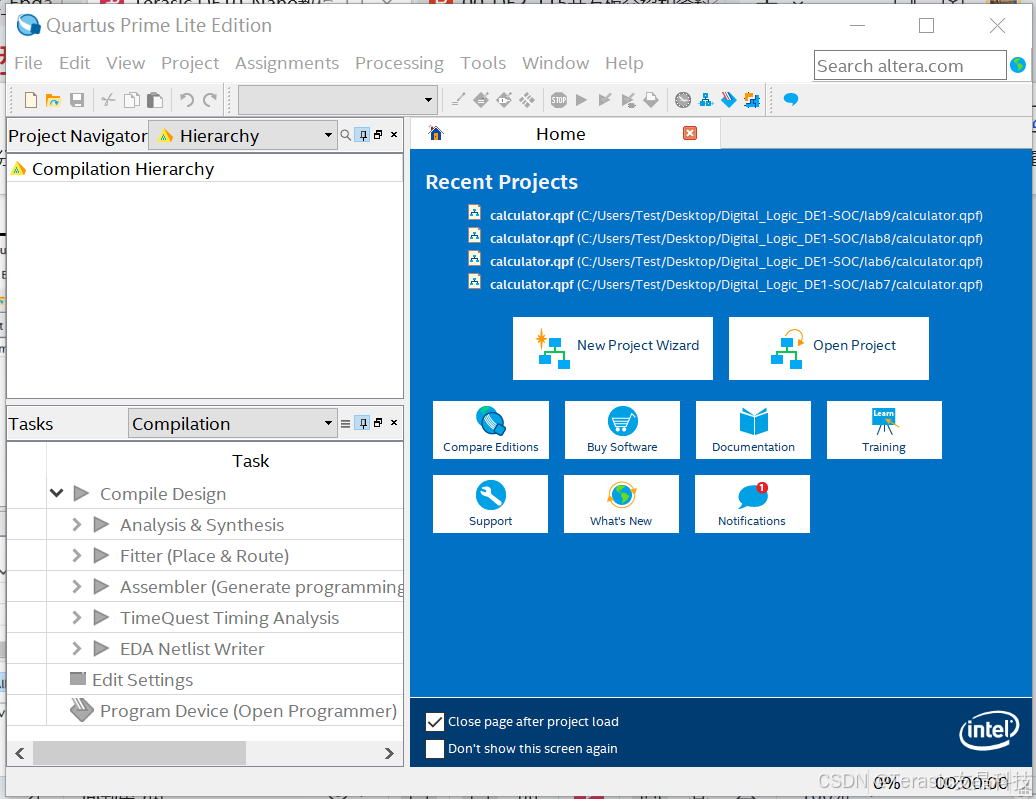

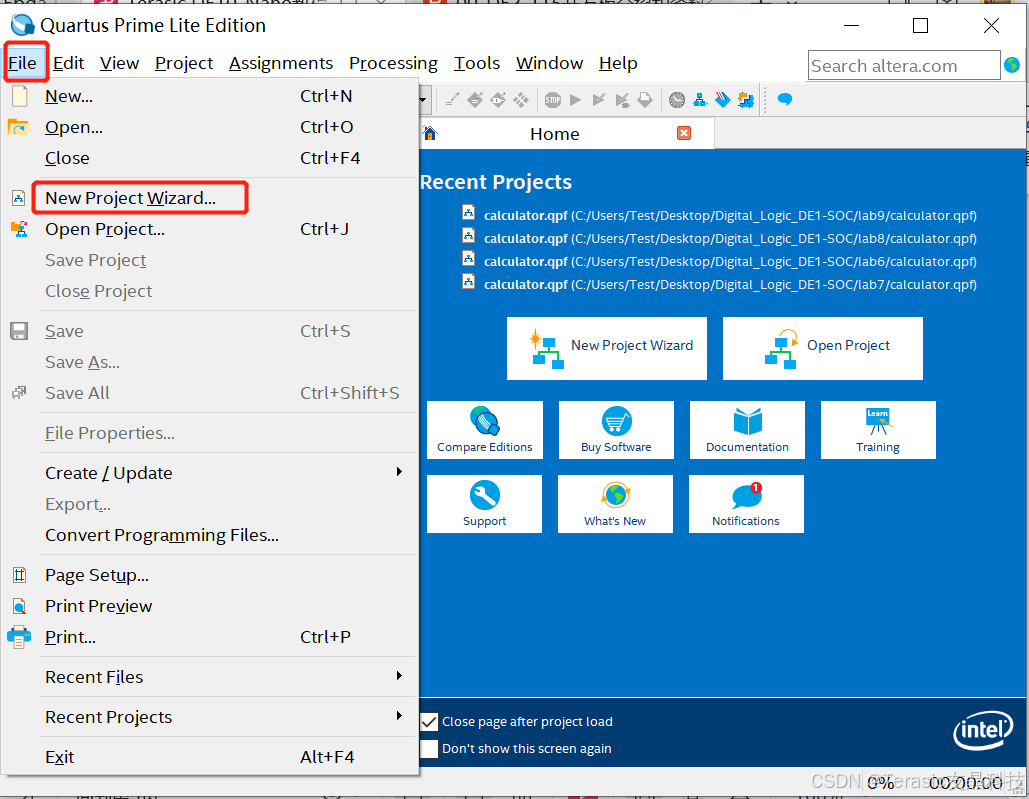

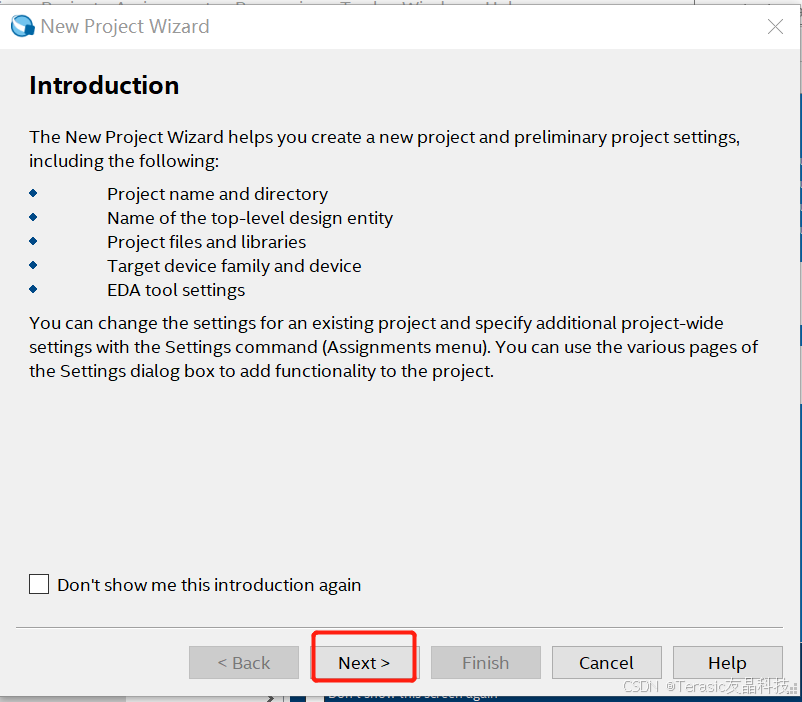

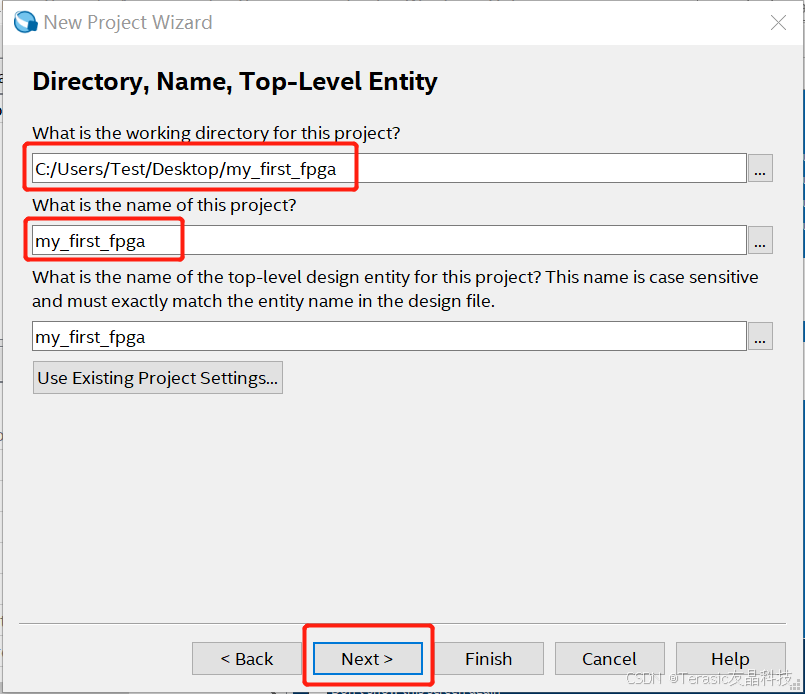

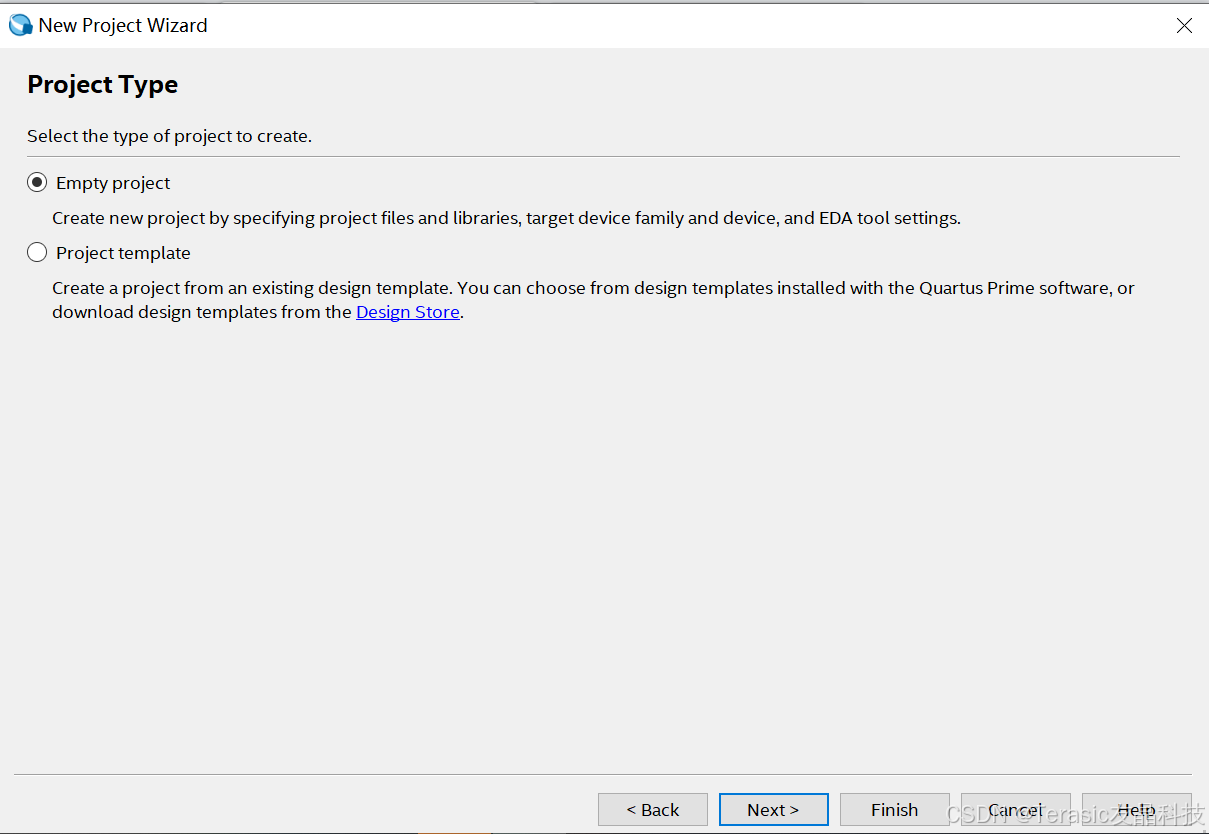

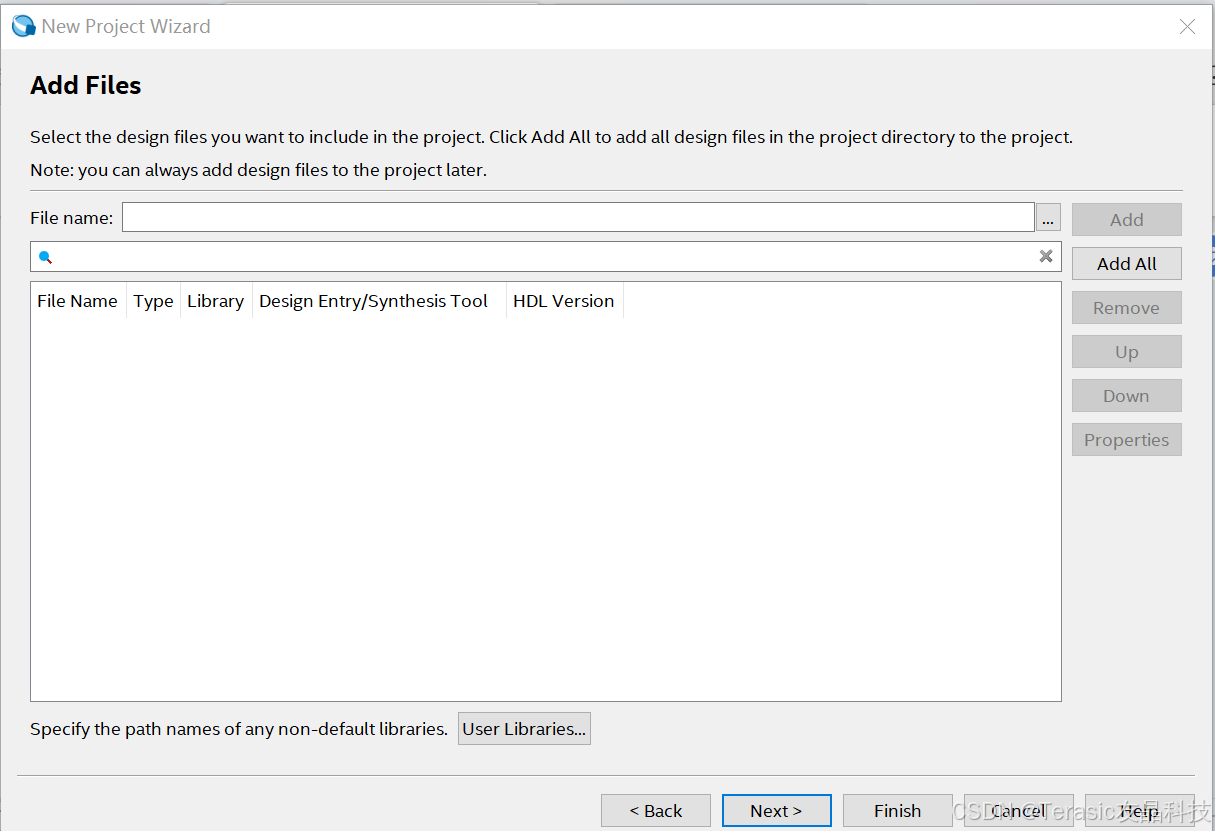

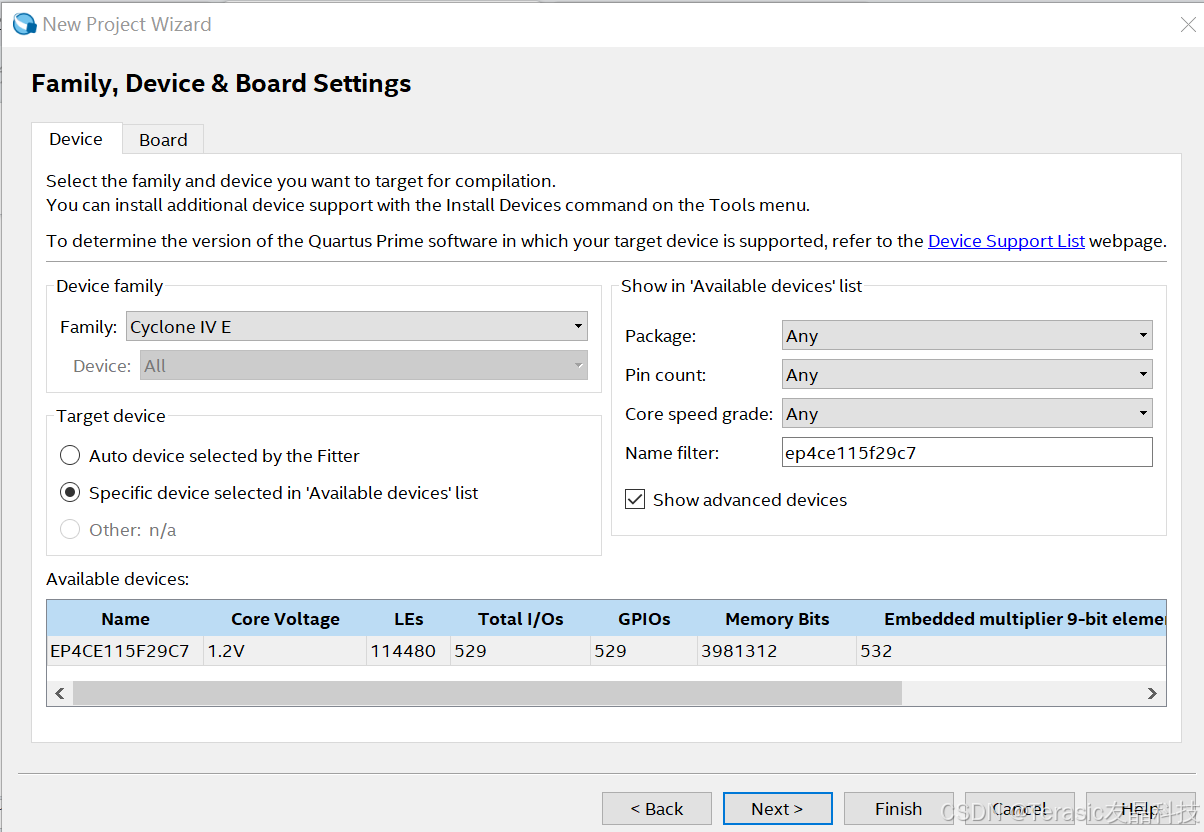

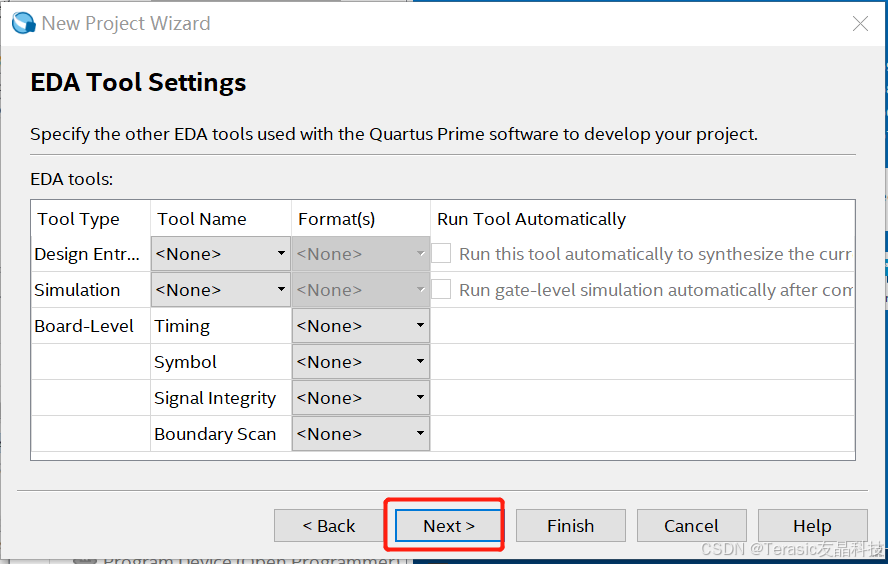

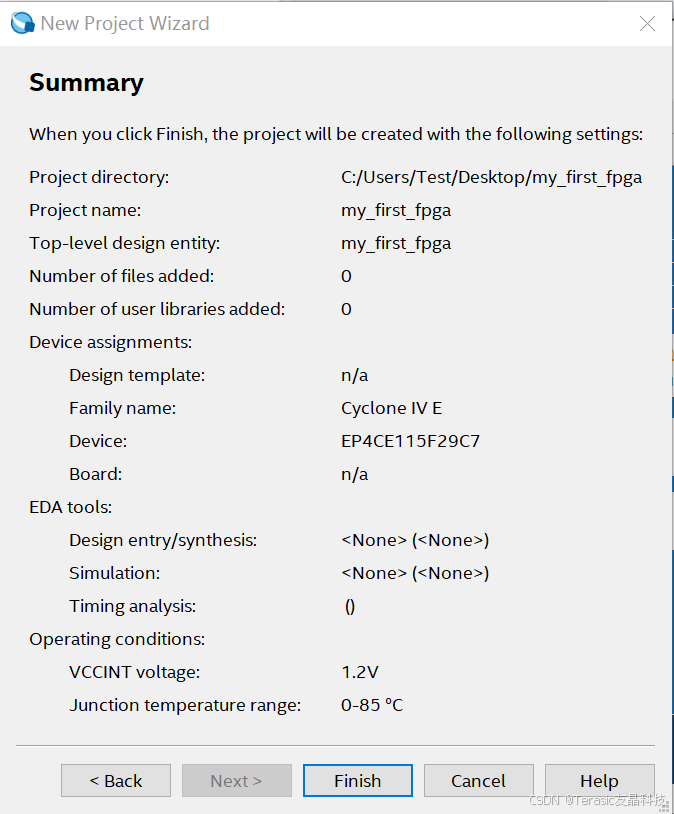

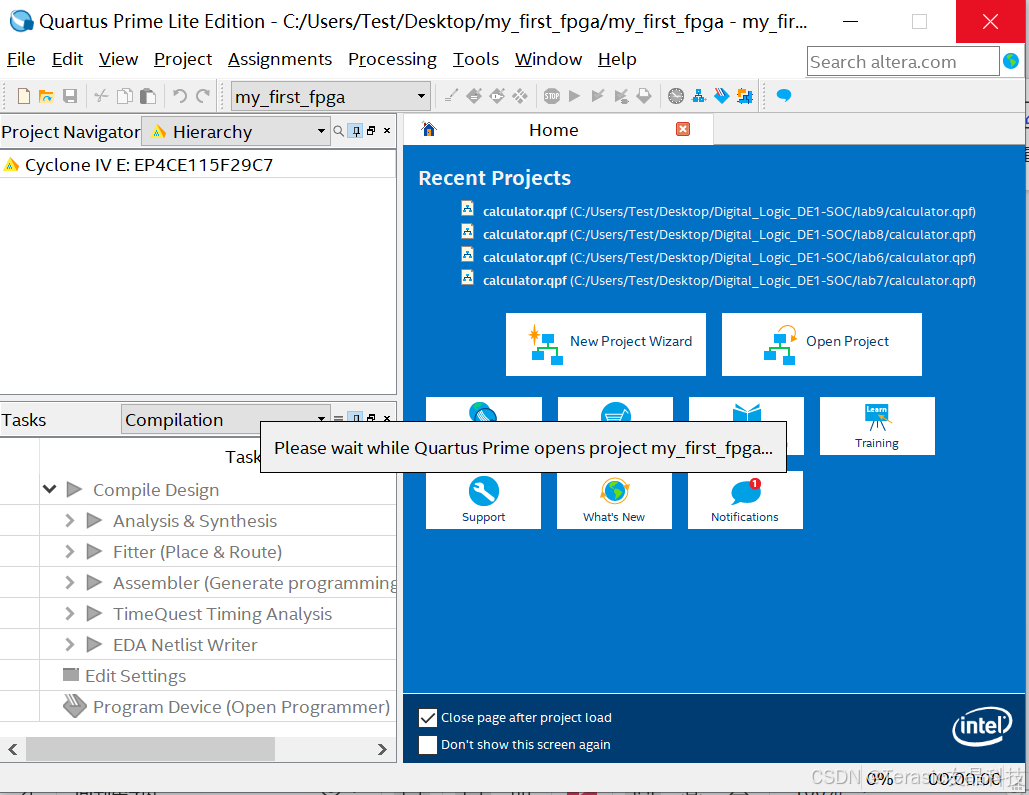

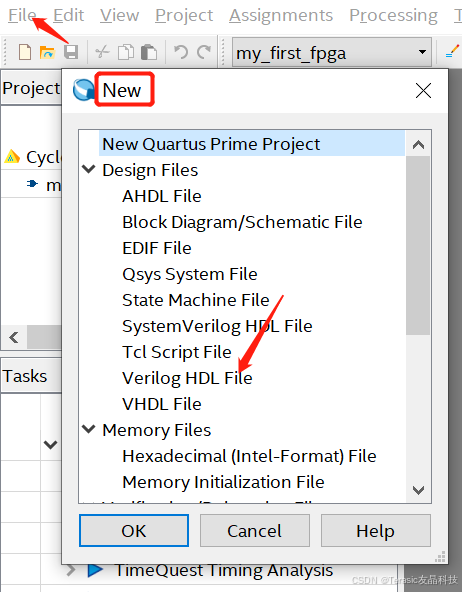

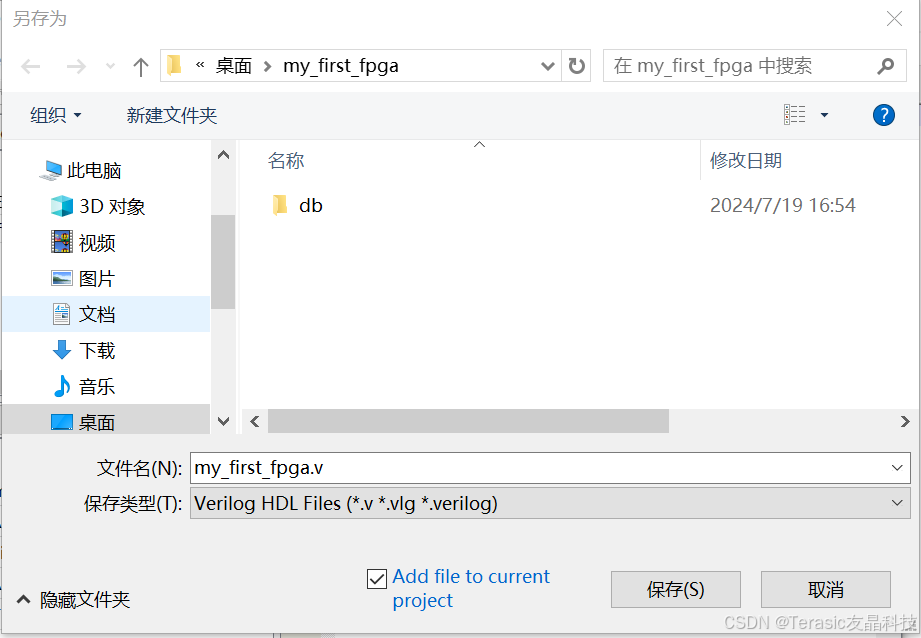

1.1. 概述 这是一个简单的练习, 可以帮助初学者开始了解如何使用Intel Quartus 软件进行 FPGA 开发。 在本章节中,您将学习如何编译 Verilog 代码,进行引脚分配,创建时序约束,然后对 FPGA 进行编程,驱动开…...

mysql中的索引和分区

目录 1.编写目的 2.索引 2.1 创建方法 2.2 最佳适用 2.3 索引相关语句 3.分区 3.1 创建方法 3.2 最佳适用 Welcome to Code Blocks blog 本篇文章主要介绍了 [Mysql中的分区和索引] ❤博主广交技术好友,喜欢文章的可以关注一下❤ 1.编写目的 在MySQL中&…...

项目实战--C#实现图书馆信息管理系统

本项目是要开发一个图书馆管理系统,通过这个系统处理常见的图书馆业务。这个系统主要功能是:(1)有客户端(借阅者使用)和管理端(图书馆管理员和系统管理员使用)。(2&#…...

信号【Linux】

文章目录 信号处理方式(信号递达)前后台进程 终端按键产生信号kill系统调用接口向进程发信号阻塞信号sigset_tsigprocmasksigpending内核态与用户态:内核空间与用户空间内核如何实现信号的捕捉 1、信号就算没有产生,进程也必须识别…...

Kafka Producer之ACKS应答机制

文章目录 1. 应答机制2. 等级03. 等级14. 等级all5. 设置等级6. ISR 1. 应答机制 异步发送的效率高,但是不安全,同步发送安全,但是效率低。 无论哪一种,有一个关键的步骤叫做回调,也就是ACKS应答机制。 其中ACKS也分…...

【深入理解SpringCloud微服务】深入理解Eureka核心原理

深入理解Eureka核心原理 Eureka整体设计Eureka服务端启动Eureka三级缓存Eureka客户端启动 Eureka整体设计 Eureka是一个经典的注册中心,通过http接收客户端的服务发现和服务注册请求,使用内存注册表保存客户端注册上来的实例信息。 Eureka服务端接收的…...

算法——滑动窗口(day7)

904.水果成篮 904. 水果成篮 - 力扣(LeetCode) 题目解析: 根据题意我们可以看出给了我们两个篮子说明我们在开始采摘到结束的过程中只能有两种水果的种类,又要求让我们返回收集水果的最大数目,这不难让我们联想到题目…...

Django学习第一天(如何创建和运行app)

前置知识: URL组成部分详解: 一个url由以下几部分组成: scheme://host:port/path/?query-stringxxx#anchor scheme:代表的是访问的协议,一般为http或者ftp等 host:主机名,域名,…...

VScode连接虚拟机运行Python文件的方法

声明:本文使用Linux发行版本为rocky_9.4 目录 1. 在rocky_9.4最小安装的系统中,默认是没有tar工具的,因此,要先下载tar工具 2. 在安装好的vscode中下载ssh远程插件工具 3. 然后连接虚拟机 4. 查看python是否已经安装 5. 下载…...

通义千问AI模型对接飞书机器人-模型配置(2-1)

一 背景 根据业务或者使用场景搭建自定义的智能ai模型机器人,可以较少我们人工回答的沟通成本,而且可以更加便捷的了解业务需求给出大家设定的业务范围的回答,目前基于阿里云的通义千问模型研究。 二 模型研究 参考阿里云帮助文档…...

[k8s源码]6.reflector

Reflector 和 Informer 是 Kubernetes 客户端库中两个密切相关但职责不同的组件。Reflector 是一个较低级别的组件,主要负责与 Kubernetes API 服务器进行交互,执行资源的初始列表操作和持续的监视操作,将获取到的数据放入队列中。而 Informe…...

前台文本直接取数据库值doFieldSQL插入SQL

实现功能:根据选择的车间主任带出角色。 实现步骤:OA的“字段联动”功能下拉选项带不出表“hrmrolemembers”,所以采用此方法。 doFieldSQL("select roleid from HrmResource as a inner join hrmrolemembers as b on a.id b.resource…...

【06】LLaMA-Factory微调大模型——微调模型评估

上文【05】LLaMA-Factory微调大模型——初尝微调模型,对LLama-3与Qwen-2进行了指令微调,本文则介绍如何对微调后的模型进行评估分析。 一、部署微调后的LLama-3模型 激活虚拟环境,打开LLaMA-Factory的webui页面 conda activate GLM cd LLa…...

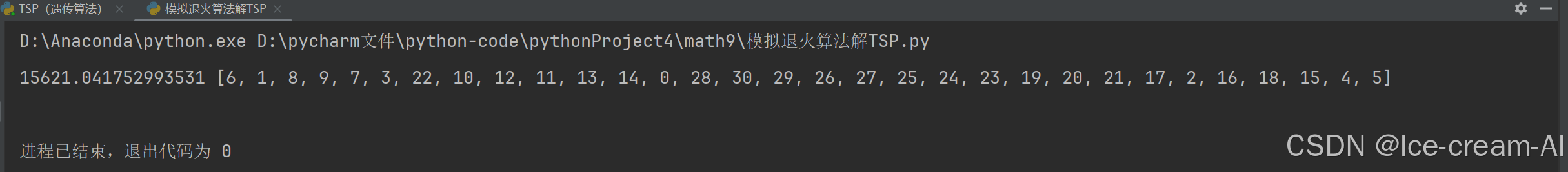

数学建模学习(1)遗传算法

一、简介 遗传算法(Genetic Algorithm, GA)是一种用于解决优化和搜索问题的进化算法。它基于自然选择和遗传学原理,通过模拟生物进化过程来寻找最优解。 以下是遗传算法的主要步骤和概念: 初始化种群(Initialization&a…...

NumPy冷知识66个

NumPy冷知识66个 多维切片: NumPy支持多维切片,可以通过指定多个索引来提取多维数组的子集。 复杂数支持: NumPy可以处理复数,提供了复数的基本运算和函数。 比特运算: NumPy支持比特运算,如与、或、异或等。 数据存储格式: NumPy可以将数…...

Wi-SUN无线通信技术 — 大规模分散式物联网应用首选

引言 在数字化浪潮的推动下,物联网(IoT)正逐渐渗透到我们生活的方方面面。Wi-SUN技术以其卓越的性能和广泛的应用前景,成为了大规模分散式物联网应用的首选。本文将深入探讨Wi-SUN技术的市场现状、核心优势、实际应用中的案例以及…...

在 Ubuntu Server 22.04 上安装 Docker 的详细步骤

在 Ubuntu Server 22.04 上安装 Docker 的详细步骤 本文档详细记录了在 Ubuntu Server 22.04 上安装 Docker 的完整过程,包括解决过程中遇到的问题。希望能对读者有所帮助。 安装过程,重点需要看官方文档。https://docs.docker.com/engine/install/ubu…...

- 素材嵌套 - 加载阶段)

前端使用 Konva 实现可视化设计器(18)- 素材嵌套 - 加载阶段

本章主要实现素材的嵌套(加载阶段)这意味着可以拖入画布的对象,不只是图片素材,还可以是嵌套的图片和图形。 请大家动动小手,给我一个免费的 Star 吧~ 大家如果发现了 Bug,欢迎来提 Issue 哟~ github源码 g…...

vue3 -layui项目-左侧导航菜单栏

1.创建目录结构 进入cmd,先cd到项目目录(项目vue3-project) cd vue3-project mkdir -p src\\views\\home\\components\\menubar 2.创建组件文件 3.编辑menu-item-content.vue <template><template v-if"item.icon"><lay-ic…...

Spring AOP(1)

目录 一、AOP 概述 什么是Spring AOP? 二、Spring AOP 快速入门 1、引入AOP依赖 2、编写AOP程序 三、Spring AOP 详解 1、Spring AOP的核心概念 (1)切点(Pointcut) (2)连接点ÿ…...

GodotPckTool 终极指南:如何在命令行中高效管理Godot游戏资源包

GodotPckTool 终极指南:如何在命令行中高效管理Godot游戏资源包 【免费下载链接】GodotPckTool Standalone tool for extracting and creating Godot .pck files 项目地址: https://gitcode.com/gh_mirrors/go/GodotPckTool 你是否曾经需要在不启动Godot引擎…...

)

别再手动改稿了!用LaTeX的soul包搞定论文批注(删除线/高亮/引用兼容)

LaTeX高效批注指南:用soul包实现学术协作的优雅排版 当导师的红色批注铺满论文初稿,或是合作者发来二十处修改意见时,大多数研究者都会面临一个共同困境——如何在保留原始内容的同时清晰标记修改痕迹?传统的手动添加删除线或高亮…...

深入解析Nordic NRF52832的NFC天线与GPIO复用设计

1. NFC天线硬件设计基础 NRF52832芯片的NFC功能通过P0.09和P0.10两个专用引脚实现,这两个引脚在设计时需要特别注意硬件连接规范。实际项目中,我遇到过不少开发者直接将这两个引脚当作普通GPIO使用导致通信异常的情况——因为默认状态下它们被硬件映射为…...

微信小程序物流信息对接实战:发货接口的完整实现指南

1. 微信小程序物流对接的核心价值 对于电商类小程序来说,物流信息同步是用户体验的关键环节。当用户下单后,最关心的就是"我的包裹到哪了"。传统做法需要用户手动复制单号到第三方平台查询,而通过微信官方物流接口,可以…...

QuickSnap:提升三维建模效率的快速对齐工具——三维建模爱好者的精准对齐解决方案

QuickSnap:提升三维建模效率的快速对齐工具——三维建模爱好者的精准对齐解决方案 【免费下载链接】quicksnap Blender addon to quickly snap objects/vertices/points to object origins/vertices/points 项目地址: https://gitcode.com/gh_mirrors/qu/quicksna…...

HelixDB部署与运维:从本地开发到生产环境的完整流程

HelixDB部署与运维:从本地开发到生产环境的完整流程 【免费下载链接】helix-db HelixDB is a powerful, graph-vector database built entirely in Rust for millisecond query latency and ease of use. 项目地址: https://gitcode.com/gh_mirrors/he/helix-db …...

7个实用技巧:从零开始开发jquery-qrcode自定义二维码生成器

7个实用技巧:从零开始开发jquery-qrcode自定义二维码生成器 【免费下载链接】jquery-qrcode qrcode generation standalone (doesnt depend on external services) 项目地址: https://gitcode.com/gh_mirrors/jq/jquery-qrcode jquery-qrcode是一款轻量级的纯…...

保姆级教程:在Windows系统本地部署Qwen3-14B-Int4-AWQ对话模型

保姆级教程:在Windows系统本地部署Qwen3-14B-Int4-AWQ对话模型 1. 前言:为什么选择本地部署? 在个人电脑上运行大语言模型听起来可能有些遥不可及,但随着模型量化技术的进步,现在即使是消费级显卡也能流畅运行14B参数…...

程序实现环境温度对传感器的误差补偿,不同温度下测量精度一致,颠覆温漂难题。

无论你是做工业传感还是消费电子,只要你测物理量(电压、电流、压力、流量),温度就是精度的头号杀手。今天我们用 Python 打造一套自适应温度补偿系统,让仪器在不同温度下“不忘初心”。一、 实际应用场景描述 (Scenari…...

FreeRTOS数据通信避坑指南:为什么我的MessageBuffer总是接收失败?

FreeRTOS消息缓冲区实战:从接收失败到高效通信的深度解析 第一次在FreeRTOS项目中使用MessageBuffer时,我遇到了一个令人抓狂的问题——明明发送端显示消息已成功写入,接收端却总是返回0字节。调试器显示缓冲区非空,但xMessageBuf…...