Verilog HDL语言入门(二)

- 强烈建议用同步设计

2.在设计时总是记住时序问题

3.在一个设计开始就要考虑到地电平或高电平复位、同步或异步复位、上升沿或下降沿触发等问题,在所有模块中都要遵守它

4.在不同的情况下用if和case,最好少用if的多层嵌套(1层或2层比较合适,当在3层以上时,最好修改写法,因为这样不仅可以reduce area,而且可以获得好的timing)

5.在锁存一个信号或总线时要小心,对于整个design,尽量避免使用latch,因为在DFT时很难test。

6.确信所有的信号被复位,在DFT时,所有的FlipFlop都是controllable,

7.永远不要再写入之前读取任何内部存储器(如SRAM)

8.从一个时钟到另一个不同的时钟传输数据时用数据缓冲,他工作像一个双时钟FIFO(是异步的),可以用Async SRAM搭建Async FIFO。

9.在VHDL中二维数组可以使用,它是非常有用的。在VERILOG中他仅仅可以使用在测试模块中,不能被综合

10.遵守register-in register-out规则

11.像synopsys的DC的综合工具是非常稳定的,任何bugs都不会从综合工具中产生

12.确保FPGA版本与ASIC的版本尽可能的相似,特别是SRAM类型,若版本一致是最理想的,但是在工作中FPGA版本一般用FPGA自带的SRAM,ASIC版本一般用厂商提供的SRAM。

13.在嵌入式存储器中使用BIST

14.虚单元和一些修正电路是必需的

15.一些简单的测试电路也是需要的,经常在一个芯片中有许多测试模块

16.除非低功耗不要用门控时钟,强烈建议不要在design中使用gate clock

17.不要依靠脚本来保证设计。但是在脚本中的一些好的约束能够起到更好的性能(例如前向加法器)

18.如果时间充裕,通过时钟做一个多锁存器来取代用MUX

19.不要用内部tri-state, ASIC需要总线保持器来处理内部tri-state,如IO cell。

20.在top level中作pad insertion

21.选择pad时要小心(如上拉能力,施密特触发器,5伏耐压等),选择合适的IO cell

22.小心由时钟偏差引起的问题

23.不要试着产生半周期信号

24.如果有很多函数要修正,请一个一个地作,修正一个函数检查一个函数

25.在一个计算等式中排列每个信号的位数是一个好习惯,即使综合工具能做

26.不要使用HDL提供的除法器

27.削减不必要的时钟。它会在设计和布局中引起很多麻烦,大多数FPGA有1-4个专门的时钟通道

良好代码编写风格可以满足信、达、雅的要求。在满足功能和性能目标的前提下,增强代码的可读性、可移植性,首要的工作是在项目开发之前为整个设计团队建立一个命名约定和缩略语清单,以文档的形式记录下来,并要求每位设计人员在代码编写过程中都要严格遵守。良好代码编写风格的通则概括如下:

(1) 对所有的信号名、变量名和端口名都用小写,这样做是为了和业界的习惯保持一致;对常量名和用户定义的类型用大写;

(2) 使用有意义的信号名、端口名、函数名和参数名;

(3) 信号名长度不要太长;

(4) 对于时钟信号使用clk 作为信号名,如果设计中存在多个时钟,使用clk 作为时钟信号的前缀;

(5) 对来自同一驱动源的信号在不同的子模块中采用相同的名字,这要求在芯片总体设计时就定义好顶层子模块间连线的名字,端口和连接端口的信号尽可能采用相同的名字;

(6) 对于低电平有效的信号,应该以一个下划线跟一个小写字母b 或n 表示。注意在同一个设计中要使用同一个小写字母表示低电平有效;

(7) 对于复位信号使用rst 作为信号名,如果复位信号是低电平有效,建议使用rst_n;

(8) 当描述多比特总线时,使用一致的定义顺序,对于verilog 建议采用bus_signal[x:0]的表示;

(9) 尽量遵循业界已经习惯的一些约定。如*_r 表示寄存器输出,*_a 表示异步信号,*_pn 表示多周期路径第n 个周期使用的信号,*_nxt 表示锁存前的信号,*_z 表示三态信号等;

(10)在源文件、批处理文件的开始应该包含一个文件头、文件头一般包含的内容如下例所示:文件名,作者,模块的实现功能概述和关键特性描述,文件创建和修改的记录,包括修改时间,修改的内容等;

(11)使用适当的注释来解释所有的always 进程、函数、端口定义、信号含义、变量含义或信号组、变量组的意义等。注释应该放在它所注释的代码附近,要求简明扼要,只要足够说明设计意图即可,避免过于复杂;

(12)每一行语句独立成行。尽管VHDL 和Verilog 都允许一行可以写多个语句,当时每个语句独立成行可以增加可读性和可维护性。同时保持每行小于或等于72 个字符,这样做都是为了提高代码得可读性;

(13)建议采用缩进提高续行和嵌套语句得可读性。缩进一般采用两个空格,如西安交通大学SOC 设计中心2 如果空格太多则在深层嵌套时限制行长。同时缩进避免使用TAB 键,这样可以避免不同机器TAB 键得设置不同限制代码得可移植能力;

(14)在RTL 源码的设计中任何元素包括端口、信号、变量、函数、任务、模块等的命名都不能取Verilog 和VHDL 语言的关键字;

(15)在进行模块的端口申明时,每行只申明一个端口,并建议采用以下顺序:

输入信号的clk、rst、enables other control signals、data and address signals。然后再申明输出信号的clk、rst、enalbes other control signals、data signals;

(16)在例化模块时,使用名字相关的显式映射而不要采用位置相关的映射,这样可以提高代码的可读性和方便debug 连线错误;

(17)如果同一段代码需要重复多次,尽可能使用函数,如果有可能,可以将函数通用化,以使得它可以复用。注意,内部函数的定义一般要添加注释,这样可以提高代码的可读性;

(18)尽可能使用循环语句和寄存器组来提高源代码的可读性,这样可以有效地减少代码行数;

(19)对一些重要的always 语句块定义一个有意义的标号,这样有助于调试。注意标号名不要与信号名、变量名重复;

(20)代码编写时的数据类型只使用IEEE 定义的标准类型,在VHDL 语言中,设计者可以定义新的类型和子类型,但是所有这些都必须基于IEEE 的标准;

(21)在设计中不要直接使用数字,作为例外,可以使用0 和1。建议采用参数定义代替直接的数字。同时,在定义常量时,如果一个常量依赖于另一个常量,建议在定义该常量时用表达式表示出这种关系;

(22)不要在源代码中使用嵌入式的dc_shell 综合命令。这是因为其他的综合工具并不认得这些隐含命令,从而导致错误的或较差的综合结果。即使使用Design Compiler,当综合策略改变时,嵌入式的综合命令也不如放到批处理综合文件中易于维护。这个规则有一个例外的综合命令,即编译开关的打开和关闭可以嵌入到代码中;

(23)在设计中避免实例化具体的门级电路。门级电路可读性差,且难于理解和维护,如果使用特定工艺的门电路,设计将变得不可移植。如果必须实例化门电路,我们建议采用独立于工艺库的门电路,如SYNOPSYS 公司提供的GTECH 库包含了高质量的常用的门级电路;

(24)避免冗长的逻辑和子表达式;

(25)避免采用内部三态电路,建议用多路选择电路代替内部三态电路。

规则 #1: 建立时序逻辑模型时,采用非阻塞赋值语句。

zC&q,s[1]F4RE0规则 #2: 建立latch模型时,采用非阻塞赋值语句。EDA中国门户网站1X!y4m]0r O B

规则 #3: 在always块中建立组合逻辑模型时,采用阻塞赋值语句。

2n$DW8?$@6W0规则 #4: 在一个always块中同时有组合和时序逻辑时时,采用非阻塞赋值语句。

'r"z T2x4p'n4U `0规则 #5: 不要在一个always块中同时采用阻塞和非阻塞赋值语句。

^p/ulTO+B0规则 #6: 同一个变量不要在多个always块中赋值。EDA中国门户网站8q%UOC%yX b:Ma

规则 #7: 调用$strobe系统函数显示用非阻塞赋值语句赋的值。EDA中国门户网站$U&]&wg4w-FE5a

规则 #8: 不要使用#0延时赋值。

组合逻辑

1,敏感变量的描述完备性

Verilog中,用always块设计组合逻辑电路时,在赋值表达式右端参与赋值的所有信号都必须在always @(敏感电平列表)中列出,always中if语句的判断表达式必须在敏感电平列表中列出。如果在赋值表达式右端引用了敏感电平列表中没有列出的信号,在综合时将会为没有列出的信号隐含地产生一个透明锁存器。这是因为该信号的变化不会立刻引起所赋值的变化,而必须等到敏感电平列表中的某一个信号变化时,它的作用才表现出来,即相当于存在一个透明锁存器,把该信号的变化暂存起来,待敏感电平列表中的某一个

信号变化时再起作用,纯组合逻辑电路不可能作到这一点。综合器会发出警告。

Example1:

input a,b,c;

reg e,d;

always @(a or b or c)

begin

e=d&a&b; /*d没有在敏感电平列表中,d变化时e不会立刻变化,直到a,b,c中某一个变化*/

d=e |c;

end

Example2:

input a,b,c;

reg e,d;

always @(a or b or c or d)

begin

e=d&a&b; /*d在敏感电平列表中,d变化时e立刻变化*/

d=e |c;

end

2,条件的描述完备性

如果if语句和case语句的条件描述不完备,也会造成不必要的锁存器。

Example1:

if (a==1'b1) q=1'b1;//如果a==1'b0,q=? q将保持原值不变,生成锁存器!

Example2:

if (a==1'b1) q=1'b1;

else q=1'b0;//q有明确的值。不会生成锁存器!

Example3:

reg[1:0] a,q;

....

case (a)

2'b00 : q=2'b00;

2'b01 : q=2'b11;//如果a==2'b10或a==2'b11,q=? q将保持原值不变,锁存器!

endcase

Example4:

reg[1:0] a,q;

....

case (a)

2'b00 : q=2'b00;

2'b01 : q=2'b11;

default: q=2'b00;//q有明确的值。不会生成锁存器!

endcase

Verilog中端口的描述

1,端口的位宽最好定义在I/O说明中,不要放在数据类型定义中;

Example1:

module test(addr,read,write,datain,dataout)

input[7:0] datain;

input[15:0] addr;

input read,write;

output[7:0] dataout; //要这样定义端口的位宽!

wire addr,read,write,datain;

reg dataout;

Example2:

module test(addr,read,write,datain,dataout)

input datain,addr,read,write;

output dataout;

wire[15:0] addr;

wire[7:0] datain;

wire read,write;

reg[7:0] dataout; //不要这样定义端口的位宽!!

2,端口的I/O与数据类型的关系:

端口的I/O 端口的数据类型

module内部 module外部

input wire wire或reg

output wire或reg wire

inout wire wire

3,assign语句的左端变量必须是wire;直接用"="给变量赋值时左端变量必须是reg!

Example:

assign a=b; //a必须被定义为wire!!

********

begin

a=b; //a必须被定义为reg!

end

VHDL中STD_LOGIC_VECTOR和INTEGER的区别

例如A是INTEGER型,范围从0到255;B是STD_LOGIC_VECTOR,定义为8位。A累加到255时,再加1就一直保持255不变,不会自动反转到0,除非令其为0;而B累加到255时,再加1就会自动反转到0。所以在使用时要特别注意!

以触发器为例说明描述的规范性

1,无置位/清零的时序逻辑

always @( posedge CLK)

begin

Q<=D;

end

2,有异步置位/清零的时序逻辑

异步置位/清零是与时钟无关的,当异步置位/清零信号到来时,触发器的输出立即 被置为1或0,不需要等到时钟沿到来才置位/清零。所以,必须要把置位/清零信号 列入always块的事件控制表达式。

always @( posedge CLK or negedge RESET)

begin

if (!RESET)

Q=0;

else

Q<=D;

end

3,有同步置位/清零的时序逻辑

同步置位/清零是指只有在时钟的有效跳变时刻置位/清零,才能使触发器的输出分 别转换为1或0。所以,不要把置位/清零信号列入always块的事件控制表达式。但是 必须在always块中首先检查置位/清零信号的电平。

always @( posedge CLK )

begin

if (!RESET)

Q=0;

else

Q<=D;

end

结构规范性

在整个芯片设计项目中,行为设计和结构设计的编码是最重要的一个步骤。 它对逻辑综合和布线结果、时序测定、校验能力、测试能力甚至产品支持 都有重要的影响。考虑到仿真器和真实的逻辑电路之间的差异,为了有效的

进行仿真测试:

1,避免使用内部生成的时钟

内部生成的时钟称为门生时钟(gated clock)。如果外部输入时钟和门生时钟同时驱动, 则不可避免的两者的步调不一致,造成逻辑混乱。而且,门生时钟将会增加测试的难度 和时间。

2,绝对避免使用内部生成的异步置位/清零信号

内部生成的置位/清零信号会引起测试问题。使某些输出信号被置位或清零,无法正常 测试。

3,避免使用锁存器

锁存器可能引起测试问题。对于测试向量自动生成(ATPG), 为了使扫描进行,锁存器需要置为透明模式(transparent mode), 反过来,测试锁存器需要构造特定的向量,这可非同一般。

4,时序过程要有明确的复位值

使触发器带有复位端,在制造测试、ATPG以及模拟初始化时,可以对整个电路进行 快速复位。

5,避免模块内的三态/双向

内部三态信号在制造测试和逻辑综合过程中难于处理.

近日读 J.Bhasker 的<verilog synthesis practical primer> , 受益匪浅,理清了不少基础电路知识 , 记下一些 tips :

1. 过程赋值(always 中触发赋值)的变量,可能会被综合成连线 或触发器 或锁存器.

2.综合成锁存器的规则:

a. 变量在条件语句(if 或case)中,被赋值.

b. 变量未在条件语句的所有分支中被赋值.

c. 在always语句多次调用之间需要保持变量值 .

以上三个条件必须同时满足.

3.综合成触发器的规则:

变量在时钟沿的控制下被赋值。

例外情况:变量的赋值和引用都仅出现在一条always语句中,则该变量被视为中

间变量而不是触发器。

4. 对于无时钟事情的always语句(即组合逻辑建模),其时间表应包括该alwa语

句引用的所有变量,否则会出现RTL与Netlist的不一致

芯片外部引脚很多都使用inout类型的,为的是节省管腿。一般信号线用做总线等双向数据传输的时候就要用到INOUT类型了。就是一个端口同时做输入和输出。 inout在具体实现上一般用三态门来实现。三态门的第三个状态就是高阻'Z'。 当inout端口不输出时,将三态门置高阻。这样信号就不会因为两端同时输出而出错了,更详细的内容可以搜索一下三态门tri-state的资料.

1 使用inout类型数据,可以用如下写法:

inout data_inout;

input data_in;

reg data_reg;//data_inout的映象寄存器

reg link_data;

assign data_inout=link_data?data_reg:1’bz;//link_data控制三态门

//对于data_reg,可以通过组合逻辑或者时序逻辑根据data_in对其赋值.通过控制link_data的高低电平,从而设置data_inout是输出数据还是处于高阻态,如果处于高阻态,则此时当作输入端口使用.link_data可以通过相关电路来控制.

2 编写测试模块时,对于inout类型的端口,需要定义成wire类型变量,而其它输入端口都定义成reg类型,这两者是有区别的.

当上面例子中的data_inout用作输入时,需要赋值给data_inout,其余情况可以断开.此时可以用assign语句实现:assign data_inout=link?data_in_t:1’bz;其中的link ,data_in_t是reg类型变量,在测试模块中赋值.

另外,可以设置一个输出端口观察data_inout用作输出的情况:

Wire data_out;

Assign data_out_t=(!link)?data_inout:1’bz;

else,in RTL

inout use in top module(PAD)

dont use inout(tri) in sub module

也就是说,在内部模块最好不要出现inout,如果确实需要,那么用两个port实现,到顶层的时候再用三态实现。理由是:在非顶层模块用双向口的话,该双向口必然有它的上层跟它相连。既然是双向口,则上层至少有一个输入口和一个输出口联到该双向口上,则发生两个内部输出单元连接到一起的情况出现,这样在综合时往往会出错。

对双向口,我们可以将其理解为2个分量:一个输入分量,一个输出分量。另外还需要一个控制信号控制输出分量何时输出。此时,我们就可以很容易地对双向端口建模。

例子:

CODE:

module dual_port (

....

inout_pin,

....

);

inout inout_pin;

wire inout_pin;

wire input_of_inout;

wire output_of_inout;

wire out_en;

assign input_of_inout = inout_pin;

assign inout_pin = out_en ? output_of_inout : 高阻;

endmodule

可见,此时input_of_inout和output_of_inout就可以当作普通信号使用了。

在仿真的时候,需要注意双向口的处理。如果是直接与另外一个模块的双向口连接,那么只要保证一个模块在输出的时候,另外一个模块没有输出(处于高阻态)就可以了。

如果是在ModelSim中作为单独的模块仿真,那么在模块输出的时候,不能使用force命令将其设为高阻态,而是使用release命令将总线释放掉

很多初学者在写testbench进行仿真和验证的时候,被inout双向口难住了。仿真器老是提示错误不能进行。下面是我个人对inout端口写testbench仿真的一些总结,并举例进行说明。在这里先要说明一下inout口在testbench中要定义为wire型变量。

先假设有一源代码为:

module xx(data_inout , ........);

inout data_inout;

........................

assign data_inout=(! link)?datareg:1'bz;

endmodule

方法一:使用相反控制信号inout口,等于两个模块之间用inout双向口互连。这种方法要注意assign 语句只能放在initial和always块内。

module test();

wire data_inout;

reg data_reg;

reg link;

initial begin

..........

end

assign data_inout=link?data_reg:1'bz;

endmodule

方法二:使用force和release语句,但这种方法不能准确反映双向端口的信号变化,但这种方法可以反在块内。

module test();

wire data_inout;

reg data_reg;

reg link;

#xx; //延时

force data_inout=1'bx; //强制作为输入端口

...............

#xx;

release data_inout; //释放输入端口

endmodule

很多读者反映仿真双向端口的时候遇到困难,这里介绍一下双向端口的仿真方法。一个典型的双向端口如图1所示。

其中inner_port与芯片内部其他逻辑相连,outer_port为芯片外部管脚,out_en用于控制双向端口的方向,out_en为1时,端口为输出方向,out_en为0时,端口为输入方向。

用Verilog语言描述如下:

module bidirection_io(inner_port,out_en,outer_port);

input out_en;

inout[7:0] inner_port;

inout[7:0] outer_port;

assign outer_port=(out_en==1)?inner_port:8'hzz;

assign inner_port=(out_en==0)?outer_port:8'hzz;

endmodule

用VHDL语言描述双向端口如下:

library ieee;

use IEEE.STD_LOGIC_1164.ALL;

entity bidirection_io is

port ( inner_port : inout std_logic_vector(7 downto 0);

out_en : in std_logic;

outer_port : inout std_logic_vector(7 downto 0) );

end bidirection_io;

architecture behavioral of bidirection_io is

begin

outer_port<=inner_port when out_en='1' else (OTHERS=>'Z');

inner_port<=outer_port when out_en='0' else (OTHERS=>'Z');

end behavioral;

仿真时需要验证双向端口能正确输出数据,以及正确读入数据,因此需要驱动out_en端口,当out_en端口为1时,testbench驱动inner_port端口,然后检查outer_port端口输出的数据是否正确;当out_en端口为0时,testbench驱动outer_port端口,然后检查inner_port端口读入的数据是否正确。由于inner_port和outer_port端口都是双向端口(在VHDL和Verilog语言中都用inout定义),因此驱动方法与单向端口有所不同。

验证该双向端口的testbench结构如图2所示。

这是一个self-checking testbench,可以自动检查仿真结果是否正确,并在Modelsim控制台上打印出提示信息。图中Monitor完成信号采样、结果自动比较的功能。

testbench的工作过程为

1)out_en=1时,双向端口处于输出状态,testbench给inner_port_tb_reg信号赋值,然后读取outer_port_tb_wire的值,如果两者一致,双向端口工作正常。

2)out_en=0时,双向端口处于输如状态,testbench给outer_port_tb_reg信号赋值,然后读取inner_port_tb_wire的值,如果两者一致,双向端口工作正常。

用Verilog代码编写的testbench如下,其中使用了自动结果比较,随机化激励产生等技术。

`timescale 1ns/10ps

module tb();

reg[7:0] inner_port_tb_reg;

wire[7:0] inner_port_tb_wire;

reg[7:0] outer_port_tb_reg;

wire[7:0] outer_port_tb_wire;

reg out_en_tb;

integer i;

initial

begin

out_en_tb=0;

inner_port_tb_reg=0;

outer_port_tb_reg=0;

i=0;

repeat(20)

begin

#50

i=$random;

out_en_tb=i[0]; //randomize out_en_tb

inner_port_tb_reg=$random; //randomize data

outer_port_tb_reg=$random;

end

end

//**** drive the ports connecting to bidirction_io

assign inner_port_tb_wire=(out_en_tb==1)?inner_port_tb_reg:8'hzz;

assign outer_port_tb_wire=(out_en_tb==0)?outer_port_tb_reg:8'hzz;

//instatiate the bidirction_io module

bidirection_io bidirection_io_inst(.inner_port(inner_port_tb_wire),

.out_en(out_en_tb),

.outer_port(outer_port_tb_wire));

//***** monitor ******

always@(out_en_tb,inner_port_tb_wire,outer_port_tb_wire)

begin

#1;

if(outer_port_tb_wire===inner_port_tb_wire)

begin

$display("\n **** time=%t ****",$time);

$display("OK! out_en=%d",out_en_tb);

$display("OK! outer_port_tb_wire=%d,inner_port_tb_wire=%d",

outer_port_tb_wire,inner_port_tb_wire);

end

else

begin

$display("\n **** time=%t ****",$time);

$display("ERROR! out_en=%d",out_en_tb);

$display("ERROR! outer_port_tb_wire != inner_port_tb_wire" );

$display("ERROR! outer_port_tb_wire=%d, inner_port_tb_wire=%d",

outer_port_tb_wire,inner_port_tb_wire);

end

end

endmodule

相关文章:

)

Verilog HDL语言入门(二)

强烈建议用同步设计2.在设计时总是记住时序问题3.在一个设计开始就要考虑到地电平或高电平复位、同步或异步复位、上升沿或下降沿触发等问题,在所有模块中都要遵守它4.在不同的情况下用if和case,最好少用if的多层嵌套(1层或2层比较合适&#…...

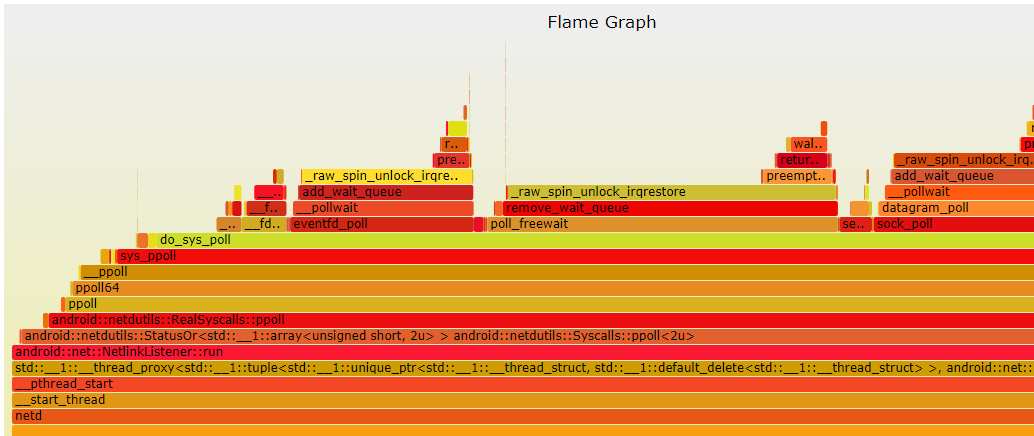

Simpleperf详细使用

一、Simpleperf介绍 Simpleperf是一个强大的命令行工具,它包含在NDK中,可以帮助我们分析应用的CPU性能。Simpleperf可以帮助我们找到应用的热点,而热点往往与性能问题相关,这样我们就可以分析修复热点源。 如果您更喜欢使用命令…...

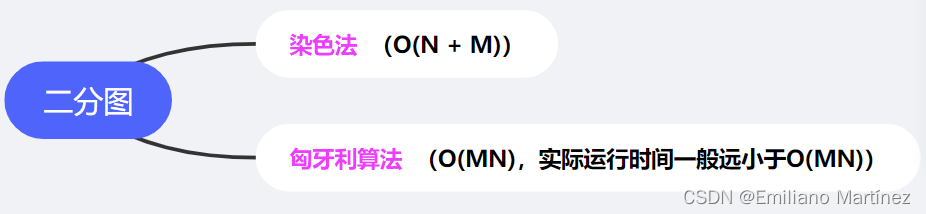

【算法基础】二分图(染色法 匈牙利算法)

一、二分图 1. 染色法 一个图是二分图,当且仅当,图中不含奇数环。在判别一个图是否为二分图⑩,其实相当于染色问题,每条边的两个点必须是不同的颜色,一共有两种颜色,如果染色过程中出现矛盾,则说明不是二分图。 for i = 1 to n:if i 未染色DFS(i, 1); //将i号点染色未…...

Caputo 分数阶微分方程-慢扩散方程初边值问题基于L1 逼近的空间二阶方法及其Matlab程序实现

2.3.3 Caputo 分数阶一维问题基于 L1 逼近的空间二阶方法 考虑如下时间分数阶慢扩散方程初边值问题 { 0 C D t α u ( x , t ) = u...

GPIO驱动)

I.MX6ULL_Linux_驱动篇(29) GPIO驱动

Linux 下的任何外设驱动,最终都是要配置相应的硬件寄存器。所以本篇的 LED 灯驱动最终也是对 I.MX6ULL 的 IO 口进行配置,与裸机实验不同的是,在 Linux 下编写驱动要符合 Linux 的驱动框架。I.MX6U-ALPHA 开发板上的 LED 连接到 I.MX6ULL 的 …...

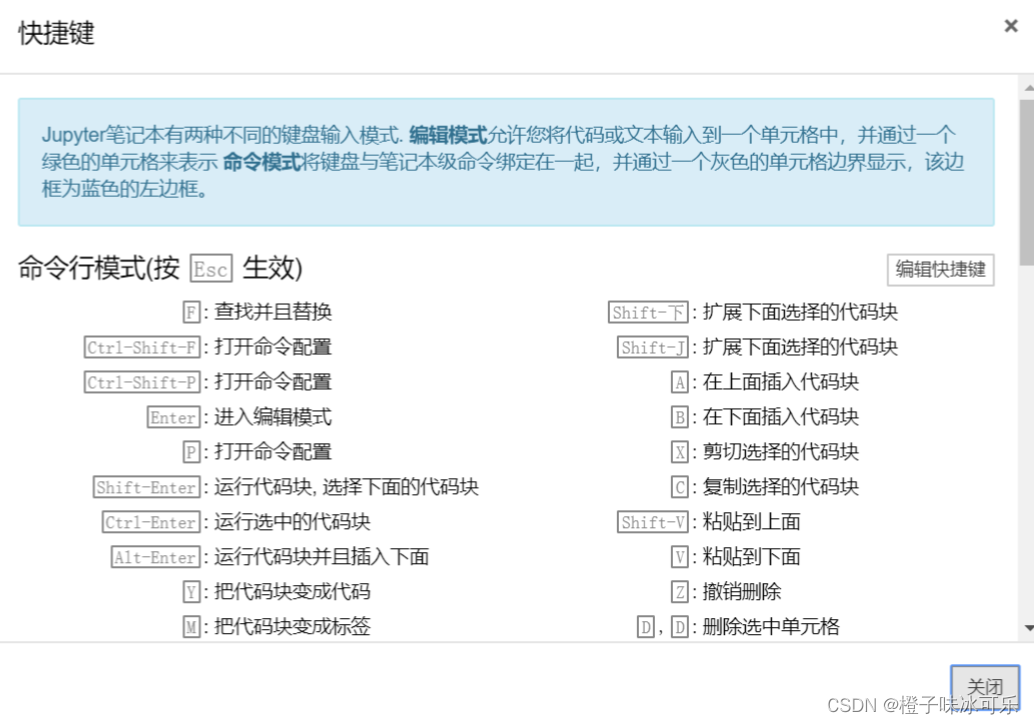

jupyter的安装和使用

目录 ❤ Jupyter Notebook是什么? notebook jupyter 简介 notebook jupyter 组成 网页应用 文档 主要特点 ❤ jupyter notebook的安装 notebook jupyter 安装有两种途径 1.通过Anaconda进行安装 2.通过pip进行安装 启动jupyter notebook ❤ jupyter …...

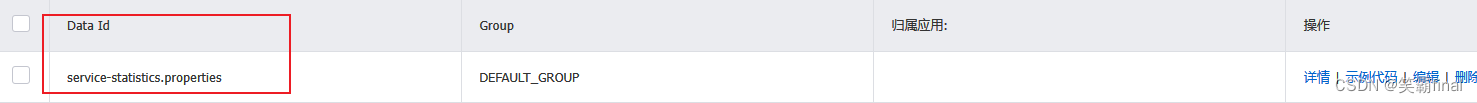

Springboot新手开发 Cloud篇

前言: 👏作者简介:我是笑霸final,一名热爱技术的在校学生。 📝个人主页:个人主页1 || 笑霸final的主页2 📕系列专栏:后端专栏 📧如果文章知识点有错误的地方,…...

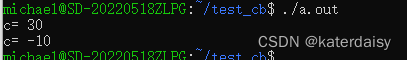

Linux:函数指针做函数参数

#include <stdio.h> #include <stdlib.h> //创建带有函数指针做参数的函数框架api //调用者要先实现回调函数 //调用者再去调用函数框架 //所谓的回调是指 调用者去调用一个带有函数指针做参数的函数框架,函数框架反过来要调用调用者提供的回调函数 …...

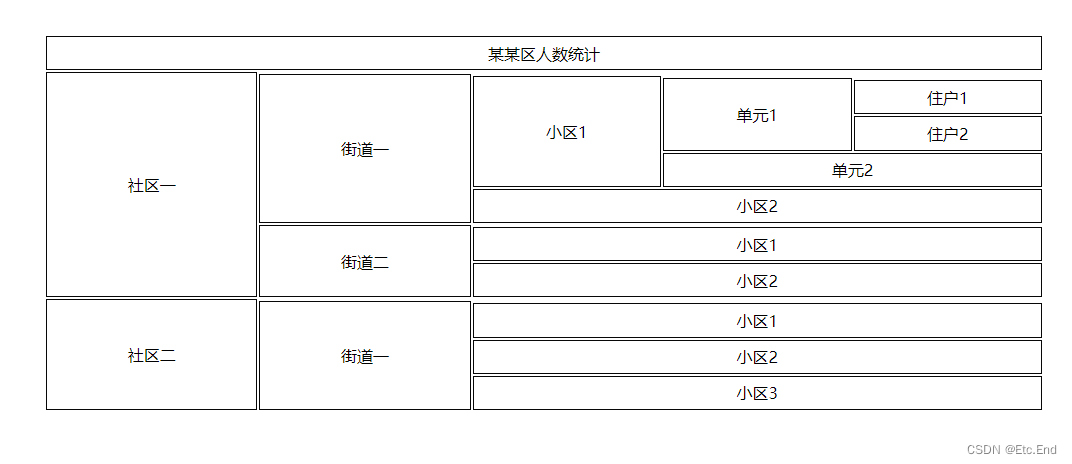

Vue3(递归组件) + 原生Table 实现树结构复杂表格

一、递归组件 什么是递归,Javascript中经常能接触到递归函数。也就是函数自己调用自己。那对于组件来说也是一样的逻辑。平时工作中见得最多应该就是菜单组件,大部分系统里面的都是递归组件。文章中我做了按需引入的配置,所以看不到我引用组…...

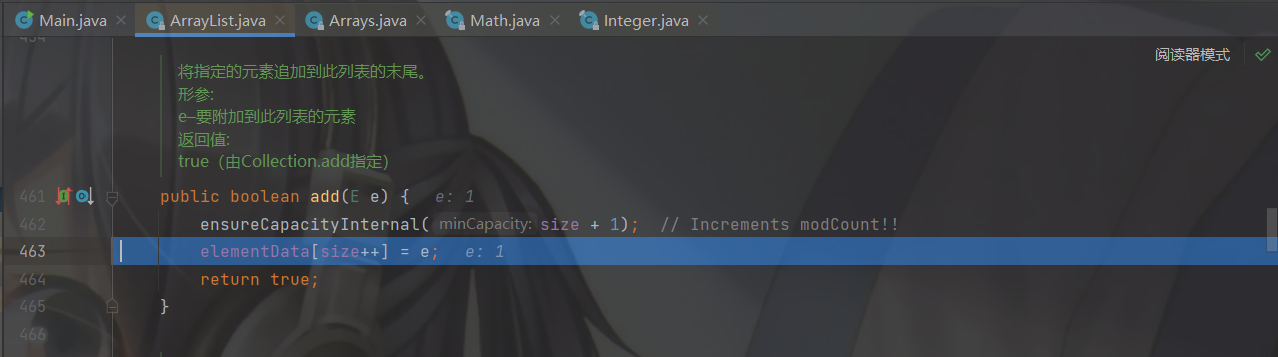

ArrayList底层源码解析

Java源码系列:下方连接 http://t.csdn.cn/Nwzed 文章目录前言一、**ArrayList底层结构和源码分析**无参构造调用创建ArrayList集合无参构造总结:发文3个工作日后 up 会把总结放入前言部分,但也诚邀读者总结,可放入评论区有参构造…...

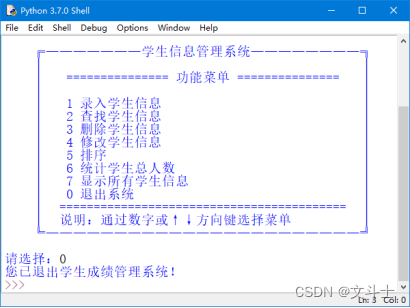

python:DIY字符画的程序使用说明.doc

目录开发环境要求运行方法具体的操作步骤如下:代码示例源码及运行程序下载地址开发环境要求 本系统的软件开发及运行环境具体如下。 操作系统:Windows 7、Windows 10。 Python版本:Python 3.7.0。 开发工具:Python IDLE。 …...

【Python/Opencv】图像权重加法函数:cv2.addWeighted()详解

【Python/Opencv】图像权重加法函数:cv2.addWeighted()详解 文章目录【Python/Opencv】图像权重加法函数:cv2.addWeighted()详解1. 介绍2. API3. 代码示例与效果3.1 代码3.2 效果4. 参考1. 介绍 在OpenCV图像加法cv2.add函数详解详细介绍了图像的加法运…...

容器的老祖宗LXC和Docker的关系

一、什么是LXC? LXC(Linux Container的缩写)是一个基于Linux内核的容器虚拟化技术,它提供了一种轻量级、快速、简便的方式来创建和管理系统容器。与传统虚拟化技术不同,LXC并不会模拟硬件,而是利用Linux内…...

)

Webpack迁移Rspack速攻实战教程(前瞻版)

前言 rspack 即将开源,但社区中不乏有已经落地的 case ,比如 rspack-migration-showcase 、 modern.js 等。 基于此,本文将介绍如何迁移一个近似于 CRA( create-react-app ) 的项目到 rspack 。 在阅读本文前&#…...

一行代码“黑”掉任意网站

文章目录只需一行代码,轻轻一点就可以把任意网站变成暗黑模式。 首先我们先做一个实验,在任意网站中,打开浏览器开发者工具(F12),在 C1onsole 控制台输入如下代码并回车: document.documentElement.style.filterinve…...

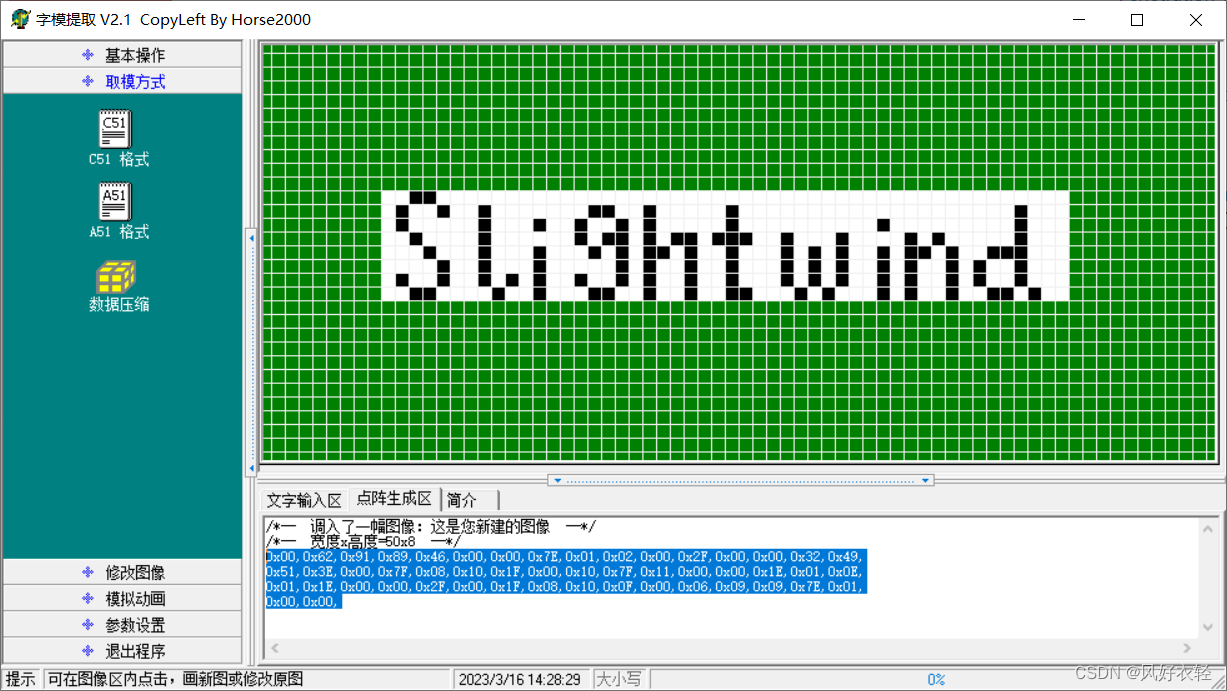

51单片机入门 -驱动 8x8 LED 点阵屏

硬件型号、软件版本、以及烧录流程 操作系统:Windows 10 x84-64单片机:STC89C52RC编译器:SDCC烧录软件:stcgal 1.6开发板:普中51单片机开发板A2套件(2022) 在 VS Code 中新建项目到烧录的过程…...

Xinlinx zynq7045国产替代 FMQL45T900全国产化 ARM 核心板+扩展板

TES745D 是一款基于 FMQL45T900 的全国产化 ARM 核心板。该核心板将 FMQL45T900(与XC7Z045-2FFG900I 兼容)的最小系统集成在了一个 87*117mm 的核心板上,可以作为一个核心模块,进行功能性扩展,能够快速的搭建起一个信号…...

硬刚ChatGPT!文心一言能否为百度止颓?中国版ChatGPT“狂飙”的机会在哪儿?

文章目录目录产品背景发展历程科技简介主要功能合作伙伴结语文心一言 (英文名:ERNIE Bot) *是百度基于文心大模型技术推出的生成式对话产品,被外界誉为“中国版ChatGPT”,将于2023年3月份面向公众开放。 [40] 百度在人…...

Python 异步: 在非阻塞子进程中运行命令(19)

动动发财的小手,点个赞吧! 我们可以从 asyncio 执行命令。该命令将在我们可以使用非阻塞 I/O 写入和读取的子进程中运行。 1. 什么是 asyncio.subprocess.Process asyncio.subprocess.Process 类提供了由 asyncio 运行的子进程的表示。它在 asyncio 程序…...

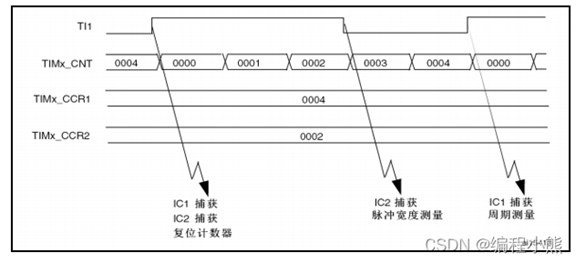

蓝桥杯嵌入式第五课--输入捕获

前言输入捕获的考题十分明确,就是测量输入脉冲波形的占空比和频率,对我们的板子而言,就是检测板载的两个信号发生器产生的信号:具体来说就是使用PA15和PB4来做输入捕获。输入捕获原理简介输入捕获能够对输入信号的上升沿和下降沿进…...

突破实时风格迁移限制:pytorch-AdaIN核心技术与跨场景实践指南

突破实时风格迁移限制:pytorch-AdaIN核心技术与跨场景实践指南 【免费下载链接】pytorch-AdaIN Unofficial pytorch implementation of Arbitrary Style Transfer in Real-time with Adaptive Instance Normalization [Huang, ICCV2017] 项目地址: https://gitcod…...

Qwen3.5-9B量子计算辅助:算法描述理解+Qiskit代码生成+实验设计建议

Qwen3.5-9B量子计算辅助:算法描述理解Qiskit代码生成实验设计建议 1. 项目概述与核心能力 Qwen3.5-9B是一款拥有90亿参数的开源大语言模型,在量子计算领域展现出强大的辅助能力。该模型特别适合用于: 算法描述理解:解析复杂的量…...

玩客云OneCloud轻量级影视站:LibreTV+Docker极简部署指南

1. 为什么选择玩客云搭建影视站? 最近两年,我发现身边越来越多的朋友开始折腾家庭影音系统。有人花大价钱买专业NAS,也有人用旧电脑改造,但最让我眼前一亮的方案,还是用玩客云OneCloud这种小设备搭建影视站。你可能要问…...

效率飞跃:利用快马AI生成智能预标注脚本,让你的labelimg标注速度提升数倍

在图像标注领域,手动标注大量图片一直是个耗时费力的工作。最近我在尝试用AI辅助标注时,发现通过InsCode(快马)平台可以快速实现一个智能预标注工具,让标注效率提升数倍。下面分享我的实践过程和经验总结。 项目背景与痛点分析 传统使用label…...

ReplaceItems.jsx:Adobe Illustrator智能对象替换脚本的技术架构与行业应用深度解析

ReplaceItems.jsx:Adobe Illustrator智能对象替换脚本的技术架构与行业应用深度解析 【免费下载链接】illustrator-scripts Adobe Illustrator scripts 项目地址: https://gitcode.com/gh_mirrors/il/illustrator-scripts 在当今设计工作流中,重复…...

MySQL实战:主键与外键的5个常见设计误区及优化方案

MySQL实战:主键与外键的5个常见设计误区及优化方案 在数据库设计领域,主键和外键的合理运用直接影响着系统的稳定性和查询效率。许多开发者在项目初期往往忽视这些基础元素的设计规范,直到面临性能瓶颈或数据混乱时才追悔莫及。本文将揭示那…...

颠覆式窗口控制:WindowResizer革命性尺寸调整技术全解析

颠覆式窗口控制:WindowResizer革命性尺寸调整技术全解析 【免费下载链接】WindowResizer 一个可以强制调整应用程序窗口大小的工具 项目地址: https://gitcode.com/gh_mirrors/wi/WindowResizer WindowResizer——这款开源窗口尺寸控制工具,正以革…...

Recaptcha2 图像识别 API 集成指南

在本篇文章中,我们将介绍如何集成 Recaptcha2 图像识别 API。该 API 可以识别用户输入的内容和 Recaptcha2 验证图像,最终返回需要点击的小图像的坐标,以完成验证。 环境准备 在使用 API 之前,您需要在 Recaptcha2 图像识别 API…...

Qwen-Turbo-BF16实战案例:电商主图生成——白底产品图+场景化展示图双输出

Qwen-Turbo-BF16实战案例:电商主图生成——白底产品图场景化展示图双输出 1. 电商主图生成的新选择 电商卖家每天都要面对一个头疼的问题:商品主图怎么设计?白底图要干净专业,场景图要吸引眼球,找设计师成本高&#…...

IntelliJ IDEA 2019安装教程及下载

软件介绍: IntelliJ IDEA 是捷克 JetBrains 公司研发的集成开发环境(IDE),主打 Java 和 Kotlin 开发,被誉为 “最佳 Java IDE”,适配不同层级开发者需求;它具备智能代码补全、静态分析、一键重…...