硬件语言Verilog HDL牛客刷题day02 组合逻辑部分

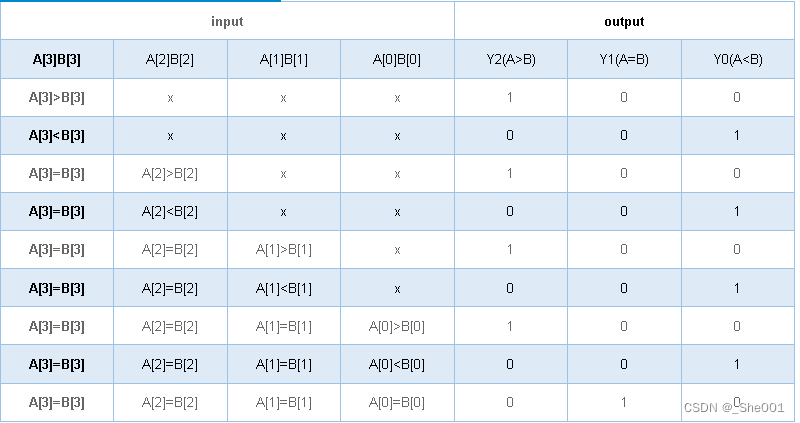

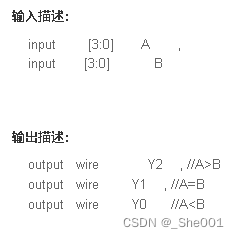

1.VL11 4位数值比较器电路

1.题目:

某4位数值比较器的功能表如下。请用Verilog语言采用门级描述方式,实现此4位数值比较器。

2.解题代码:

`timescale 1ns/1nsmodule comparator_4(input [3:0] A ,input [3:0] B ,output wire Y2 , //A>Boutput wire Y1 , //A=Boutput wire Y0 //A<B

);wire W2[0:3];

wire W1[0:3];

wire W0[0:3];genvar i;

for(i=0;i<4;i=i+1)beginthree_compare U1(.A (A[i]),.B (B[i]),.Y2 (W2[i]),.Y1 (W1[i]),.Y0 (W0[i]));end

assign Y2 = W2[3] | ((W1[3])&&(W2[2])) | ((W1[3]) && (W1[2]) && (W2[1])) | ((W1[3]) && (W1[2]) && (W1[1]) && (W2[0]));

assign Y0 = W0[3] | ((W1[3])&&(W0[2])) | ((W1[3]) && (W1[2]) && (W0[1])) | ((W1[3]) && (W1[2]) && (W1[1]) && (W0[0]));

assign Y1 = W1[3] & W1[2] & W1[1] &W1[0];endmodule//定义另外一个模块 判断三个数的关系

module three_compare(input A, //输入值 1 或者 0 input B, //输入值 1 或者 0output Y2, //假如Y2=1 , 这两个数大于output Y1, //假如Y1=1 ,这两个数等于 output Y0 //假如Y0=1 , 这两个数小于

);assign Y2 = A & (!B); //持续赋值 Y2 大于的标志

assign Y0 = (!A) & B; //持续赋值 Y0 小于的标志

assign Y1 = !(Y2 | Y0); //持续赋值 , 除非Y2 Y0 都不等于1 那时候Y1 =1

endmodule

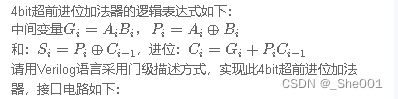

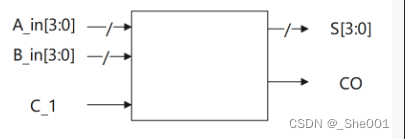

2.VL12 4bit超前进位加法器电路

1.题目:

2.解题代码:

`timescale 1ns/1nsmodule lca_4(input [3:0] A_in ,input [3:0] B_in ,input C_1 ,output wire CO ,output wire [3:0] S

);wire[3:0] G;

wire[3:0] P;

wire[3:0] C;genvar i;

generatefor(i=0;i<4;i=i+1)beginadd_half U1(.A (A_in[i]),.B (B_in[i]),.C (G[i]),.D (P[i]));assign S[i] = (i>0) ? P[i]^C[i-1] : P[i]^C_1;assign C[i] = (i>0) ? G[i] | P[i] & C[i-1] : G[i] + P[i] & C_1;//assign C[i] = (i == 0) ? (G[i] | (P[i] & C_1)) : (G[i] | (P[i] & C[i-1])); //assign S[i] = (i == 0) ? (P[i] ^ C_1) : (P[i] ^ C[i-1]);end

endgenerate

assign CO = C[3];endmodulemodule add_half(

input A,

input B,

output C,

output D

);

assign C = A & B;

assign D = A ^ B;

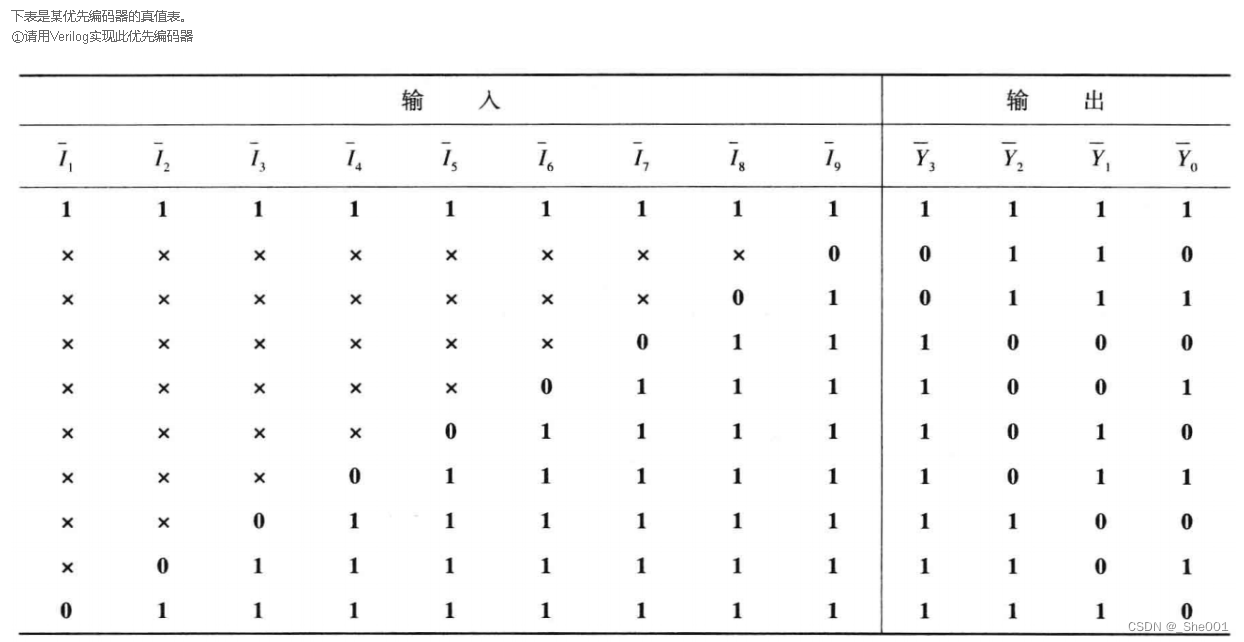

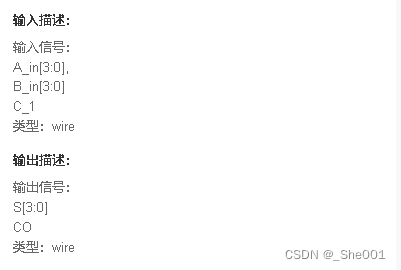

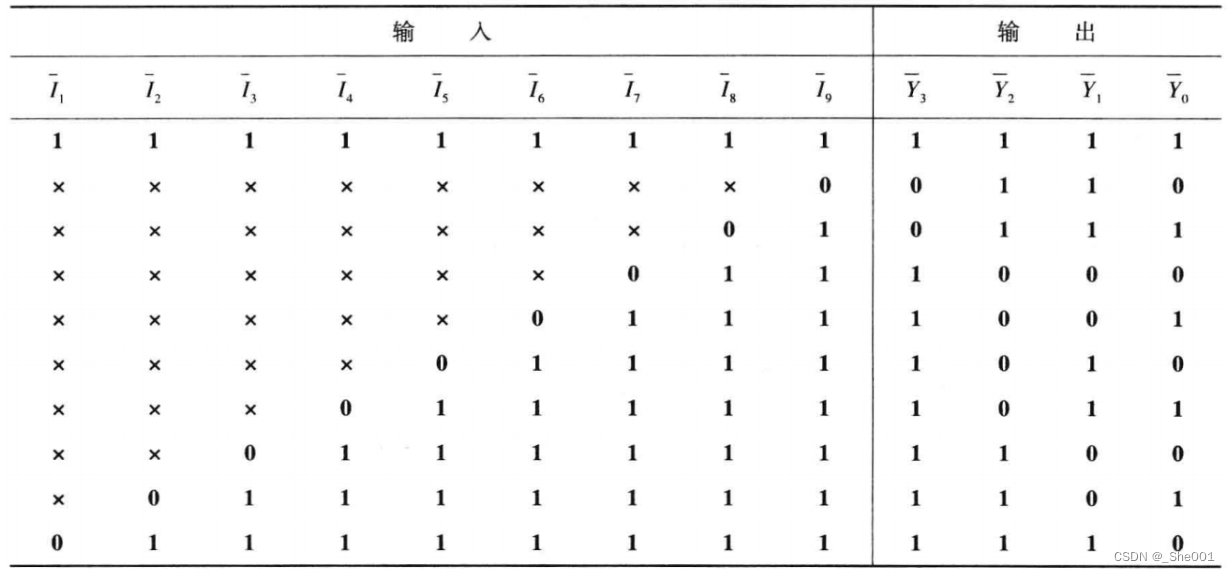

endmodule3.VL13 优先编码器电路①

1.题目:

2.解题代码

`timescale 1ns/1nsmodule encoder_0(input [8:0] I_n ,output reg [3:0] Y_n

);always@(*)begincasex (I_n)9'b1_1111_1111 : Y_n= 4'b1111;9'b0_????_???? : Y_n= 4'b0110;9'b1_0???_???? : Y_n= 4'b0111;9'b1_10??_???? : Y_n= 4'b1000;9'b1_110?_???? : Y_n= 4'b1001;9'b1_1110_???? : Y_n= 4'b1010;9'b1_1111_0??? : Y_n= 4'b1011;9'b1_1111_10?? : Y_n= 4'b1100;9'b1_1111_110? : Y_n= 4'b1101;9'b1_1111_1110 : Y_n= 4'b1110;default: Y_n=4'b0000;endcaseend

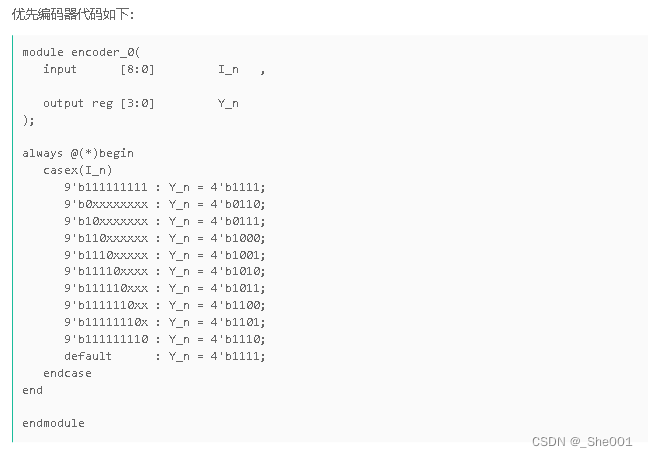

endmodule4.VL14 用优先编码器①实现键盘编码电路

1.题目:

请使用优先编码器①实现键盘编码电路,可添加并例化题目中已给出的优先编码器代码。

10个按键分别对应十进制数0-9,按键9的优先级别最高;按键悬空时,按键输出高电平,按键按下时,按键输出低电平;键盘编码电路的输出是8421BCD码。

要求:键盘编码电路要有工作状态标志,以区分没有按键按下和按键0按下两种情况。

优先编码器真值表如下图:

2.解题代码:

`timescale 1ns/1ns

module encoder_0(input [8:0] I_n ,output reg [3:0] Y_n

);always @(*)begincasex(I_n)9'b111111111 : Y_n = 4'b1111;9'b0xxxxxxxx : Y_n = 4'b0110;9'b10xxxxxxx : Y_n = 4'b0111;9'b110xxxxxx : Y_n = 4'b1000;9'b1110xxxxx : Y_n = 4'b1001;9'b11110xxxx : Y_n = 4'b1010;9'b111110xxx : Y_n = 4'b1011;9'b1111110xx : Y_n = 4'b1100;9'b11111110x : Y_n = 4'b1101;9'b111111110 : Y_n = 4'b1110;default : Y_n = 4'b1111;endcase

end endmodulemodule key_encoder(input [9:0] S_n , output wire[3:0] L ,output wire GS

);wire[3:0] l_temp;

encoder_0 U1(.I_n (S_n[9:1]),.Y_n (l_temp)

);

assign L = ~l_temp;

assign GS = ~(S_n[0] & l_temp[3] & l_temp[2] & l_temp[1] & l_temp[0]); endmodule5.VL15 优先编码器Ⅰ

1.题目:

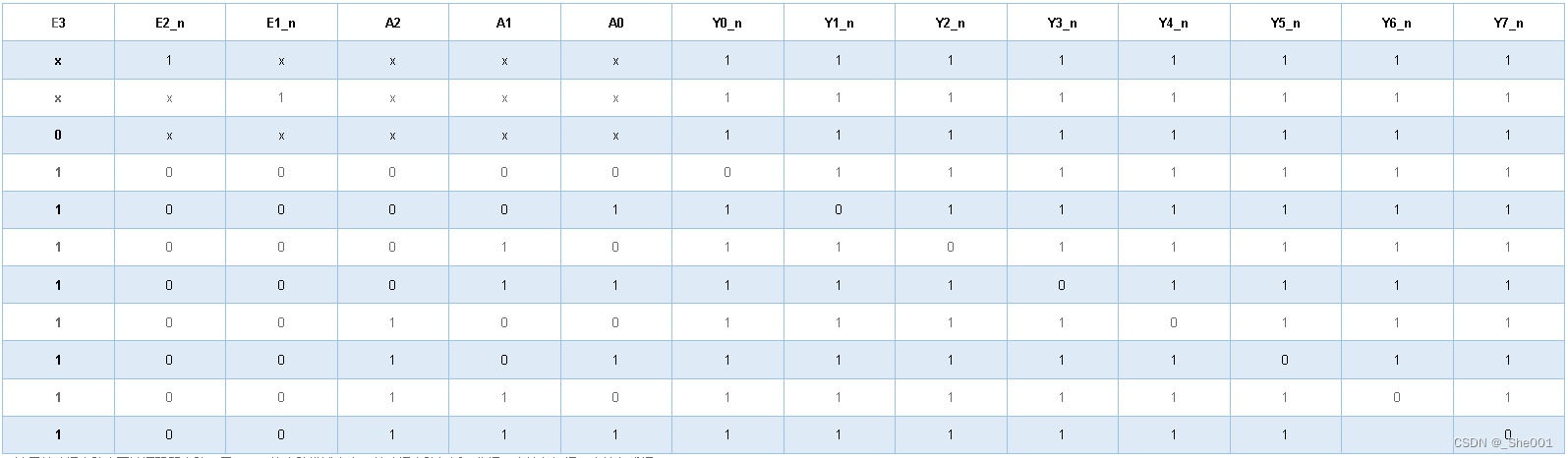

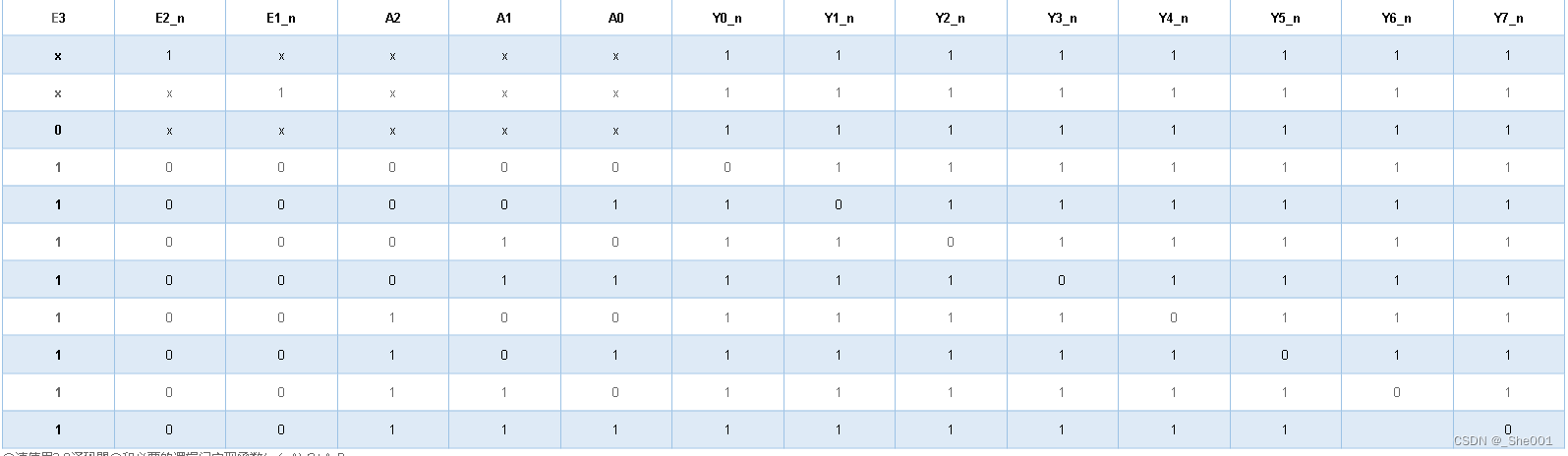

下表是8线-3线优先编码器Ⅰ的功能表。

①请根据该功能表,用Verilog实现该优先编码器Ⅰ。

2.解题代码

`timescale 1ns/1nsmodule encoder_83(input [7:0] I ,input EI ,output wire [2:0] Y ,output wire GS ,output wire EO

);reg [2:0] Y_r;reg GS_r, EO_r;always@(*) begincasez({EI, I})9'b0_????_????: {Y_r, GS_r, EO_r} = 5'b000_0_0;9'b1_0000_0000: {Y_r, GS_r, EO_r} = 5'b000_0_1;9'b1_1???_????: {Y_r, GS_r, EO_r} = 5'b111_1_0;9'b1_01??_????: {Y_r, GS_r, EO_r} = 5'b110_1_0;9'b1_001?_????: {Y_r, GS_r, EO_r} = 5'b101_1_0;9'b1_0001_????: {Y_r, GS_r, EO_r} = 5'b100_1_0;9'b1_0000_1???: {Y_r, GS_r, EO_r} = 5'b011_1_0;9'b1_0000_01??: {Y_r, GS_r, EO_r} = 5'b010_1_0;9'b1_0000_001?: {Y_r, GS_r, EO_r} = 5'b001_1_0;9'b1_0000_0001: {Y_r, GS_r, EO_r} = 5'b000_1_0;default: {Y_r, GS_r, EO_r} = 5'b000_0_0;endcaseendassign Y = Y_r;assign GS = GS_r;assign EO = EO_r;

endmodule

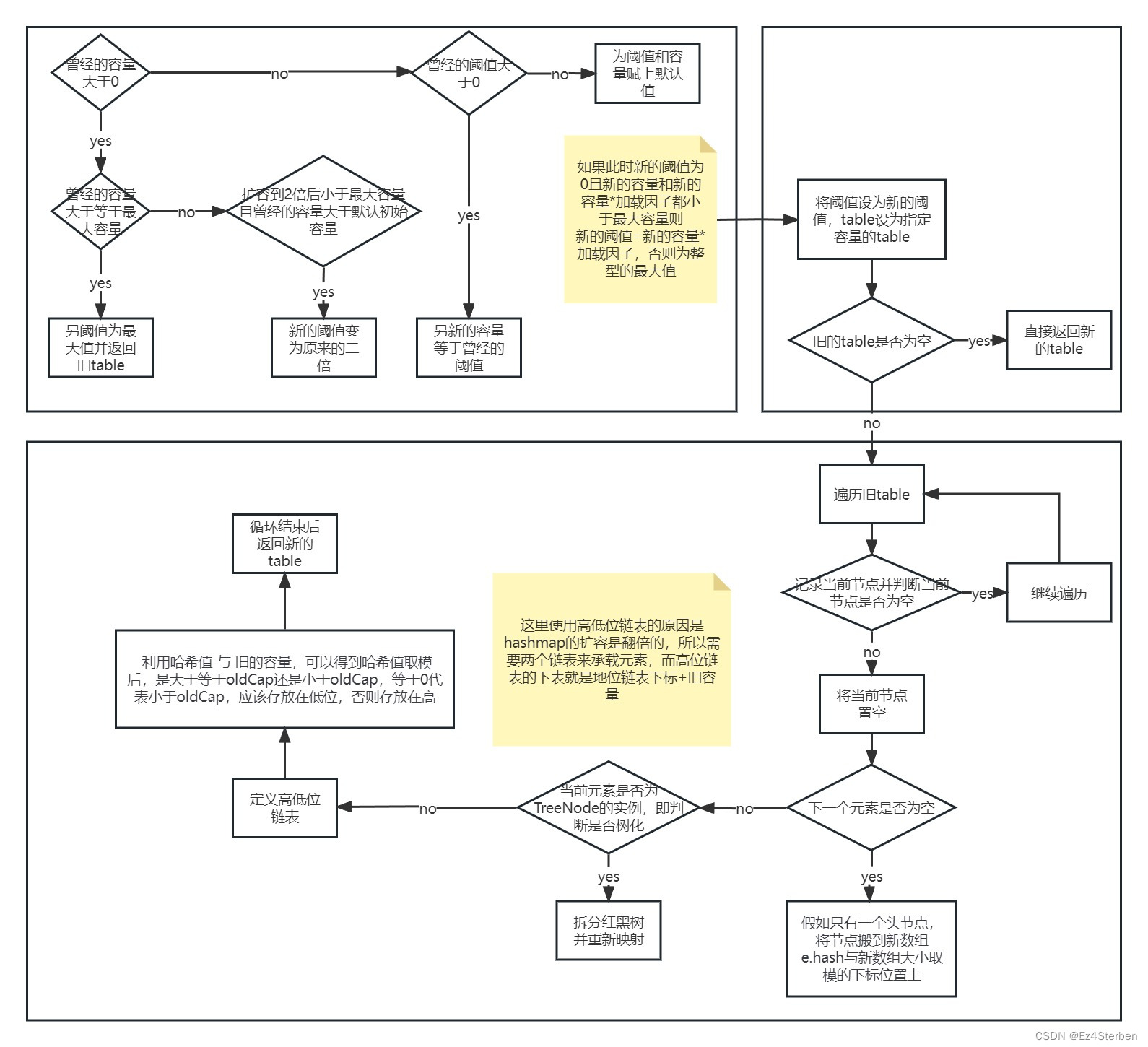

6.VL16 使用8线-3线优先编码器工实现16线-4线优先编码器

1.题目 :

请使用2片该优先编码器Ⅰ及必要的逻辑电路实现16线-4线优先编码器。优先编码器Ⅰ的真值表和代码已给出。

可将优先编码器Ⅰ的代码添加到本题答案中,并例化。

2.解题思路:

2.1首先把16位的数据数据输入分为 2 个8 位的数据输入。当有一个 83线编码器工作时,另外一个不工作。 控制这个的数据位为E1 (高电平启动83编码器 ), 当一个83编码器运行之后的EO 输出为 0 . 所以我们可以使用 E1(使能输入) EO(使能输出)来控制两个编码器的运行。

2.2EI EO 思路举例说明:

EI(最开始的输入) -> 编码器1 -> EO1 -> 编码器2 EI -> EO (最后的EO) 2.3然后是 15 位 到 8位 的83编码器 的输出,可以这样比喻, 当15位 到 8位的 83编码器使用 它的输出的3 位的数据直接 + 2'b1000 就行。 (自己想一想)

编码器1 (15-8位) 输出的3 位数据 B1

16-4 编码器输出 L[3:0];

wire[3:0] B1 ; //assign持续赋值 wire

B1 = 83编码器的输出 + 2'b1000/2'b0000;= 83编码器的输出 + GS1 (是否使用 ,使用 1, 没有使用0)B1[3] = GS1;

L[3] = B1[3] = GS1;

L[3] = GS1;

2.4 最后的16-4 编码器的输出结果是 两个编码器相 或。

3.解题遇到的问题

3.1 问题: main.v:53:error:B1['sd3]在encoder_164中不是有效的l值。 main.v:31::B1['sd3]在这里被声明为wire。 main.v:55:错误:B1['sd3]在encoder_164中不是有效的l值。 main.v:31::B1['sd3]在这里被声明为wire。

错误原因:数据类型定义错误 或者 赋值类型错误

解决方法: 在always 过程块中被赋值的变量必须是 reg (寄存器型),用 assign 连续赋值的对象 必须定义成 wire(线型);

4.解题代码

`timescale 1ns/1ns

module encoder_83(input [7:0] I ,input EI ,output wire [2:0] Y ,output wire GS ,output wire EO

);

assign Y[2] = EI & (I[7] | I[6] | I[5] | I[4]);

assign Y[1] = EI & (I[7] | I[6] | ~I[5]&~I[4]&I[3] | ~I[5]&~I[4]&I[2]);

assign Y[0] = EI & (I[7] | ~I[6]&I[5] | ~I[6]&~I[4]&I[3] | ~I[6]&~I[4]&~I[2]&I[1]);assign EO = EI&~I[7]&~I[6]&~I[5]&~I[4]&~I[3]&~I[2]&~I[1]&~I[0];assign GS = EI&(I[7] | I[6] | I[5] | I[4] | I[3] | I[2] | I[1] | I[0]);

//assign GS = EI&(| I);endmodulemodule encoder_164(input [15:0] A ,input EI ,output wire [3:0] L ,output wire GS ,output wire EO

);wire[2:0] A1;

wire[2:0] B1;

wire Gs1,Gs2;

wire EO1;encoder_83 U1(.EI (EO1),.I (A[7:0]),.Y (A1[2:0]),.GS (Gs1),.EO (EO)

);encoder_83 S2(.EI (EI),.I (A[15:8]),.Y (B1[2:0]),.GS (Gs2),.EO (EO1)

);assign L[3] = Gs2;

assign L[2] = A1[2] | B1[2];

assign L[1] = A1[1] | B1[1];

assign L[0] = A1[0] | B1[0];

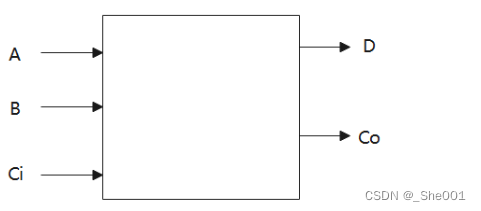

assign GS = Gs1 | Gs2;endmodule7.VL17 用3-8译码器实现全减器

1.题目:

请使用3-8译码器和必要的逻辑门实现全减器,全减器接口图如下,A是被减数,B是减数,Ci是来自低位的借位,D是差,Co是向高位的借位。

3-8译码器代码如下,可将参考代码添加并例化到本题答案中。

module decoder_38(input E ,input A0 ,input A1 ,input A2 ,output reg Y0n , output reg Y1n , output reg Y2n , output reg Y3n , output reg Y4n , output reg Y5n , output reg Y6n , output reg Y7n

);always @(*)beginif(!E)beginY0n = 1'b1;Y1n = 1'b1;Y2n = 1'b1;Y3n = 1'b1;Y4n = 1'b1;Y5n = 1'b1;Y6n = 1'b1;Y7n = 1'b1;end else begincase({A2,A1,A0})3'b000 : beginY0n = 1'b0; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b001 : beginY0n = 1'b1; Y1n = 1'b0; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b010 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b0; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b011 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b0; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b100 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b0; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b101 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b0; Y6n = 1'b1; Y7n = 1'b1;end 3'b110 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b0; Y7n = 1'b1;end 3'b111 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b0;end default: beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;endendcase end

end endmodule2.解题代码

`timescale 1ns/1nsmodule decoder_38(input E ,input A0 ,input A1 ,input A2 ,output reg Y0n , output reg Y1n , output reg Y2n , output reg Y3n , output reg Y4n , output reg Y5n , output reg Y6n , output reg Y7n

);always @(*)beginif(!E)beginY0n = 1'b1;Y1n = 1'b1;Y2n = 1'b1;Y3n = 1'b1;Y4n = 1'b1;Y5n = 1'b1;Y6n = 1'b1;Y7n = 1'b1;end else begincase({A2,A1,A0})3'b000 : begin Y0n = 1'b0; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b001 : beginY0n = 1'b1; Y1n = 1'b0; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b010 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b0; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b011 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b0; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b100 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b0; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;end 3'b101 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b0; Y6n = 1'b1; Y7n = 1'b1;end 3'b110 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b0; Y7n = 1'b1;end 3'b111 : beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b0;end default: beginY0n = 1'b1; Y1n = 1'b1; Y2n = 1'b1; Y3n = 1'b1; Y4n = 1'b1; Y5n = 1'b1; Y6n = 1'b1; Y7n = 1'b1;endendcase end

end endmodulemodule decoder1(input A ,input B ,input Ci ,output wire D ,output wire Co

);wire Y0n,Y1n,Y2n,Y3n,Y4n,Y5n,Y6n,Y7n;decoder_38 decoder_1(.E(1) ,.A0(Ci) ,.A1(A) ,.A2(B) ,.Y0n(Y0n) , .Y1n(Y1n) , .Y2n(Y2n) , .Y3n(Y3n) , .Y4n(Y4n) , .Y5n(Y5n) , .Y6n(Y6n) , .Y7n(Y7n)

);assign D = ~(Y1n&Y2n&Y4n&Y7n);assign Co = ~(Y1n&Y4n&Y5n&Y7n);

endmodule

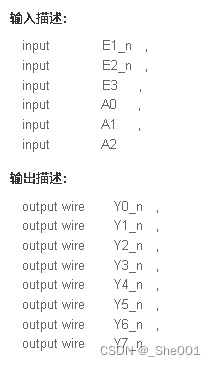

8.VL18 实现3-8译码器①

1.题目:

下表是74HC138译码器的功能表.

请用基础门电路实现该译码器电路,用Verilog将电路描述出来。基础门电路包括:非门、多输入与门、多输入或门。

2.解题代码

`timescale 1ns/1nsmodule decoder_38(input E1_n ,input E2_n ,input E3 ,input A0 ,input A1 ,input A2 ,output wire Y0_n , output wire Y1_n , output wire Y2_n , output wire Y3_n , output wire Y4_n , output wire Y5_n , output wire Y6_n , output wire Y7_n

);wire [7:0] Y;

wire EN;

//首先是公式 就是真值表转 公式 因为 38 译码器的输出 是低电平,没事我们两边加上一个 ~ 就和之前的列出公式差不多了, 只要列出 输出为0 的。

//列出输出的公式

//使用或门 第一个为输出的值 第二第三为 相或的参数

//第一个为使能输出, 标准的正常的使能为 E3=1 ,E2_n =0 , E1_n =0;and(EN,E3 , ~E2_n, ~E1_n);

// 输出 0 的真值表的公式

and(Y[0],EN,~A0,~A1,~A2);

and(Y[1],EN,A0,~A1,~A2);

and (Y[2] , EN , ~A0,A1,~A2);

and (Y[3] , EN , A0,A1,~A2);

and (Y[4] , EN , ~A0,~A1,A2);

and (Y[5] , EN , A0,~A1,A2);

and (Y[6] , EN , ~A0,A1,A2);

and (Y[7] , EN , A0,A1,A2);//非门 ,因为两边加了一个非门

not (Y0_n , Y[0]);

not (Y1_n , Y[1]);

not (Y2_n , Y[2]);

not (Y3_n , Y[3]);

not (Y4_n , Y[4]);

not (Y5_n , Y[5]);

not (Y6_n , Y[6]);

not (Y7_n , Y[7]);endmodule9.VL19 使用3-8译码器①实现逻辑函数

1.题目:

下表是74HC138译码器的功能表

②请使用3-8译码器①和必要的逻辑门实现函数L=(~A)·C+A·B

可在本题答案中添加并例化3-8译码器①代码,3-8译码器①代码如下:

module decoder_38(input E1_n ,input E2_n ,input E3 ,input A0 ,input A1 ,input A2 ,output wire Y0_n , output wire Y1_n , output wire Y2_n , output wire Y3_n , output wire Y4_n , output wire Y5_n , output wire Y6_n , output wire Y7_n

);

wire E ;

assign E = E3 & ~E2_n & ~E1_n;

assign Y0_n = ~(E & ~A2 & ~A1 & ~A0);

assign Y1_n = ~(E & ~A2 & ~A1 & A0);

assign Y2_n = ~(E & ~A2 & A1 & ~A0);

assign Y3_n = ~(E & ~A2 & A1 & A0);

assign Y4_n = ~(E & A2 & ~A1 & ~A0);

assign Y5_n = ~(E & A2 & ~A1 & A0);

assign Y6_n = ~(E & A2 & A1 & ~A0);

assign Y7_n = ~(E & A2 & A1 & A0);endmodule

2.解题代码

`timescale 1ns/1nsmodule decoder_38(input E1_n ,input E2_n ,input E3 ,input A0 ,input A1 ,input A2 ,output wire Y0_n , output wire Y1_n , output wire Y2_n , output wire Y3_n , output wire Y4_n , output wire Y5_n , output wire Y6_n , output wire Y7_n

);

wire E ;

assign E = E3 & ~E2_n & ~E1_n;

assign Y0_n = ~(E & ~A2 & ~A1 & ~A0);

assign Y1_n = ~(E & ~A2 & ~A1 & A0);

assign Y2_n = ~(E & ~A2 & A1 & ~A0);

assign Y3_n = ~(E & ~A2 & A1 & A0);

assign Y4_n = ~(E & A2 & ~A1 & ~A0);

assign Y5_n = ~(E & A2 & ~A1 & A0);

assign Y6_n = ~(E & A2 & A1 & ~A0);

assign Y7_n = ~(E & A2 & A1 & A0);endmodulemodule decoder0(input A ,input B ,input C ,output wire L

);wire Y0_n ;

wire Y1_n ;

wire Y2_n ;

wire Y3_n ;

wire Y4_n ;

wire Y5_n ;

wire Y6_n ;

wire Y7_n ;decoder_38 U0(.E1_n (1'b0),.E2_n (1'b0),.E3 (1'b1),.A0 (C),.A1 (B),.A2 (A),.Y0_n (Y0_n), .Y1_n (Y1_n), .Y2_n (Y2_n), .Y3_n (Y3_n), .Y4_n (Y4_n), .Y5_n (Y5_n), .Y6_n (Y6_n), .Y7_n (Y7_n)

);assign L = ~(Y1_n & Y3_n & Y6_n & Y7_n);endmodule10.VL20 数据选择器实现逻辑电路

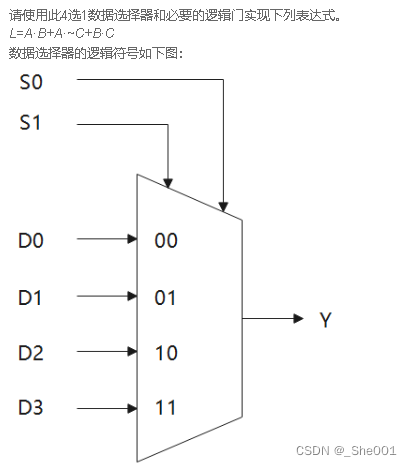

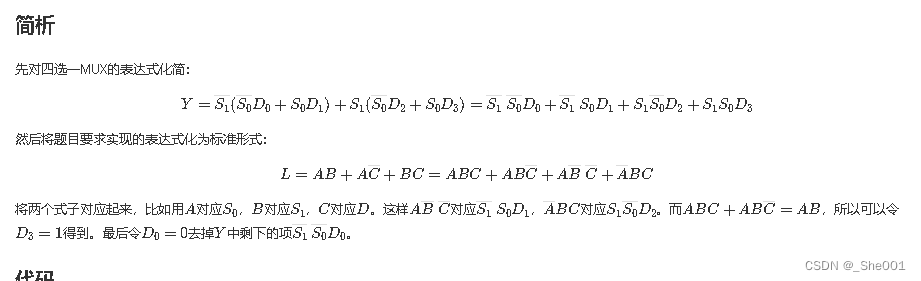

1.题目:

数据选择器代码如下,可在本题答案中添加并例化此数据选择器。

module data_sel(input S0 ,input S1 ,input D0 ,input D1 ,input D2 ,input D3 ,output wire Y

);assign Y = ~S1 & (~S0&D0 | S0&D1) | S1&(~S0&D2 | S0&D3);endmodule

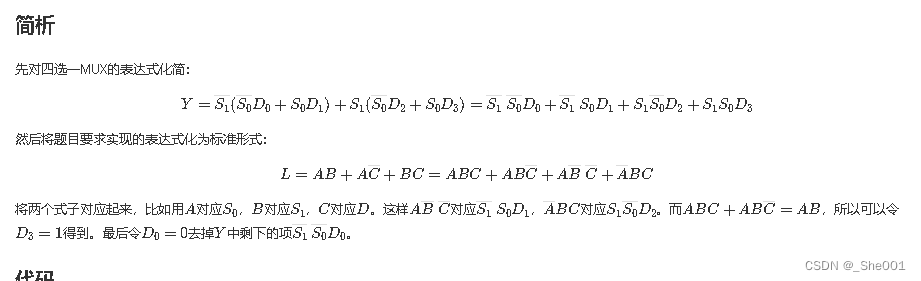

2.解题思路:

D1 = ~D2

D1 = C

D2 = ~C

3.解题代码

`timescale 1ns/1nsmodule data_sel(input S0 ,input S1 ,input D0 ,input D1 ,input D2 ,input D3 ,output wire Y

);assign Y = ~S1 & (~S0&D0 | S0&D1) | S1&(~S0&D2 | S0&D3);endmodulemodule sel_exp(input A ,input B ,input C ,output wire L

);data_sel c1(.S0(A),.S1(B),.D0(0),.D1(~C),.D2(C),.D3(1),.Y(L) );endmodule相关文章:

硬件语言Verilog HDL牛客刷题day02 组合逻辑部分

1.VL11 4位数值比较器电路 1.题目: 某4位数值比较器的功能表如下。请用Verilog语言采用门级描述方式,实现此4位数值比较器。 2.解题代码: timescale 1ns/1nsmodule comparator_4(input [3:0] A ,input [3:0] B ,output …...

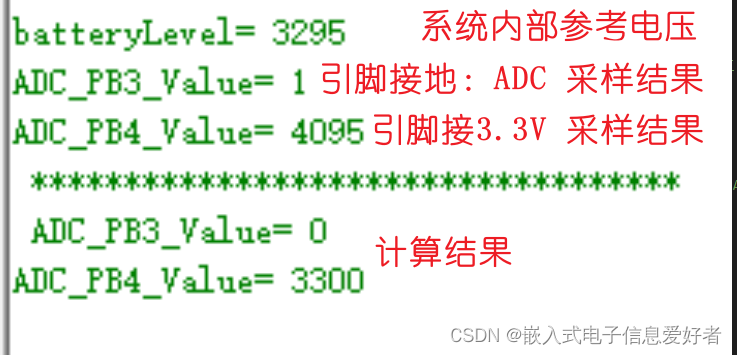

【LM401】ADC采集代码解读

本文主要实现基于LM401模组,,测试ADC低功耗采集,详细解析代码基于计算方式 对于小白理解ADC有更详细的理解 【LM401】ADC采集代码解读1. 单片机ADC与DAC简单理解2. 模组ADC通道介绍3. ADC初始化4. 采集值的计算5.测试结果硬件基于易智联的LM401的LoRa模组…...

CSDN 编程竞赛四十期题解

竞赛总览 CSDN 编程竞赛四十期:比赛详情 (csdn.net) 竞赛题解 题目1、小鱼的航程 有一只小鱼,它上午游泳150公里,下午游泳100公里,晚上和周末都休息(实行双休日)。假设从周x(1<x<7)开…...

【TypeScript学习之路】泛型

【TypeScript学习之路】泛型 文章目录【TypeScript学习之路】泛型写在前面前言一、认识泛型1.1 什么是泛型1.2 泛型函数的使用二、泛型接口与泛型类2.1 泛型接口2.2 泛型类三、泛型约束写在前面 🤗这里是前端程序员小张! 🌻人海茫茫ÿ…...

数据分析学习项目:东京奥运会跳水评论分析

“中国跳水梦之队” ————有关东京奥运会跳水评论分析 导语 第32届夏季奥林匹克运动会于2021年07月23日-2021年08月08日在日本东京举办。 四年一届的奥运会可以说是世界瞩目的盛会,奥运健儿们在赛场上的精神风貌不只是代表了他们自身的运动精神,更昭…...

、OrderBy(排序并自定义排序规则))

Winform/Csharp中使用Linq的Where条件筛选、Select字段映射(左外连接并设置无匹配时默认值)、OrderBy(排序并自定义排序规则)

场景 Java8新特性-Stream对集合进行操作的常用API: Java8新特性-Stream对集合进行操作的常用API_streamapi操作集合_霸道流氓气质的博客-CSDN博客 上面讲的是在Java中使用Stream中对集合的常用操作。 在C#中Linq是有对应的类似的api。 完整和详细的用法可自行查…...

Linux-常用的Shell命令

文章目录前言常用的Shell命令文件和目录管理查看文件、目录信息查看文件内容查看文件类型查找文件查找内容查看目录大小创建文件删除文件拷贝文件移动文件创建目录删除目录拷贝目录压缩文件解压文件路径相关操作目录切换显示当前路径用户、用户组管理创建用户删除用户创建用户组…...

Go语言基础:数组定义及循环遍历

前言 大家好,我是沐风晓月,本文go语言入门-掌握go语言函数收录于《go语言学习专栏》专栏,此专栏带你从零开始学习go语言,持续更新中,欢迎点赞收藏。 🏠个人主页:我是沐风晓月 🧑个人…...

【树与二叉树】二叉树顺序结构实现以及堆的概念及结构--详解介绍

📝个人主页:Sherry的成长之路 🏠学习社区:Sherry的成长之路(个人社区) 📖专栏链接:数据结构 🎯长路漫漫浩浩,万事皆有期待 文章目录1. 二叉树顺序结构2.…...

天狗实战(二)SpringBoot API开发详解 --SpringMVC注解+封装结果+支持跨域+打包(下)

本文目录 前言专栏介绍一、创建SpringBoot项目1.1 添加springboot依赖1.2 创建启动类1.3 创建控制器类1.4 Run 或 Debug二、开发图书管理API2.1 web层BookAdminControllerBookVO2.2 service层BookServiceBookServiceImplBookBO2.3 dal层...

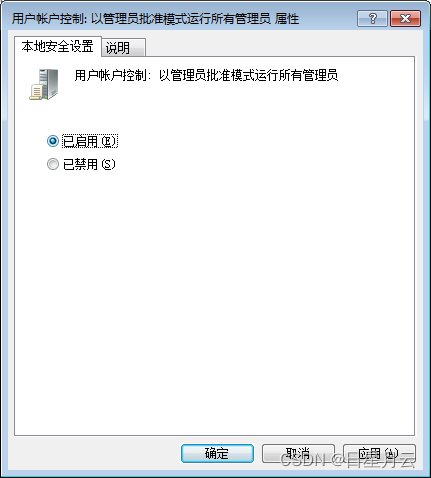

实验一 Windows系统安全实验【网络安全】

实验一 Windows系统安全实验【网络安全】前言推荐实验一 Windows系统安全实验3.1 帐户和口令的安全设置3.1.1 实验目的3.1.2 实验环境3.1.3 实验内容和步骤1. 删除不再使用的帐户并禁用guest帐户2.启用密码策略和帐户锁定策略3.查看“用户权限分配”4.查看“用户组权限分配”5.…...

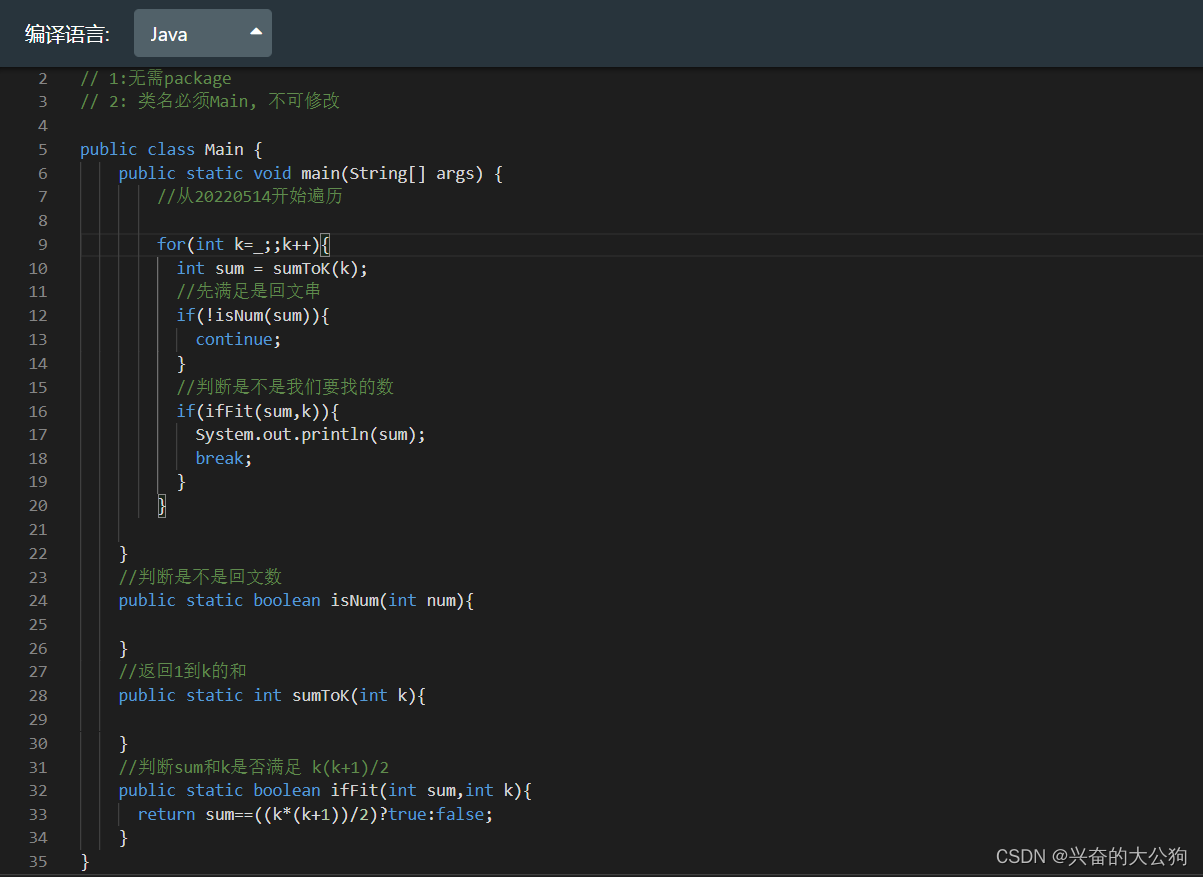

蓝桥杯正确的解题姿势

在做算法题的过程中最忌讳的就是上来就一顿乱敲,一开始我就是这样,但随着不断的刷题和老师的指导,总结了自己的刷题方法 示例题目 三角回文数 问题描述 对于正整数 n, 如果存在正整数 k使得 n123...kk(k1)/2 , 则 n 称为三角数。例如, 66066 …...

【mysql】性能优化

目录一、硬件与操作系统二、架构设计层面的优化三、mysql程序配置优化四、mysql执行优化一、硬件与操作系统 1.使用高性能cpu,提高计算能力 2.增大可用内存,提高读取能力 3.提高硬盘的读写速度,使用专用的固态硬盘 4.增大网络带宽,…...

Jupyter安装与远程使用过程记录

Jupyter安装与远程使用过程记录 文章目录Jupyter安装与远程使用过程记录Jupyter在线试用在服务器上安装Jupyter Notebook配置服务器远程连接首先保证ip地址连通性其次开启服务器访问端口然后在服务器启动服务最后测试连通性后续使用教程Jupyter在线试用 官网适用,感…...

Swift入门

基本数据类型 Int、UInt:整数型、非负整数Float、Double:单精度浮点数、双精度浮点数Bool:布偶值String、Character:字符串、字符 其他类型 Array, Dictionary:数组、字典StructClassvar:变量let&#x…...

【HashMap】jdk1.8中HashMap的插入扩容源码学习分析

jdk1.8中HashMap的插入扩容源码学习分析 一、成员变量 首先介绍HashMap中各个成员变量的作用,在HashMap中有以下成员变量 size记录了HashMap中键值对的个数 loadFactor(加载因子)用来决定size达到容量的百分之多少时触发扩容机制 默认是0…...

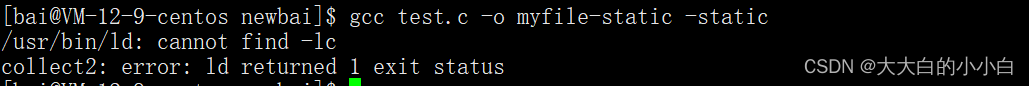

Linux编译器-gcc/g++ 使用

在介绍gcc/g的使用前我们先了解一下两者的不同 gcc时主要编译c语言,而g主要编译c的,但是两者的选项是相同的,因此我们以gcc和c语言为例来讲解。背景知识 gcc和g都是编译器其核心作用将文本类文件翻译成二进制可执行 那么其过程是怎样的&…...

网络安全专家最爱用的9大工具

网络安全专家,不是你认为的那种搞破坏的 “黑客”。网络安全专家,即 “ethical hackers”,是一群专门模拟网络安全专家攻击,帮助客户了解自己网络的弱点,并为客户提出改进建议的网络安全专家。 网络安全专家在工作中&a…...

Linux内核设计与实现第四章学习笔记

文章目录Linux内核设计与实现第四章学习笔记具体场景Linux调度算法传统的调度公平调度调度的实现时间记账调度器实体虚拟实时进程选择调度器入口睡眠和唤醒抢占和上下文切换用户抢占内核抢占实时调度策略Linux内核设计与实现第四章学习笔记 进程优先级:Linux中采用…...

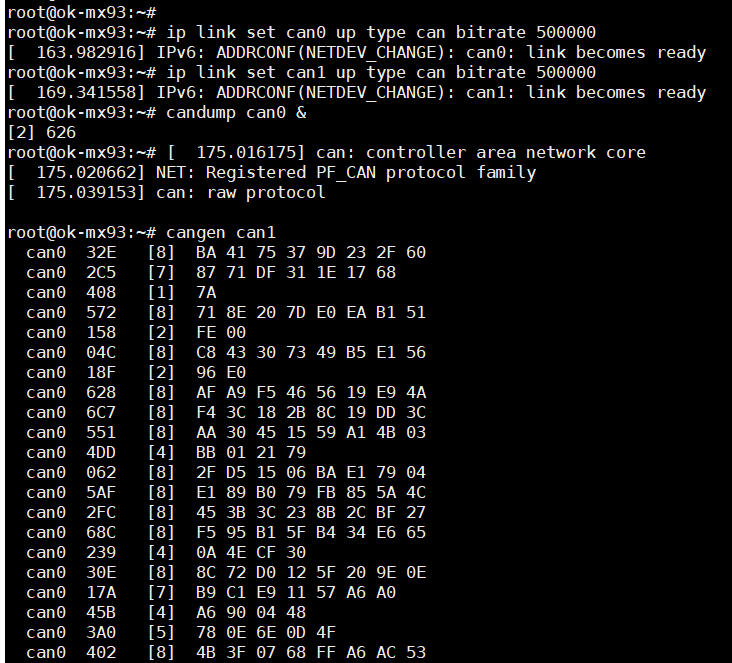

i.MX9352——介绍一款多核异构开发板

本篇来介绍一款多核异构的Linux开发板——OK-MX9352-C开发板。 1 开发板硬件介绍 OK-MX9352-C开发板由核心板和底板组成,核心板采用处理器芯片为NXP的i.MX9352,这是一款多核异构的芯片,核心板基础配置如下 CPU:2Cortex-A551.5G…...

抖音增长新引擎:品融电商,一站式全案代运营领跑者

抖音增长新引擎:品融电商,一站式全案代运营领跑者 在抖音这个日活超7亿的流量汪洋中,品牌如何破浪前行?自建团队成本高、效果难控;碎片化运营又难成合力——这正是许多企业面临的增长困局。品融电商以「抖音全案代运营…...

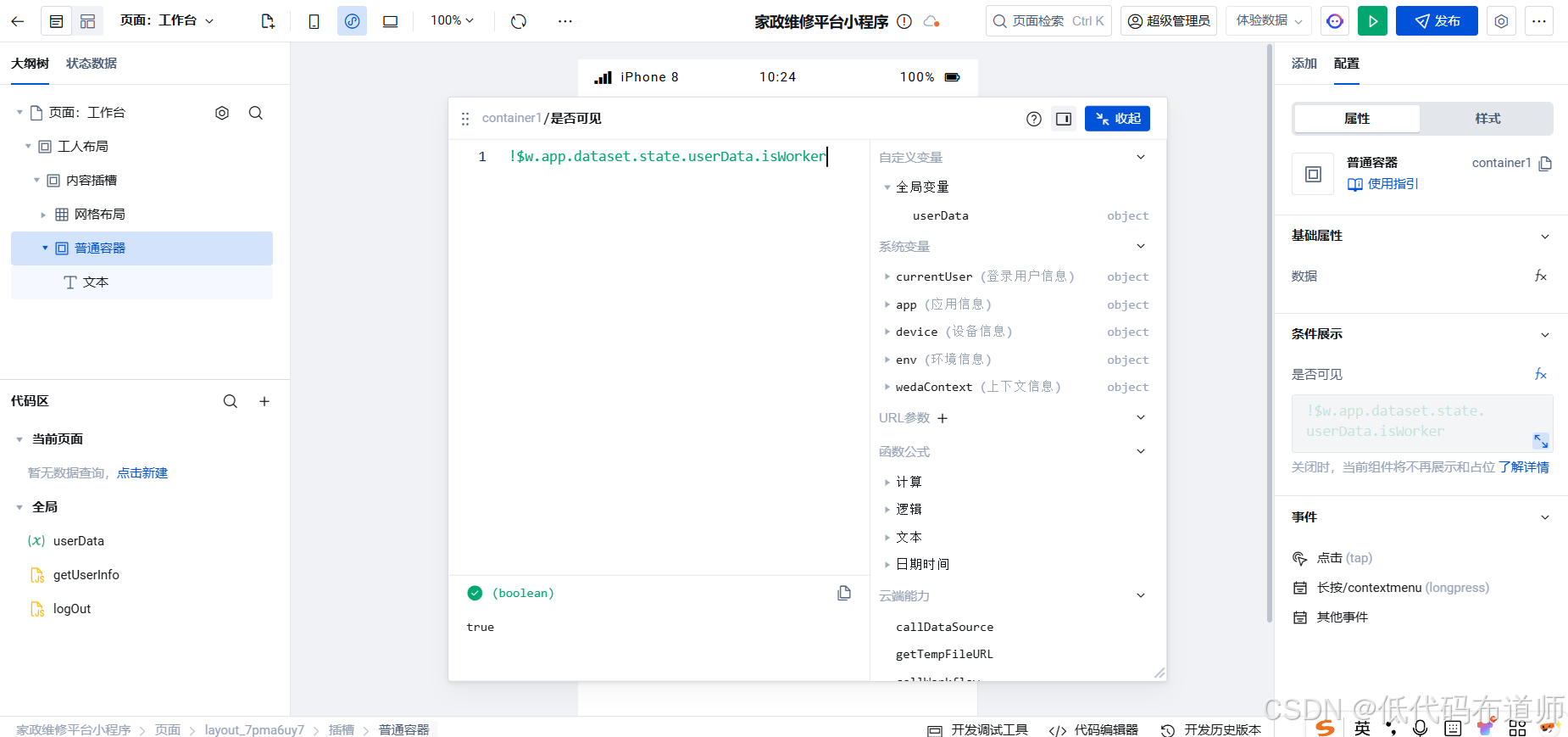

家政维修平台实战20:权限设计

目录 1 获取工人信息2 搭建工人入口3 权限判断总结 目前我们已经搭建好了基础的用户体系,主要是分成几个表,用户表我们是记录用户的基础信息,包括手机、昵称、头像。而工人和员工各有各的表。那么就有一个问题,不同的角色…...

高防服务器能够抵御哪些网络攻击呢?

高防服务器作为一种有着高度防御能力的服务器,可以帮助网站应对分布式拒绝服务攻击,有效识别和清理一些恶意的网络流量,为用户提供安全且稳定的网络环境,那么,高防服务器一般都可以抵御哪些网络攻击呢?下面…...

2023赣州旅游投资集团

单选题 1.“不登高山,不知天之高也;不临深溪,不知地之厚也。”这句话说明_____。 A、人的意识具有创造性 B、人的认识是独立于实践之外的 C、实践在认识过程中具有决定作用 D、人的一切知识都是从直接经验中获得的 参考答案: C 本题解…...

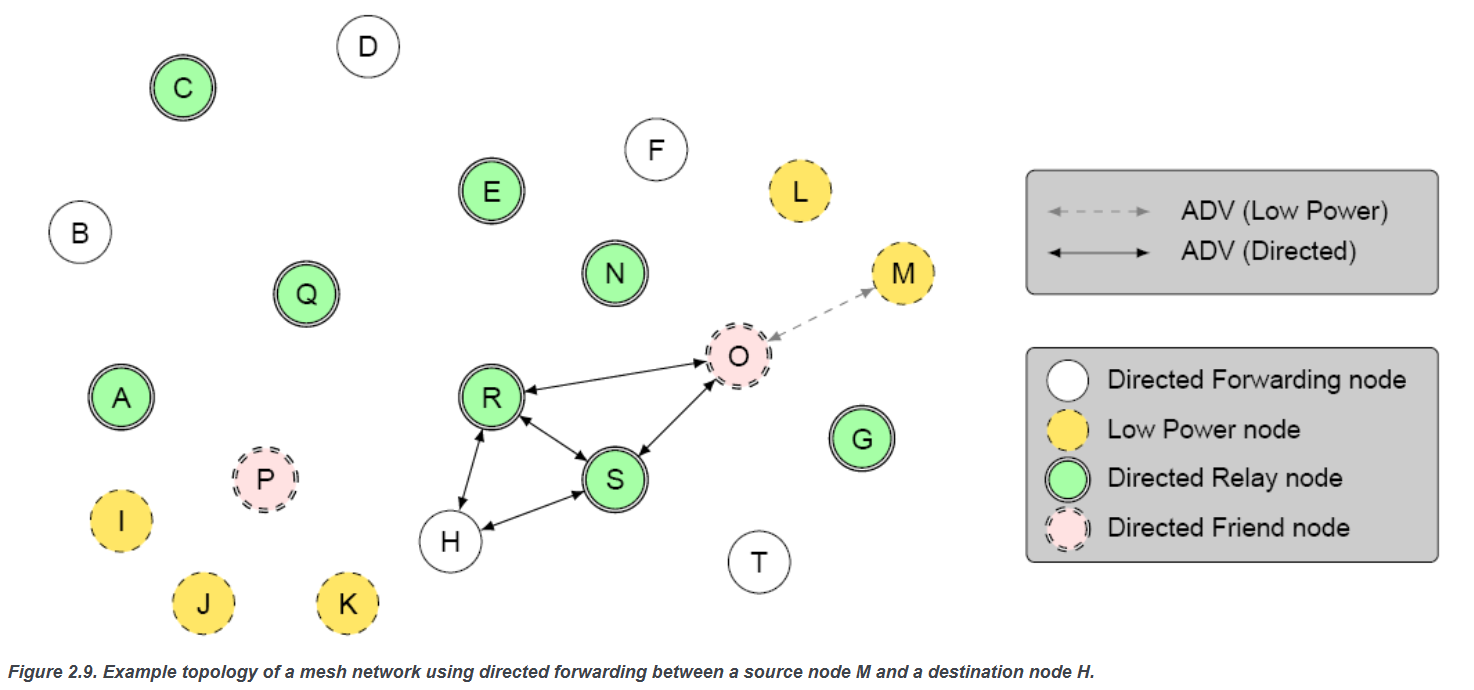

【p2p、分布式,区块链笔记 MESH】Bluetooth蓝牙通信 BLE Mesh协议的拓扑结构 定向转发机制

目录 节点的功能承载层(GATT/Adv)局限性: 拓扑关系定向转发机制定向转发意义 CG 节点的功能 节点的功能由节点支持的特性和功能决定。所有节点都能够发送和接收网格消息。节点还可以选择支持一个或多个附加功能,如 Configuration …...

HybridVLA——让单一LLM同时具备扩散和自回归动作预测能力:训练时既扩散也回归,但推理时则扩散

前言 如上一篇文章《dexcap升级版之DexWild》中的前言部分所说,在叠衣服的过程中,我会带着团队对比各种模型、方法、策略,毕竟针对各个场景始终寻找更优的解决方案,是我个人和我司「七月在线」的职责之一 且个人认为,…...

全面解析数据库:从基础概念到前沿应用

在数字化时代,数据已成为企业和社会发展的核心资产,而数据库作为存储、管理和处理数据的关键工具,在各个领域发挥着举足轻重的作用。从电商平台的商品信息管理,到社交网络的用户数据存储,再到金融行业的交易记录处理&a…...

【深尚想】TPS54618CQRTERQ1汽车级同步降压转换器电源芯片全面解析

1. 元器件定义与技术特点 TPS54618CQRTERQ1 是德州仪器(TI)推出的一款 汽车级同步降压转换器(DC-DC开关稳压器),属于高性能电源管理芯片。核心特性包括: 输入电压范围:2.95V–6V,输…...

Python的__call__ 方法

在 Python 中,__call__ 是一个特殊的魔术方法(magic method),它允许一个类的实例像函数一样被调用。当你在一个对象后面加上 () 并执行时(例如 obj()),Python 会自动调用该对象的 __call__ 方法…...

用js实现常见排序算法

以下是几种常见排序算法的 JS实现,包括选择排序、冒泡排序、插入排序、快速排序和归并排序,以及每种算法的特点和复杂度分析 1. 选择排序(Selection Sort) 核心思想:每次从未排序部分选择最小元素,与未排…...