verilog编程规范

verilog编程规范

文章目录

- verilog编程规范

- 前言

- 一、代码划分

- 二、verilog编码

- A

- B

- C

- D

- E

- F

- G

前言

高内聚,低耦合,干净清爽的代码

一、代码划分

高内聚:

- 一个功能一个模块

- 干净的接口

- 提取公共的代码

低耦合:

- 模块之间低耦合尽量用少量的线连接

模块划分:关键路径逻辑和非关键路径逻辑放在不同的模块。方便对关键路径做速度优化,非关键路径做面积优化

二、verilog编码

A

- 设计文档和应用文档

- 一个模块一个文件,并命名相同

- 顶层模块只包模块之间的连线

B

- 避免门级电路,变得不可移植

- 避免三态门,而使用多路选择电路

- 避免latch

C

- 保证时钟和复位不出现gilch(竞争冒险产生的毛刺)。尽量使用同步复位

- 单个模块的reg使用同步复位

- 小心使用门控时钟(一般在低功耗设计中是用),门控时钟容易产生毛刺。如果要使用门控,尽量借助综合工具自动插入门控时钟。如果是手动,门控信号要从reg中给出,避免glitch

- 避免使用模块内部产生的使用,用PLL或者mmCM

- 一个模块中只使用一个时钟

- 避免多周期路径和假路径(多周期路径就是一个寄存器输出到另一个寄存器输入的路径不能再一个时钟周期完成)

- 要写可测试性设计(DFT):写功能时,就要考虑ATPG和BIST,要添加各种测试逻辑和bypass逻辑

- 一个模块中只用一个时钟沿。如果需要两个,则分开模块或者,将该时钟进行取反后输入(取反后的使用IBUFG)

- 跨时钟处理:要同步的信号从reg中出来。要同步的信号至少锁存两个clk。对cnt同步要用格雷码

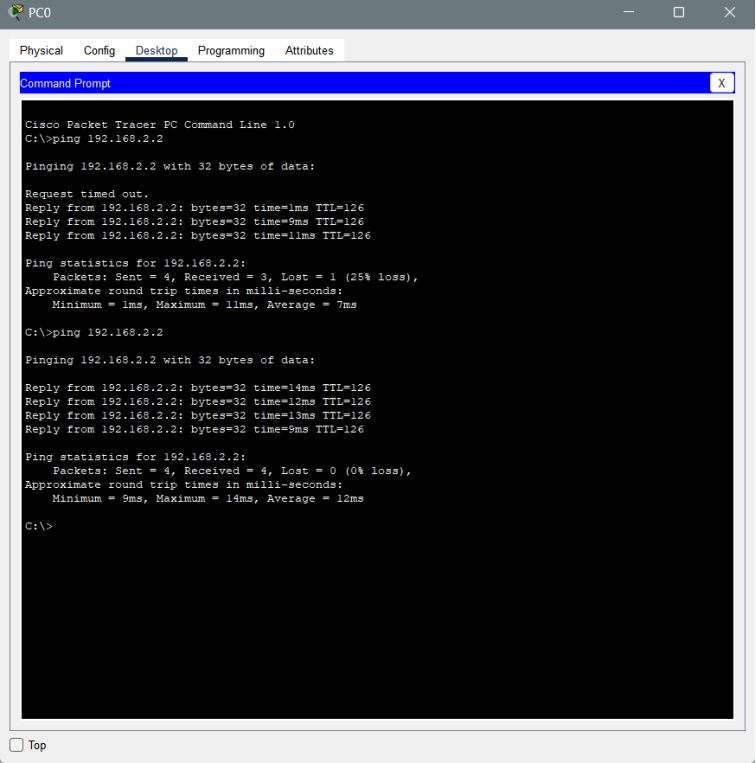

关于跨时钟处理,有以下代码可以比较:

100MHz时钟域下有一个单周期的脉冲,如何将其转换到80MHz时钟域下的单周期脉冲。

使用电平同步,将100MHZ的信号扩展,然后使用边沿检测。但是下面代码存在问题。

module test( input

i_clk1, //100MHz

input i_clk2, //80MHz

input i_pulse,

output o_new_pulse);

reg r1_pulse;

reg r2_pulse;

wire w_pulse;

always @(posedge i_clk1) //100Mbegin r1_pulse <= i_pulse ; r2_pulse <= r1_pulse;

end

assign w_pulse = r1_pulse | r2_pulse;

reg r1_new_pulse;

reg r2_new_pulse;

reg r3_new_pulse;

wire w_new_pulse;

always @(posedge i_clk2) //80Mbegin

r1_new_pulse <= w_pulse;

r2_new_pulse <= r1_new_pulse;

r3_new_pulse <= r2_new_pulse;

end

assign o_new_pulse = ~r3_new_pulse & r2_new_pulse;

endmodule

问题代码在这里:assign w_pulse = r1_pulse | r2_pulse;

两个寄存器之间是有延迟的,通过把脉冲变成电平信号,如果出现上图的情况,会导致电平信号又断点。在80MHZ的时钟周期的采样,可能或漏。处理方式如下面说的“要同步的信号从reg中出来”。即先在当前时钟域下先展宽之后,在从reg中输出出来给别人用,这样就避免使用组合逻辑了。

因此代码修改如下

always @(posedge i_clk1) //100Mbegin r1_pulse <= i_pulse ; r2_pulse <= r1_pulse; w_pulse <= r1_pulse | r2_pulse;end

reg r1_new_pulse;

reg r2_new_pulse;

reg r3_new_pulse;

wire w_new_pulse;

always @(posedge i_clk2) //80Mbegin

r1_new_pulse <= w_pulse;

r2_new_pulse <= r1_new_pulse;

r3_new_pulse <= r2_new_pulse;end

小结:

会议竞争和冒险的原理,可以发现,assign B = a & b; 这如果a和b因为布线延迟的原因,那么该组合逻辑就可能产生毛刺。在写组合逻辑的时候,也尽量去考虑布线的延迟问题,是否产生的毛刺会给设计带来影响。

参阅文章 竞争和冒险

D

- 用always@(*)

- 注意阻塞赋值和非阻塞赋值的场合:1.不要混用。2.组合逻辑always@()用=;锁存逻辑always@()用<=.3.时钟逻辑用<=

- 使用三段式状态机,且组合逻辑的转态跳转要用default

- case比if的时序好,case无优先级。if有优先级。

- if语句书写:嵌套要用begin

if(a == 1) beginif(c == 1)...else...end

else...

E

- 模块的输入先reg再使用。模块的输出先reg再输出。使得输入的时序,输出强度和延迟好预测。这样可以获得更好的时序

如代码:

module ins(input i_clk,input i_rst,input i_data,output o_vld

);

reg ri_data;

reg ro_vld;assign o_vld = ro_vld;always@(posedge i_clk)ri_data <= i_data;always@(posedge i_clk)ro_vld<= 1'b1;

endmodule

- 不要驱动input

- 保证所有output被驱动,如果没有使用则用assign 输出为0或者1

- 要声明所有信号,反之会被综合为1bit

- reg只能在一个always中赋值

- 在写验证代码时,不要用内部信号,用点操作符有时候会有问题,因为内部信号在综合为网表之后就不见了,在使用ila抓数时,使用点操作符去索引内部信号,可能会报错(综合时被优化掉了名字)。

- 设计代码时,不要使用force release initial forever === !===等

F

- 不要在include中写目录名字,写工层的相对路径,否则移植很麻烦

- 使用vh头文件

G

使用简洁的代码书写

c[3:0] = b[3:0] & d[3:0];

改写为

c=b&d;

// 没必要不用begin end

always@(posedge i_cllk)if(a == 1'b1) ro_data <= 1'b1;else ro_data <= 1'b0;- 模块端口按照功能划分

- 如果用 i_

- 输出用 o_

- inout用io_

- wire用w_

- reg用r_

- 打拍用r_data_d1

- 关于注释:注释的核心就是把代码删除了,看注释还能明白其功能。1.模块开头的注释,实现功能和关键特性。2.代码中的注释简明扼要。3.删除陈旧的代码和注释

- 使用参数化parameter

相关文章:

verilog编程规范

verilog编程规范 文章目录 verilog编程规范前言一、代码划分二、verilog编码ABCDEFG 前言 高内聚,低耦合,干净清爽的代码 一、代码划分 高内聚: 一个功能一个模块干净的接口提取公共的代码 低耦合: 模块之间低耦合尽量用少量…...

飞飞5.4游戏源码(客户端+服务端+工具完整源代码+5.3fix+5.4patch+数据库可编译进游戏)

飞飞5.4游戏源码(客户端服务端工具完整源代码5.3fix5.4patch数据库可编译进游戏) 下载地址: 通过网盘分享的文件:【源码】飞飞5.4游戏源码(客户端服务端工具完整源代码5.3fix5.4patch数据库可编译进游戏) 链…...

【MySQL】——用一文领悟表的增删查改

目录 前言 🍃1.表的增加 🍙1.1增——insert 🍙1.2插入否则更新 🍤1.2.1影响行说明 🍂2.表的查询 🍘2.1查询——select 🍘2.2特殊表查询 🍥2.2.1添加表达式 🍥…...

Zabbix监控Oracle 19c数据库完整配置指南

Zabbix监控Oracle 19c数据库完整配置指南 本文将详细介绍如何使用Zabbix配置Oracle 19c数据库监控,包括安装、配置、问题排查等全过程。本指南适合新手独立完成配置。 1. 环境准备 1.1 系统要求 Oracle 19c数据库服务器Zabbix服务器(版本5.0或更高&a…...

静态路由与交换机配置实验

1.建立网络拓扑 添加2台计算机,标签名为PC0、PC1;添加2台二层交换机2960,标签名为S0、S1;添加2台路由器2811,标签名为R0、R1;交换机划分的VLAN及端口根据如下拓扑图,使用直通线、DCE串口线连接…...

【jvm】讲讲jvm中的gc

目录 1. 说明2. 主要算法2.1 标记-清除算法2.2 复制算法2.3 标记-整理算法3. 主要回收器3.1 Serial GC3.2 Parallel GC3.3 CMS(Concurrent Mark-Sweep)GC3.4 G1(Garbage-First)GC 4. 触发条件4.1 Minor GC(Young GC&am…...

openlayers地图事件

OpenLayers是一个开源的JavaScript库,用于在Web上创建交互式地图。它提供了许多地图事件,使用户可以与地图进行交互。以下是OpenLayers常用的地图事件: 1. click:当用户单击地图时触发该事件。 2. dblclick:当用户双…...

杂记9---一些场景git操作汇总

背景:不同项目需求,所需要git操作集合,不太一样,这里汇总记录一下。 场景1:给本地项目添加到远程仓库的新建分支上 把本地节点保存在自己库的一个分支: git init git remote add origin xxx.git 远程仓库…...

Mysql索引,聚簇索引,非聚簇索引,回表查询

什么是索引 数据库索引是为了实现高效数据查询的一种有序的数据数据结构,类似于书的目录,通过目录可以快速的定位到想要的数据,因为一张表中的数据会有很多,如果直接去表中检索数据效率会很低,所以需要为表中的数据建立…...

【优选算法 二分查找】二分查找算法入门详解:二分查找小专题

x 的平方根 题目解析 算法原理 解法一: 暴力解法 如果要求一个数(x)的平方根,可以从 0 往后枚举,直到有一个数(a),a^2<x,(a1)^2>x,a即为所求; 解法二:二分查找 …...

如何将CSDN博客下载为PDF文件

1.打开CSDN文章内容 2.按键盘上的f12键(或者右键—审查元素)进入浏览器调试模式,点击控制台(Console)进入控制台 3.在控制台输入以下代码,回车 4.在弹出的打印页面中将布局设置成横向,纵向会…...

pdf转word/markdown等格式——MinerU的部署:2024最新的智能数据提取工具

一、简介 MinerU是开源、高质量的数据提取工具,支持多源数据、深度挖掘、自定义规则、快速提取等。含数据采集、处理、存储模块及用户界面,适用于学术、商业、金融、法律等多领域,提高数据获取效率。一站式、开源、高质量的数据提取工具&…...

2024年下半年网络工程师案例分析真题及答案解析

2024年下半年网络工程师案例分析真题及答案解析 试题一(15分) [说明] 公司为某科技园区的不同企业提供网络服务,不同企业的业务有所不同,每个企业因业务需要在不同的地点有多个分支机构。其拓扑结构如图1所示。企业用户通过楼层接入交换机、楼栋汇聚交换机和区域交换机接…...

English phonetic symbol

英语音标发音表-英语48个音标在线读 (jiwake.com) 【英语音标教程】从此学会国际音标|英式音标|BBC音标教程全解_哔哩哔哩_bilibili 元音 单元音 /iː/,/ɪ/ 这两个音不是发音长短的区别, /uː/ /ʊ/ 上面那个就正常读,下面那个她的气大概是往你斜…...

普及组集训--图论最短路径设分层图

P4568 [JLOI2011] 飞行路线 - 洛谷 | 计算机科学教育新生态 可以设置分层图:(伪代码) E(u,v)w;无向图 add(u,v,w),add(v,u,w); for(j1~k){add(ujn,vjn,w);add(vjn,ujn,w);add(ujn-j,vjn-j,0);add(vjn-j,ujn-j,0); } add(ujn-j,vjn-j,0); add(vjn-j,uj…...

SYN6288语音合成模块使用说明(MicroPython、STM32、Arduino)

模块介绍 SYN6288中文语音合成模块是北京宇音天下科技有限公司推出的语音合成模块。该模块通过串口接收主控传来的语音编码后,可自动进行自然流畅的中文语音播报。 注:SYN6288模块无法播报英文单词和句子,只能按字母播报英文 ;而…...

Spring完整知识三(完结)

Spring集成MyBatis 注意 Spring注解形式集成MyBatis时,若SQL语句比较复杂则仍采用映射文件形式书写SQL语句;反之则用注解形式书写SQL语句,具体可详见Spring注解形式 环境准备相同步骤 Step1: 导入相关坐标,完整pom.…...

保姆级教程Docker部署Redis镜像

目录 1、创建挂载目录和配置文件 2、运行Redis镜像 3、查看redis运行状态 1、创建挂载目录和配置文件 # 创建宿主机Redis配置文件存放目录 sudo mkdir -p /data/docker/redis/conf# 创建Redis配置文件 cd /data/docker/redis/conf sudo touch redis.conf 到Github上找到Redi…...

子类有多个父类的情况下Super不支持指定父类来调用方法

1、Super使用方法 super()函数在Python中用于调用父类的方法。它返回一个代理对象,可以通过该对象调用父类的方法。 要使用super()方法,需要在子类的方法中调用super(),并指定子类本身以及方法的名称。这样就可以在子类中调用父类的方法。 …...

AI大模型ollama结合Open-webui

AI大模型Ollama结合Open-webui 作者:行癫(盗版必究) 一:认识 Ollama 1.什么是Ollama Ollama是一个开源的 LLM(大型语言模型)服务工具,用于简化在本地运行大语言模型,降低使用大语言模型的门槛,使得大模型的开发者、研究人员和爱好者能够在本地环境快速实验、管理和…...

使用VSCode开发Django指南

使用VSCode开发Django指南 一、概述 Django 是一个高级 Python 框架,专为快速、安全和可扩展的 Web 开发而设计。Django 包含对 URL 路由、页面模板和数据处理的丰富支持。 本文将创建一个简单的 Django 应用,其中包含三个使用通用基本模板的页面。在此…...

)

椭圆曲线密码学(ECC)

一、ECC算法概述 椭圆曲线密码学(Elliptic Curve Cryptography)是基于椭圆曲线数学理论的公钥密码系统,由Neal Koblitz和Victor Miller在1985年独立提出。相比RSA,ECC在相同安全强度下密钥更短(256位ECC ≈ 3072位RSA…...

vue3 定时器-定义全局方法 vue+ts

1.创建ts文件 路径:src/utils/timer.ts 完整代码: import { onUnmounted } from vuetype TimerCallback (...args: any[]) > voidexport function useGlobalTimer() {const timers: Map<number, NodeJS.Timeout> new Map()// 创建定时器con…...

PL0语法,分析器实现!

简介 PL/0 是一种简单的编程语言,通常用于教学编译原理。它的语法结构清晰,功能包括常量定义、变量声明、过程(子程序)定义以及基本的控制结构(如条件语句和循环语句)。 PL/0 语法规范 PL/0 是一种教学用的小型编程语言,由 Niklaus Wirth 设计,用于展示编译原理的核…...

关于 WASM:1. WASM 基础原理

一、WASM 简介 1.1 WebAssembly 是什么? WebAssembly(WASM) 是一种能在现代浏览器中高效运行的二进制指令格式,它不是传统的编程语言,而是一种 低级字节码格式,可由高级语言(如 C、C、Rust&am…...

高防服务器能够抵御哪些网络攻击呢?

高防服务器作为一种有着高度防御能力的服务器,可以帮助网站应对分布式拒绝服务攻击,有效识别和清理一些恶意的网络流量,为用户提供安全且稳定的网络环境,那么,高防服务器一般都可以抵御哪些网络攻击呢?下面…...

逻辑回归暴力训练预测金融欺诈

简述 「使用逻辑回归暴力预测金融欺诈,并不断增加特征维度持续测试」的做法,体现了一种逐步建模与迭代验证的实验思路,在金融欺诈检测中非常有价值,本文作为一篇回顾性记录了早年间公司给某行做反欺诈预测用到的技术和思路。百度…...

Cilium动手实验室: 精通之旅---13.Cilium LoadBalancer IPAM and L2 Service Announcement

Cilium动手实验室: 精通之旅---13.Cilium LoadBalancer IPAM and L2 Service Announcement 1. LAB环境2. L2公告策略2.1 部署Death Star2.2 访问服务2.3 部署L2公告策略2.4 服务宣告 3. 可视化 ARP 流量3.1 部署新服务3.2 准备可视化3.3 再次请求 4. 自动IPAM4.1 IPAM Pool4.2 …...

[USACO23FEB] Bakery S

题目描述 Bessie 开了一家面包店! 在她的面包店里,Bessie 有一个烤箱,可以在 t C t_C tC 的时间内生产一块饼干或在 t M t_M tM 单位时间内生产一块松糕。 ( 1 ≤ t C , t M ≤ 10 9 ) (1 \le t_C,t_M \le 10^9) (1≤tC,tM≤109)。由于空间…...

Java 与 MySQL 性能优化:MySQL 慢 SQL 诊断与分析方法详解

文章目录 一、开启慢查询日志,定位耗时SQL1.1 查看慢查询日志是否开启1.2 临时开启慢查询日志1.3 永久开启慢查询日志1.4 分析慢查询日志 二、使用EXPLAIN分析SQL执行计划2.1 EXPLAIN的基本使用2.2 EXPLAIN分析案例2.3 根据EXPLAIN结果优化SQL 三、使用SHOW PROFILE…...