基于Verilog HDL的状态机描述方法

⭐本专栏针对FPGA进行入门学习,从数电中常见的逻辑代数讲起,结合Verilog HDL语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机FSM进行剖析与建模。

🔥文章和代码已归档至【Github仓库:hardware-tutorial】,需要的朋友们自取。或者关注公众号【AIShareLab】,回复 FPGA 也可获取。

文章目录

- 状态图的建立过程

- 状态图描述方法

- 单个always块描述状态机的方法(尽量避免)

- 两个always块描述状态机的方法(推荐写法)

- 使用三个always块分别描述

- 三种描述方法比较

状态图的建立过程

设计一个序列检测器电路。功能是检测出串行输入数据Sin中的4位二进制序列0101(自左至右输入),当检测到该序列时,输出Out=1;没有检测到该序列时,输出Out=0。(注意考虑序列重叠的可能性,如010101,相当于出现两个0101序列)。

解:首先,确定采用米利型状态机设计该电路。因为该电路在连续收到信号0101时,输出为1,其他情况下输出为0,所以采用米利型状态机。

其次,确定状态机的状态图。根据设计要求,该电路至少应有四个状态,分别用S1、S2、S3、S4表示。若假设电路的初始状态用S0表示,则可用五个状态来描述该电路。根据分析,可以画出图(a)所示的原始状态图。

观察该图可以看出,S2、S4为等价状态,可用S2代替S4,于是得到简化状态图。

然后,根据上面的状态图给出该状态机的输出逻辑。该状态机只有一个输出变量Out,其输出逻辑非常简单,直接标注在状态图中了。若输出变量较多,则可以列出输出逻辑真值表。

最后,就可以使用硬件描述语言对状态图进行描述了。

状态图描述方法

利用Verilog HDL语言描述状态图主要包含四部分内容:

-

利用参数定义语句parameter描述状态机中各个状态的名称,并指定状态编码。例如,对序列检测器的状态分配可以使用最简单的自然二进制码,其描述如下:

parameter S0=2'b00, S1=2'b01, S2 = 2'b10, S3 = 2'b11;或者,

parameter [1:0] S0=2'b00, S1=2'b01, S2 = 2'b10, S3 = 2'b11; -

用时序的always 块描述状态触发器实现的状态存储。

-

使用敏感表和case语句(也可以采用if-else等价语句)描述的状态转换逻辑。

-

描述状态机的输出逻辑。

描述状态图的方法多种多样,下面介绍几种:

单个always块描述状态机的方法(尽量避免)

用一个always块对该例的状态机进行描述,其代码如下:

module Detector1 ( Sin, CP, nCR, Out) ;input Sin, CP, nCR; //声明输入变量output Out ; //声明输出变量reg Out; reg [1:0] state;

// 声明两个状态触发器变量state[1]和state[0],记忆电路现态

//The state labels and their assignments

parameter [1:0] S0=2'b00, S1=2'b01, S2 = 2'b10, S3 = 2'b11;

always @(posedge CP or negedge nCR)

begin

if (~nCR)

state <= S0; //在nCR跳变为0时,异步清零

elsecase(state) S0: begin Out =1’b0; state <= (Sin==1)? S0 : S1; endS1: begin Out = 1’b0; state <= (Sin==1)? S2 : S1; endS2: begin Out = 1’b0; state <= (Sin==1)? S0 : S3; end S3: if (Sin==1) begin Out =1’b1; state <= S2; endelse begin Out =1’b0; state <= S1; end endcase

end

endmodule

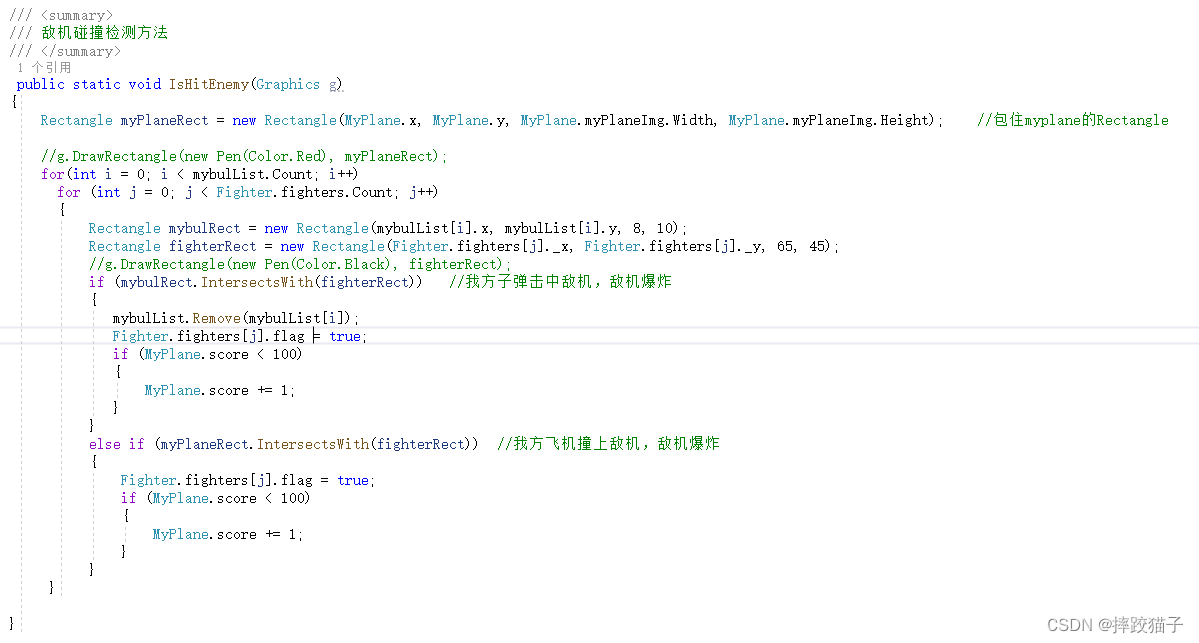

严格地说,对序列检测器电路用单个always块的描述方法所描述的逻辑存在着一个隐含的错误,即输出信号Out的描述。

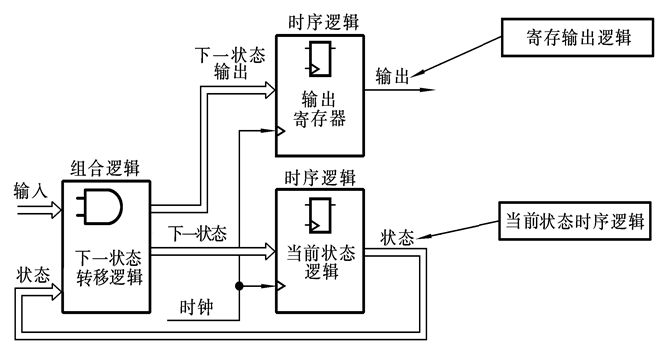

case语句中对输出向量的赋值应是下一个状态输出,这点易出错;状态向量与输出向量都由寄存器实现,面积大,不能实现异步米勒状态机。因此,单个always块描述状态机的写法仅仅适用于穆尔型状态机。单个always块写法的电路结构框图可以用下图进行概括。

两个always块描述状态机的方法(推荐写法)

用两个always块对该例的状态机进行描述,其代码如下:

module Detector2 ( Sin, CP, nCR, Out) ;

input Sin, CP, nCR; //定义输入变量

output Out ; //定义输出变量

reg Out;

reg [1:0] Current_state, Next_state;

parameter [1:0] S0=2'b00, S1=2'b01, S2 = 2'b10, S3 = 2'b11;

//状态转换,时序逻辑always @(posedge CP or negedge nCR )

begin

if (~nCR)Current_state <= S0; //异步清零

elseCurrent_state <= Next_state; //在CP上升沿触发器状态翻转end//下一状态产生和输出信号,组合逻辑

always @( Current_state or Sin) begin Next_state =2’bxx; Out=1’b 0;case(Current_state )S0: begin Out =1’b0; Next_state = (Sin==1)? S0 : S1; endS1: begin Out =1’b0; Next_state = (Sin==1)? S2 : S1; endS2: begin Out =1’b0; Next_state = (Sin==1)? S0 : S3; end S3: if (Sin==1)begin Out =1’b1; Next_state = S2; endelsebegin Out =1’b0; Next_state = S1; end endcaseend endmodule

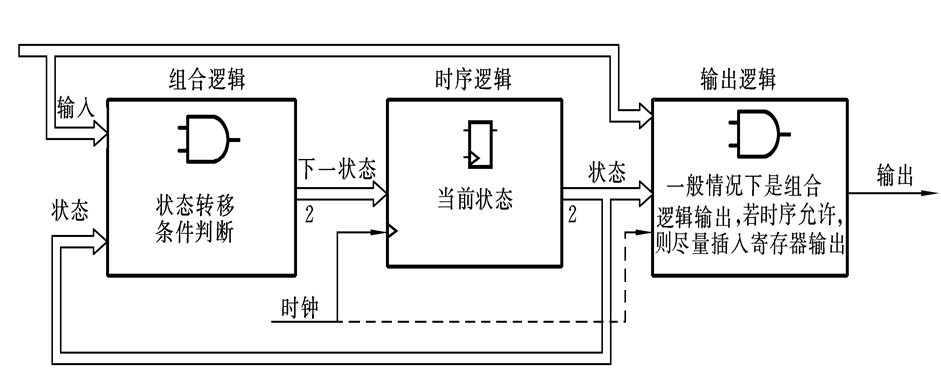

用两个always块描述状态机的写法是值得推荐的方法之一,两个always块写法的电路结构框图可以用下图进行概括。

两个always块写法的电路结构框图概括。

第一个always模块采用同步时序逻辑方式描述状态转移(中间方框); 第二个always模块采用组合逻辑方式描述状态转移规律(第一个方框)和描述电路的输出信号(第三个方框)。

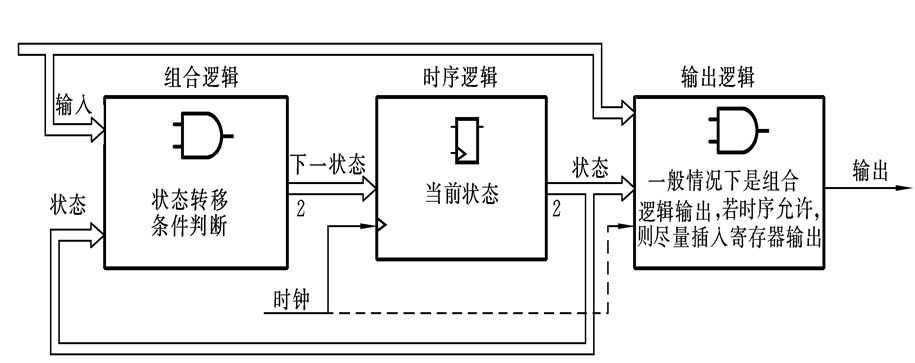

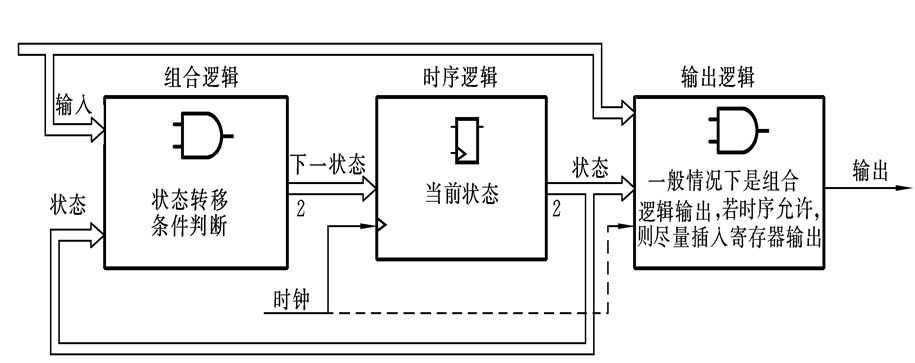

使用三个always块分别描述

即第一个always模块采用同步时序逻辑方式描述状态转移(中间方框); 第二个always模块采用组合逻辑方式描述状态转移规律(第一个方框); 第三个always模块描述电路的输出信号,在时序允许的情况下,通常让输出信号经过一个寄存器再输出,保证输出信号中没有毛刺。

用三个always块对该例的状态机进行描述,其代码如下:

module Detector3 ( Sin, CP, nCR, Out) ;input Sin, CP, nCR; //定义输入变量output Out ; //定义输出变量reg Out; reg [1:0] Current_state, Next_state;parameter [1:0] S0=2'b00, S1=2'b01, S2 = 2'b10, S3 = 2'b11;

//状态转换,时序逻辑

always @(posedge CP or negedge nCR )beginif (~nCR)Current_state <= S0; //异步清零elseCurrent_state <= Next_state; //在CP上升沿触发器状态翻转end //下一状态产生,组合逻辑

always @( Current_state or Sin) begin Next_state =2’bxx; case(Current_state )S0: begin Next_state = (Sin==1)? S0 : S1; endS1: begin Next_state = (Sin==1)? S2 : S1; endS2: begin Next_state = (Sin==1)? S0 : S3; end S3: if (Sin==1)begin Next_state = S2; endelsebegin Next_state = S1; end endcaseend /* 输出逻辑: 让输出信号经过一个寄存器再输出,可以消除Out信号中的毛刺,时序逻辑*/

always @ (posedge CP or negedge nCR )beginif (~nCR) Out <= 1’b 0;else begin case(Current_state )S0, S1, S2: Out <= 1’b0; S3: if (Sin==1) Out <= 1’b1; else Out <= 1’b0; endcaseend end

endmodule

三种描述方法比较

| 1-always | 2-always | 3-always | |

|---|---|---|---|

| 结构化设计 | 否 | 是 | 是 |

| 代码编写/理解 | 不宜,理解难 | 宜 | 宜 |

| 输出信号 | 寄存器输出 | 组合逻辑输出 | 寄存器输出 |

| 不产生毛刺 | 产生毛刺 | 不产生毛刺 | |

| 面积消耗 | 大 | 最小 | 小 |

| 时序约束 | 不利 | 有利 | 有利 |

| 可靠性、可维护性 | 低 | 较高 | 最高 |

| 后端物理设计 | 不利 | 有利 | 有利 |

参考文献:

- Verilog HDL与FPGA数字系统设计,罗杰,机械工业出版社,2015年04月

- Verilog HDL与CPLD/FPGA项目开发教程(第2版), 聂章龙, 机械工业出版社, 2015年12月

- Verilog HDL数字设计与综合(第2版), Samir Palnitkar著,夏宇闻等译, 电子工业出版社, 2015年08月

- Verilog HDL入门(第3版), J. BHASKER 著 夏宇闻甘伟 译, 北京航空航天大学出版社, 2019年03月

相关文章:

基于Verilog HDL的状态机描述方法

⭐本专栏针对FPGA进行入门学习,从数电中常见的逻辑代数讲起,结合Verilog HDL语言学习与仿真,主要对组合逻辑电路与时序逻辑电路进行分析与设计,对状态机FSM进行剖析与建模。 🔥文章和代码已归档至【Github仓库…...

6年软件测试经历:成长、迷茫、奋斗

前言 测试工作6年,经历过不同产品、共事过不同专业背景、能力的同事,踩过测试各种坑、遇到过各种bug。测试职场生涯积极努力上进业务和技术能力快速进步过、也有努力付出却一无所得过、有对测试生涯前景充满希望认为一片朝气蓬勃过、也有对中年危机思考不…...

OpenMMLab AI实战营第五次课程

语义分割与MMSegmentation 什么是语义分割 任务: 将图像按照物体的类别分割成不同的区域 等价于: 对每个像素进行分类 应用:无人驾驶汽车 自动驾驶车辆,会将行人,其他车辆,行车道,人行道、交…...

【软考】系统集成项目管理工程师(二十)项目风险管理

一、项目风险管理概述1. 风险概念2. 风险分类3. 风险成本二、项目风险管理子过程1. 规划风险管理2. 识别风险3. 实施定性风险分析4. 实施定量风险分析5. 规划风险应对6. 控制风险三、项目风险管理流程梳理一、项目风险管理概述 1. 风险概念 风险是一种不确定事件或条件,一旦…...

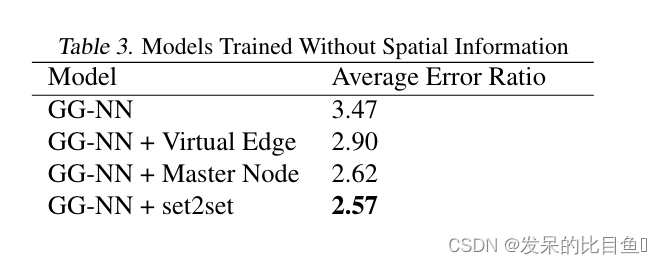

2017-PMLR-Neural Message Passing for Quantum Chemistry

2017-PMLR-Neural Message Passing for Quantum Chemistry Paper: https://arxiv.org/pdf/1704.01212.pdf Code: https://github.com/brain-research/mpnn 量子化学的神经信息传递 这篇文献作者主要是总结了先前神经网络模型的共性,提出了一种消息传递神经网络&am…...

)

Python:每日一题之全球变暖(DFS连通性判断)

题目描述 你有一张某海域 NxN 像素的照片,"."表示海洋、"#"表示陆地,如下所示: ....... .##.... .##.... ....##. ..####. ...###. ....... 其中"上下左右"四个方向上连在一起的一片陆地组成一座岛屿…...

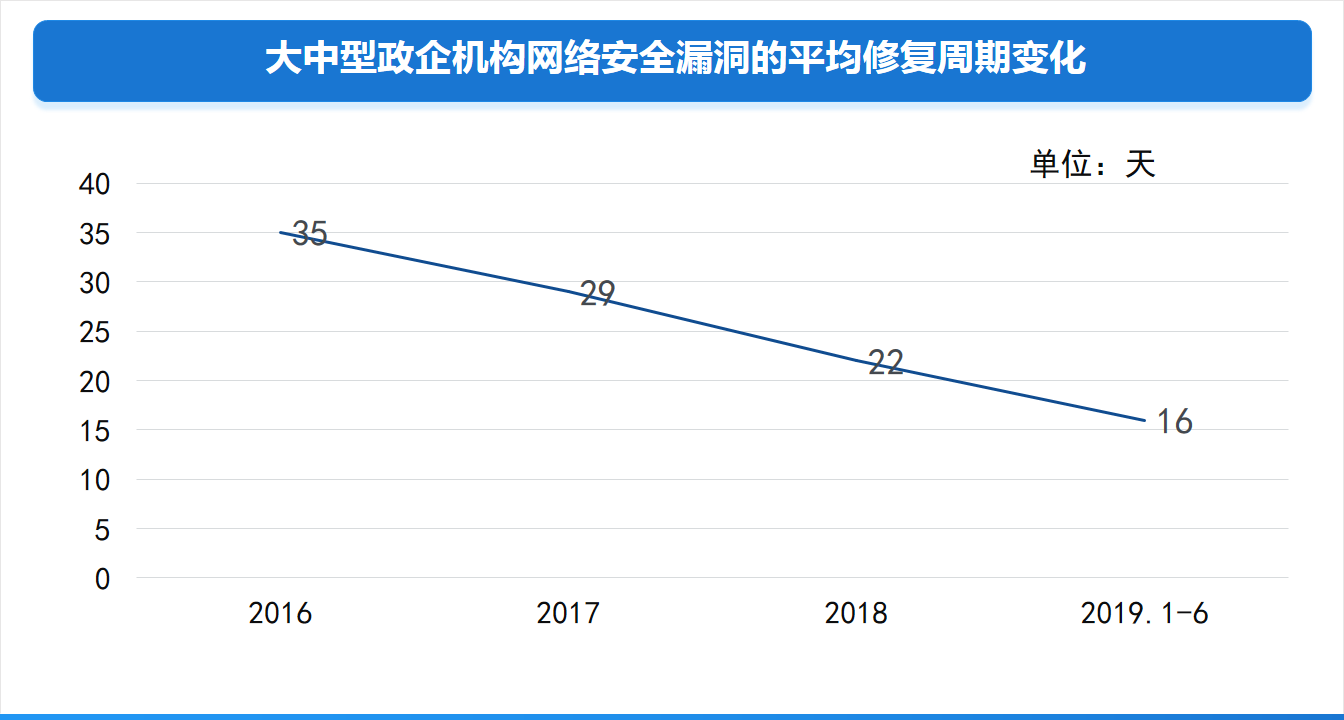

企业级安全软件装机量可能大增

声明 本文是学习大中型政企机构网络安全建设发展趋势研究报告. 而整理的学习笔记,分享出来希望更多人受益,如果存在侵权请及时联系我们 研究背景 大中型政企机构是网络安全保护的重中之重,也是国内网络安全建设投入最大,应用新技术、新产品最多的机构…...

为什么要用频谱分析仪测量频谱?

频谱分析仪是研究电信号频谱结构的仪器,用于信号失真度、调制度、谱纯度、频率稳定度和交调失真等信号参数的测量,可用以测量放大器和滤波器等电路系统的某些参数,是一种多用途的电子测量仪器。从事通信工程的技术人员,在很多时候…...

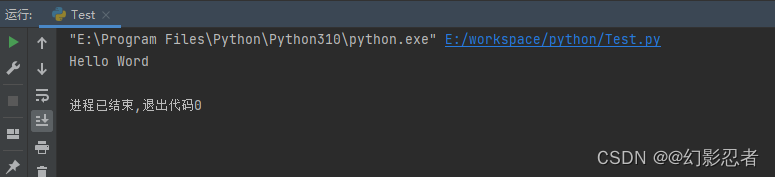

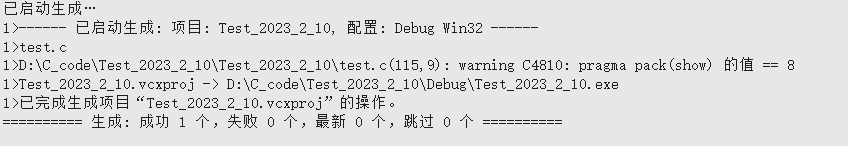

Python环境搭建、Idea整合

1、学python先要下载什么? 2、python官网 3、idea配置Python 4、idea新建python 学python先要下载什么? python是一种语言,首先你需要下载python,有了python环境,你才可以在你的电脑上使用python。现在大多使用的是pyt…...

HTTP请求返回304状态码以及研究nginx中的304

文章目录1. 引出问题2. 分析问题3. 解决问题4. 研究nginx中的3044.1 启动服务4.2 ETag说明4.3 响应头Cache-Control1. 引出问题 之前在调试接口时,代码总出现304问题,如下所示: 2. 分析问题 HTTP 304: Not Modified是什么意思? …...

【GD32F427开发板试用】使用Arm-2D显示电池电量

本篇文章来自极术社区与兆易创新组织的GD32F427开发板评测活动,更多开发板试用活动请关注极术社区网站。作者:boc 【虽迟但到】 由于快递的原因,11月份申请的,12月1日才收到GD32F427开发板。虽然姗姗来迟,但也没有减少…...

TS第二天 Typesrcipt编译

文章目录自动编译tsconfig.json配置选项include 比较重要excludeextendsfilescompilerOptions 比较重要自动编译 手动模式:每次ts文件修改完,手动编译一次 tsc 01.ts监视模式:ts文件修改完,自动监视编译 tsc 01.ts -w编译所有文…...

基于C#制作一个飞机大战小游戏

此文主要基于C#制作一个飞机大战游戏,重温经典的同时亦可学习。 实现流程1、创建项目2、界面绘制3、我方飞机4、敌方飞机5、子弹及碰撞检测实现流程 1、创建项目 打开Visual Studio,右侧选择创建新项目。 搜索框输入winform,选择windows窗体…...

git修改历史提交(commit)信息

我们在开发中使用git经常会遇到想要修改之前commit的提交信息,这里记录下怎么使用git修改之前已经提交的信息。一、修改最近一次commit的信息 首先通过git log查看commit信息。 我这里一共有6次commit记录。 最新的commit信息为“Merge branch ‘master’ of https:…...

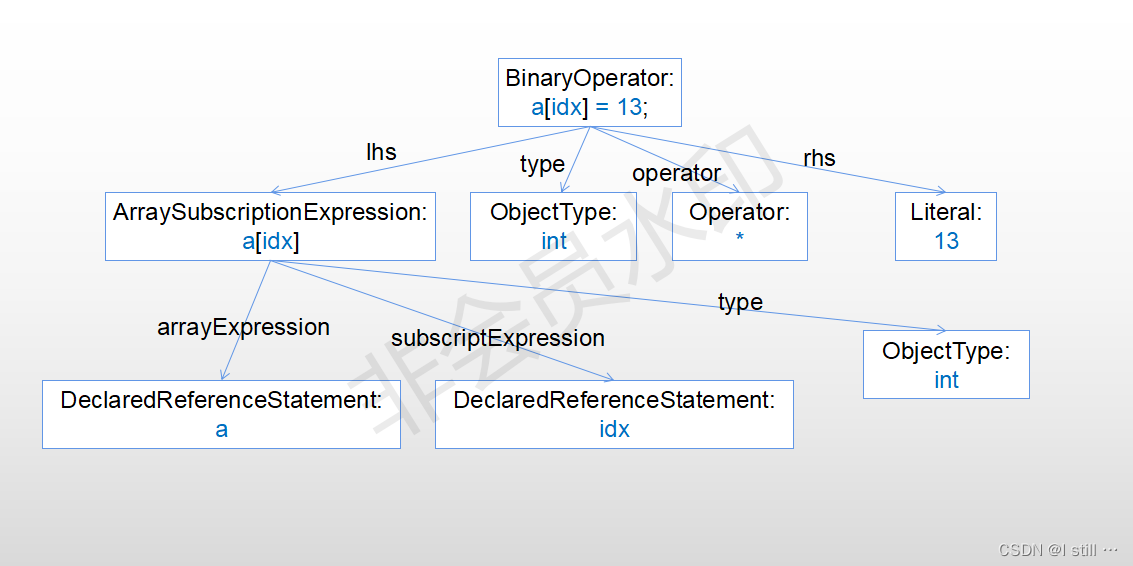

代码解析工具cpg

cpg 是一个跨语言代码属性图解析工具,它目前支持C/C (C17), Java (Java 13)并且对Go, LLVM, python, TypeScript也有支持,在这个项目的根目录下: cpg-core为cpg解析模块的核心功能,主要包括将代码解析为图,core模块只包括对C/C/Ja…...

Linux虚拟机部署Java环境-Jdk-Mysql

Linux虚拟机部署 author hf 1.安装 电脑安装x-shell工具,然后使用堡垒机基础控件windows版进行安装扫描,最后点击自动检测,保证能扫描到X-shell工具的安装路径 使用堡垒机登录快照夏选择工具点击Xshell进行连接 查看linux版本 root:~# ca…...

每日学术速递2.9

CV - 计算机视觉 | ML - 机器学习 | RL - 强化学习 | NLP 自然语言处理 Subjects: cs.CV、cs.AI、cs.LG、cs.IR 1.Graph Signal Sampling for Inductive One-Bit Matrix Completion: a Closed-form Solution(ICLR 2023) 标题:归纳单比特矩阵完成的图信号采样&am…...

【Linux】进程优先级 | 进程的切换 | 环境变量详解

🤣 爆笑教程 👉 《看表情包学Linux》👈 猛戳订阅 🔥 💭 写在前面:我们先讲解进程的优先级,探讨为什么会存在优先级,以及如何查看系统进程、进程优先级的修改。然后讲解进程的切…...

leaflet 实现左卷帘效果 (代码示例045)

第045个 点击查看专栏目录 本示例的目的是介绍演示如何在vue+leaflet中实现左卷帘效果,这里主要引用了leaflet-side-by-side这个插件,直接调用的话,CSS方面有些问题,需要自行调整一下。 直接复制下面的 vue+leaflet源代码,操作2分钟即可运行实现效果 文章目录 示例效果配…...

程序的翻译环境和执行环境

程序环境和预处理🦖程序的翻译环境和执行环境🦖详解编译链接🐳 翻译环境🐳 详解编译过程🐳 运行环境🦖预处理详解🐳 预定义符号🐳 #define🦀 #define 定义标识符…...

AI-调查研究-01-正念冥想有用吗?对健康的影响及科学指南

点一下关注吧!!!非常感谢!!持续更新!!! 🚀 AI篇持续更新中!(长期更新) 目前2025年06月05日更新到: AI炼丹日志-28 - Aud…...

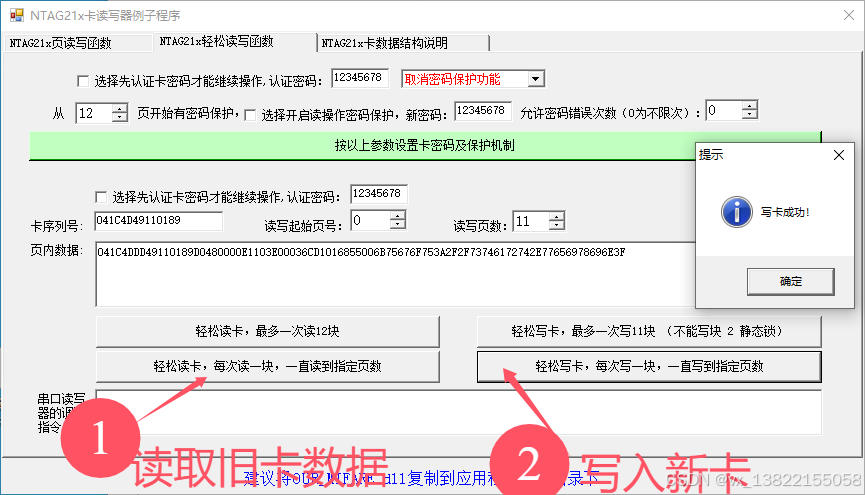

VB.net复制Ntag213卡写入UID

本示例使用的发卡器:https://item.taobao.com/item.htm?ftt&id615391857885 一、读取旧Ntag卡的UID和数据 Private Sub Button15_Click(sender As Object, e As EventArgs) Handles Button15.Click轻松读卡技术支持:网站:Dim i, j As IntegerDim cardidhex, …...

大语言模型如何处理长文本?常用文本分割技术详解

为什么需要文本分割? 引言:为什么需要文本分割?一、基础文本分割方法1. 按段落分割(Paragraph Splitting)2. 按句子分割(Sentence Splitting)二、高级文本分割策略3. 重叠分割(Sliding Window)4. 递归分割(Recursive Splitting)三、生产级工具推荐5. 使用LangChain的…...

JUC笔记(上)-复习 涉及死锁 volatile synchronized CAS 原子操作

一、上下文切换 即使单核CPU也可以进行多线程执行代码,CPU会给每个线程分配CPU时间片来实现这个机制。时间片非常短,所以CPU会不断地切换线程执行,从而让我们感觉多个线程是同时执行的。时间片一般是十几毫秒(ms)。通过时间片分配算法执行。…...

ABAP设计模式之---“简单设计原则(Simple Design)”

“Simple Design”(简单设计)是软件开发中的一个重要理念,倡导以最简单的方式实现软件功能,以确保代码清晰易懂、易维护,并在项目需求变化时能够快速适应。 其核心目标是避免复杂和过度设计,遵循“让事情保…...

华硕a豆14 Air香氛版,美学与科技的馨香融合

在快节奏的现代生活中,我们渴望一个能激发创想、愉悦感官的工作与生活伙伴,它不仅是冰冷的科技工具,更能触动我们内心深处的细腻情感。正是在这样的期许下,华硕a豆14 Air香氛版翩然而至,它以一种前所未有的方式&#x…...

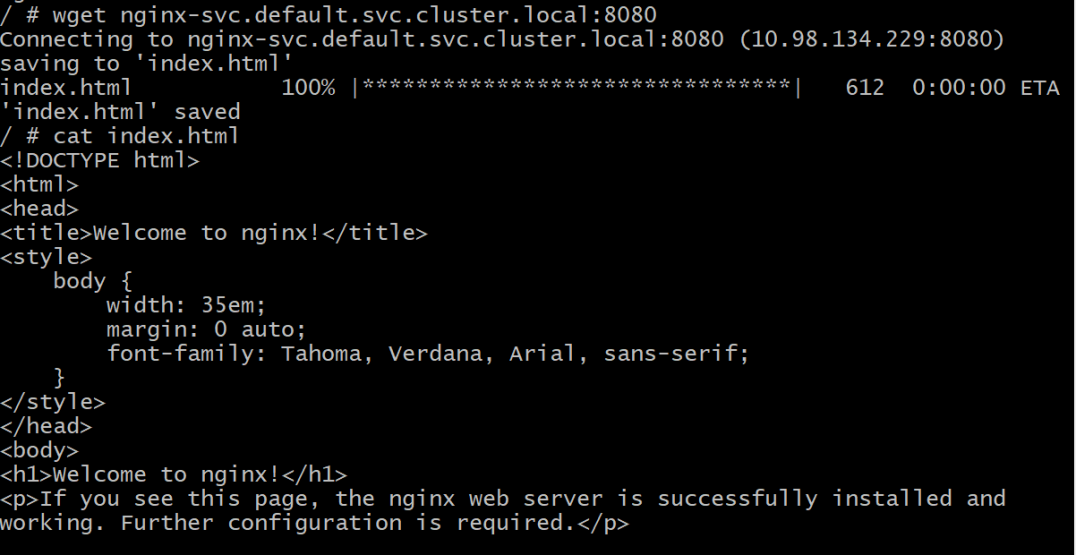

初探Service服务发现机制

1.Service简介 Service是将运行在一组Pod上的应用程序发布为网络服务的抽象方法。 主要功能:服务发现和负载均衡。 Service类型的包括ClusterIP类型、NodePort类型、LoadBalancer类型、ExternalName类型 2.Endpoints简介 Endpoints是一种Kubernetes资源…...

【Go语言基础【13】】函数、闭包、方法

文章目录 零、概述一、函数基础1、函数基础概念2、参数传递机制3、返回值特性3.1. 多返回值3.2. 命名返回值3.3. 错误处理 二、函数类型与高阶函数1. 函数类型定义2. 高阶函数(函数作为参数、返回值) 三、匿名函数与闭包1. 匿名函数(Lambda函…...

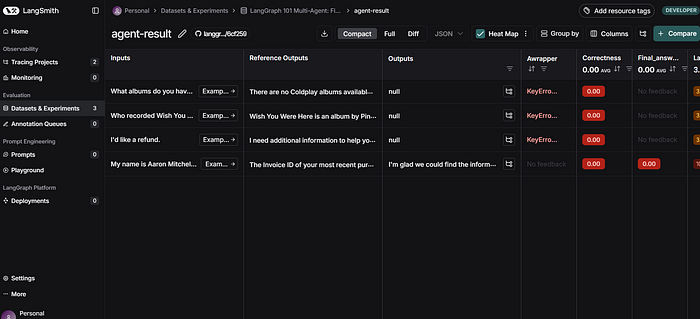

使用LangGraph和LangSmith构建多智能体人工智能系统

现在,通过组合几个较小的子智能体来创建一个强大的人工智能智能体正成为一种趋势。但这也带来了一些挑战,比如减少幻觉、管理对话流程、在测试期间留意智能体的工作方式、允许人工介入以及评估其性能。你需要进行大量的反复试验。 在这篇博客〔原作者&a…...

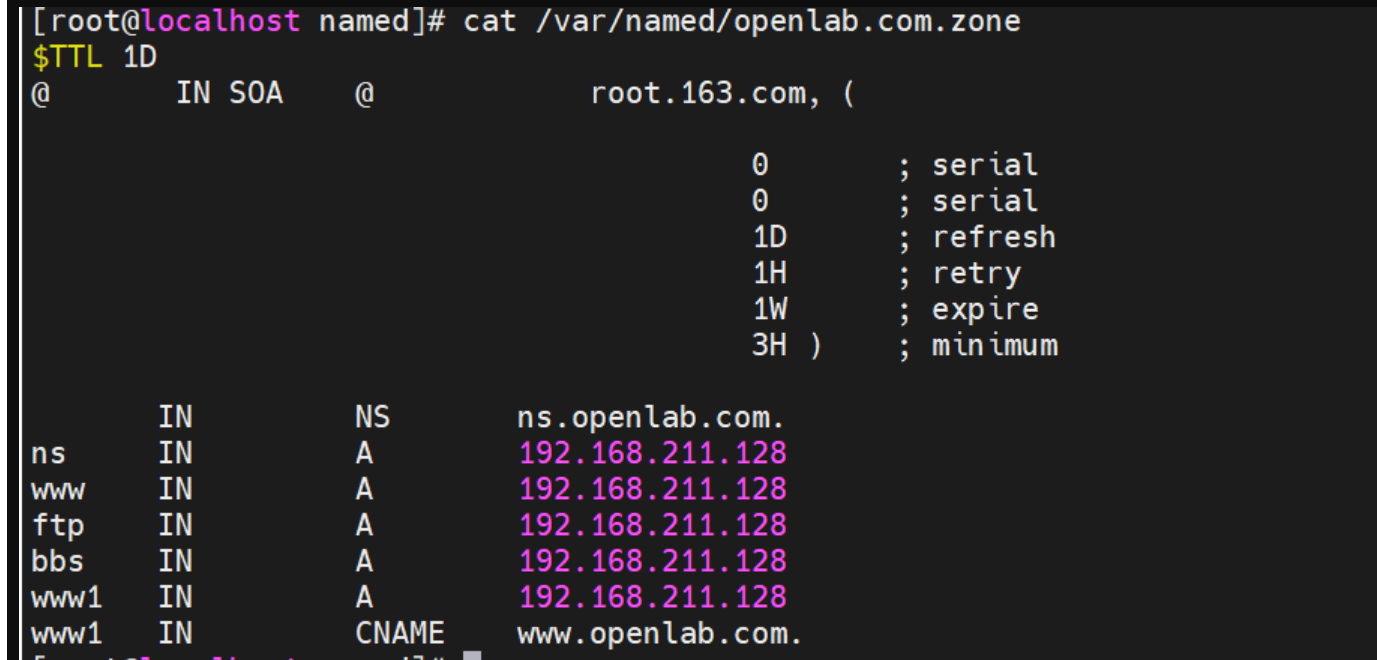

搭建DNS域名解析服务器(正向解析资源文件)

正向解析资源文件 1)准备工作 服务端及客户端都关闭安全软件 [rootlocalhost ~]# systemctl stop firewalld [rootlocalhost ~]# setenforce 0 2)服务端安装软件:bind 1.配置yum源 [rootlocalhost ~]# cat /etc/yum.repos.d/base.repo [Base…...