Mac 开发 Tang Nano FPGA 指南(使用终端和使用 VS Code 和插件,适用所有 Gowin FPGA)

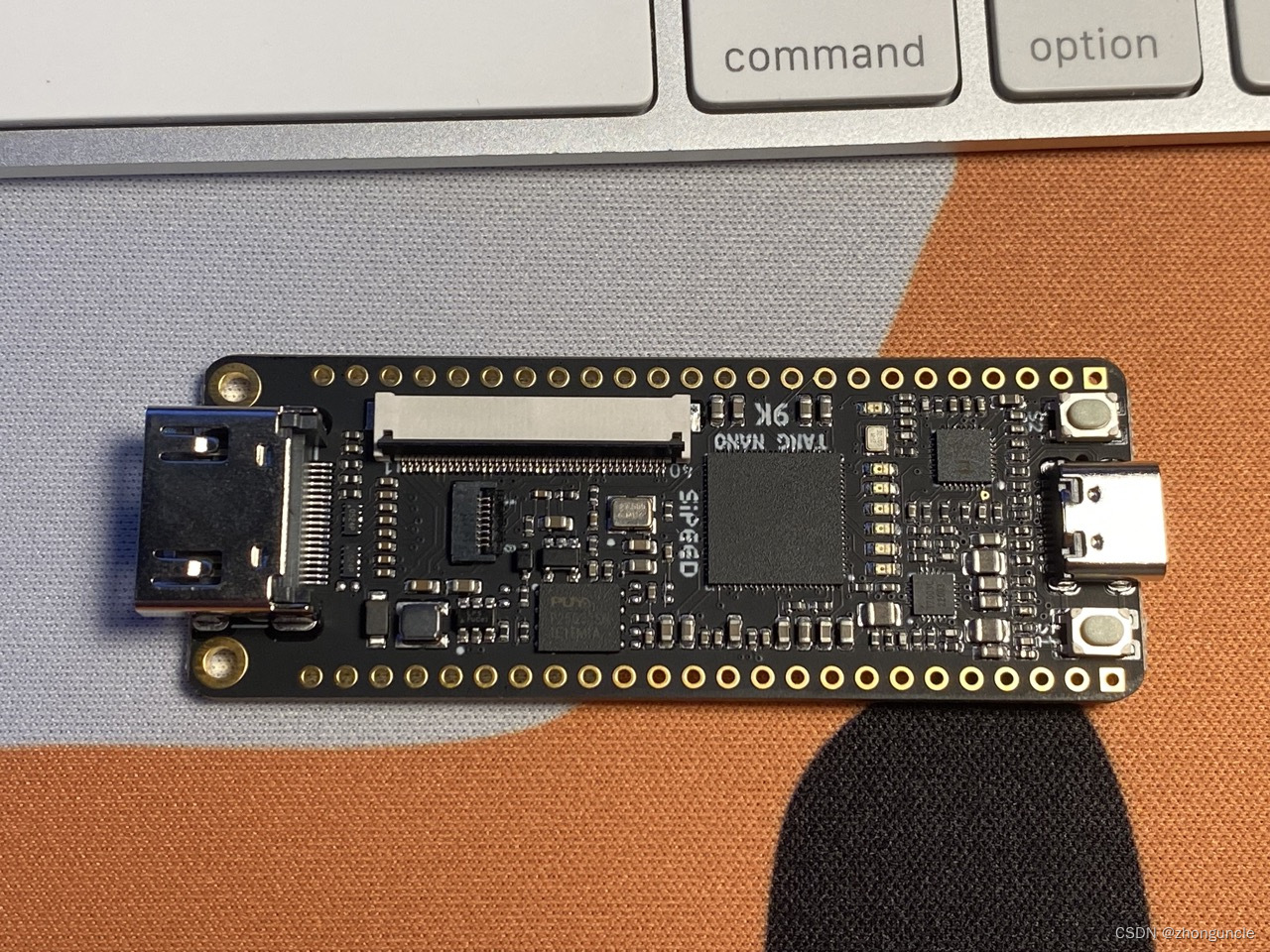

最近收到了一个 Tang nano 9K FPGA开发板,就想借此机会研究一下。

官方文档里介绍如果想使用高云的 FPGA,就需要使用 GOWIN IDE,但是需要申请 license 提交一堆资料,我是别人送的就不太方便让别人弄。加上 IDE 其实并不是很适合学习和投入生产,因为 IDE 忽略了很多细节,以及对一些工作做了处理。所以就想找到其他的工作流程,就像可以使用任何文本编辑器加上 Clang/LLVM 就可以编译 C/C++ 程序一样。

FPGA开发是在开发什么?

首先是需要知道,FPGA 开发到底是在开发什么,这样才能找到需要的工具和软件。

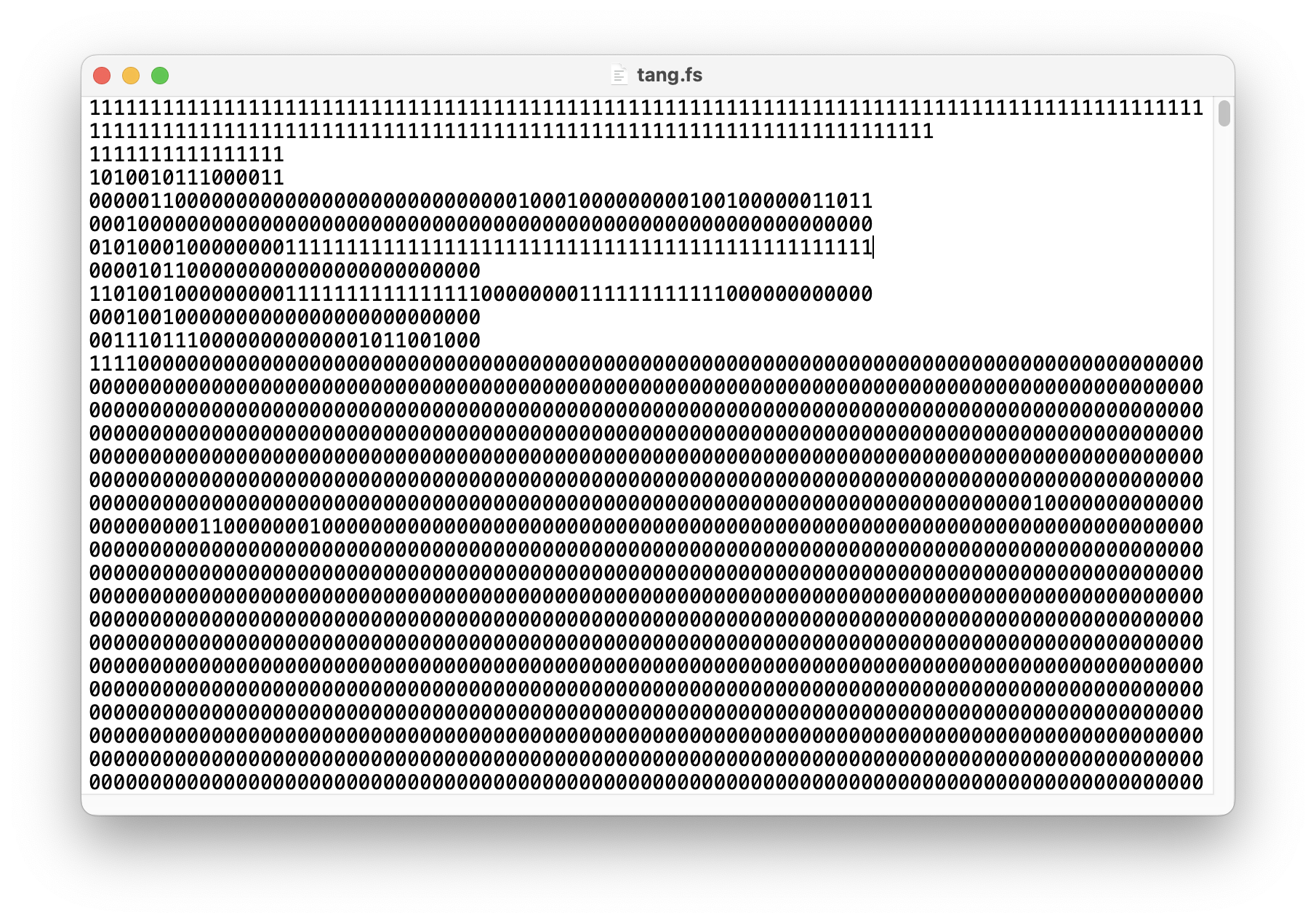

计算机械执行各种指令的本质是给一系列逻辑单元的引脚通电,然后经过逻辑电路之后输出新的电路信号。从软件的层面来说,每个引脚的输入就是一个常见到的一串二进制数字(比如01011101010)中的一位(一般使用的正逻辑中,1表示高电平,0表示低电平),早期的打孔板就是实体版的这种二进制数字。也就是说,最终我们需要的是一个存放二进制指令的文件,然后由 FPGA 执行。

这时候还有一个问题:指令怎么知道接口和针脚谁是谁呢?不知道的话,是没有办法弄到正确的二进制指令的,因为一些指令的操作对象就可能是错误的。

接口和针脚本质是一些数字表示的,需要通过这些数字来标识,所以我们还需要标识对应接口和针脚的文件。

简而言之,开发 FPGA 就是编写两个文件:xxxx.v和xxxx.cst。

.v文件里存放的是 Verilog 语言的代码,用来连接电路中的各种门、寄存器,以及一些硬 IP(hard intellectual property)。.cst文件里存放的是引脚约束文件,用来表示 FPGA 开发板上每个引脚的作用和电压。

然后再通过一些工具,最后将其转换成存放了一堆位(bit)的文件,称之为比特流文件,来控制各部分的连接、工作等。不同 FPGA 厂商使用的文件格式不一样。这里 Tang nano 9K 使用的文件后缀为.fs,内容如下:

安装和配置需要的工具

前提

你需要有Python 3.8 或更新的版本,因为生成比特流需要使用一个 Python 脚本。Mac 一般回预装 Python,你只需要检查和更新版本即可。

工具链 OSS CAD Suite

接下来使用需要 OSS CAD Suite,这是一个工具链,可以将xxxx.v和xxxx.cst转换成最终的比特流文件(有点像编译器或者说交叉编译里的工具链),最后将其写入 FPGA。

这个套件包含了很多 FPGA 的工具,一般目录名或程序名带

gowin的便是这里 Tang Nano 系列所需的。但其实可以只安装 Gowin FPGA 芯片所需的工具的,不过 OSS CAD Suite 不光终端可以使用,VS Code 也可以使用,所以使用 OSS CAD Suite 比较方便两头使用,如果你使用其他 FPGA 的话,也可以减少安装新的工具链。

OSS CAD Suite 下载地址为:https://github.com/YosysHQ/oss-cad-suite-build/releases/latest

如果你使用最新的 OSS CAD Suite 构建时出现下列这种错误,那么建议下载 2023 年 2 月或 3 月的版本(版本更新特别快,基本上几天就一版,随便哪天的都行)

gowin_pack -d GW1N-9C -o rio.fs rio_pnr.json

Traceback (most recent call last):

File "/opt/oss-cad-suite/libexec/gowin_pack", line 33, in

sys.exit(load_entry_point('Apycula==0.8.2a1', 'console_scripts', 'gowin_pack')())

File "/opt/oss-cad-suite/lib/python3.8/site-packages/Apycula-0.8.2a1-py3.8.egg/apycula/gowin_pack.py", line 984, in main

AttributeError: module 'importlib.resources' has no attribute 'files'

make: *** [Makefile:16: rio.fs] Error 1

然后将 OSS-CAD-Suite 中bin的路径放到环境变量PATH中,你可以放到你的 Shell 配置文件中。语句如下:

export PATH="存放位置/oss-cad-suite/bin:$PATH"

然后使用source激活更新或者新开一个终端窗口即可。

只安装 Gowin FPGA 需要的工具链

Tang Nano 使用的 Gowin FPGA 芯片,它的比特流和格式的工具在 Apicula 项目中,这是地址:https://github.com/YosysHQ/apicula。如果你需要阅读文档,那么也在这个项目中。

安装方法如下:

$ pip3 install apycula

如果你想简洁安装,那么可以使用这种方法。这样下载安装的包体积会小特别多(4.1 MB 对 1.35 GB),但是万一开发过程中需要使用其他的工具,那么就得自己再去单独下载这些工具了。

文本编辑器 VS Code

编写代码这里使用 Visual Studio Code,当然你使用任何文本编辑器来编写代码,比如 Vim、Emacs 等。但是不能使用 Word、Pages 这种应用程序,因为这种应用程序实际上并不是文本编辑器,而是文本处理器,在底层并不是简单的文本。

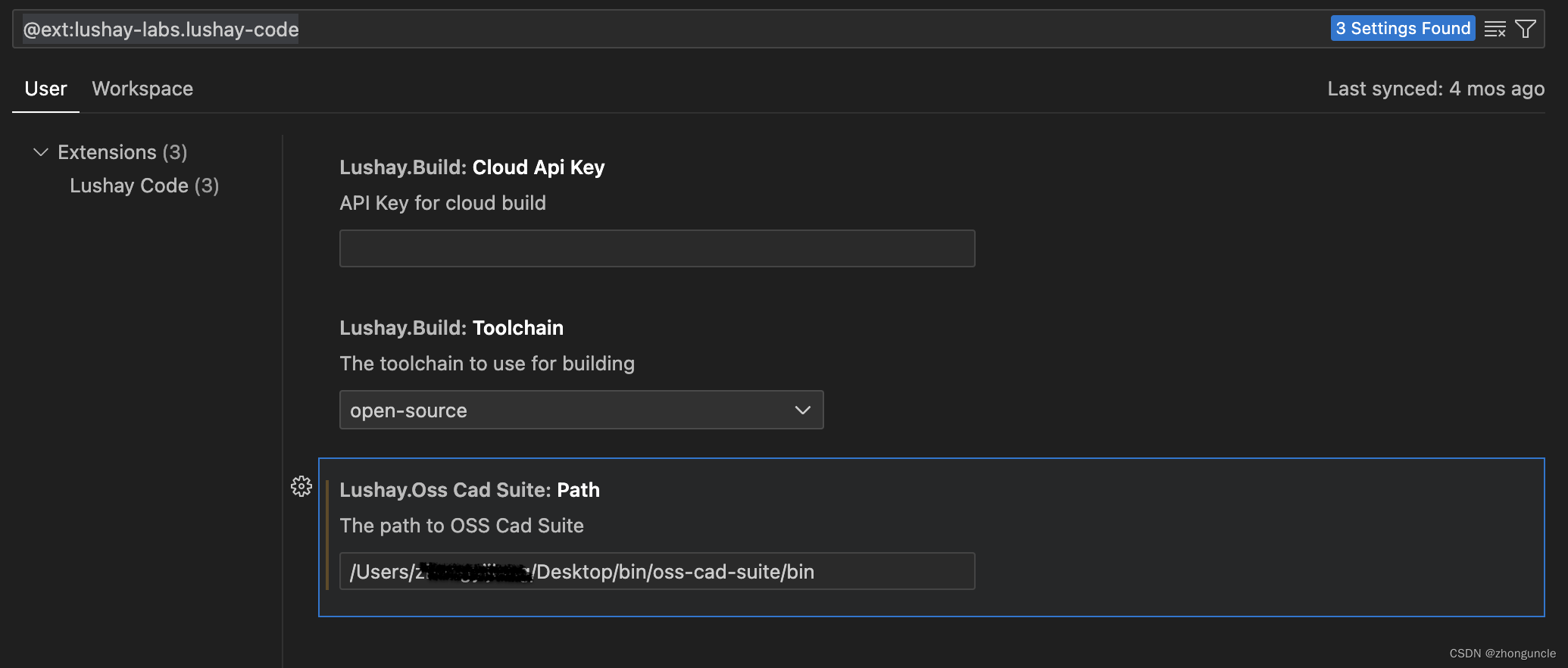

这里使用 Visual Studio Code 的原因主要是扩展会高亮代码和方便设置针脚,以及构建最终的比特流文件必须要使用一个插件来自动构建。所以需要安装两个扩展:Lushay Code和Verilog-HDL/SystemVerilog/Bluespec SystemVerilo。Lushay Code是为了使用 OSS-CAD-Suite,这是一个自动构建工具,而后者是为了高亮代码和方便设置针脚。如果Lushay Code不支持你的 FPGA,那么还请找一下支持自己 FPGA 的扩展插件。

此外要配置一下扩展,在“设置-扩展”中,将你的 OSS-CAD-Suite 位置输入到下图位置,这样 VS Code 才可以使用 OSS-CAD-Suite:

示例代码:让板载 LED 逐个亮起

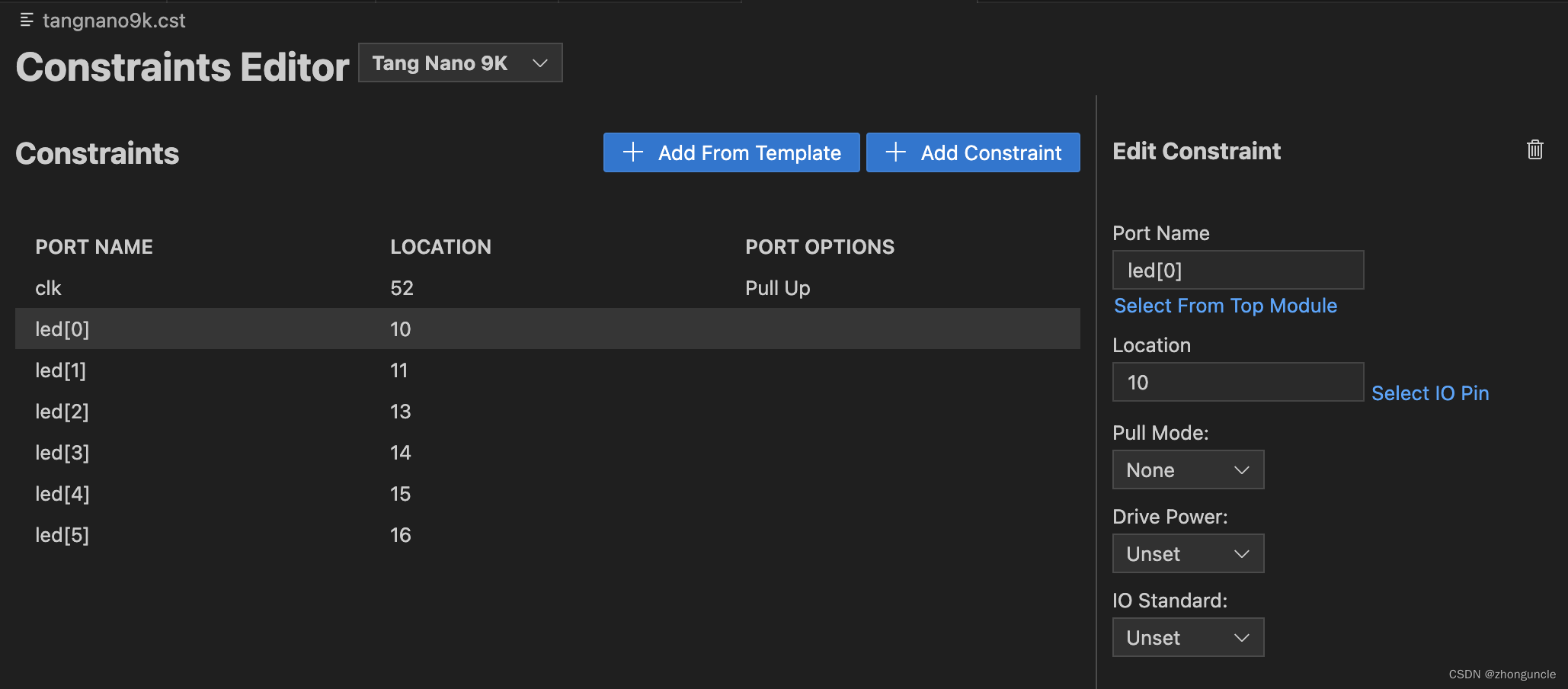

这里有两个文件:top.v和tangnano9k.cst,内容分别如下(需要注意top.v最后需要有一个空行)

// top.v

module top

(input clk,output [5:0] led

);localparam WAIT_TIME = 13500000;

reg [23:0] clockCounter = 0;

reg [5:0] cur_state = 6'b111111; // 这个六位二进制数的每一位都表示一个 LEDalways @(posedge clk) beginclockCounter <= clockCounter + 1;if (clockCounter == WAIT_TIME) beginclockCounter <= 0;cur_state <= cur_state << 1;if (cur_state == 6'b000000) begincur_state <= 6'b111111;endend

endassign led[5:0] = cur_state[5:0];endmodule// tangnano9k.cst

IO_LOC "clk" 52;

IO_PORT "clk" PULL_MODE=UP;IO_LOC "led[0]" 10;IO_LOC "led[1]" 11;IO_LOC "led[2]" 13;IO_LOC "led[3]" 14;IO_LOC "led[4]" 15;IO_LOC "led[5]" 16;如果你的tangnano9k.cst是用 VS Code 设置的,那么应该如下:

构建项目

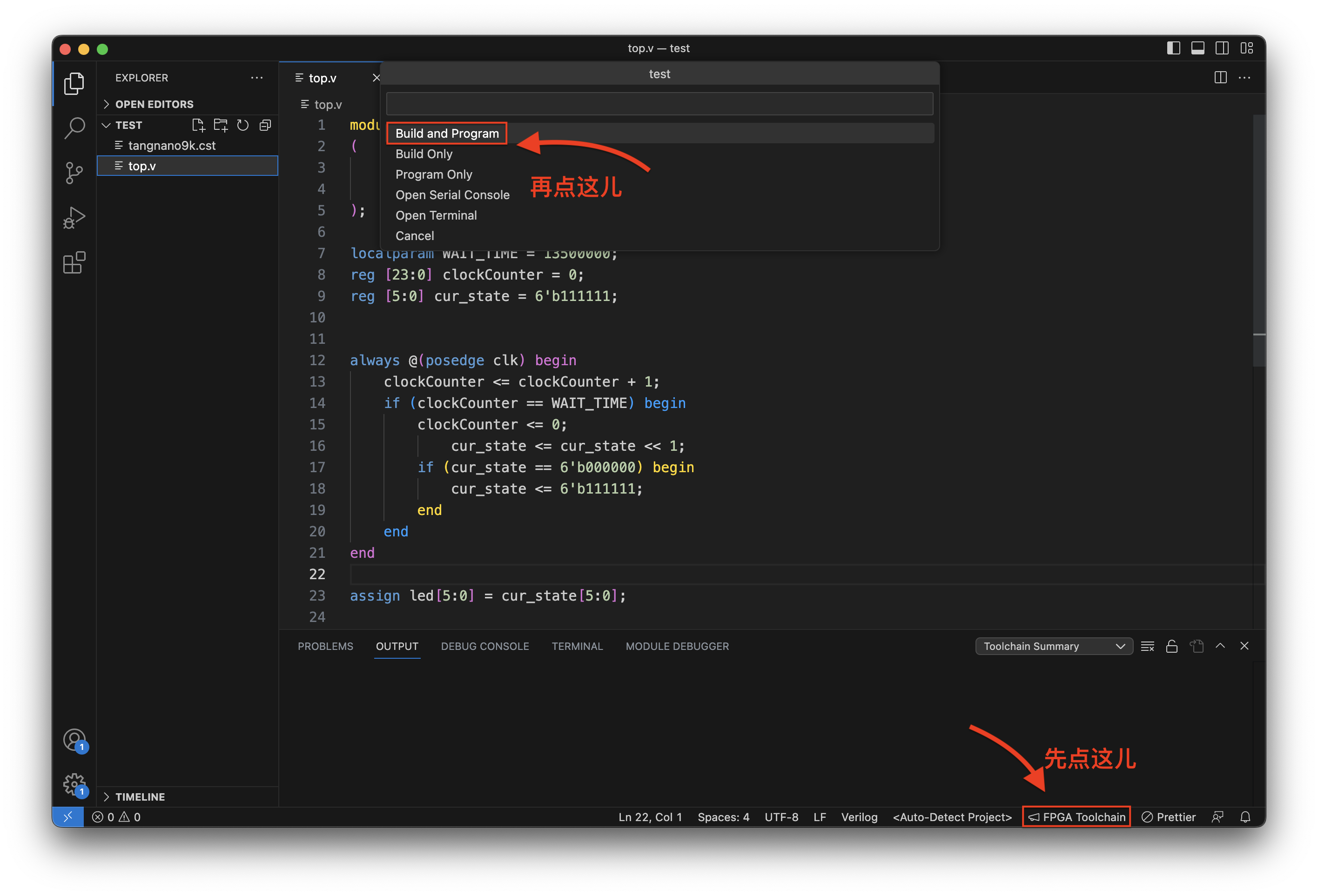

使用 VS Code 构建

这种方法很简单,如果你之前配置好了 VS Code,并且也已经将你的 FPGA 连接到 Mac 上,直接按照下图的顺序点击,等一会儿,fs文件就已经构建好并且将其烧录到 FPGA 上了:

使用终端构建

这部分划成两节,第一节详细介绍了每一步的使用和原由,第二节则将其整理成一个脚本,这样就方便许多了。

逐步来说

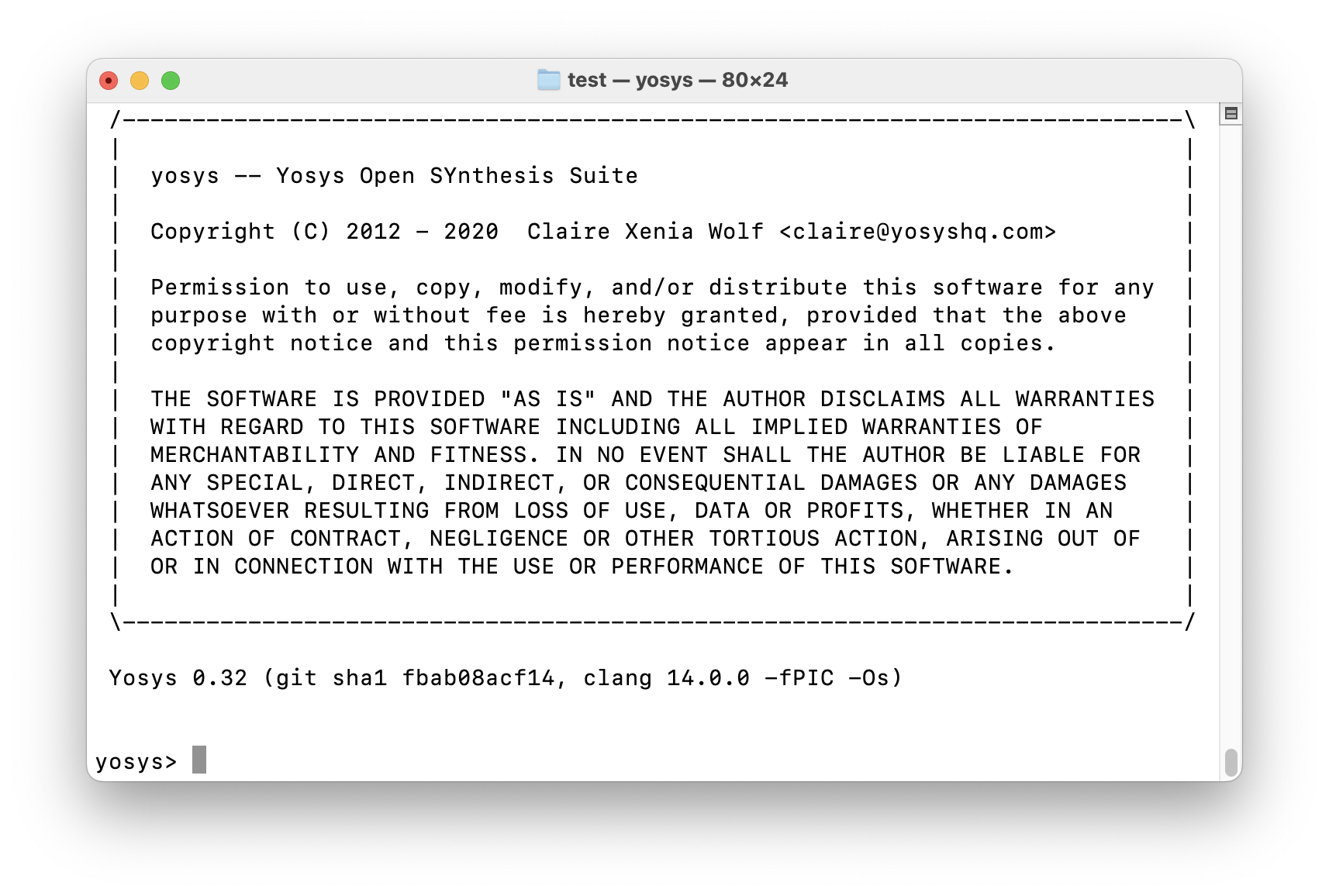

首先进入yosys(输入按回车),页面如下:

然后输入以下命令:

# 读取分析top.v的内容

> read -sv top.v

# 将top.v的内容合成转换为json格式(由于yosys已经分析了文件,所以不用文件名top.v,而是模块名top)

> synth_gowin -top top -json test.json

# 退出yosys

> exit

当然上面这部分可以化简成一句话:

$ yosys -p "read_verilog top.v; synth_gowin -json test.json"

然后使用下面的命令来进行进一步的工作:

# 通过设置设备名、CST文件和刚才生成的 JSON 文件来生成 FPGA 布局和布线信息,并且放入 test_pnr.json 中。

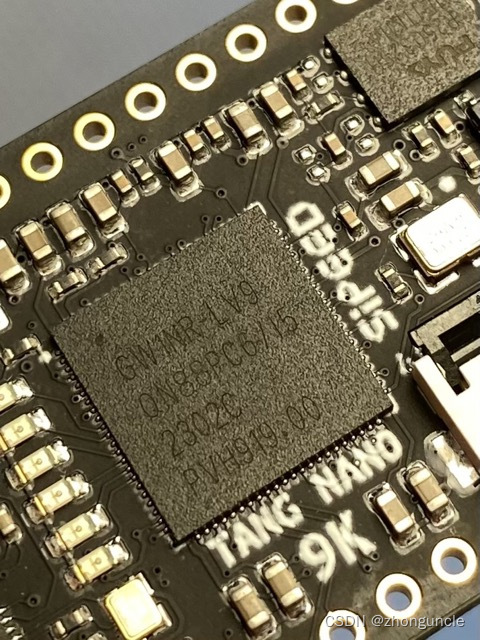

$ nextpnr-gowin --family GW1N-9C --device GW1NR-LV9QN88PC6/I5 --cst tangnano9k.cst --json test.json --write test_pnr.json

上面的家族名和设备名需要根据你自己的 FPGA 型号进行修改(如果不是 Tang nano 9K 的话可以不写--family这个选项),这个型号不是官网上短的那种。你可以在自己 FPGA 芯片封装上看到,比如下图就是 Tang nano 9K 的设备名GW1NR-LV9QN88PC6/I5:

也可以根据下面的表格进行查找:

| 名称 | 设备名(device) | 板子的名称(board) |

|---|---|---|

| Trenz TEC0117 | GW1NR-UV9QN881C6/I5 | tec0117 |

| Sipeed Tang Nano: | GW1N-LV1QN48C6/I5 | tangnano |

| Sipeed Tang Nano 1K | GW1NZ-LV1QN48C6/I5 | tangnano1k |

| Sipeed Tang Nano 4K | GW1NSR-LV4CQN48PC7/I6 | tangnano4k |

| Sipeed Tang Nano 9K | GW1NR-LV9QN88PC6/I5 | tangnano9k |

| Seeed RUNBER | GW1N-UV4LQ144C6/I5 | runber |

| @Disasm honeycomb | GW1NS-UX2CQN48C5/I4 | honeycomb |

接下来需要注意,如果你和我一样是 Tang nano 9K,那么使用下面的语句(设备不能写上面那个长的):

$ gowin_pack -d GW1N-9C -o top.fs test_pnr.json

如果你是其他型号的 Gowin FPGA,那么使用:

$ gowin_pack -d 你的设备型号 -o top.fs test_pnr.json

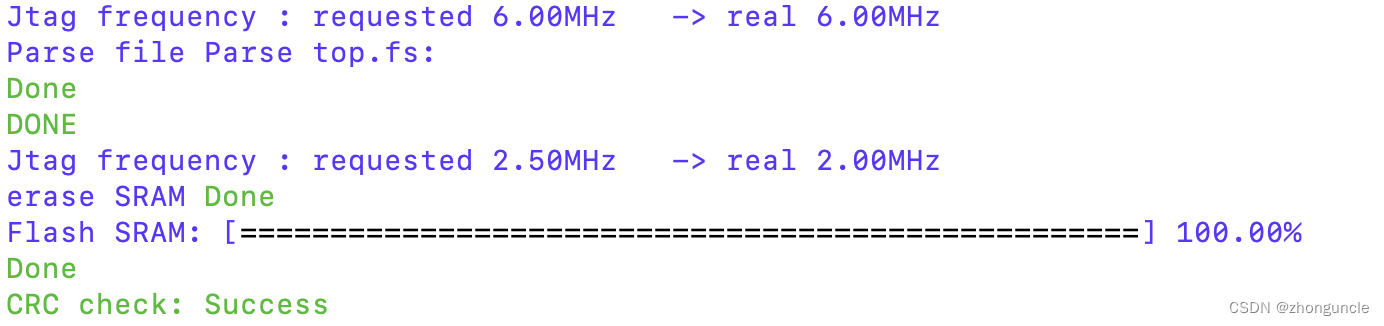

然后就是将比特流文件烧录到 FPGA 上:

openFPGALoader -b 板子的名字 pack.fs

这个板子的名称在上面的表格里可以看到对应的。如果你看到类似下面的内容,那么就是烧录成功了:

然后就可以看到这样的现象:

写个脚本

这里搞点生产力,我们将其写成脚本来实现“一步生成和烧录”,你可以根据自己的型号进行修改.

新建一个空白文本文件build.sh,然后输入:

#!/bin/bashDEVICE='GW1NR-LV9QN88PC6/I5|tangnano9k'

BOARD='tangnano9k'yosys -p "read_verilog top.v; synth_gowin -json temp.json"

nextpnr-gowin --family GW1N-9C --device GW1NR-LV9QN88PC6/I5 --cst tangnano9k.cst --json temp.json --write test_pnr.json

gowin_pack -d GW1N-9C -o top.fs test_pnr.json

openFPGALoader -b $BOARD top.fs

然后使用下面的语句赋予运行权限:

chmod +x build.sh

这样只用./build.sh就可以在当前目录下进行构建和烧录了。

扩展阅读

FPGA 是数电的一个分支,FPGA 学习过程中需要了解很多数电的术语和概念,所以可以使用数电专业的专业书来做一些入门,这对后续学习也有帮助。这里推荐剑桥大学的这些资料:

这些资料对于非数电专业的人士来说是一些不错的资料。其中很多知识点并不是问题,初高中都学过,主要是国内中学时期使用的是苏联式的符号,而绝大部分资料使用的都是美式符号或者现在的国标符号,所以如果你直接看电路图可能会看不懂。

如果你和我一样是 FPGA 新手,那么关于 FPGA 的一些术语会让人头大。比如说 Verilog 是什么?硬 IP 又是什么?针对这些 FPGA 的术语和概念,我推荐看看 Intel 联合出版的一本书《FPGAs for Dummies》,你可以很轻松的在搜索引擎中通过“FPGAs for Dummies PDF”找到,《FPGAs for Dummies》的封面如下图:

这本书用非常轻松的语言介绍了你准备踏入 FPGA 领域所需的术语、语言、设计思路、发展历程、应用等各方面的知识,以及最基础的那个问题:为什么你要使用 FPGA。

《XXX FOR DUMMIES》是一个系列书籍,致力于用诙谐、简单的语言介绍技术,类似《十分钟学会xxx》,但是作者有一些事业内蛮厉害的人。这个系列并不是 Intel 的,只是 FPGA 这本是 Intel 合作的。

关于 tang nano 9k 还有国外写的很不错的专栏,介绍了很多案例和用法,上文中提到的 Lushay Code 插件就是这个团队做的:https://learn.lushaylabs.com/getting-setup-with-the-tang-nano-9k/

然后就是 YosysHQ 一些项目的代码和文档了,比如说上文提到的:

- OSS CAD Suite:https://github.com/YosysHQ/oss-cad-suite-build

- Project Apicula:https://github.com/YosysHQ/apicula

- nextpnr:https://github.com/YosysHQ/nextpnr

希望能帮到有需要的人~

相关文章:

Mac 开发 Tang Nano FPGA 指南(使用终端和使用 VS Code 和插件,适用所有 Gowin FPGA)

最近收到了一个 Tang nano 9K FPGA开发板,就想借此机会研究一下。 官方文档里介绍如果想使用高云的 FPGA,就需要使用 GOWIN IDE,但是需要申请 license 提交一堆资料,我是别人送的就不太方便让别人弄。加上 IDE 其实并不是很适合学…...

基于深度学习的铁路异物侵限检测算法研究_整体认知感觉欠点意思,但是有一个新的变形卷积-Octave 卷积

相比于其他的交通运输方式,铁路运输具有准时性高、连续性强、速度快、运输量大、运输成本低以及安全可靠等优点。同时由于国家高速铁路网络建设的不断推进,铁路运输逐渐成为我国客运与货运的主要运输方式。虽然铁路运输为人们出行和货物运输带来的极大的…...

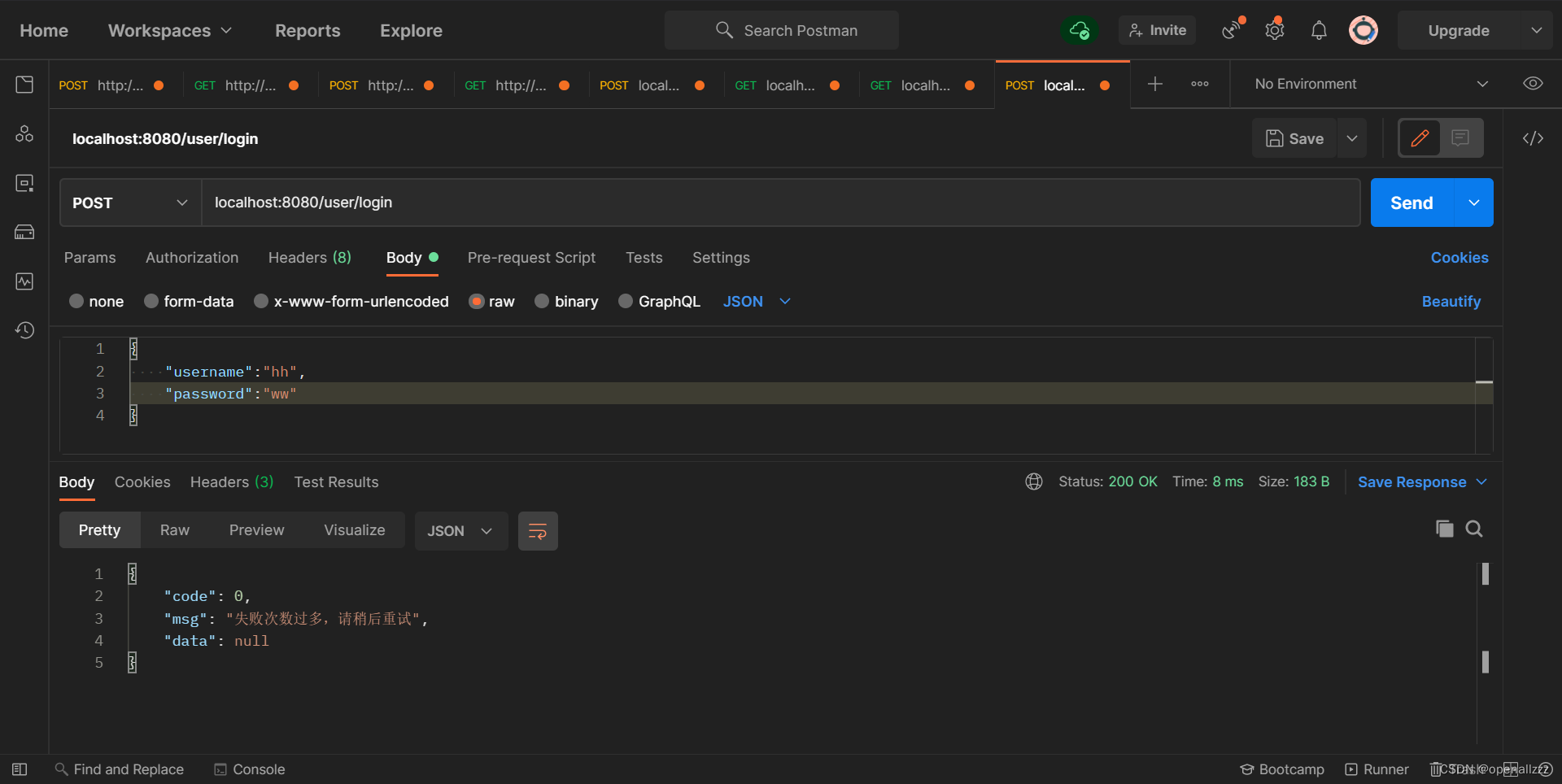

Spring项目使用Redis限制用户登录失败的次数以及暂时锁定用户登录权限

文章目录 背景环境代码实现0. 项目结构图(供参考)1. 数据库中的表(供参考)2. 依赖(pom.xml)3. 配置文件(application.yml)4. 配置文件(application-dev.yml)5…...

2023.8 - java - 变量类型

在Java语言中,所有的变量在使用前必须声明。声明变量的基本格式如下: type identifier [ value][, identifier [ value] ...] ; 格式说明: type -- 数据类型。identifier -- 是变量名,可以使用逗号 , 隔开来声明多个同类型变量…...

【Kubernetes】Kubernetes的Pod控制器

Pod控制器 一、Pod 控制器的概念1. Pod 控制器及其功用2. Pod 控制器有多种类型2.1 ReplicaSet2.2 Deployment2.3 DaemonSet2.4 StatefulSet2.5 Job2.6 Cronjob 3. Pod 与控制器之间的关系 二、Pod 控制器的使用1. Deployment2. SatefulSet2.1 为什么要有headless?2…...

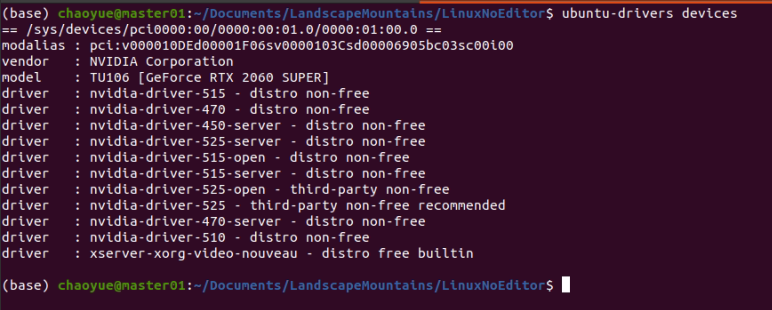

Ubuntu20.04安装Nvidia显卡驱动教程

1、禁用nouveau 1、创建文件,如果没有下载vim编辑器,将vim换成gedit即可 $ sudo vim /etc/modprobe.d/blacklist-nouveau.conf 2、在文件中插入以下内容,将nouveau加入黑名单,默认不开启 blacklist nouveau options nouveau m…...

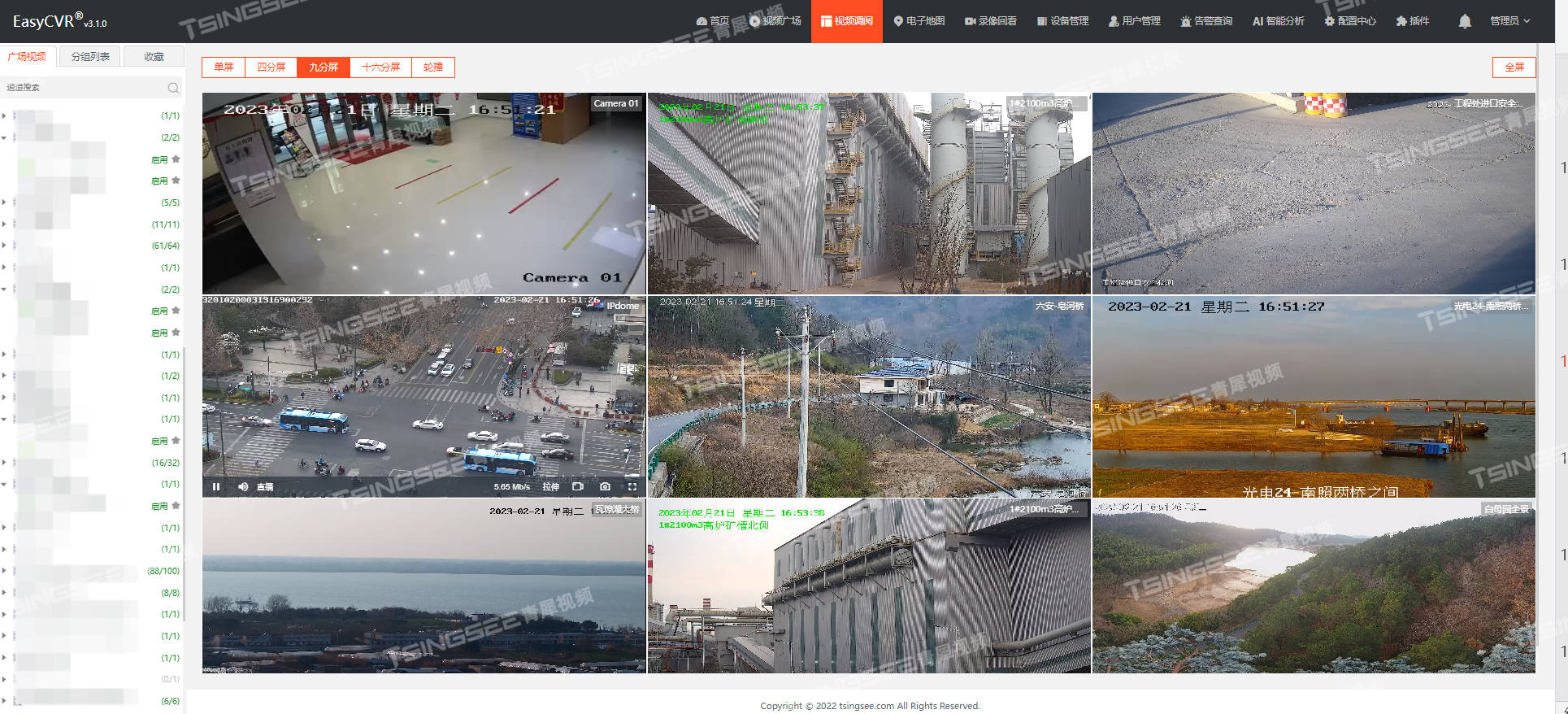

视频汇聚/视频云存储/视频监控管理平台EasyCVR添加萤石云设备详细操作来啦!

安防视频监控/视频集中存储/云存储/磁盘阵列EasyCVR平台可拓展性强、视频能力灵活、部署轻快,可支持的主流标准协议有国标GB28181、RTSP/Onvif、RTMP等,以及支持厂家私有协议与SDK接入,包括海康Ehome、海大宇等设备的SDK等。平台既具备传统安…...

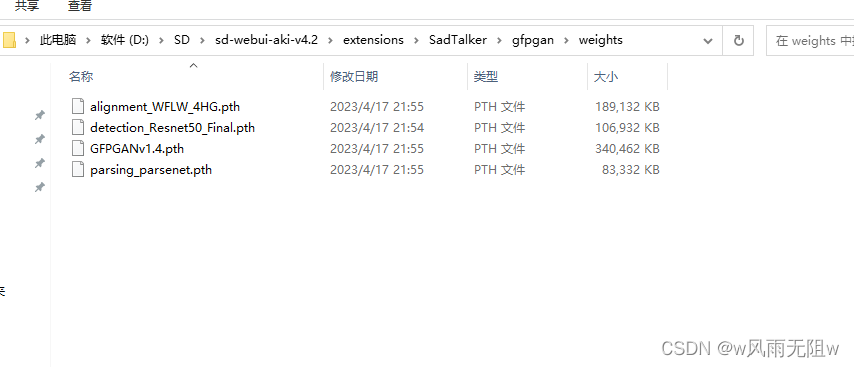

AI 绘画Stable Diffusion 研究(十二)SD数字人制作工具SadTlaker插件安装教程

免责声明: 本案例所用安装包免费提供,无任何盈利目的。 大家好,我是风雨无阻。 想必大家经常看到,无论是在产品营销还是品牌推广时,很多人经常以数字人的方式来为自己创造财富。而市面上的数字人收费都比较昂贵,少则几…...

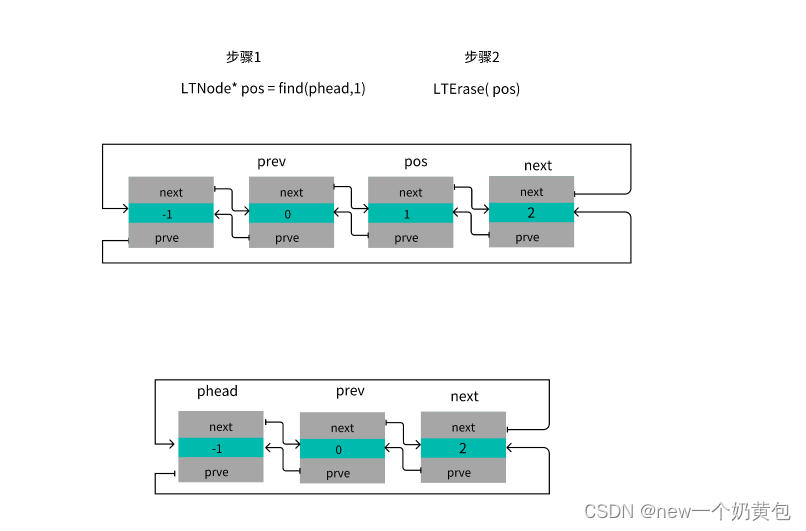

数据结构——链表详解

链表 文章目录 链表前言认识链表单链表结构图带头单循环链表结构图双向循环链表结构图带头双向循环链表结构图 链表特点 链表实现(带头双向循环链表实现)链表结构体(1) 新建头节点(2) 建立新节点(3)尾部插入节点(4)删除节点(5)头部插入节点(6) 头删节点(7) 寻找节点(8) pos位置…...

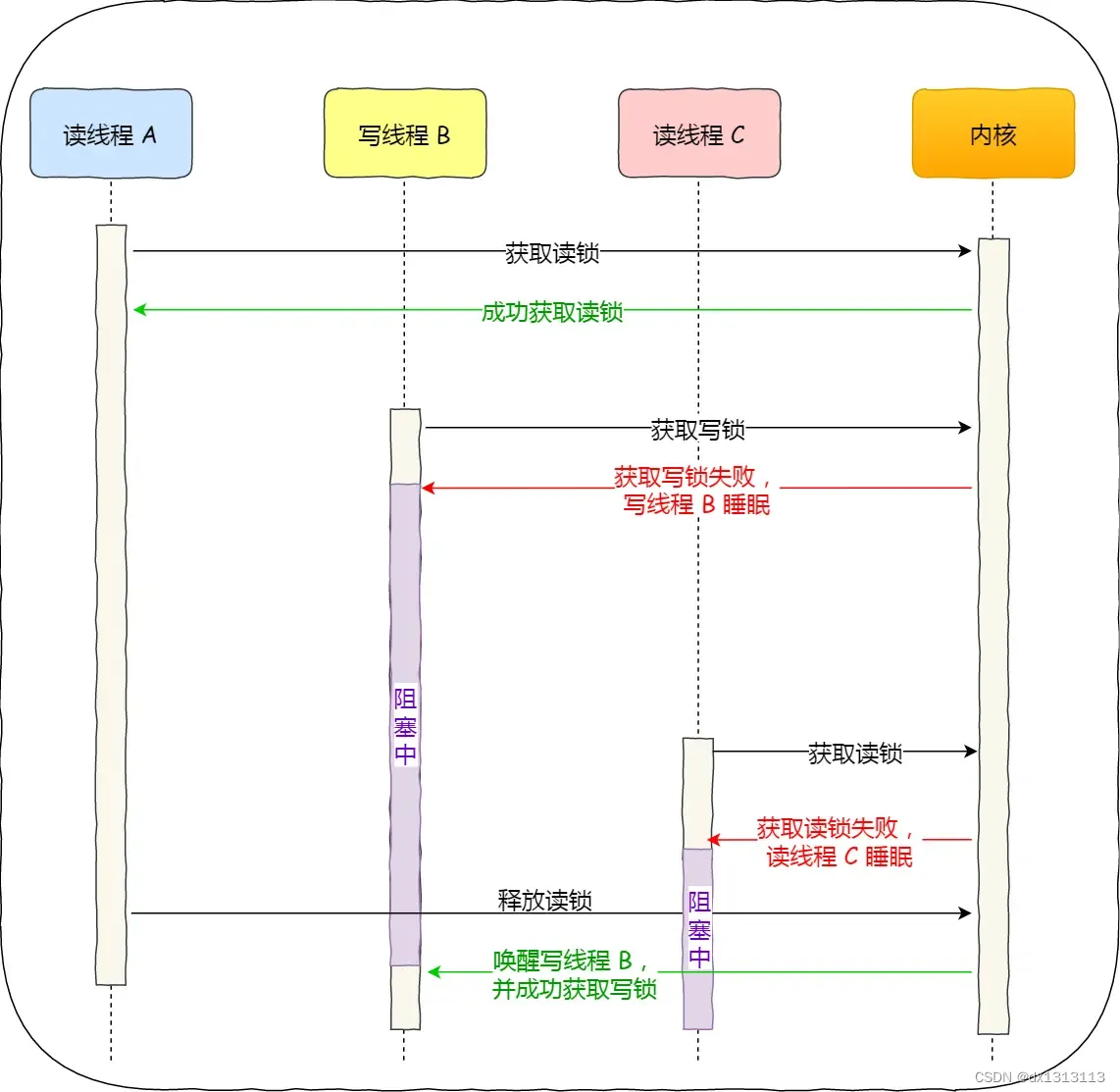

(学习笔记-进程管理)什么是悲观锁、乐观锁?

互斥锁与自旋锁 最底层的两种就是 [互斥锁和自旋锁],有很多高级的锁都是基于它们实现的。可以认为它们是各种锁的地基,所以我们必须清楚它们之间的区别和应用。 加锁的目的就是保证共享资源在任意时间内,只有一个线程访问,这样就…...

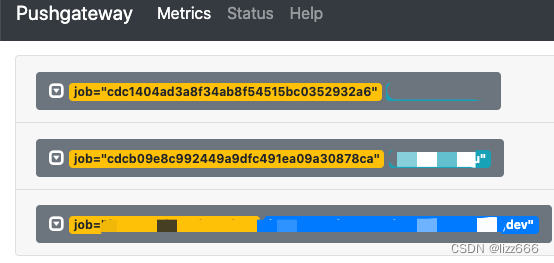

actuator/prometheus使用pushgateway上传jvm监控数据

场景 准备 prometheus已经部署pushgateway服务,访问{pushgateway.server:9091}可以看到面板 实现 基于springboot引入支持组件,版本可以 <!--监控检查--><dependency><groupId>org.springframework.boot</groupId><artifa…...

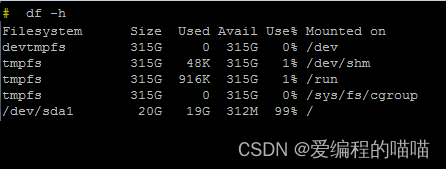

Linux设置临时目录路径的解决方案

大家好,我是爱编程的喵喵。双985硕士毕业,现担任全栈工程师一职,热衷于将数据思维应用到工作与生活中。从事机器学习以及相关的前后端开发工作。曾在阿里云、科大讯飞、CCF等比赛获得多次Top名次。现为CSDN博客专家、人工智能领域优质创作者。喜欢通过博客创作的方式对所学的…...

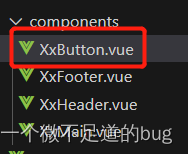

19-普通组件的注册使用

普通组件的注册使用-局部注册 一. 组件注册的两种方式:1.局部注册:只能在注册的组件内使用 (1) 创建 vue 文件(单文件组件) (2) 在使用的组件内导入,并注册 components:{ 组件名: 组件对象 } // 导入需要注册的组件 import 组件对象 from.vue文件路径 import HmHeader from ./…...

Java基础篇:抽象类与接口

1、抽象类和接口的定义: (1)抽象类主要用来抽取子类的通用特性,作为子类的模板,它不能被实例化,只能被用作为子类的超类。 (2)接口是抽象方法的集合,声明了一系列的方法…...

面对对象编程范式

本文是阅读《设计模式之美》的总结和心得,跳过了书中对面试和工作用处不大或不多的知识点,总结总共分为三章,分别是面对对象编程范式、设计原则和设计模式 现如今,编程范式存在三种,它们分别是面向对象编程、面向过程编…...

“深度学习”学习日记:Tensorflow实现VGG每一个卷积层的可视化

2023.8.19 深度学习的卷积对于初学者是非常抽象,当时在入门学习的时候直接劝退一大班人,还好我坚持了下来。可视化时用到的图片(我们学校的一角!!!)以下展示了一个卷积和一次Relu的变化 作者使…...

146. LRU 缓存

题目描述 请你设计并实现一个满足 LRU (最近最少使用) 缓存 约束的数据结构。 实现 LRUCache 类: LRUCache(int capacity) 以 正整数 作为容量 capacity 初始化 LRU 缓存int get(int key) 如果关键字 key 存在于缓存中,则返回关键字的值,否…...

Unity框架学习--场景切换管理器

活动场景 用脚本实例化的游戏对象都会生成在活动场景中。 哪个场景是活动场景,则当前的天空盒就会使用该场景的天空盒。 只能有一个场景是活动场景。 在Hierarchy右击一个场景,点击“Set Active Scene”可以手动把这个场景设置为活动场景。也可以使用…...

Kotlin Lambda和高阶函数

Lambda和高阶函数 本文链接: 文章目录 Lambda和高阶函数 lambda输出(返回类型)深入探究泛型 inline原理探究 高阶函数集合、泛型自己实现Kotlin内置函数 扩展函数原理companion object 原理 > 静态内部类函数式编程 lambda 1、lambda的由…...

ELKstack-Elasticsearch配置与使用

一. 部署前准备 最小化安装 Centos 7.x/Ubuntu x86_64 操作系统的虚拟机,vcpu 2,内存 4G 或更多, 操作系统盘 50G,主机名设置规则为 es-server-nodeX , 额外添加一块单独的数据磁盘 大小为 50G 并格式化挂载到/data/e…...

conda相比python好处

Conda 作为 Python 的环境和包管理工具,相比原生 Python 生态(如 pip 虚拟环境)有许多独特优势,尤其在多项目管理、依赖处理和跨平台兼容性等方面表现更优。以下是 Conda 的核心好处: 一、一站式环境管理:…...

OpenLayers 可视化之热力图

注:当前使用的是 ol 5.3.0 版本,天地图使用的key请到天地图官网申请,并替换为自己的key 热力图(Heatmap)又叫热点图,是一种通过特殊高亮显示事物密度分布、变化趋势的数据可视化技术。采用颜色的深浅来显示…...

基于大模型的 UI 自动化系统

基于大模型的 UI 自动化系统 下面是一个完整的 Python 系统,利用大模型实现智能 UI 自动化,结合计算机视觉和自然语言处理技术,实现"看屏操作"的能力。 系统架构设计 #mermaid-svg-2gn2GRvh5WCP2ktF {font-family:"trebuchet ms",verdana,arial,sans-…...

8k长序列建模,蛋白质语言模型Prot42仅利用目标蛋白序列即可生成高亲和力结合剂

蛋白质结合剂(如抗体、抑制肽)在疾病诊断、成像分析及靶向药物递送等关键场景中发挥着不可替代的作用。传统上,高特异性蛋白质结合剂的开发高度依赖噬菌体展示、定向进化等实验技术,但这类方法普遍面临资源消耗巨大、研发周期冗长…...

五年级数学知识边界总结思考-下册

目录 一、背景二、过程1.观察物体小学五年级下册“观察物体”知识点详解:由来、作用与意义**一、知识点核心内容****二、知识点的由来:从生活实践到数学抽象****三、知识的作用:解决实际问题的工具****四、学习的意义:培养核心素养…...

基于数字孪生的水厂可视化平台建设:架构与实践

分享大纲: 1、数字孪生水厂可视化平台建设背景 2、数字孪生水厂可视化平台建设架构 3、数字孪生水厂可视化平台建设成效 近几年,数字孪生水厂的建设开展的如火如荼。作为提升水厂管理效率、优化资源的调度手段,基于数字孪生的水厂可视化平台的…...

【git】把本地更改提交远程新分支feature_g

创建并切换新分支 git checkout -b feature_g 添加并提交更改 git add . git commit -m “实现图片上传功能” 推送到远程 git push -u origin feature_g...

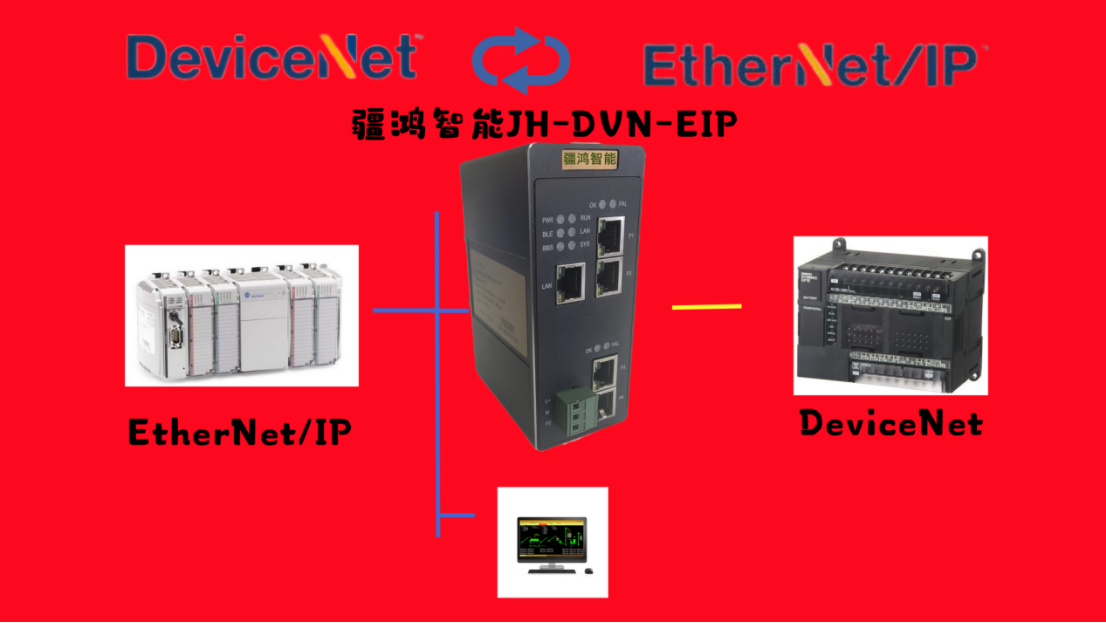

EtherNet/IP转DeviceNet协议网关详解

一,设备主要功能 疆鸿智能JH-DVN-EIP本产品是自主研发的一款EtherNet/IP从站功能的通讯网关。该产品主要功能是连接DeviceNet总线和EtherNet/IP网络,本网关连接到EtherNet/IP总线中做为从站使用,连接到DeviceNet总线中做为从站使用。 在自动…...

CRMEB 框架中 PHP 上传扩展开发:涵盖本地上传及阿里云 OSS、腾讯云 COS、七牛云

目前已有本地上传、阿里云OSS上传、腾讯云COS上传、七牛云上传扩展 扩展入口文件 文件目录 crmeb\services\upload\Upload.php namespace crmeb\services\upload;use crmeb\basic\BaseManager; use think\facade\Config;/*** Class Upload* package crmeb\services\upload* …...

Unit 1 深度强化学习简介

Deep RL Course ——Unit 1 Introduction 从理论和实践层面深入学习深度强化学习。学会使用知名的深度强化学习库,例如 Stable Baselines3、RL Baselines3 Zoo、Sample Factory 和 CleanRL。在独特的环境中训练智能体,比如 SnowballFight、Huggy the Do…...