BL808学习日志-2-LVGL for M0 and D0

一、lvgl测试环境

对拿到的M1S_DOCK开发板进行开发板测试,博流的官方SDK是支持M0和D0两个内核都进行测试的;但是目前只实现了M0的LVGLBenchmark,测试D0内核中发现很多莫名其妙的问题。一会详细记录。

使用的是开发板自带的SPI显示屏,280*240分辨率。

二、M0内核lvgl测试

使用官方默认的SDK进行编译会报错缓存不够,按照下列方式修改SDK中的.ld内存分布文件

/bouffalo_sdk/bsp/board/bl808dk/bl808_flash_m0.ld文件。主要目的就是修改ram_memory的大小,把ram_wifi的大小暂时调整为0,因为目前官方SDK无法启用无线功能。如果测试过程中卡住,就是ram_memory太小了,缓存不够使用了,调大即可。

/****************************************************************************************

* @file flash.ld

*

* @brief This file is the link script file (gnuarm or armgcc).

*

* Copyright (C) BouffaloLab 2021

*

****************************************************************************************

*//* configure the CPU type */

OUTPUT_ARCH( "riscv" )/* configure the entry point */

ENTRY(__start)StackSize = 0x0400; /* 1KB */

HeapMinSize = 0x1000; /* 4KB */

psram_min_size = 0x1000;__EM_SIZE = DEFINED(btble_controller_init) ? 32K : 0K;MEMORY

{fw_header_memory (rx) : ORIGIN = 0x58000000 - 0x1000, LENGTH = 4Kxip_memory (rx) : ORIGIN = 0x58000000, LENGTH = 32Mram_psram (wxa) : ORIGIN = 0x50000000, LENGTH = 64Mitcm_memory (rx) : ORIGIN = 0x62020000, LENGTH = 32Kdtcm_memory (rx) : ORIGIN = 0x62028000, LENGTH = 16Knocache_ram_memory (!rx) : ORIGIN = 0x2202C000, LENGTH = 16Kram_memory (!rx) : ORIGIN = 0x62038000, LENGTH = 128Kram_wifi (wxa) : ORIGIN = 0x22058000, LENGTH = 0Kxram_memory (!rx) : ORIGIN = 0x40000000, LENGTH = 16K

}SECTIONS

{.fw_header :{KEEP(*(.fw_header))} > fw_header_memory.init :{KEEP (*(SORT_NONE(.init)))KEEP (*(SORT_NONE(.vector)))} > xip_memory.text :{. = ALIGN(4);__text_code_start__ = .;*(.text)*(.text.*)/* section information for shell */. = ALIGN(4);__fsymtab_start = .;KEEP(*(FSymTab))__fsymtab_end = .;. = ALIGN(4);__vsymtab_start = .;KEEP(*(VSymTab))__vsymtab_end = .;/* section information for usb usbh_class_info */. = ALIGN(4);__usbh_class_info_start__ = .;KEEP(*(.usbh_class_info)). = ALIGN(4);__usbh_class_info_end__ = .;/*put .rodata**/*(EXCLUDE_FILE( *bl808_glb*.o* \*bl808_glb_gpio*.o* \*bl808_pds*.o* \*bl808_aon*.o* \*bl808_hbn*.o* \*bl808_l1c*.o* \*bl808_common*.o* \*bl808_clock*.o* \*bl808_ef_ctrl*.o* \*bl808_sf_cfg*.o* \*bl808_sf_ctrl*.o* \*bl808_sflash*.o* \*bl808_xip_sflash*.o* \*bl808_romapi_patch*.o* ) .rodata*)*(.srodata)*(.srodata.*). = ALIGN(4);__text_code_end__ = .;} > xip_memory. = ALIGN(4);__itcm_load_addr = .;.itcm_region : AT (__itcm_load_addr){. = ALIGN(4);__tcm_code_start__ = .;*(.tcm_code.*)*(.tcm_const.*)*(.sclock_rlt_code.*)*(.sclock_rlt_const.*)*bl808_glb*.o*(.rodata*)*bl808_glb_gpio*.o*(.rodata*)*bl808_pds*.o*(.rodata*)*bl808_aon*.o*(.rodata*)*bl808_hbn*.o*(.rodata*)*bl808_l1c*.o*(.rodata*)*bl808_common*.o*(.rodata*)*bl808_clock*.o*(.rodata*)*bl808_ef_ctrl*.o*(.rodata*)*bl808_sf_cfg*.o*(.rodata*)*bl808_sf_ctrl*.o*(.rodata*)*bl808_sflash*.o*(.rodata*)*bl808_xip_sflash*.o*(.rodata*)*bl808_romapi_patch*.o*(.rodata*). = ALIGN(4);__tcm_code_end__ = .;} > itcm_memory__dtcm_load_addr = __itcm_load_addr + SIZEOF(.itcm_region);.dtcm_region : AT (__dtcm_load_addr){. = ALIGN(4);__tcm_data_start__ = .;*(.tcm_data)/* *finger_print.o(.data*) */. = ALIGN(4);__tcm_data_end__ = .;} > dtcm_memory/*************************************************************************//* .stack_dummy section doesn't contains any symbols. It is only* used for linker to calculate size of stack sections, and assign* values to stack symbols later */.stack_dummy (NOLOAD):{. = ALIGN(0x4);. = . + StackSize;. = ALIGN(0x4);} > dtcm_memory/* Set stack top to end of RAM, and stack limit move down by* size of stack_dummy section */__StackTop = ORIGIN(dtcm_memory) + LENGTH(dtcm_memory);PROVIDE( __freertos_irq_stack_top = __StackTop);__StackLimit = __StackTop - SIZEOF(.stack_dummy);/* Check if data + heap + stack exceeds RAM limit */ASSERT(__StackLimit >= __tcm_data_end__, "region RAM overflowed with stack")/*************************************************************************/__nocache_ram_load_addr = __dtcm_load_addr + SIZEOF(.dtcm_region);.nocache_ram_region : AT (__nocache_ram_load_addr){. = ALIGN(4);__nocache_ram_data_start__ = .;*(.nocache_ram). = ALIGN(4);__nocache_ram_data_end__ = .;} > nocache_ram_memory__ram_load_addr = __nocache_ram_load_addr + SIZEOF(.nocache_ram_region);/* Data section */RAM_DATA : AT (__ram_load_addr){. = ALIGN(4);__ram_data_start__ = .;PROVIDE( __global_pointer$ = . + 0x800 );*(.data)*(.data.*)*(.sdata)*(.sdata.*)*(.sdata2)*(.sdata2.*). = ALIGN(4);__bflog_tags_start__ = .;*(.bflog_tags_array). = ALIGN(4);__bflog_tags_end__ = .;__ram_data_end__ = .;} > ram_memory__psram_load_addr = (__ram_load_addr + SIZEOF (RAM_DATA));.psram_data_region : AT (__psram_load_addr){. = ALIGN(4);__psram_data_start__ = .;KEEP(*(.psram_data*)). = ALIGN(4);__psram_data_end__ = .;} > ram_psram__etext_final = (__psram_load_addr + SIZEOF (.psram_data_region));ASSERT(__etext_final <= ORIGIN(xip_memory) + LENGTH(xip_memory), "code memory overflow").bss (NOLOAD) :{. = ALIGN(4);__bss_start__ = .;*(.bss*)*(.sbss*)*(COMMON). = ALIGN(4);__bss_end__ = .;} > ram_memory.noinit_data (NOLOAD) :{. = ALIGN(4);__noinit_data_start__ = .;*(.noinit_data*). = ALIGN(4);__noinit_data_end__ = .;} > ram_memory.nocache_noinit_ram_region (NOLOAD) :{. = ALIGN(4);__nocache_noinit_ram_data_start__ = .;*(.nocache_noinit_ram)*(.noncacheable). = ALIGN(4);__nocache_noinit_ram_data_end__ = .;} > nocache_ram_memory.heap (NOLOAD):{. = ALIGN(4);__HeapBase = .;/*__end__ = .;*//*end = __end__;*/KEEP(*(.heap*)). = ALIGN(4);__HeapLimit = .;} > ram_memory__HeapLimit = ORIGIN(ram_memory) + LENGTH(ram_memory);ASSERT(__HeapLimit - __HeapBase >= HeapMinSize, "heap region overflow").psram_noinit_data (NOLOAD):{. = ALIGN(4);__psram_noinit_data_start__ = .;KEEP(*(.psram_noinit*)). = ALIGN(4);__psram_noinit_data_end__ = .;} > ram_psram.psram_heap (NOLOAD):{. = ALIGN(4);__psram_heap_base = .;KEEP(*(.psram_heap*)). = ALIGN(4);__psram_heap_end = .;} > ram_psram__psram_limit = ORIGIN(ram_psram) + LENGTH(ram_psram);ASSERT(__psram_limit - __psram_heap_base >= psram_min_size, "psram heap region overflow").wifibss (NOLOAD) :{PROVIDE( __wifi_bss_start = ADDR(.wifibss) );PROVIDE( __wifi_bss_end = ADDR(.wifibss) + SIZEOF(.wifibss) );*ipc_shared.o(COMMON)*sdu_shared.o(COMMON)*hal_desc.o(COMMON)*txl_buffer_shared.o(COMMON)*txl_frame_shared.o(COMMON)*scan_shared.o(COMMON)*scanu_shared.o(COMMON)*mfp_bip.o(COMMON)*me_mic.o(COMMON)*bl_sta_mgmt_others.o(COMMON)*bl_pmk_mgmt.o(COMMON)*bl_pmk_mgmt_internal.o(COMMON)*libwifi_drv.a:bl_utils.o(COMMON)*libwifi_drv.a:bl_utils.o(.bss*)*(.wifi_ram*). = ALIGN(16);} > ram_wifiPROVIDE(__LD_CONFIG_EM_SEL = __EM_SIZE);

}修改完成后最好把LP内核的内存分布文件也修改一下。这里引申出一个问题,就是内存的分布肯定是LP和M0内核共享OCRAM+WRAM,但是不知道两个内核的itcm_memory 和dtcm_memory的大小是不是要按照规格书改成32K+16K,官方默认的大小是20K+4K,搞不懂是什么用意。而且两个内核的部分区域在官方SDK中竟然重叠了,好奇怪。对于初学者来说,实在是头大,官方也没有任何说明。

这里直接贴图一个成绩。

____ __ __ _ _ _| _ \ / _|/ _| | | | | | || |_) | ___ _ _| |_| |_ __ _| | ___ | | __ _| |__| _ < / _ \| | | | _| _/ _` | |/ _ \| |/ _` | '_ \| |_) | (_) | |_| | | | || (_| | | (_) | | (_| | |_) ||____/ \___/ \__,_|_| |_| \__,_|_|\___/|_|\__,_|_.__/Build:10:29:32,Oct 4 2023

Copyright (c) 2022 Bouffalolab team

======== flash cfg ========

flash size 0x01000000

jedec id 0xEF4018

mid 0xEF

iomode 0x04

clk delay 0x01

clk invert 0x01

read reg cmd0 0x05

read reg cmd1 0x35

write reg cmd0 0x01

write reg cmd1 0x31

qe write len 0x01

cread support 0x00

cread code 0xFF

burst wrap cmd 0x77

===========================

dynamic memory init success,heap size = 86 Kbyte

sig1:ffff32ff

sig2:0000ffff

lvgl case

lvgl success

[LVGL]

LVGL v8.3.7 Benchmark (in csv format)

[LVGL] Weighted FPS: 67

[LVGL] Opa. speed: 97%

[LVGL] Text small,19

[LVGL] Text small + opa,[LVGL] 19

[LVGL] Text medium,19

[LVGL] Text medium + opa,[LVGL] 19

[LVGL] Text large,19

[LVGL] Text large + opa,[LVGL] 19

[LVGL] Text large compressed,16

[LVGL] Substr. shadow,19

[LVGL] Substr. text,15

[LVGL] Rectangle,60

[LVGL] Rectangle + opa,[LVGL] 57

[LVGL] Rectangle rounded,53

[LVGL] Rectangle rounded + opa,[LVGL] 52

[LVGL] Circle,49

[LVGL] Circle + opa,[LVGL] 48

[LVGL] Border,59

[LVGL] Border + opa,[LVGL] 59

[LVGL] Border rounded,52

[LVGL] Border rounded + opa,[LVGL] 52

[LVGL] Circle border,46

[LVGL] Circle border + opa,[LVGL] 46

[LVGL] Border top,54

[LVGL] Border top + opa,[LVGL] 54

[LVGL] Border left,54

[LVGL] Border left + opa,[LVGL] 54

[LVGL] Border top + left,53

[LVGL] Border top + left + opa,[LVGL] 52

[LVGL] Border left + right,53

[LVGL] Border left + right + opa,[LVGL] 52

[LVGL] Border top + bottom,52

[LVGL] Border top + bottom + opa,[LVGL] 53

[LVGL] Shadow small,40

[LVGL] Shadow small + opa,[LVGL] 39

[LVGL] Shadow small offset,35

[LVGL] Shadow small offset + opa,[LVGL] 35

[LVGL] Shadow large,26

[LVGL] Shadow large + opa,[LVGL] 25

[LVGL] Shadow large offset,27

[LVGL] Shadow large offset + opa,[LVGL] 28

[LVGL] Image RGB,170

[LVGL] Image RGB + opa,[LVGL] 180

[LVGL] Image ARGB,161

[LVGL] Image ARGB + opa,[LVGL] 154

[LVGL] Image chorma keyed,165

[LVGL] Image chorma keyed + opa,[LVGL] 164

[LVGL] Image indexed,150

[LVGL] Image indexed + opa,[LVGL] 151

[LVGL] Image alpha only,158

[LVGL] Image alpha only + opa,[LVGL] 150

[LVGL] Image RGB recolor,156

[LVGL] Image RGB recolor + opa,[LVGL] 150

[LVGL] Image ARGB recolor,142

[LVGL] Image ARGB recolor + opa,[LVGL] 141

[LVGL] Image chorma keyed recolor,151

[LVGL] Image chorma keyed recolor + opa,[LVGL] 142

[LVGL] Image indexed recolor,144

[LVGL] Image indexed recolor + opa,[LVGL] 143

[LVGL] Image RGB rotate,118

[LVGL] Image RGB rotate + opa,[LVGL] 118

[LVGL] Image RGB rotate anti aliased,100

[LVGL] Image RGB rotate anti aliased + opa,[LVGL] 96

[LVGL] Image ARGB rotate,114

[LVGL] Image ARGB rotate + opa,[LVGL] 112

[LVGL] Image ARGB rotate anti aliased,86

[LVGL] Image ARGB rotate anti aliased + opa,[LVGL] 86

[LVGL] Image RGB zoom,125

[LVGL] Image RGB zoom + opa,[LVGL] 121

[LVGL] Image RGB zoom anti aliased,108

[LVGL] Image RGB zoom anti aliased + opa,[LVGL] 107

[LVGL] Image ARGB zoom,118

[LVGL] Image ARGB zoom + opa,[LVGL] 120

[LVGL] Image ARGB zoom anti aliased,97

[LVGL] Image ARGB zoom anti aliased + opa,[LVGL] 98

[LVGL] Text small,19

[LVGL] Text small + opa,[LVGL] 19

[LVGL] Text medium,19

[LVGL] Text medium + opa,[LVGL] 19

[LVGL] Text large,19

[LVGL] Text large + opa,[LVGL] 19

[LVGL] Text small compressed,18

[LVGL] Text small compressed + opa,[LVGL] 18

[LVGL] Text medium compressed,17

[LVGL] Text medium compressed + opa,[LVGL] 17

[LVGL] Text large compressed,16

[LVGL] Text large compressed + opa,[LVGL] 16

[LVGL] Line,53

[LVGL] Line + opa,[LVGL] 54

[LVGL] Arc think,44

[LVGL] Arc think + opa,[LVGL] 43

[LVGL] Arc thick,44

[LVGL] Arc thick + opa,[LVGL] 43

[LVGL] Substr. rectangle,36

[LVGL] Substr. rectangle + opa,[LVGL] 36

[LVGL] Substr. border,37

[LVGL] Substr. border + opa,[LVGL] 37

[LVGL] Substr. shadow,19

[LVGL] Substr. shadow + opa,[LVGL] 19

[LVGL] Substr. image,125

[LVGL] Substr. image + opa,[LVGL] 126

[LVGL] Substr. line,33

[LVGL] Substr. line + opa,[LVGL] 33

[LVGL] Substr. arc,42

[LVGL] Substr. arc + opa,[LVGL] 42

[LVGL] Substr. text,15

[LVGL] Substr. text + opa,[LVGL] 15

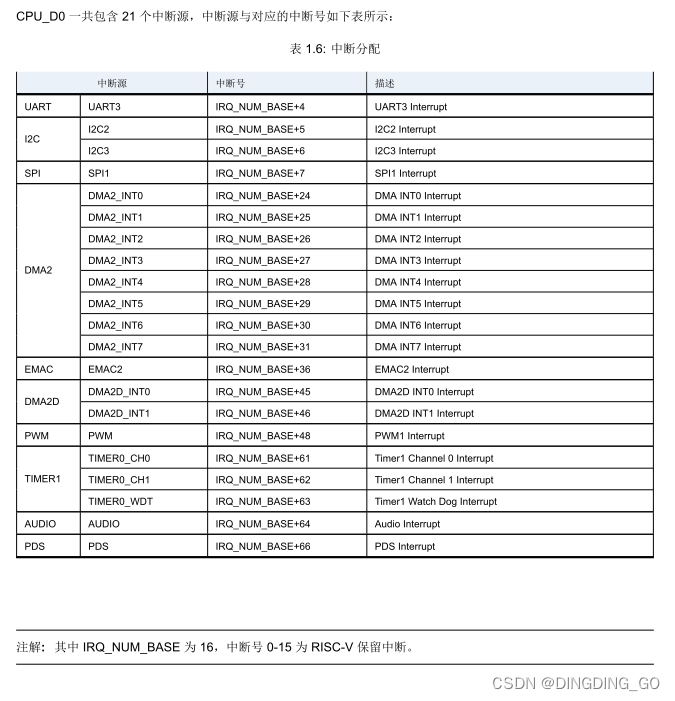

三、D0内核调试挖坑!!!

测试D0内核花费了3天时间也没搞定,总是进入初始化以后,直接就卡屏卡死了。因为在假期,没带DEBUG工具,只能随便打点测试了一下;

1.SPI1无法启用

按照官方SDK进行测试,发现根本没有使用SPI1,而且在lcd_spi_hard_4_init(lcd_spi_hard_4_init_t *dbi_parra)初始化过程中,spi_hd = bflb_device_get_by_name(LCD_SPI_HARD_4_NAME);得到的是spi0。。。

int lcd_spi_hard_4_init(lcd_spi_hard_4_init_t *dbi_parra)

{/* spi */struct bflb_spi_config_s spi_cfg = {.freq = dbi_parra->clock_freq,.role = SPI_ROLE_MASTER,.mode = SPI_MODE3,.data_width = SPI_DATA_WIDTH_8BIT,.bit_order = SPI_BIT_MSB,.byte_order = SPI_BYTE_LSB,.tx_fifo_threshold = 0,.rx_fifo_threshold = 0,};/* dma cfg */struct bflb_dma_channel_config_s dma_spi_tx_cfg = {.direction = DMA_MEMORY_TO_PERIPH,.src_req = DMA_REQUEST_NONE,.dst_req = DMA_REQUEST_SPI0_TX,.src_addr_inc = DMA_ADDR_INCREMENT_ENABLE,.dst_addr_inc = DMA_ADDR_INCREMENT_DISABLE,.src_burst_count = DMA_BURST_INCR4,.dst_burst_count = DMA_BURST_INCR4,.src_width = DMA_DATA_WIDTH_16BIT,.dst_width = DMA_DATA_WIDTH_16BIT,};pixel_format = dbi_parra->pixel_format;#if (SPI_FIFO_WIDTH_VARIABLE_SUPPORT)/* SPI support burst*4 */spi_cfg.tx_fifo_threshold = (2 * 4 - 1);spi_cfg.rx_fifo_threshold = (2 * 4 - 1);spi_cfg.byte_order = SPI_BYTE_MSB;

#elifspi_cfg.tx_fifo_threshold = 4 - 1;spi_cfg.rx_fifo_threshold = 4 - 1;

#endifspi_hd = bflb_device_get_by_name(LCD_SPI_HARD_4_NAME);/* CS and DC pin init */gpio = bflb_device_get_by_name("gpio");bflb_gpio_init(gpio, LCD_SPI_HARD_4_PIN_CS, GPIO_OUTPUT | GPIO_PULLUP | GPIO_SMT_EN | GPIO_DRV_1);bflb_gpio_init(gpio, LCD_SPI_HARD_4_PIN_DC, GPIO_OUTPUT | GPIO_PULLUP | GPIO_SMT_EN | GPIO_DRV_1);LCD_SPI_HARD_4_CS_HIGH;LCD_SPI_HARD_4_DC_HIGH;if (spi_hd->idx == 0) {bflb_gpio_init(gpio, LCD_SPI_HARD_4_PIN_CLK, GPIO_FUNC_SPI0 | GPIO_ALTERNATE | GPIO_PULLUP | GPIO_SMT_EN | GPIO_DRV_2);bflb_gpio_init(gpio, LCD_SPI_HARD_4_PIN_DAT, GPIO_FUNC_SPI0 | GPIO_ALTERNATE | GPIO_PULLUP | GPIO_SMT_EN | GPIO_DRV_2);}

#if defined(GPIO_FUNC_SPI1)else if (spi_hd->idx == 1) {bflb_gpio_init(gpio, LCD_SPI_HARD_4_PIN_CLK, GPIO_FUNC_SPI1 | GPIO_ALTERNATE | GPIO_PULLUP | GPIO_SMT_EN | GPIO_DRV_2);bflb_gpio_init(gpio, LCD_SPI_HARD_4_PIN_DAT, GPIO_FUNC_SPI1 | GPIO_ALTERNATE | GPIO_PULLUP | GPIO_SMT_EN | GPIO_DRV_2);}#endif/* spi init */bflb_spi_init(spi_hd, &spi_cfg);/* spi enabled continuous mode */// bflb_spi_feature_control(spi_hd, SPI_CMD_SET_CS_INTERVAL, true);if (pixel_format == LCD_SPI_LCD_PIXEL_FORMAT_RGB565) {dma_spi_tx_cfg.src_width = DMA_DATA_WIDTH_16BIT;dma_spi_tx_cfg.dst_width = DMA_DATA_WIDTH_16BIT;}if (spi_hd->idx == 0) {dma_spi_tx_cfg.dst_req = DMA_REQUEST_SPI0_TX;spi_tx_fifo_address = DMA_ADDR_SPI0_TDR;}

#if defined(DMA_REQUEST_SPI1_TX)else if (spi_hd->idx == 1) {dma_spi_tx_cfg.dst_req = DMA_REQUEST_SPI1_TX;spi_tx_fifo_address = DMA_ADDR_SPI1_TDR;}

#endif/* dma init */spi_dma_hd = bflb_device_get_by_name(LCD_SPI_HARD_4_DMA_NAME);bflb_dma_channel_init(spi_dma_hd, &dma_spi_tx_cfg);/* dma int cfg */bflb_dma_channel_irq_attach(spi_dma_hd, spi_dma_callback, NULL);return 0;

}按照device_table.c文件中,竟然没有规定spi1..........,也没有规定DMA2的对应0-7个通道,但是却规定了DMA0的0-7个通道,官方datasheet中DMA0和DMA1只有一个通道。8个通道的寄存器基地址都是DMA0_BASE( #define DMA0_BASE ((uint32_t)0x2000c000)),在else这个分支里面竟然中断号都是0XFF,真是被这SDK搞懵了。看这样子好像官方并不想让使用spi1来使用?????这个问题等待后续解决。

{ .name = "spi0",.reg_base = SPI0_BASE,

#if defined(CPU_M0) || defined(CPU_LP).irq_num = BL808_IRQ_SPI0,

#else.irq_num = 0xff,

#endif.idx = 0,.dev_type = BFLB_DEVICE_TYPE_SPI,.user_data = NULL

},{ .name = "dma0_ch0",.reg_base = DMA0_BASE + 1 * DMA_CHANNEL_OFFSET,

#if defined(CPU_M0) || defined(CPU_LP).irq_num = BL808_IRQ_DMA0_ALL,

#else.irq_num = 0xff,

#endif.idx = 0,.sub_idx = 0,.dev_type = BFLB_DEVICE_TYPE_DMA,.user_data = NULL

},

四、引申出来的RAM分配问题

下面贴一下官方的SDK中定义的分配方案,看的我脑袋大,有点看不懂能不能这样使用,或者是这样使用会不会出现冲突。(0x62020000的意思是使用chache访问,和直接访问0x2202000是一个意思,但是nocache_ram_memory区域必须使用0x22034000直接访问,不能使用cache访问)。

1.M0的ram_memory区域,ram_memory (!rx) : ORIGIN = 0x6202A000, LENGTH = 24K,也就是0x2202A000-0x2203000,但是LP内核的itcm_memory (rx) : ORIGIN = 0x2202C000, LENGTH = 16K,也就是0x2202C000-0x2203000;

2.LP内核区域的dtcm_memory (rx) : ORIGIN = 0x22030000, LENGTH = 16K和M0内核的ram_wifi (wxa) : ORIGIN = 0x22030000, LENGTH = 160K - __EM_SIZE冲突,虽然LP内核内部没有cache功能,但是也好奇怪为什么还会划分idata和ddata这两个区域。

3.我自己曾经尝试过按照不冲突的RAM地址升序顺序和严格按照手册所写的itcm和dtcm大小进行内存划分,没有发现明显区别,coremark和lvgl都没有任何提升。看看后续如何理解这个问题和解决问题。

LP-MEMORY

{fw_header_memory (rx) : ORIGIN = 0x58020000 - 0x1000, LENGTH = 4Kxip_memory (rx) : ORIGIN = 0x58020000, LENGTH = 1Mitcm_memory (rx) : ORIGIN = 0x2202C000, LENGTH = 16Kdtcm_memory (rx) : ORIGIN = 0x22030000, LENGTH = 16Knocache_ram_memory (!rx) : ORIGIN = 0x22030000, LENGTH = 0Kram_memory (!rx) : ORIGIN = 0x22034000, LENGTH = 16Kxram_memory (!rx) : ORIGIN = 0x40000000, LENGTH = 16K

}M0-MEMORY

{fw_header_memory (rx) : ORIGIN = 0x58000000 - 0x1000, LENGTH = 4Kxip_memory (rx) : ORIGIN = 0x58000000, LENGTH = 32Mram_psram (wxa) : ORIGIN = 0x50000000, LENGTH = 64Mitcm_memory (rx) : ORIGIN = 0x62020000, LENGTH = 20Kdtcm_memory (rx) : ORIGIN = 0x62025000, LENGTH = 4Knocache_ram_memory (!rx) : ORIGIN = 0x22026000, LENGTH = 16Kram_memory (!rx) : ORIGIN = 0x6202A000, LENGTH = 24Kram_wifi (wxa) : ORIGIN = 0x22030000, LENGTH = 160K - __EM_SIZExram_memory (!rx) : ORIGIN = 0x40000000, LENGTH = 16K

}D0-MEMORY

{fw_header_memory (rx) : ORIGIN = 0x58000000 - 0x1000, LENGTH = 4Kxip_memory (rx) : ORIGIN = 0x58000000, LENGTH = 32Mitcm_memory (rx) : ORIGIN = 0x3eff0000, LENGTH = 28Kdtcm_memory (rx) : ORIGIN = 0x3eff7000, LENGTH = 4Knocache_ram_memory (!rx) : ORIGIN = 0x3eff8000, LENGTH = 0Kram_memory (!rx) : ORIGIN = 0x3eff8000, LENGTH = 32K + 32Kxram_memory (!rx) : ORIGIN = 0x40004000, LENGTH = 16K

}还是希望官方能够多给点文档看啊,linux下的M1S_DOCK_SDK好像就有很多正常的功能寄存器,还有库文件,我看文件抬头都是博流写的,真的是无语了。

后续还是在Linux下使用M1S_DOCK_SDK开发吧,官方的库我实在是搞不懂。浪费精力。

相关文章:

BL808学习日志-2-LVGL for M0 and D0

一、lvgl测试环境 对拿到的M1S_DOCK开发板进行开发板测试,博流的官方SDK是支持M0和D0两个内核都进行测试的;但是目前只实现了M0的LVGLBenchmark,测试D0内核中发现很多莫名其妙的问题。一会详细记录。 使用的是开发板自带的SPI显示屏ÿ…...

treectrl类封装 2023/8/13 下午4:07:35

2023/8/13 下午4:07:35 treectrl类封装 2023/8/13 下午4:07:53 TreeCtrl 类是一个常用的图形用户界面控件,用于实现树形结构的展示和交互。以下是一个简单的 TreeCtrl 类的封装示例: python import wxclass MyTreeCtrl(wx.TreeCtrl):def __init__(self, parent):super()…...

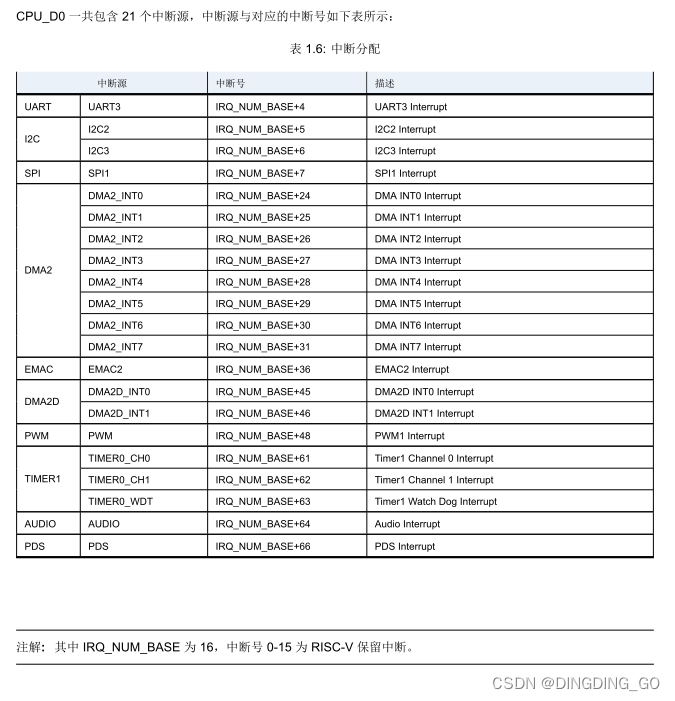

Android学习之路(20) 进程间通信

IPC IPC为 (Inter-Process Communication) 缩写,称为进程间通信或跨进程通信,指两个进程间进行数据交换的过程。安卓中主要采用 Binder 进行进程间通信,当然也支持其他 IPC 方式,如:管道,Socket࿰…...

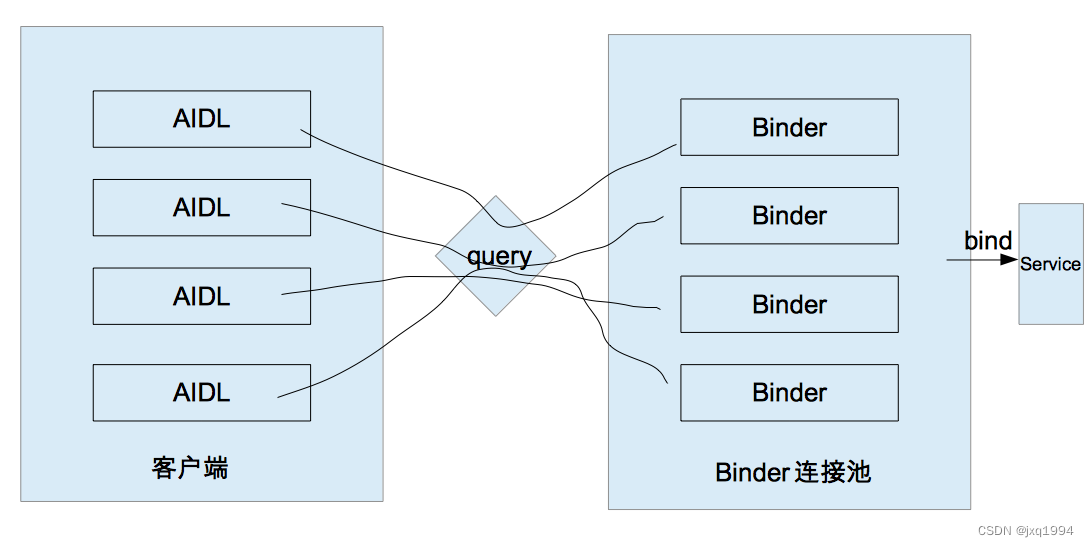

机器学习——KNN算法流程详解(以iris为例)

、 目 录 前情说明 问题陈述 数据说明 KNN算法流程概述 代码实现 运行结果 基于可视化的改进 可视化代码 全部数据可视化总览 分类投票结果 改进后最终代码 前情说明 本书基于《特征工程入门与入门与实践》庄家盛 译版P53页K最近邻(KNN)算…...

国庆假期day5

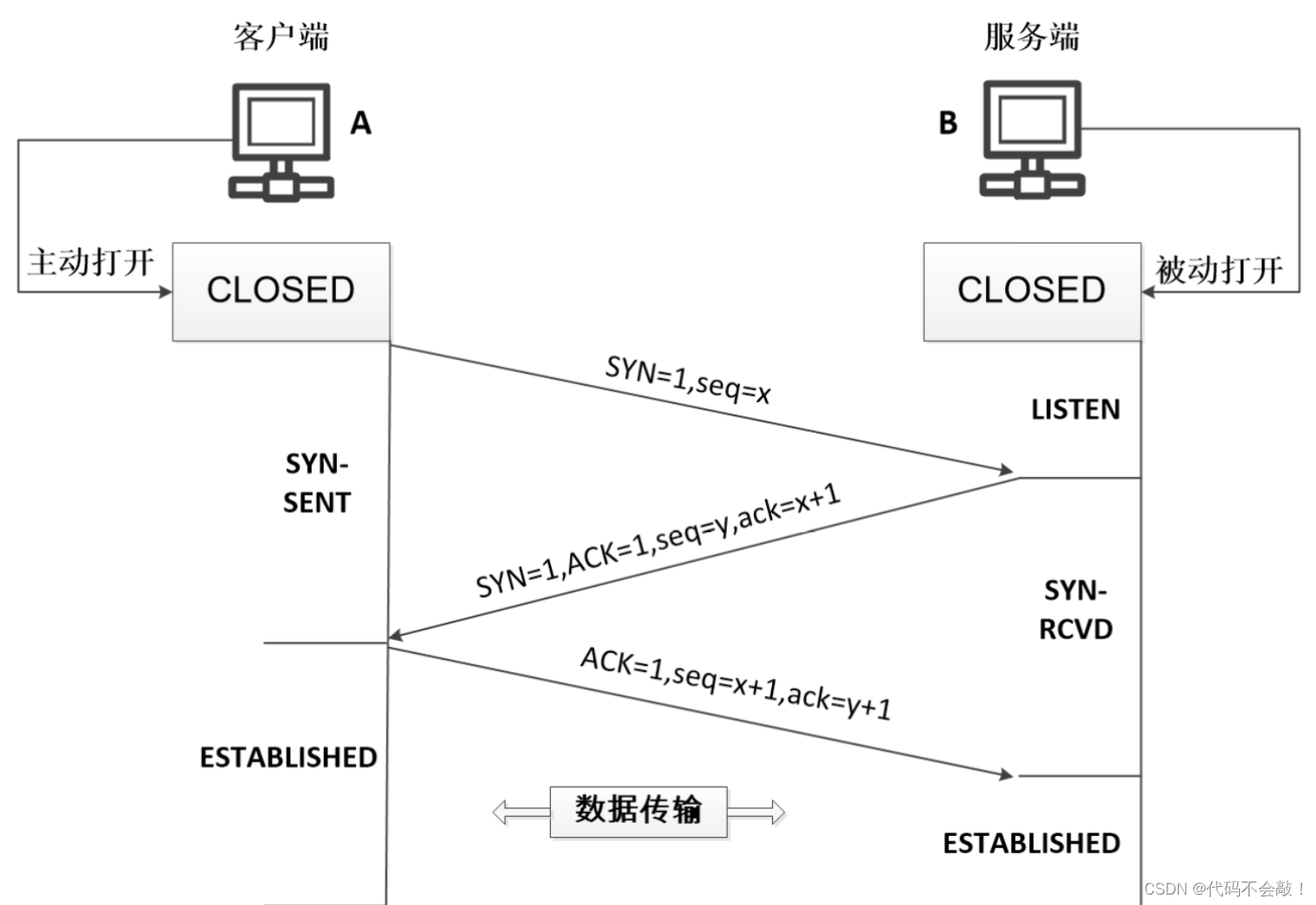

作业:请写出七层模型及每一层的功能,请绘制三次握手四次挥手的流程图 1.OSI七层模型: 应用层--------提供函 表示层--------表密缩 会话层--------会话 传输层--------进程的接收和发送 网络层--------寻主机 数据链路层----相邻节点的可靠传…...

ES6中的let、const

let ES6中新增了let命令,用来声明变量,和var类似但是也有一定的区别 1. 块级作用域 只能在当前作用域内使用,各个作用域不能互相使用,否则会报错。 {let a 1;var b 1; } console.log(a); // 会报错 console.log(b); // 1为什…...

Python 列表操作指南3

示例,将新列表中的所有值设置为 ‘hello’: newlist [hello for x in fruits]表达式还可以包含条件,不像筛选器那样,而是作为操纵结果的一种方式: 示例,返回 “orange” 而不是 “banana”: …...

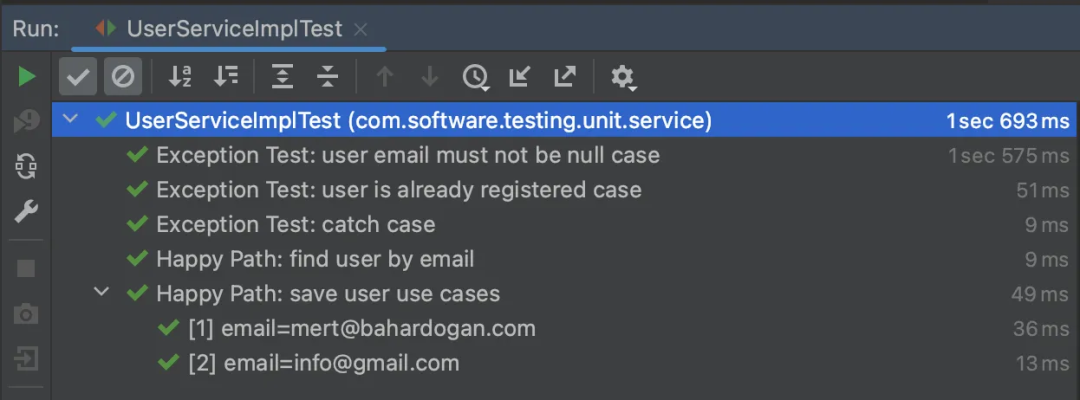

三个要点,掌握Spring Boot单元测试

单元测试是软件开发中不可或缺的重要环节,它用于验证软件中最小可测试单元的准确性。结合运用Spring Boot、JUnit、Mockito和分层架构,开发人员可以更便捷地编写可靠、可测试且高质量的单元测试代码,确保软件的正确性和质量。 一、介绍 本文…...

【nginx】Nginx配置:

文章目录 一、什么是Nginx:二、为什么使用Nginx:三、如何处理请求:四、什么是正向代理和反向代理:五、nginx 启动和关闭:六、目录结构:七、配置文件nginx.conf:八、location:九、单页…...

CSS3与HTML5

box-sizing content-box:默认,宽高包不含边框和内边距 border-box:也叫怪异盒子,宽高包含边框和内边距 动画:移动translate,旋转、transform等等 走马灯:利用动画实现animation:from…...

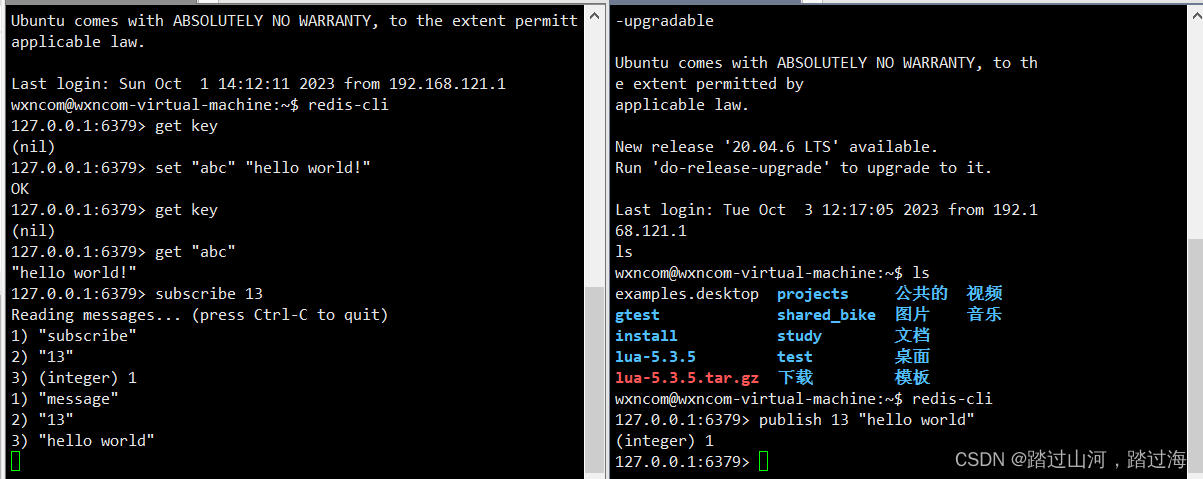

redis的简单使用

文章目录 环境安装与配置redis发布-订阅相关命令redis发布-订阅的客户端编程redis的订阅发布的例子 环境安装与配置 sudo apt-get install redis-server # ubuntu命令安装redis服务ubuntu通过上面命令安装完redis,会自动启动redis服务,通过ps命令确认&a…...

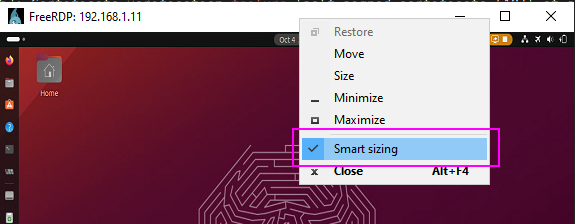

Windows下启动freeRDP并自适应远端桌面大小

几个二进制文件 xfreerdp # Linux下的,an X11 Remote Desktop Protocol (RDP) client which is part of the FreeRDP project wfreerdp.exe # Windows下的,freerdp2.0 主程序,freerdp3.0将废弃 sdl-freerdp.exe # Windows下的&…...

ES6中的数值扩展

1. 二进制和八进制的表示法 二进制和八进制的前缀分别为0b(或0B)和0o(或0O)表示 在ES5的严格模式下,八进制不再允许使用前缀0表示 如果要将0b和0x前缀的字符串数值转为十进制,要使用Number方法 Number(0b111); // 7 Number(0o10); // 82. Number.isF…...

自定义注解实现Redis分布式锁、手动控制事务和根据异常名字或内容限流的三合一的功能

自定义注解实现Redis分布式锁、手动控制事务和根据异常名字或内容限流的三合一的功能 文章目录 [toc] 1.依赖2.Redisson配置2.1单机模式配置2.2主从模式2.3集群模式2.4哨兵模式 3.实现3.1 RedisConfig3.2 自定义注解IdempotentManualCtrlTransLimiterAnno3.3自定义切面Idempote…...

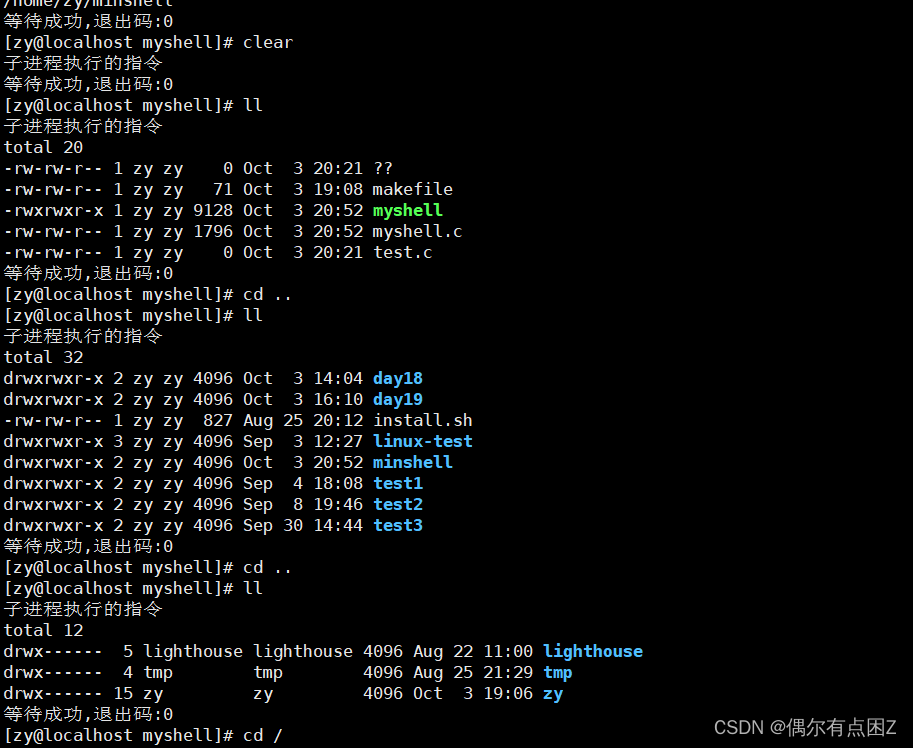

Linux:minishell

目录 1.实现逻辑 2.代码及效果展示 1.打印字符串提示用户输入指令 2.父进程拆解指令 3.子进程执行指令,父进程等待结果 4.效果 3.实现过程中遇到的问题 1.打印字符串的时候不显示 2.多换了一行 3.cd路径无效 4.优化 1.ll指令 2.给文件或目录加上颜色 代码链接 模…...

STM32驱动步进电机

前言 (1)本章介绍用stm32驱动42步进电机,将介绍需要准备的硬件器材、所需芯片资源以及怎么编程及源代码等等。 (2)实验效果:按下按键,步进电机顺时针或逆时针旋转90度。 (3ÿ…...

计算机视觉——飞桨深度学习实战-深度学习网络模型

深度学习网络模型的整体架构主要数据集、模型组网以及学习优化过程三部分,本章主要围绕着深度学习网络模型的算法架构、常见模型展开了详细介绍,从经典的深度学习网络模型以CNN、RNN为代表,到为了解决显存不足、实时性不够等问题的轻量化网络…...

实现手撸神经网咯230901)

用c动态数组(不用c++vector)实现手撸神经网咯230901

用c语言动态数组(不用c++的vector)实现:输入数据inputs = { {1, 1}, {0,0},{1, 0},{0,1} };目标数据targets={0,0,1,1}; 测试数据 inputs22 = { {1, 0}, {1,1},{0,1} }; 构建神经网络,例如:NeuralNetwork nn({ 2, 4,3,1 }); 则网络有四层、输入层2个nodes、输出层1个节点、第…...

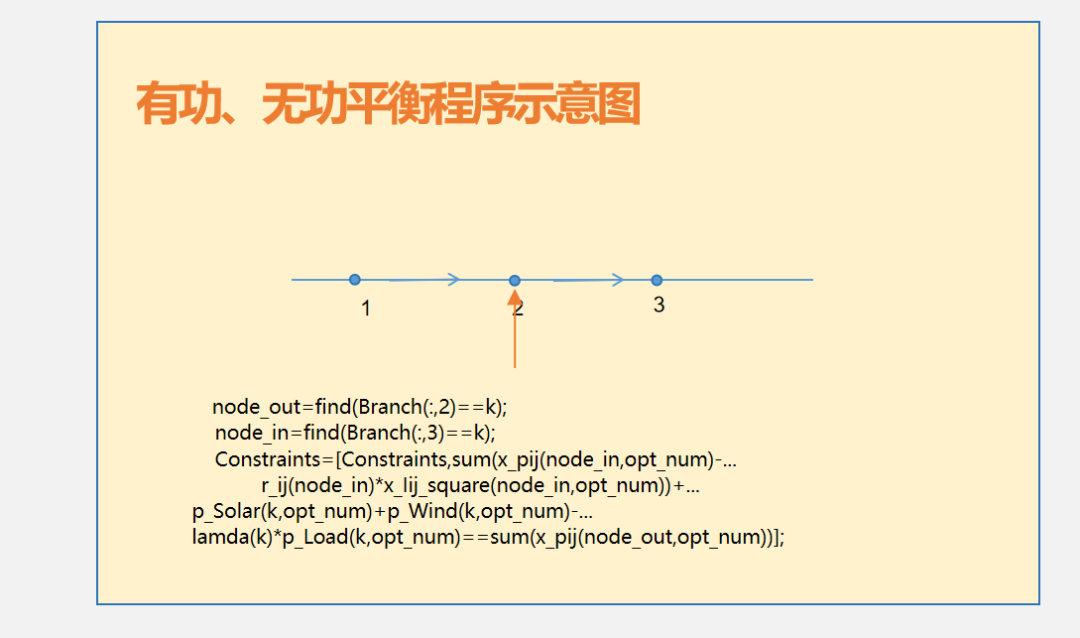

视频讲解|基于DistFlow潮流的配电网故障重构代码

目录 1 主要内容 2 视频链接 1 主要内容 该视频为基于DistFlow潮流的配电网故障重构代码讲解内容,对应的资源下载链接为基于DistFlow潮流的配电网故障重构(输入任意线路),对该程序进行了详尽的讲解,基本做到句句分析和讲解(讲解…...

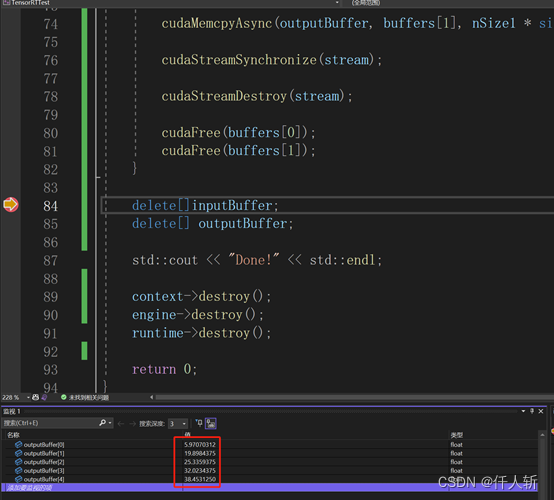

Ultralytics(YoloV8)开发环境配置,训练,模型转换,部署全流程测试记录

关键词:windows docker tensorRT Ultralytics YoloV8 配置开发环境的方法: 1.Windows的虚拟机上配置: Python3.10 使用Ultralytics 可以得到pt onnx,但无法转为engine,找不到GPU,手动转也不行࿰…...

)

浏览器访问 AWS ECS 上部署的 Docker 容器(监听 80 端口)

✅ 一、ECS 服务配置 Dockerfile 确保监听 80 端口 EXPOSE 80 CMD ["nginx", "-g", "daemon off;"]或 EXPOSE 80 CMD ["python3", "-m", "http.server", "80"]任务定义(Task Definition&…...

ubuntu搭建nfs服务centos挂载访问

在Ubuntu上设置NFS服务器 在Ubuntu上,你可以使用apt包管理器来安装NFS服务器。打开终端并运行: sudo apt update sudo apt install nfs-kernel-server创建共享目录 创建一个目录用于共享,例如/shared: sudo mkdir /shared sud…...

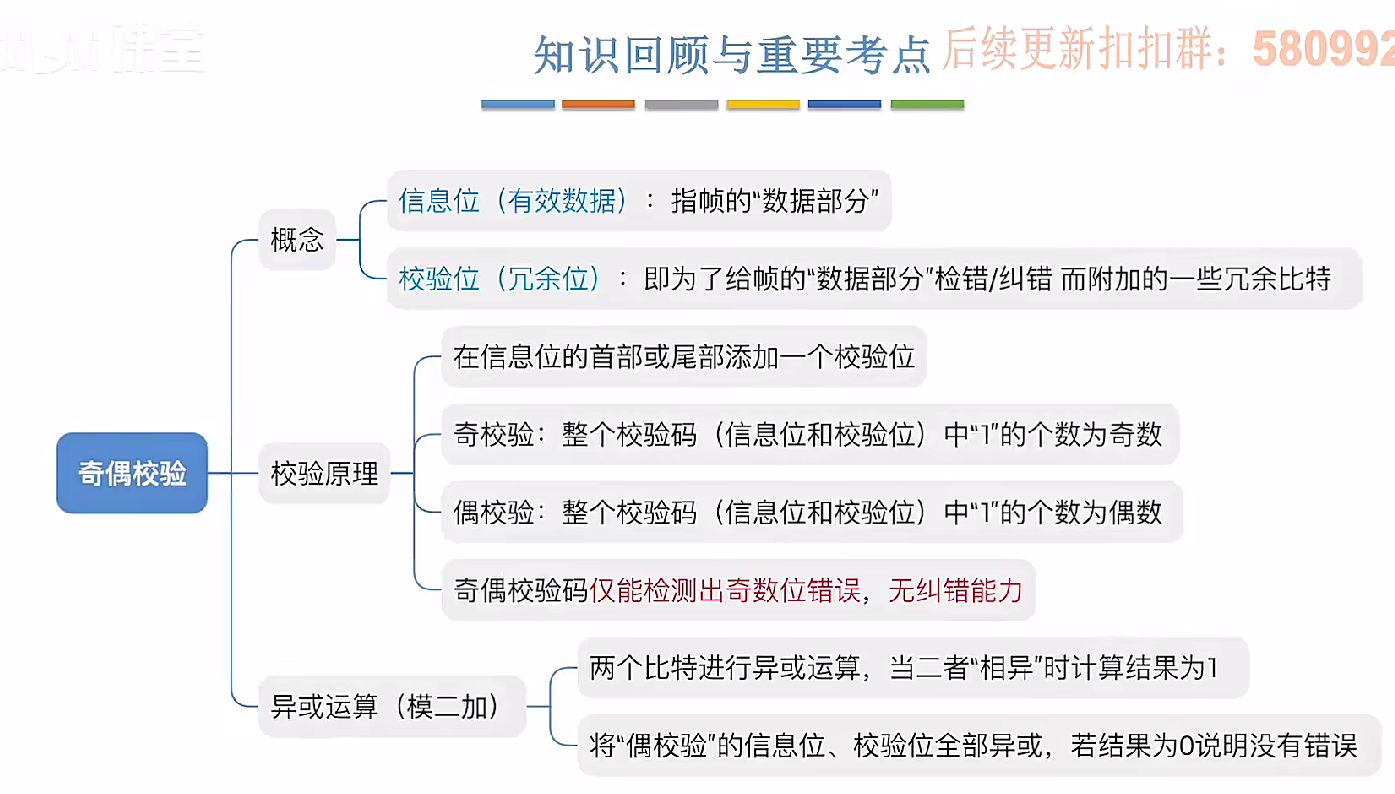

3.3.1_1 检错编码(奇偶校验码)

从这节课开始,我们会探讨数据链路层的差错控制功能,差错控制功能的主要目标是要发现并且解决一个帧内部的位错误,我们需要使用特殊的编码技术去发现帧内部的位错误,当我们发现位错误之后,通常来说有两种解决方案。第一…...

Python爬虫实战:研究feedparser库相关技术

1. 引言 1.1 研究背景与意义 在当今信息爆炸的时代,互联网上存在着海量的信息资源。RSS(Really Simple Syndication)作为一种标准化的信息聚合技术,被广泛用于网站内容的发布和订阅。通过 RSS,用户可以方便地获取网站更新的内容,而无需频繁访问各个网站。 然而,互联网…...

【网络安全产品大调研系列】2. 体验漏洞扫描

前言 2023 年漏洞扫描服务市场规模预计为 3.06(十亿美元)。漏洞扫描服务市场行业预计将从 2024 年的 3.48(十亿美元)增长到 2032 年的 9.54(十亿美元)。预测期内漏洞扫描服务市场 CAGR(增长率&…...

【AI学习】三、AI算法中的向量

在人工智能(AI)算法中,向量(Vector)是一种将现实世界中的数据(如图像、文本、音频等)转化为计算机可处理的数值型特征表示的工具。它是连接人类认知(如语义、视觉特征)与…...

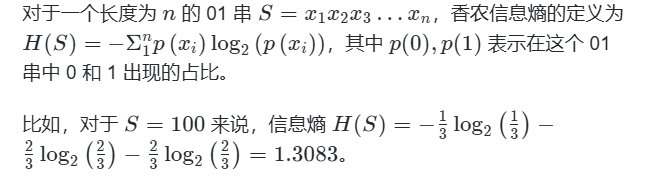

蓝桥杯3498 01串的熵

问题描述 对于一个长度为 23333333的 01 串, 如果其信息熵为 11625907.5798, 且 0 出现次数比 1 少, 那么这个 01 串中 0 出现了多少次? #include<iostream> #include<cmath> using namespace std;int n 23333333;int main() {//枚举 0 出现的次数//因…...

Mac下Android Studio扫描根目录卡死问题记录

环境信息 操作系统: macOS 15.5 (Apple M2芯片)Android Studio版本: Meerkat Feature Drop | 2024.3.2 Patch 1 (Build #AI-243.26053.27.2432.13536105, 2025年5月22日构建) 问题现象 在项目开发过程中,提示一个依赖外部头文件的cpp源文件需要同步,点…...

Go 语言并发编程基础:无缓冲与有缓冲通道

在上一章节中,我们了解了 Channel 的基本用法。本章将重点分析 Go 中通道的两种类型 —— 无缓冲通道与有缓冲通道,它们在并发编程中各具特点和应用场景。 一、通道的基本分类 类型定义形式特点无缓冲通道make(chan T)发送和接收都必须准备好࿰…...

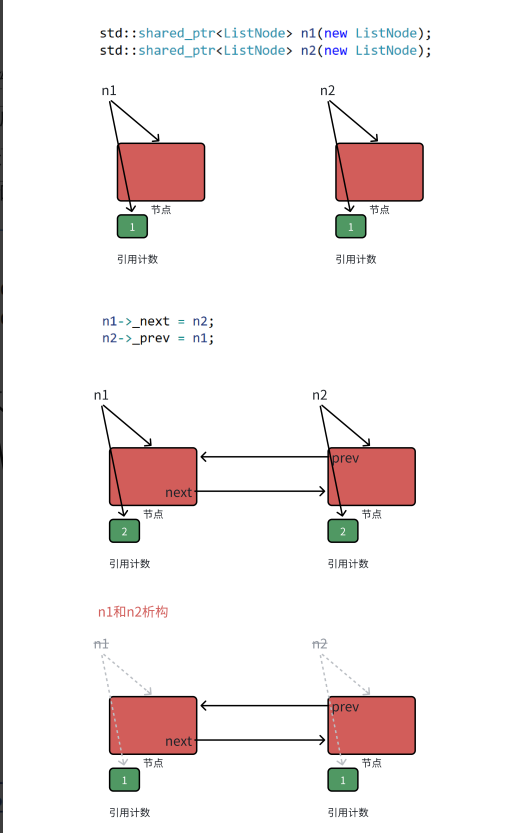

【C++进阶篇】智能指针

C内存管理终极指南:智能指针从入门到源码剖析 一. 智能指针1.1 auto_ptr1.2 unique_ptr1.3 shared_ptr1.4 make_shared 二. 原理三. shared_ptr循环引用问题三. 线程安全问题四. 内存泄漏4.1 什么是内存泄漏4.2 危害4.3 避免内存泄漏 五. 最后 一. 智能指针 智能指…...