06 分频器设计

分频器简介

实现分频一般有两种方法,一种方法是直接使用 PLL 进行分频,比如在 FPGA 或者 ASIC 设计中,都可以直接使用 PLL 进行分频。但是这种分频有时候受限于 PLL 本身的特性,无法得到频率很低的时钟信号,比如输入 100Mhz 时钟,很多PLL 都无法得到 1Mhz 以下的时钟信号。另外一种方法是直接使用 Verilog 代码来实现分频。

注意:

使用 Verilog 代码分频得到的时钟信号尽量不要当做其他模块的输入时钟信号,因为通过 Verilog 代码分频得到的时钟信号默认不会连接到 FPGA 的时钟网络上,这样会导致时钟出现偏移和抖动,在高频电路中会影响电路稳定性,这种分频方式一般用于产生外部低速总线的参考时钟,如SPI、I2C的参考时钟。

偶数分频器和奇数分频器

根据分频器的分频比例是偶数还是奇数,可以将其分为偶数分频器和奇数分频器。

- 偶数分频:就是分频前的频率和分频后的频率比值是偶数,比如一个 50Mhz 的晶振时钟,进行二分频后,就是 50Mhz/2=25Mhz

- 奇数分频:就是分配前的频率和分频后的频率比值是奇数。比如一个 50Mhz 的晶振时钟,进行三分频后,就是 50Mhz/3=16.667Mhz

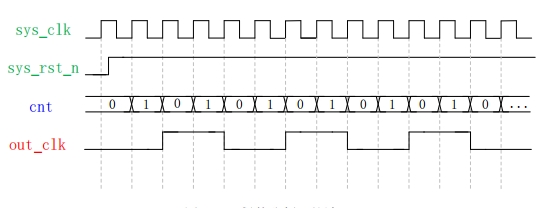

偶数分频实现

假设 N(N为偶数)分频,只需计数到 N/2-1,然后时钟翻转、计数器清零,如此循环就可以得到 N 分频。举个例子,比如晶振时钟是 100Mhz 时钟,想得到一个 25Mhz 的时钟,那么这个是一个 100/25=4 的四分频设计,按照我们刚说的计数到 4/2-1=1,然后时钟翻转、计数器清零,就可以得到一个 25Mhz 的时钟。

偶数分频 Verilog 代码

`timescale 1ns / 1psmodule divider4(input sys_clk,input sys_rst_n,output reg out_clk

);//分频计数器

reg [2:0] count;//分频计数器,按分频比/2-1进行计数

always @(posedge sys_clk) beginif(!sys_rst_n)count <= 2'd0;else if(count < 2'd1)count <= count + 2'd1;elsecount <= 2'd0;

end//翻转输出时钟

always @(posedge sys_clk) beginif(!sys_rst_n)out_clk<= 1'b0;else if(count == 2'd1)out_clk <= ~out_clk;

endendmodule

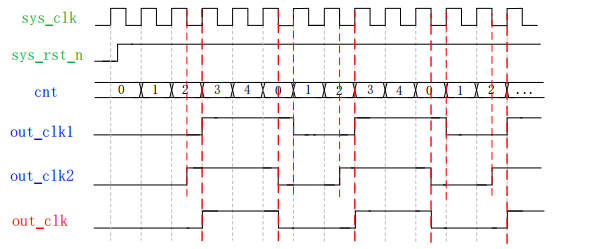

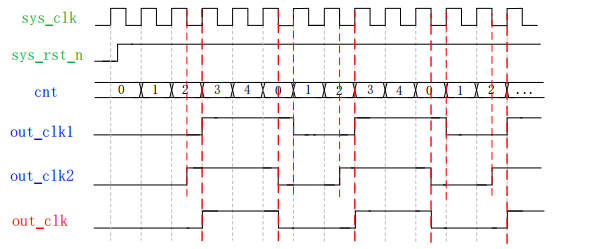

奇数分频器实现

同样假设 N(N为奇数)分频,计数器需要计数到 N-1,当计数器为0时输出时钟1在输入时钟的上升沿拉低,当计数器计数到 N/2 取整时输出时钟1在输入时钟的上升沿进行拉高,同时当计数器为0时输出时钟2在输入时钟的下降沿拉低,当计数器计数到 N/2 取整时输出时钟2在输入时钟的下降沿进行拉高,将输出时钟1和输出时钟2相与即可得到真正的输出时钟。

奇数分频 Verilog 代码

`timescale 1ns / 1psmodule divider5(input sys_clk,input sys_rst_n,output out_clk

);//分频计数器

reg [2:0] count;

//上升沿跳变的中间时钟

reg out_clk1;

//下降沿跳变的中间时钟

reg out_clk2;//分频计数器,按分频比-1进行计数

always @(posedge sys_clk) beginif(!sys_rst_n)count <= 3'd0;else if(count < 3'd4)count <= count + 3'd1;elsecount <= 3'd0;

end//输出时钟1

always @(posedge sys_clk) beginif(!sys_rst_n)out_clk1 <= 1'b0;else if(count == 3'd0)out_clk1 <= 1'b0;else if(count == 3'd2)out_clk1 <= 1'b1;

end//输出时钟2

always @(negedge sys_clk) beginif(!sys_rst_n)out_clk2 <= 1'b0;else if(count == 3'd0)out_clk2 <= 1'b0;else if(count == 3'd2)out_clk2 <= 1'b1;

end//输出分频后的时钟

assign out_clk = out_clk1 & out_clk2;endmodule

任意分频器实现

在实现任意分频器时可以利用条件生成语句,当模块例化时传入的参数为偶数则生成偶数分频的代码,否则生成奇数分频的代码,有关生成语句相关的内容参考03 Verilog HDL 语法。

任意分频 Verilog 代码

`timescale 1ns / 1psmodule divider #(//参数列表parameter COUNT_WIDTH = 3, //内部分频计数器宽度parameter DIV = 5 //分频系数

)

(input sys_clk,input sys_rst_n,output reg out_clk

);//分频计数器

reg [COUNT_WIDTH-1:0] count;generateif((DIV % 2) == 0) begin//偶数分频//按分频比/2-1进行计数always @(posedge sys_clk) beginif(!sys_rst_n)count <= 0;else if(count < (DIV / 2 -1))count <= count + 1;elsecount <= 0;end//翻转输出时钟always @(posedge sys_clk) beginif(!sys_rst_n)out_clk <= 1'b0;else if(count == (DIV / 2 -1))out_clk <= ~out_clk;endendelse begin//奇数分频//上升沿跳变的中间时钟reg out_clk1;//下降沿跳变的中间时钟reg out_clk2;//按分频比-1进行计数always @(posedge sys_clk) beginif(!sys_rst_n)count <= 0;else if(count < (DIV -1))count <= count + 1;elsecount <= 0;end//输出时钟1always @(posedge sys_clk) beginif(!sys_rst_n)out_clk1 <= 1'b0;else if(count == 0)out_clk1 <= 1'b0;else if(count == (DIV / 2))out_clk1 <= 1'b1;end//输出时钟2always @(negedge sys_clk) beginif(!sys_rst_n)out_clk2 <= 1'b0;else if(count == 0)out_clk2 <= 1'b0;else if(count == (DIV / 2))out_clk2 <= 1'b1;end//输出分频后的时钟always @(*) beginout_clk = out_clk1 & out_clk2;endend

endgenerateendmodule

相关文章:

06 分频器设计

分频器简介 实现分频一般有两种方法,一种方法是直接使用 PLL 进行分频,比如在 FPGA 或者 ASIC 设计中,都可以直接使用 PLL 进行分频。但是这种分频有时候受限于 PLL 本身的特性,无法得到频率很低的时钟信号,比如输入 …...

力扣hot100题解(python版7-9题)

7、接雨水 给定 n 个非负整数表示每个宽度为 1 的柱子的高度图,计算按此排列的柱子,下雨之后能接多少雨水。 示例 1: 输入:height [0,1,0,2,1,0,1,3,2,1,2,1] 输出:6 解释:上面是由数组 [0,1,0,2,1,0,1,…...

迭代器 与 生成器)

ECMAScript 6+ 新特性 ( 四 ) 迭代器 与 生成器

2.14.迭代器 2.14.1.for…of for...of 是 JavaScript ES6 引入的一种新的循环结构,,用于遍历可迭代对象(Iterable objects)的每个元素。 它可以自动调用目标对象的迭代器接口,并按顺序逐个访问集合中的每个值。 它…...

【MySQL】事务的一致性究竟怎么理解?

众所周知,事务有四大特性:原子性、一致性、隔离性、持久性,除了一致性,其他三类特性都很好理解。而关于一致性的解释有点让人头疼,我查了很多文章,大多类似:事务的执行必须使数据库处于一致状态…...

证件照(兼容H5,APP,小程序)

证件照由uniappuyui开发完成,并同时兼容H5、App、微信小程序、支付宝小程序,其他端暂未测试。 先看部分效果图吧具体可以下方复制链接体验demo 首页代码 <template><view class""><view class"uy-m-x-30 uy-m-b-20"…...

pytorch-textregression,中文文本回归实践,支持多值输出

pytorch-textregression,中文文本回归实践,支持多值输出 pytorch-textregression是一个以pytorch和transformers为基础,专注于中文文本回归的轻量级自然语言处理工具,支持多值回归等。 目录 数据使用方式paper参考 项目地址 py…...

go语言学而思【持续更新】

问题:在Go语言中nil是什么意思? 答:在Go语言中,nil是一个预声明的标识符,用于表示某些类型的零值。它可以被用作以下类型的零值: 指针(Pointer)切片(Slice)…...

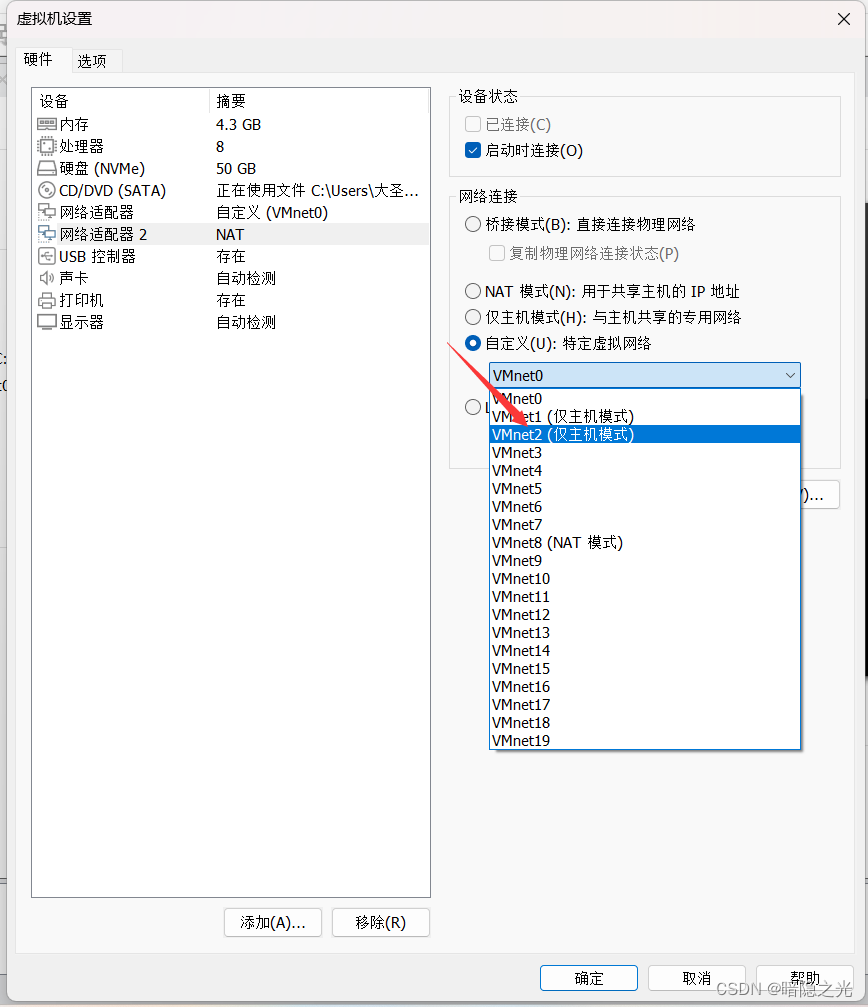

LVS-NAT之VMNET环境搭建

目录 搭建拓扑图 搭建规划 VMNET0 搭建 VMNET2 搭建 LVS端增加网卡 搭建拓扑图: 搭建规划: CLIENT(servera): VMNET0 LVS(serverb): VMNET0 VMNET2 WEB1(serverd): VMNET2 WEB2(servere): VMNET2 VMNE…...

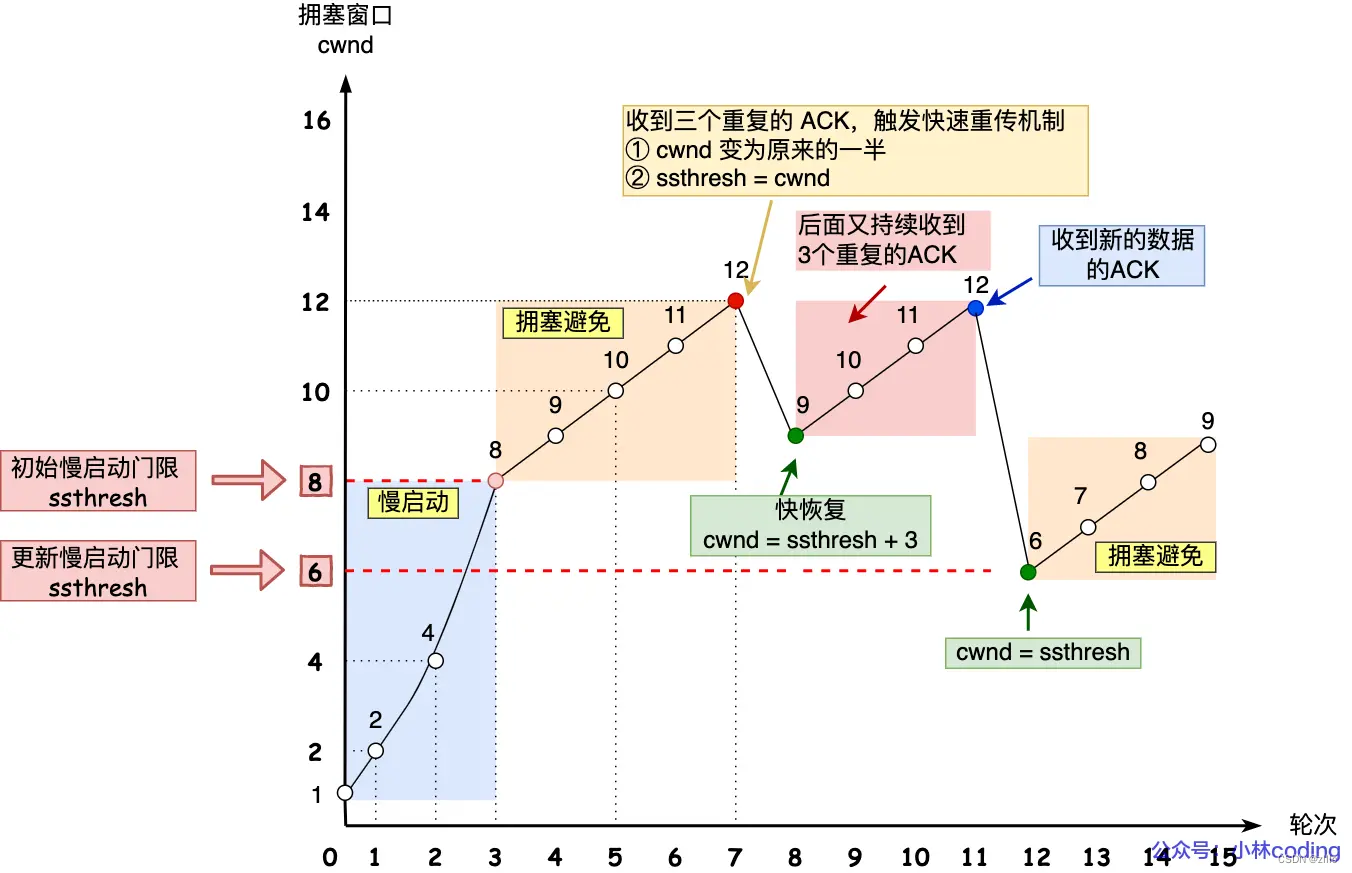

[TCP] TCP/IP 基础知识词典(2)

我想统计一下,TCP/IP 尤其是TCP协议,能搜到的常见的问题,整理起来,关键词添加在目录中,便于以后查阅。 目前预计整理共3篇: [TCP] TCP/IP 基础知识问答 :基础知识 [TCP] TCP/IP 基础知识问答&…...

【牛牛送书 | 第四期】《高效使用Redis:一书学透数据存储与高可用集群》带你快速学习使用Redis

前言: 当今互联网技术日新月异,随着数据量的爆炸式增长,如何高效地存储和管理数据成为了每个公司都必须面对的挑战。与此同时,用户对于应用程序的响应速度和稳定性要求也越来越高。在这个背景下,Redis 作为一个…...

Threejs 实现3D影像地图,Json地图,地图下钻

1.使用threejs实现3D影像地图效果,整体效果看起来还可以,底层抽象了基类,实现了通用,对任意省份,城市都可以只替换数据,即可轻松实现效果。 效果如下: 链接https://www.bilibili.com/video/BV1…...

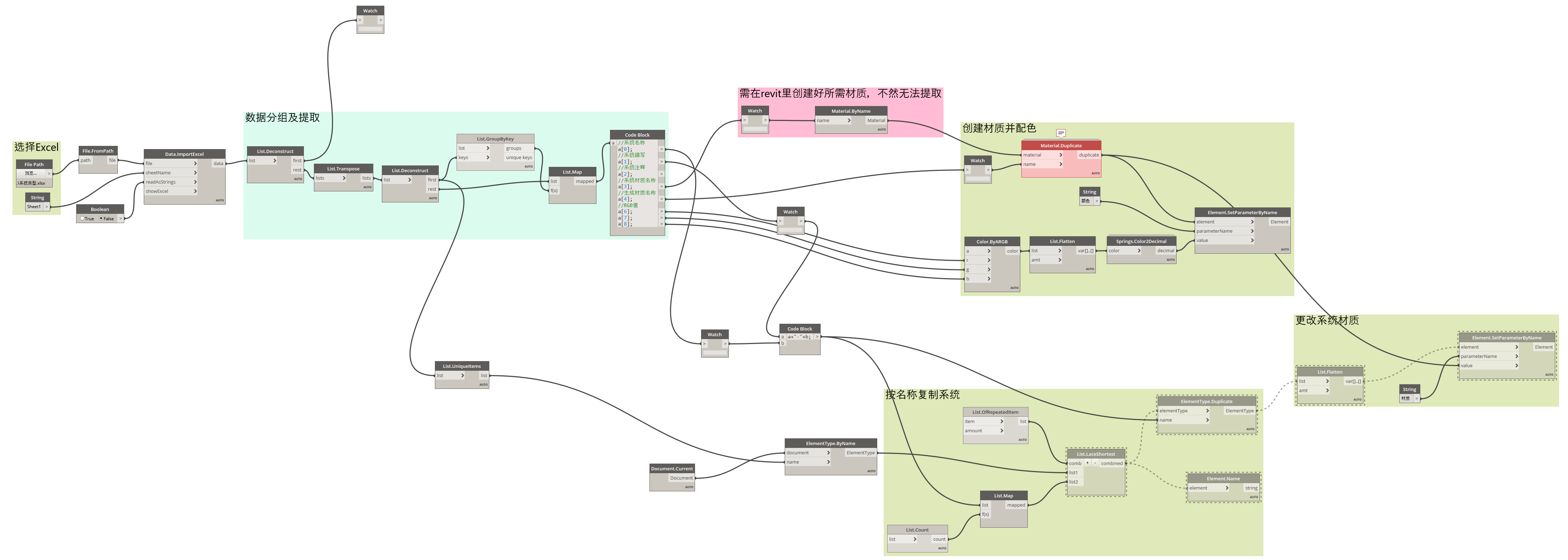

根据Excel创建管道系统及材质

之前看过程鑫老师的文章,介绍过根据Excel数据创建管道系统,但是有小伙伴问过我,照着他这个做,没成功,于是呢,我就想试下,结果发现也没成功。 然后我逐个节点过了一遍,发现可能是因为…...

第八篇【传奇开心果系列】python的文本和语音相互转换库技术点案例示例:Google Text-to-Speech虚拟现实(VR)沉浸式体验经典案例

传奇开心果博文系列 系列博文目录python的文本和语音相互转换库技术点案例示例系列 博文目录前言一、雏形示例代码二、扩展思路介绍三、虚拟导游示例代码四、交互式学习示例代码五、虚拟角色对话示例代码六、辅助用户界面示例代码七、实时语音交互示例代码八、多语言支持示例代…...

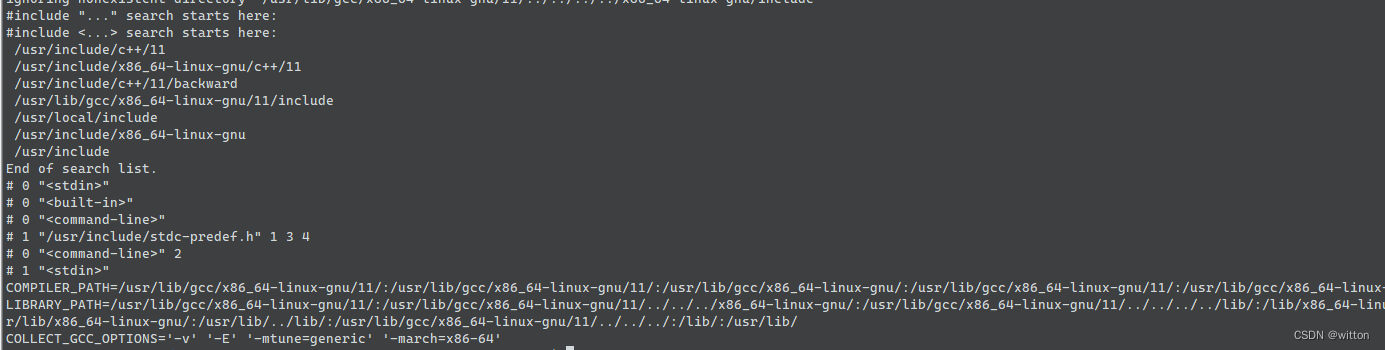

ubuntu使用LLVM官方发布的tar.xz来安装Clang编译器

ubuntu系统上的软件相比CentOS更新还是比较快的,但是还是难免有一些软件更新得不那么快,比如LLVM Clang编译器,目前ubuntu 22.04版本最高还只能安装LLVM 15,而LLVM 18 rc版本都出来了。参见https://github.com/llvm/llvm-project/…...

Windows 远程控制 Mac 电脑怎么操作

要从 Windows 远程控制 Mac 电脑,您可以使用内置 macOS 功能或第三方软件解决方案。以下是一些方法: 一、使用内置 macOS 功能(屏幕共享) 1、在 macOS 上启用屏幕共享 转至系统偏好设置 > 共享;选中“屏幕共享”…...

c# HttpCookie操作,建立cookie工具类

HttpCookie 是一个在.NET Framework中用于管理和操作HTTP Cookie的类。它提供了一种方便的方式来创建、设置、读取和删除Cookie。 Cookie是一种在客户端和服务器之间传递数据的机制,用于跟踪用户的会话状态和存储用户相关的信息。它通常由服务器发送给客户端&#…...

【这个词(Sequence-to-Sequence)在深度学习中怎么解释,有什么作用?】

🚀 作者 :“码上有前” 🚀 文章简介 :深度学习笔记 🚀 欢迎小伙伴们 点赞👍、收藏⭐、留言💬 Sequence-to-Sequence(Seq2Seq) Sequence-to-Sequence(Seq2Seq…...

挑战30天学完Python:Day16 日期时间

📘 Day 16 🎉 本系列为Python基础学习,原稿来源于 30-Days-Of-Python 英文项目,大奇主要是对其本地化翻译、逐条验证和补充,想通过30天完成正儿八经的系统化实践。此系列适合零基础同学,或仅了解Python一点…...

Web3之光:揭秘数字创新的未来

随着数字化时代的深入发展,Web3正以其独特的技术和理念,为我们打开数字创新的崭新视角。作为数字化时代的新兴力量,Web3将深刻影响着我们的生活、工作和社会。本文将揭秘Web3的奥秘,探讨其在数字创新领域的前景和潜力。 1. 重新定…...

Stable Diffusio——采样方法使用与原理详解

简介 当使用稳定扩散(Stable Diffusion)技术生成图像时,首先会生成一张带有噪声的图像。然后,通过一系列步骤逐渐去除图像中的噪声,这个过程类似于从一块毛坯的白色大理石开始,经过多日的精细雕刻…...

智能在线客服平台:数字化时代企业连接用户的 AI 中枢

随着互联网技术的飞速发展,消费者期望能够随时随地与企业进行交流。在线客服平台作为连接企业与客户的重要桥梁,不仅优化了客户体验,还提升了企业的服务效率和市场竞争力。本文将探讨在线客服平台的重要性、技术进展、实际应用,并…...

)

postgresql|数据库|只读用户的创建和删除(备忘)

CREATE USER read_only WITH PASSWORD 密码 -- 连接到xxx数据库 \c xxx -- 授予对xxx数据库的只读权限 GRANT CONNECT ON DATABASE xxx TO read_only; GRANT USAGE ON SCHEMA public TO read_only; GRANT SELECT ON ALL TABLES IN SCHEMA public TO read_only; GRANT EXECUTE O…...

dify打造数据可视化图表

一、概述 在日常工作和学习中,我们经常需要和数据打交道。无论是分析报告、项目展示,还是简单的数据洞察,一个清晰直观的图表,往往能胜过千言万语。 一款能让数据可视化变得超级简单的 MCP Server,由蚂蚁集团 AntV 团队…...

Linux --进程控制

本文从以下五个方面来初步认识进程控制: 目录 进程创建 进程终止 进程等待 进程替换 模拟实现一个微型shell 进程创建 在Linux系统中我们可以在一个进程使用系统调用fork()来创建子进程,创建出来的进程就是子进程,原来的进程为父进程。…...

docker 部署发现spring.profiles.active 问题

报错: org.springframework.boot.context.config.InvalidConfigDataPropertyException: Property spring.profiles.active imported from location class path resource [application-test.yml] is invalid in a profile specific resource [origin: class path re…...

Go语言多线程问题

打印零与奇偶数(leetcode 1116) 方法1:使用互斥锁和条件变量 package mainimport ("fmt""sync" )type ZeroEvenOdd struct {n intzeroMutex sync.MutexevenMutex sync.MutexoddMutex sync.Mutexcurrent int…...

HubSpot推出与ChatGPT的深度集成引发兴奋与担忧

上周三,HubSpot宣布已构建与ChatGPT的深度集成,这一消息在HubSpot用户和营销技术观察者中引发了极大的兴奋,但同时也存在一些关于数据安全的担忧。 许多网络声音声称,这对SaaS应用程序和人工智能而言是一场范式转变。 但向任何技…...

vue3 daterange正则踩坑

<el-form-item label"空置时间" prop"vacantTime"> <el-date-picker v-model"form.vacantTime" type"daterange" start-placeholder"开始日期" end-placeholder"结束日期" clearable :editable"fal…...

Python 高效图像帧提取与视频编码:实战指南

Python 高效图像帧提取与视频编码:实战指南 在音视频处理领域,图像帧提取与视频编码是基础但极具挑战性的任务。Python 结合强大的第三方库(如 OpenCV、FFmpeg、PyAV),可以高效处理视频流,实现快速帧提取、压缩编码等关键功能。本文将深入介绍如何优化这些流程,提高处理…...

之(六) ——通用对象池总结(核心))

怎么开发一个网络协议模块(C语言框架)之(六) ——通用对象池总结(核心)

+---------------------------+ | operEntryTbl[] | ← 操作对象池 (对象数组) +---------------------------+ | 0 | 1 | 2 | ... | N-1 | +---------------------------+↓ 初始化时全部加入 +------------------------+ +-------------------------+ | …...