【005_音频开发_基础篇_ALSA_Codec_驱动-MA120x0P功放】

005_音频开发_基础篇_ALSA_Codec_驱动-MA120x0P功放

文章目录

- 005_音频开发_基础篇_ALSA_Codec_驱动-MA120x0P功放

- 创作背景

- MA120X0P

- 输出模式

- BTL

- SE

- PBTL

- SE+BTL

- 硬件配置方式/硬件

- Limiter限幅器

- 限幅器作用过程

- 主要寄存器

- 操作指令

- `ma120x0p.c`

- `ma120x0p.h`

创作背景

学历代表过去、能力代表现在、学习力代表将来。 一个良好的学习方法是通过输出来倒逼自己输入。写博客既是对过去零散知识点的总结和复盘,也是参加了 零声教育 写博客活动。

零声教育体验课:https://xxetb.xetslk.com/s/3fbO81

本文是开发过程中的知识点总结,供大家学习交流使用,如有任何错误或不足之处,请在评论区指出。

MA120X0P

输出模式

| 输出模式 | 描述 |

|---|---|

| 桥接负载/BTL | Bridge Tied Load |

| 单端/SE | Single Ended |

| 并联桥接负载/PBTL | Parallel Bridge Tied Load |

| 混合模式 | SE+BTL = 单端模式/SE + 桥接负载/BTL |

BTL

SE

PBTL

SE+BTL

硬件配置方式/硬件

| MSEL0 | MSEL1 | 配置 |

|---|---|---|

| 0 | 0 | 并联桥接负载/PBTL (1 channel) |

| 0 | 1 | 桥接负载/BTL (1 channel) + 单端负载/SE (2 channel) |

| 1 | 0 | 桥接负载/BTL (2 channel) |

| 1 | 1 | 单端模式/SE (4 channel) |

Limiter限幅器

-

图中上面表示限幅器“attack”和“release”的变化过程

-

下面表示增益收到“attack”和“relase”的变化过程。

-

限幅器斜率(slew-rate)有限,输出信号有时可能会超过设定的阈值。

限幅器作用过程

当限幅器在活跃状态后恢复增益到单位增益时,增益增加的速度受到释放时间常数的限制。

- 超过阈值,进入限幅状态(Attack过程)

- 减小增益,减小的过程会播放超过阈值的音频,直到较小到阈值

- 增益减小到阈值的速度可以通过寄存器设置attack时间“慢速”、“正常”和“快速”

- 音频增益正常,退出限幅状态(Release过程)

- 增加增益,直到变为音频正常增益

- 增益增加到正常速度可以通过寄存器设置release时间“慢速”、“正常”和“快速”

主要寄存器

-

电源模式

- 0x00

-

软裁剪/Soft-clipping & 过流保护

- 0x0A

-

I2S 格式配置

- 0x35(bit[2:0])

- I2S 模式

- 左对齐/Left justified

- 右对齐/Right justifed(16/18/20/24bits)

- 0x36(bit[5:0])

- 0x35(bit[2:0])

-

VLP控制寄存器

- 0x35, 0x36

-

Volume控制

- 0x40-0x48

操作指令

-

查看I2C总线

i2cdetect -l

-

查看寄存器

i2cdump -y -f 3 0x20- 总线地址为3,从机地址为0x20

-

设置寄存器 0x0A

i2cset -y -f 3 0x20 0x0A 0x80

-

设置寄存器 0x1D

i2cset -y -f 3 0x20 0x1D 0x02

-

设置寄存器 0x26

i2cset -y -f 3 0x20 0x26 0x04

-

设置寄存器I2S模式 0x35

i2cset -y -f 3 0x20 0x35 0x58

-

设置寄存器Umute

i2cset -y -f 3 0x20 0x36 0x41

-

设置寄存器 Volume

i2cset -y -f 3 0x20 0x40 0x4C

ma120x0p.c

// SPDX-License-Identifier: GPL-2.0-or-later

/** ASoC Driver for Infineon Merus(TM) MA120x0p multi-level class-D amplifier** Authors: Ariel Muszkat <ariel.muszkat@gmail.com>* Jorgen Kragh Jakobsen <jorgen.kraghjakobsen@infineon.com>* Nicolai Dyre Bülow <nixen.dyre@gmail.com> ** Copyright (C) 2022 Infineon Technologies AG**/

#include <linux/module.h>

#include <linux/moduleparam.h>

#include <linux/init.h>

#include <linux/delay.h>

#include <linux/pm_runtime.h>

#include <linux/i2c.h>

#include <linux/of_device.h>

#include <linux/spi/spi.h>

#include <linux/regmap.h>

#include <linux/regulator/consumer.h>

#include <linux/slab.h>

#include <linux/gpio/consumer.h>

#include <linux/gpio.h>

#include <sound/core.h>

#include <sound/pcm.h>

#include <sound/pcm_params.h>

#include <sound/soc.h>

#include <sound/soc-dapm.h>

#include <sound/initval.h>

#include <sound/tlv.h>

#include <linux/interrupt.h>#include <linux/kernel.h>

#include <linux/string.h>

#include <linux/fs.h>

#include <linux/uaccess.h>#include "ma120x0p.h"#define SOC_ENUM_ERR(xname, xenum)\

{ .iface = SNDRV_CTL_ELEM_IFACE_MIXER, .name = (xname),\.access = SNDRV_CTL_ELEM_ACCESS_READ,\.info = snd_soc_info_enum_double,\.get = snd_soc_get_enum_double, .put = snd_soc_put_enum_double,\.private_value = (unsigned long)&(xenum) }static struct i2c_client *i2c;struct ma120x0p_priv {struct regmap *regmap;int mclk_div;struct snd_soc_component *component;struct gpio_desc *enable_gpio;struct gpio_desc *mute_gpio;struct gpio_desc *booster_gpio;struct gpio_desc *error_gpio;

};static struct ma120x0p_priv *priv_data;// Used to share the IRQ number within this file

static unsigned int irqNumber;// Function prototype for the custom IRQ handler function

static irqreturn_t ma120x0p_irq_handler(int irq, void *data);/** _ _ ___ _ ___ _ _* /_\ | | / __| /_\ / __|___ _ _| |_ _ _ ___| |___* / _ \| |__\__ \/ _ \ | (__/ _ \ ' \ _| '_/ _ \ (_-<* /_/ \_\____|___/_/ \_\ \___\___/_||_\__|_| \___/_/__/**/static const char * const limenable_text[] = {"Bypassed", "Enabled"};

static const char * const limatack_text[] = {"Slow", "Normal", "Fast"};

static const char * const limrelease_text[] = {"Slow", "Normal", "Fast"};

//static const char * const audioproc_mute_text[] = {"Play", "Mute"};static const char * const err_flycap_text[] = {"Ok", "Error"};

static const char * const err_overcurr_text[] = {"Ok", "Error"};

static const char * const err_pllerr_text[] = {"Ok", "Error"};

static const char * const err_pvddunder_text[] = {"Ok", "Error"};

static const char * const err_overtempw_text[] = {"Ok", "Error"};

static const char * const err_overtempe_text[] = {"Ok", "Error"};

static const char * const err_pinlowimp_text[] = {"Ok", "Error"};

static const char * const err_dcprot_text[] = {"Ok", "Error"};static const char * const pwr_mode_prof_text[] = {"PMF0", "PMF1", "PMF2",

"PMF3", "PMF4"};static const struct soc_enum lim_enable_ctrl =SOC_ENUM_SINGLE(ma_audio_proc_limiterenable__a,ma_audio_proc_limiterenable__shift,ma_audio_proc_limiterenable__len + 1,limenable_text);

static const struct soc_enum limatack_ctrl =SOC_ENUM_SINGLE(ma_audio_proc_attack__a,ma_audio_proc_attack__shift,ma_audio_proc_attack__len + 1,limatack_text);

static const struct soc_enum limrelease_ctrl =SOC_ENUM_SINGLE(ma_audio_proc_release__a,ma_audio_proc_release__shift,ma_audio_proc_release__len + 1,limrelease_text);

static const struct soc_enum err_flycap_ctrl =SOC_ENUM_SINGLE(ma_error__a, 0, 3, err_flycap_text);

static const struct soc_enum err_overcurr_ctrl =SOC_ENUM_SINGLE(ma_error__a, 1, 3, err_overcurr_text);

static const struct soc_enum err_pllerr_ctrl =SOC_ENUM_SINGLE(ma_error__a, 2, 3, err_pllerr_text);

static const struct soc_enum err_pvddunder_ctrl =SOC_ENUM_SINGLE(ma_error__a, 3, 3, err_pvddunder_text);

static const struct soc_enum err_overtempw_ctrl =SOC_ENUM_SINGLE(ma_error__a, 4, 3, err_overtempw_text);

static const struct soc_enum err_overtempe_ctrl =SOC_ENUM_SINGLE(ma_error__a, 5, 3, err_overtempe_text);

static const struct soc_enum err_pinlowimp_ctrl =SOC_ENUM_SINGLE(ma_error__a, 6, 3, err_pinlowimp_text);

static const struct soc_enum err_dcprot_ctrl =SOC_ENUM_SINGLE(ma_error__a, 7, 3, err_dcprot_text);

static const struct soc_enum pwr_mode_prof_ctrl =SOC_ENUM_SINGLE(ma_pmprofile__a, ma_pmprofile__shift, 5,pwr_mode_prof_text);static const char * const pwr_mode_texts[] = {"Dynamic power mode","Power mode 1","Power mode 2","Power mode 3",};static const int pwr_mode_values[] = {0x10,0x50,0x60,0x70,};static const SOC_VALUE_ENUM_SINGLE_DECL(pwr_mode_ctrl,ma_pm_man__a, 0, 0x70,pwr_mode_texts,pwr_mode_values);static const DECLARE_TLV_DB_SCALE(ma120x0p_vol_tlv, -5000, 100, 0);

static const DECLARE_TLV_DB_SCALE(ma120x0p_lim_tlv, -5000, 100, 0);

static const DECLARE_TLV_DB_SCALE(ma120x0p_lr_tlv, -5000, 100, 0);static const struct snd_kcontrol_new ma120x0p_snd_controls[] = {//Master VolumeSOC_SINGLE_RANGE_TLV("A.Mstr Vol Volume",ma_vol_db_master__a, 0, 0x18, 0x4a, 1, ma120x0p_vol_tlv),//L-R Volume ch0SOC_SINGLE_RANGE_TLV("B.L Vol Volume",ma_vol_db_ch0__a, 0, 0x18, 0x4a, 1, ma120x0p_lr_tlv),SOC_SINGLE_RANGE_TLV("C.R Vol Volume",ma_vol_db_ch1__a, 0, 0x18, 0x4a, 1, ma120x0p_lr_tlv),//L-R Limiter Threshold ch0-ch1SOC_DOUBLE_R_RANGE_TLV("D.Lim thresh Volume",ma_thr_db_ch0__a, ma_thr_db_ch1__a, 0, 0x0e, 0x4a, 1, ma120x0p_lim_tlv),//Enum Switches/Selectors//SOC_ENUM("E.AudioProc Mute", audioproc_mute_ctrl),SOC_ENUM("F.Limiter Enable", lim_enable_ctrl),SOC_ENUM("G.Limiter Attck", limatack_ctrl),SOC_ENUM("H.Limiter Rls", limrelease_ctrl),//Enum Error Monitor (read-only)SOC_ENUM_ERR("I.Err flycap", err_flycap_ctrl),SOC_ENUM_ERR("J.Err overcurr", err_overcurr_ctrl),SOC_ENUM_ERR("K.Err pllerr", err_pllerr_ctrl),SOC_ENUM_ERR("L.Err pvddunder", err_pvddunder_ctrl),SOC_ENUM_ERR("M.Err overtempw", err_overtempw_ctrl),SOC_ENUM_ERR("N.Err overtempe", err_overtempe_ctrl),SOC_ENUM_ERR("O.Err pinlowimp", err_pinlowimp_ctrl),SOC_ENUM_ERR("P.Err dcprot", err_dcprot_ctrl),//Power modes profilesSOC_ENUM("Q.PM Prof", pwr_mode_prof_ctrl),// Power mode selection (Dynamic,1,2,3)SOC_ENUM("R.Power Mode", pwr_mode_ctrl),

};/** __ __ _ _ ___ _* | \/ |__ _ __| |_ (_)_ _ ___ | \ _ _(_)_ _____ _ _* | |\/| / _` / _| ' \| | ' \/ -_) | |) | '_| \ V / -_) '_|* |_| |_\__,_\__|_||_|_|_||_\___| |___/|_| |_|\_/\___|_|**/static int ma120x0p_hw_params(struct snd_pcm_substream *substream,struct snd_pcm_hw_params *params, struct snd_soc_dai *dai)

{u16 blen = 0x00;struct snd_soc_component *component = dai->component;priv_data->component = component;switch (params_format(params)) {case SNDRV_PCM_FORMAT_S16_LE:// Technically supported, but requires the BCLK to be locked at 64 x FS, effectively padding each word with an extra 16 zeros.blen = 0x16;// dev_info(dai->dev, "Configuring FMT to 16-bit \n");break;case SNDRV_PCM_FORMAT_S24_LE:// In the case of 24-bit, we just let the MA interpret it as though it's 32-bit.blen = 0x00;// dev_info(dai->dev, "Configuring FMT to 24-bit \n");break;case SNDRV_PCM_FORMAT_S24_3LE:// This format is not supported by the Raspberry PI! - But is supported by the amplifier. blen = 0x08;// dev_info(dai->dev, "Configuring FMT to 24/3-bit \n"); break; case SNDRV_PCM_FORMAT_S32_LE:// Preferred by the amplifier. In 32-bit format, no hardcoded BCLK ratio is technically, with this format, needed.blen = 0x00;// dev_info(dai->dev, "Configuring FMT to 32-bit \n"); break;default:dev_err(dai->dev, "Unsupported word length: %u\n", params_format(params));return -EINVAL;}/*Good read: https://alsa-devel.alsa-project.narkive.com/aGiYbNu8/what-is-the-difference-between-sndrv-pcm-fmtbit-s24-le-and-sndrv-pcm-fmtbit-s24-3le*/// Set word lengthsnd_soc_component_update_bits(component, ma_i2s_framesize__a,ma_i2s_framesize__mask, blen);return 0;

}static int ma120x0p_mute_stream(struct snd_soc_dai *dai, int mute, int stream)

{int val = 0;struct ma120x0p_priv *ma120x0p;struct snd_soc_component *component = dai->component;ma120x0p = snd_soc_component_get_drvdata(component);if (mute)val = 0;elseval = 1;gpiod_set_value_cansleep(priv_data->mute_gpio, val);return 0;

}static const struct snd_soc_dai_ops ma120x0p_dai_ops = {.hw_params = ma120x0p_hw_params,.mute_stream = ma120x0p_mute_stream,

};static struct snd_soc_dai_driver ma120x0p_dai = {.name = "ma120x0p-amp",.playback = {.stream_name = "Playback",.channels_min = 2,.channels_max = 2,.rates = SNDRV_PCM_RATE_CONTINUOUS,.rate_min = 44100,.rate_max = 48000,.formats = SNDRV_PCM_FMTBIT_S32_LE // | SNDRV_PCM_FMTBIT_S24_LE | SNDRV_PCM_FMTBIT_S16_LE | SNDRV_PCM_FMTBIT_S24_3LE/* Notes on format and sample rate:Currently only 32_LE works properly with the raspberry pi. This does, however, stll allow for 16 and 24 bit playback. If the above is outcommented, the amplifier will be correctly configured for 16 and 24 bit accordingly. (But don't on a raspberry pi.) Although upto 192KHz fs is supported by the amplifier - a master clock signal is required before enabling the amplifier, for it to workproperly at higher (than 48KHz) sample rates. Unfortunately the raspberry pi I2S driver disables the I2S clocks whenever it's not playing audio, and as a result, the amplifier will not play audio, as it looses it's master clock. So either we'd want to driver reboot and reconfigure (probe) the amplifier whenever an audio stream is played, or we somehow have the I2S driver always output its BCLK (which doesn't seem doable). */},.ops = &ma120x0p_dai_ops,

};/** ___ _ ___ _* / __|___ __| |___ __ | \ _ _(_)_ _____ _ _* | (__/ _ \/ _` / -_) _| | |) | '_| \ V / -_) '_|* \___\___/\__,_\___\__| |___/|_| |_|\_/\___|_|**/

static int ma120x0p_clear_err(struct snd_soc_component *component)

{int ret = 0;struct ma120x0p_priv *ma120x0p;ma120x0p = snd_soc_component_get_drvdata(component);ret = snd_soc_component_update_bits(component,ma_eh_clear__a, ma_eh_clear__mask, 0x00);if (ret < 0)return ret;ret = snd_soc_component_update_bits(component,ma_eh_clear__a, ma_eh_clear__mask, 0x04);if (ret < 0)return ret;ret = snd_soc_component_update_bits(component,ma_eh_clear__a, ma_eh_clear__mask, 0x00);if (ret < 0)return ret;return 0;

}static void ma120x0p_remove(struct snd_soc_component *component)

{struct ma120x0p_priv *ma120x0p;ma120x0p = snd_soc_component_get_drvdata(component);

}static int ma120x0p_probe(struct snd_soc_component *component)

{struct ma120x0p_priv *ma120x0p;int ret = 0;i2c = container_of(component->dev, struct i2c_client, dev);ma120x0p = snd_soc_component_get_drvdata(component);//Reset errorma120x0p_clear_err(component);if (ret < 0)return ret;// set serial audio format I2S and enable audio processorret = snd_soc_component_write(component, ma_i2s_format__a, 0x08);if (ret < 0)return ret;// Enable audio limiterret = snd_soc_component_update_bits(component,ma_audio_proc_limiterenable__a, ma_audio_proc_limiterenable__mask, 0x40);if (ret < 0)return ret;// Set lim attack to fastret = snd_soc_component_update_bits(component,ma_audio_proc_attack__a,ma_audio_proc_attack__mask, 0x80);if (ret < 0)return ret;// Set lim attack to lowret = snd_soc_component_update_bits(component,ma_audio_proc_release__a, ma_audio_proc_release__mask, 0x00);if (ret < 0)return ret;// set volume to 0dBret = snd_soc_component_write(component, ma_vol_db_master__a, 0x18);if (ret < 0)return ret;// set ch0 lim thresh to -15dBret = snd_soc_component_write(component, ma_thr_db_ch0__a, 0x27);if (ret < 0)return ret;// set ch1 lim thresh to -15dBret = snd_soc_component_write(component, ma_thr_db_ch1__a, 0x27);if (ret < 0)return ret;//Check for errorsret = snd_soc_component_test_bits(component, ma_error_acc__a, 0x00, 0);if (ret < 0)return ret;ret = snd_soc_component_test_bits(component, ma_error_acc__a, 0x01, 0);if (ret < 0)return ret;ret = snd_soc_component_test_bits(component, ma_error_acc__a, 0x02, 0);if (ret < 0)return ret;ret = snd_soc_component_test_bits(component, ma_error_acc__a, 0x08, 0);if (ret < 0)return ret;ret = snd_soc_component_test_bits(component, ma_error_acc__a, 0x10, 0);if (ret < 0)return ret;ret = snd_soc_component_test_bits(component, ma_error_acc__a, 0x20, 0);if (ret < 0)return ret;ret = snd_soc_component_test_bits(component, ma_error_acc__a, 0x40, 0);if (ret < 0)return ret;ret = snd_soc_component_test_bits(component, ma_error_acc__a, 0x80, 0);if (ret < 0)return ret;return 0;

}static int ma120x0p_set_bias_level(struct snd_soc_component *component, enum snd_soc_bias_level level)

{int ret = 0;struct ma120x0p_priv *ma120x0p;ma120x0p = snd_soc_component_get_drvdata(component);switch (level) {case SND_SOC_BIAS_ON:break;case SND_SOC_BIAS_PREPARE:break;case SND_SOC_BIAS_STANDBY:ret = gpiod_get_value_cansleep(priv_data->enable_gpio);if (ret != 0) {dev_err(component->dev, "Device ma120x0p disabled in STANDBY BIAS: %d\n",ret);return ret;}break;case SND_SOC_BIAS_OFF:break;}return 0;

}static const struct snd_soc_dapm_widget ma120x0p_dapm_widgets[] = {SND_SOC_DAPM_OUTPUT("OUT_A"),SND_SOC_DAPM_OUTPUT("OUT_B"),

};static const struct snd_soc_dapm_route ma120x0p_dapm_routes[] = {{ "OUT_B", NULL, "Playback" },{ "OUT_A", NULL, "Playback" },

};static const struct snd_soc_component_driver ma120x0p_component_driver = {.probe = ma120x0p_probe,.remove = ma120x0p_remove,.set_bias_level = ma120x0p_set_bias_level,.dapm_widgets = ma120x0p_dapm_widgets,.num_dapm_widgets = ARRAY_SIZE(ma120x0p_dapm_widgets),.dapm_routes = ma120x0p_dapm_routes,.num_dapm_routes = ARRAY_SIZE(ma120x0p_dapm_routes),.controls = ma120x0p_snd_controls,.num_controls = ARRAY_SIZE(ma120x0p_snd_controls),.use_pmdown_time = 1,.endianness = 1,.non_legacy_dai_naming = 1,

};/** ___ ___ ___ ___ _* |_ _|_ ) __| | \ _ _(_)_ _____ _ _* | | / / (__ | |) | '_| \ V / -_) '_|* |___/___\___| |___/|_| |_|\_/\___|_|**/static const struct reg_default ma120x0p_reg_defaults[] = {{ 0x01, 0x3c },

};static bool ma120x0p_reg_volatile(struct device *dev, unsigned int reg)

{switch (reg) {case ma_error__a:case ma_error_acc__a:return true;default:return false;}

}static const struct of_device_id ma120x0p_of_match[] = {{ .compatible = "ma,ma120x0p", },{ }

};MODULE_DEVICE_TABLE(of, ma120x0p_of_match);static struct regmap_config ma120x0p_regmap_config = {.reg_bits = 8,.val_bits = 8,.max_register = 255,.volatile_reg = ma120x0p_reg_volatile,.cache_type = REGCACHE_RBTREE,.reg_defaults = ma120x0p_reg_defaults,.num_reg_defaults = ARRAY_SIZE(ma120x0p_reg_defaults),

};static irqreturn_t ma120x0p_exception_handler(int irq, void *data)

{struct snd_soc_component *component;int ret;component = priv_data->component;ret = snd_soc_component_read(component, ma_error_acc__a);if (ret != 0){if (ret & 0x01){dev_info(component->dev, "Flying Capacitor Overvoltage Error\n");}if (ret & 0x02){dev_info(component->dev, "Over Current Protection Error\n");}if (ret & 0x04){dev_info(component->dev, "Amplifier PLL Error\n");}if (ret & 0x08){dev_info(component->dev, "Over temperature Warning\n");}if (ret & 0x10){dev_info(component->dev, "Over Temperature Error\n");}if (ret & 0x20){dev_info(component->dev, "Pin to Pin low impedance");}if (ret & 0x40){dev_info(component->dev, "DC Protection \n");}ma120x0p_clear_err(component);dev_info(component->dev, "Error Register Attemped Cleared \n");/* If an error occurs, the error will be stated in dmesg, after which the error registerin the amplifier will be cleared, and the amplifier will continue. One could here implement some more protection/mittigation, however, the amplifier is already protected from the most catastrophic failures in hardware.*/}return IRQ_HANDLED;

}static int ma120x0p_i2c_probe(struct i2c_client *i2c,const struct i2c_device_id *id)

{printk(KERN_INFO "Start Merus I2C Probe init");int ret;priv_data = devm_kzalloc(&i2c->dev, sizeof(*priv_data), GFP_KERNEL);if (!priv_data)return -ENOMEM;i2c_set_clientdata(i2c, priv_data);priv_data->regmap = devm_regmap_init_i2c(i2c, &ma120x0p_regmap_config);if (IS_ERR(priv_data->regmap)) {ret = PTR_ERR(priv_data->regmap);return ret;}// Startup sequence:// Make sure the device is mutedpriv_data->mute_gpio = devm_gpiod_get(&i2c->dev, "mute_gp",GPIOD_OUT_LOW);if (IS_ERR(priv_data->mute_gpio)) {ret = PTR_ERR(priv_data->mute_gpio);dev_err(&i2c->dev, "Failed to get mute gpio line: %d\n", ret);return ret;}msleep(50);// MA120xx0P devices can be powered by an integrated boost converter.// An option GPIO control line is provided to enable a booster properly and// in sync with the enable and mute GPIO lines.priv_data->booster_gpio = devm_gpiod_get_optional(&i2c->dev,"booster_gp", GPIOD_OUT_LOW);if (IS_ERR(priv_data->booster_gpio)) {ret = PTR_ERR(priv_data->booster_gpio);dev_err(&i2c->dev, "Failed to get booster enable gpio line: %d\n", ret);return ret;}msleep(50);// Enable booster and wait 200ms until PVDD stablises. gpiod_set_value_cansleep(priv_data->booster_gpio, 1);msleep(200);printk(KERN_INFO "Boost Converter enabled");// Enable MA120x0ppriv_data->enable_gpio = devm_gpiod_get(&i2c->dev, "enable_gp",GPIOD_OUT_LOW);if (IS_ERR(priv_data->enable_gpio)) {ret = PTR_ERR(priv_data->enable_gpio);dev_err(&i2c->dev, "Failed to get ma120x0p enable gpio line: %d\n", ret);return ret;}msleep(50);// Optional use of MA120x0p error line as an interrupt trigger to// platform GPIO.// Get error input gpio MA120x0p and register it as interrupt, with appropriate callback.priv_data->error_gpio = devm_gpiod_get_optional(&i2c->dev,"error_gp", GPIOD_IN);if (IS_ERR(priv_data->error_gpio)) {ret = PTR_ERR(priv_data->error_gpio);dev_err(&i2c->dev, "Failed to get ma120x0p error gpio line: %d\n", ret);return ret;}printk(KERN_INFO "Registering Error interrupt");if (priv_data->error_gpio != NULL) {irqNumber = gpiod_to_irq(priv_data->error_gpio);printk(KERN_INFO "GPIO: The button is mapped to IRQ: %d\n",irqNumber);ret = devm_request_threaded_irq(&i2c->dev,irqNumber, ma120x0p_irq_handler,ma120x0p_exception_handler, IRQF_TRIGGER_FALLING,"ma120x0p", priv_data);if (ret != 0) {dev_warn(&i2c->dev, "Failed to request IRQ: %d\n", ret);} else {printk(KERN_INFO "GPIO_TEST: The interrupt request result is: %d\n",ret);}}ret = devm_snd_soc_register_component(&i2c->dev,&ma120x0p_component_driver, &ma120x0p_dai, 1);return ret;

}static irqreturn_t ma120x0p_irq_handler(int irq, void *data)

{// gpiod_set_value_cansleep(priv_data->mute_gpio, 0);// gpiod_set_value_cansleep(priv_data->enable_gpio, 1);// ^ If commented in, the amplifier with mute and disable in case of any error!return IRQ_WAKE_THREAD;

}static int ma120x0p_i2c_remove(struct i2c_client *i2c)

{snd_soc_unregister_component(&i2c->dev);i2c_set_clientdata(i2c, NULL);gpiod_set_value_cansleep(priv_data->mute_gpio, 0);msleep(30);gpiod_set_value_cansleep(priv_data->enable_gpio, 1);msleep(200);gpiod_set_value_cansleep(priv_data->booster_gpio, 0);msleep(200);kfree(priv_data);return 0;

}static void ma120x0p_i2c_shutdown(struct i2c_client *i2c)

{snd_soc_unregister_component(&i2c->dev);i2c_set_clientdata(i2c, NULL);gpiod_set_value_cansleep(priv_data->mute_gpio, 0);msleep(30);gpiod_set_value_cansleep(priv_data->enable_gpio, 1);msleep(200);gpiod_set_value_cansleep(priv_data->booster_gpio, 0);msleep(200);kfree(priv_data);

}static const struct i2c_device_id ma120x0p_i2c_id[] = {{ "ma120x0p", 0 },{ }

};MODULE_DEVICE_TABLE(i2c, ma120x0p_i2c_id);static struct i2c_driver ma120x0p_i2c_driver = {.driver = {.name = "ma120x0p",.owner = THIS_MODULE,.of_match_table = ma120x0p_of_match,},.probe = ma120x0p_i2c_probe,.remove = ma120x0p_i2c_remove,.shutdown = ma120x0p_i2c_shutdown,.id_table = ma120x0p_i2c_id

};static int __init ma120x0p_modinit(void)

{int ret = 0;ret = i2c_add_driver(&ma120x0p_i2c_driver);if (ret) {printk(KERN_ERR "Failed to register ma120x0p I2C driver: %d\n", ret);}return ret;

}module_init(ma120x0p_modinit);static void __exit ma120x0p_exit(void)

{i2c_del_driver(&ma120x0p_i2c_driver);

}

module_exit(ma120x0p_exit);MODULE_AUTHOR("Ariel Muszkat ariel.muszkat@gmail.com>");

MODULE_DESCRIPTION("ASoC driver for ma120x0p");

MODULE_LICENSE("GPL v2");ma120x0p.h

// SPDX-License-Identifier: GPL-2.0-or-later

/** ASoC Driver for Infineon Merus(TM) ma120x0p multi-level class-D amplifier** Author: Ariel Muszkat <ariel.muszkat@gmail.com>* Jorgen Kragh Jakobsen <jorgen.kraghjakobsen@infineon.com>** Copyright (C) 2019 Infineon Technologies AG**/

#ifndef _MA120X0P_

#define _MA120X0P_

//------------------------------------------------------------------manualPM---

// Select Manual PowerMode control

#define ma_manualpm__a 0

#define ma_manualpm__len 1

#define ma_manualpm__mask 0x40

#define ma_manualpm__shift 0x06

#define ma_manualpm__reset 0x00

//--------------------------------------------------------------------pm_man---

// manual selected power mode

#define ma_pm_man__a 0

#define ma_pm_man__len 2

#define ma_pm_man__mask 0x30

#define ma_pm_man__shift 0x04

#define ma_pm_man__reset 0x03

//------------------------------------------ ----------------------mthr_1to2---

// mod. index threshold value for pm1=>pm2 change.

#define ma_mthr_1to2__a 1

#define ma_mthr_1to2__len 8

#define ma_mthr_1to2__mask 0xff

#define ma_mthr_1to2__shift 0x00

#define ma_mthr_1to2__reset 0x3c

//-----------------------------------------------------------------mthr_2to1---

// mod. index threshold value for pm2=>pm1 change.

#define ma_mthr_2to1__a 2

#define ma_mthr_2to1__len 8

#define ma_mthr_2to1__mask 0xff

#define ma_mthr_2to1__shift 0x00

#define ma_mthr_2to1__reset 0x32

//-----------------------------------------------------------------mthr_2to3---

// mod. index threshold value for pm2=>pm3 change.

#define ma_mthr_2to3__a 3

#define ma_mthr_2to3__len 8

#define ma_mthr_2to3__mask 0xff

#define ma_mthr_2to3__shift 0x00

#define ma_mthr_2to3__reset 0x5a

//-----------------------------------------------------------------mthr_3to2---

// mod. index threshold value for pm3=>pm2 change.

#define ma_mthr_3to2__a 4

#define ma_mthr_3to2__len 8

#define ma_mthr_3to2__mask 0xff

#define ma_mthr_3to2__shift 0x00

#define ma_mthr_3to2__reset 0x50

//-------------------------------------------------------------pwmclkdiv_nom---

// pwm default clock divider value

#define ma_pwmclkdiv_nom__a 8

#define ma_pwmclkdiv_nom__len 8

#define ma_pwmclkdiv_nom__mask 0xff

#define ma_pwmclkdiv_nom__shift 0x00

#define ma_pwmclkdiv_nom__reset 0x26

//--------- ----------------------------------------------------ocp_latch_en---

// high to use permanently latching level-2 ocp

#define ma_ocp_latch_en__a 10

#define ma_ocp_latch_en__len 1

#define ma_ocp_latch_en__mask 0x02

#define ma_ocp_latch_en__shift 0x01

#define ma_ocp_latch_en__reset 0x00

//---------------------------------------------------------------lf_clamp_en---

// high (default) to enable lf int2+3 clamping on clip

#define ma_lf_clamp_en__a 10

#define ma_lf_clamp_en__len 1

#define ma_lf_clamp_en__mask 0x80

#define ma_lf_clamp_en__shift 0x07

#define ma_lf_clamp_en__reset 0x00

//-------------------------------------------------------pmcfg_btl_b.modtype---

//

#define ma_pmcfg_btl_b__modtype__a 18

#define ma_pmcfg_btl_b__modtype__len 2

#define ma_pmcfg_btl_b__modtype__mask 0x18

#define ma_pmcfg_btl_b__modtype__shift 0x03

#define ma_pmcfg_btl_b__modtype__reset 0x02

//-------------------------------------------------------pmcfg_btl_b.freqdiv---

#define ma_pmcfg_btl_b__freqdiv__a 18

#define ma_pmcfg_btl_b__freqdiv__len 2

#define ma_pmcfg_btl_b__freqdiv__mask 0x06

#define ma_pmcfg_btl_b__freqdiv__shift 0x01

#define ma_pmcfg_btl_b__freqdiv__reset 0x01

//----------------------------------------------------pmcfg_btl_b.lf_gain_ol---

//

#define ma_pmcfg_btl_b__lf_gain_ol__a 18

#define ma_pmcfg_btl_b__lf_gain_ol__len 1

#define ma_pmcfg_btl_b__lf_gain_ol__mask 0x01

#define ma_pmcfg_btl_b__lf_gain_ol__shift 0x00

#define ma_pmcfg_btl_b__lf_gain_ol__reset 0x01

//-------------------------------------------------------pmcfg_btl_c.freqdiv---

//

#define ma_pmcfg_btl_c__freqdiv__a 19

#define ma_pmcfg_btl_c__freqdiv__len 2

#define ma_pmcfg_btl_c__freqdiv__mask 0x06

#define ma_pmcfg_btl_c__freqdiv__shift 0x01

#define ma_pmcfg_btl_c__freqdiv__reset 0x01

//-------------------------------------------------------pmcfg_btl_c.modtype---

//

#define ma_pmcfg_btl_c__modtype__a 19

#define ma_pmcfg_btl_c__modtype__len 2

#define ma_pmcfg_btl_c__modtype__mask 0x18

#define ma_pmcfg_btl_c__modtype__shift 0x03

#define ma_pmcfg_btl_c__modtype__reset 0x01

//----------------------------------------------------pmcfg_btl_c.lf_gain_ol---

//

#define ma_pmcfg_btl_c__lf_gain_ol__a 19

#define ma_pmcfg_btl_c__lf_gain_ol__len 1

#define ma_pmcfg_btl_c__lf_gain_ol__mask 0x01

#define ma_pmcfg_btl_c__lf_gain_ol__shift 0x00

#define ma_pmcfg_btl_c__lf_gain_ol__reset 0x00

//-------------------------------------------------------pmcfg_btl_d.modtype---

//

#define ma_pmcfg_btl_d__modtype__a 20

#define ma_pmcfg_btl_d__modtype__len 2

#define ma_pmcfg_btl_d__modtype__mask 0x18

#define ma_pmcfg_btl_d__modtype__shift 0x03

#define ma_pmcfg_btl_d__modtype__reset 0x02

//-------------------------------------------------------pmcfg_btl_d.freqdiv---

//

#define ma_pmcfg_btl_d__freqdiv__a 20

#define ma_pmcfg_btl_d__freqdiv__len 2

#define ma_pmcfg_btl_d__freqdiv__mask 0x06

#define ma_pmcfg_btl_d__freqdiv__shift 0x01

#define ma_pmcfg_btl_d__freqdiv__reset 0x02

//----------------------------------------------------pmcfg_btl_d.lf_gain_ol---

//

#define ma_pmcfg_btl_d__lf_gain_ol__a 20

#define ma_pmcfg_btl_d__lf_gain_ol__len 1

#define ma_pmcfg_btl_d__lf_gain_ol__mask 0x01

#define ma_pmcfg_btl_d__lf_gain_ol__shift 0x00

#define ma_pmcfg_btl_d__lf_gain_ol__reset 0x00

//------------ -------------------------------------------pmcfg_se_a.modtype---

//

#define ma_pmcfg_se_a__modtype__a 21

#define ma_pmcfg_se_a__modtype__len 2

#define ma_pmcfg_se_a__modtype__mask 0x18

#define ma_pmcfg_se_a__modtype__shift 0x03

#define ma_pmcfg_se_a__modtype__reset 0x01

//--------------------------------------------------------pmcfg_se_a.freqdiv---

//

#define ma_pmcfg_se_a__freqdiv__a 21

#define ma_pmcfg_se_a__freqdiv__len 2

#define ma_pmcfg_se_a__freqdiv__mask 0x06

#define ma_pmcfg_se_a__freqdiv__shift 0x01

#define ma_pmcfg_se_a__freqdiv__reset 0x00

//-----------------------------------------------------pmcfg_se_a.lf_gain_ol---

//

#define ma_pmcfg_se_a__lf_gain_ol__a 21

#define ma_pmcfg_se_a__lf_gain_ol__len 1

#define ma_pmcfg_se_a__lf_gain_ol__mask 0x01

#define ma_pmcfg_se_a__lf_gain_ol__shift 0x00

#define ma_pmcfg_se_a__lf_gain_ol__reset 0x01

//-----------------------------------------------------pmcfg_se_b.lf_gain_ol---

//

#define ma_pmcfg_se_b__lf_gain_ol__a 22

#define ma_pmcfg_se_b__lf_gain_ol__len 1

#define ma_pmcfg_se_b__lf_gain_ol__mask 0x01

#define ma_pmcfg_se_b__lf_gain_ol__shift 0x00

#define ma_pmcfg_se_b__lf_gain_ol__reset 0x00

//--------------------------------------------------------pmcfg_se_b.freqdiv---

//

#define ma_pmcfg_se_b__freqdiv__a 22

#define ma_pmcfg_se_b__freqdiv__len 2

#define ma_pmcfg_se_b__freqdiv__mask 0x06

#define ma_pmcfg_se_b__freqdiv__shift 0x01

#define ma_pmcfg_se_b__freqdiv__reset 0x01

//--------------------------------------------------------pmcfg_se_b.modtype---

//

#define ma_pmcfg_se_b__modtype__a 22

#define ma_pmcfg_se_b__modtype__len 2

#define ma_pmcfg_se_b__modtype__mask 0x18

#define ma_pmcfg_se_b__modtype__shift 0x03

#define ma_pmcfg_se_b__modtype__reset 0x01

//----------------------------------------------------------balwaitcount_pm1---

// pm1 balancing period.

#define ma_balwaitcount_pm1__a 23

#define ma_balwaitcount_pm1__len 8

#define ma_balwaitcount_pm1__mask 0xff

#define ma_balwaitcount_pm1__shift 0x00

#define ma_balwaitcount_pm1__reset 0x14

//----------------------------------------------------------balwaitcount_pm2---

// pm2 balancing period.

#define ma_balwaitcount_pm2__a 24

#define ma_balwaitcount_pm2__len 8

#define ma_balwaitcount_pm2__mask 0xff

#define ma_balwaitcount_pm2__shift 0x00

#define ma_balwaitcount_pm2__reset 0x14

//----------------------------------------------------------balwaitcount_pm3---

// pm3 balancing period.

#define ma_balwaitcount_pm3__a 25

#define ma_balwaitcount_pm3__len 8

#define ma_balwaitcount_pm3__mask 0xff

#define ma_balwaitcount_pm3__shift 0x00

#define ma_balwaitcount_pm3__reset 0x1a

//-------------------------------------------------------------usespread_pm1---

// pm1 pwm spread-spectrum mode on/off.

#define ma_usespread_pm1__a 26

#define ma_usespread_pm1__len 1

#define ma_usespread_pm1__mask 0x40

#define ma_usespread_pm1__shift 0x06

#define ma_usespread_pm1__reset 0x00

//---------------------------------------------------------------dtsteps_pm1---

// pm1 dead time setting [10ns steps].

#define ma_dtsteps_pm1__a 26

#define ma_dtsteps_pm1__len 3

#define ma_dtsteps_pm1__mask 0x38

#define ma_dtsteps_pm1__shift 0x03

#define ma_dtsteps_pm1__reset 0x04

//---------------------------------------------------------------baltype_pm1---

// pm1 balancing sensor scheme.

#define ma_baltype_pm1__a 26

#define ma_baltype_pm1__len 3

#define ma_baltype_pm1__mask 0x07

#define ma_baltype_pm1__shift 0x00

#define ma_baltype_pm1__reset 0x00

//-------------------------------------------------------------usespread_pm2---

// pm2 pwm spread-spectrum mode on/off.

#define ma_usespread_pm2__a 27

#define ma_usespread_pm2__len 1

#define ma_usespread_pm2__mask 0x40

#define ma_usespread_pm2__shift 0x06

#define ma_usespread_pm2__reset 0x00

//---------------------------------------------------------------dtsteps_pm2---

// pm2 dead time setting [10ns steps].

#define ma_dtsteps_pm2__a 27

#define ma_dtsteps_pm2__len 3

#define ma_dtsteps_pm2__mask 0x38

#define ma_dtsteps_pm2__shift 0x03

#define ma_dtsteps_pm2__reset 0x03

//---------------------------------------------------------------baltype_pm2---

// pm2 balancing sensor scheme.

#define ma_baltype_pm2__a 27

#define ma_baltype_pm2__len 3

#define ma_baltype_pm2__mask 0x07

#define ma_baltype_pm2__shift 0x00

#define ma_baltype_pm2__reset 0x01

//-------------------------------------------------------------usespread_pm3---

// pm3 pwm spread-spectrum mode on/off.

#define ma_usespread_pm3__a 28

#define ma_usespread_pm3__len 1

#define ma_usespread_pm3__mask 0x40

#define ma_usespread_pm3__shift 0x06

#define ma_usespread_pm3__reset 0x00

//---------------------------------------------------------------dtsteps_pm3---

// pm3 dead time setting [10ns steps].

#define ma_dtsteps_pm3__a 28

#define ma_dtsteps_pm3__len 3

#define ma_dtsteps_pm3__mask 0x38

#define ma_dtsteps_pm3__shift 0x03

#define ma_dtsteps_pm3__reset 0x01

//---------------------------------------------------------------baltype_pm3---

// pm3 balancing sensor scheme.

#define ma_baltype_pm3__a 28

#define ma_baltype_pm3__len 3

#define ma_baltype_pm3__mask 0x07

#define ma_baltype_pm3__shift 0x00

#define ma_baltype_pm3__reset 0x03

//-----------------------------------------------------------------pmprofile---

// pm profile select. valid presets: 0-1-2-3-4. 5=> custom profile.

#define ma_pmprofile__a 29

#define ma_pmprofile__len 3

#define ma_pmprofile__mask 0x07

#define ma_pmprofile__shift 0x00

#define ma_pmprofile__reset 0x00

//-------------------------------------------------------------------pm3_man---

// custom profile pm3 contents. 0=>a, 1=>b, 2=>c, 3=>d

#define ma_pm3_man__a 30

#define ma_pm3_man__len 2

#define ma_pm3_man__mask 0x30

#define ma_pm3_man__shift 0x04

#define ma_pm3_man__reset 0x02

//-------------------------------------------------------------------pm2_man---

// custom profile pm2 contents. 0=>a, 1=>b, 2=>c, 3=>d

#define ma_pm2_man__a 30

#define ma_pm2_man__len 2

#define ma_pm2_man__mask 0x0c

#define ma_pm2_man__shift 0x02

#define ma_pm2_man__reset 0x03

//-------------------------------------------------------------------pm1_man---

// custom profile pm1 contents. 0=>a, 1=>b, 2=>c, 3=>d

#define ma_pm1_man__a 30

#define ma_pm1_man__len 2

#define ma_pm1_man__mask 0x03

#define ma_pm1_man__shift 0x00

#define ma_pm1_man__reset 0x03

//-----------------------------------------------------------ocp_latch_clear---

// low-high clears current ocp latched condition.

#define ma_ocp_latch_clear__a 32

#define ma_ocp_latch_clear__len 1

#define ma_ocp_latch_clear__mask 0x80

#define ma_ocp_latch_clear__shift 0x07

#define ma_ocp_latch_clear__reset 0x00

//-------------------------------------------------------------audio_in_mode---

// audio input mode; 0-1-2-3-4-5

#define ma_audio_in_mode__a 37

#define ma_audio_in_mode__len 3

#define ma_audio_in_mode__mask 0xe0

#define ma_audio_in_mode__shift 0x05

#define ma_audio_in_mode__reset 0x00

//-----------------------------------------------------------------eh_dcshdn---

// high to enable dc protection

#define ma_eh_dcshdn__a 38

#define ma_eh_dcshdn__len 1

#define ma_eh_dcshdn__mask 0x04

#define ma_eh_dcshdn__shift 0x02

#define ma_eh_dcshdn__reset 0x01

//---------------------------------------------------------audio_in_mode_ext---

// if set, audio_in_mode is controlled from audio_in_mode register. if not set

//audio_in_mode is set from fuse bank setting

#define ma_audio_in_mode_ext__a 39

#define ma_audio_in_mode_ext__len 1

#define ma_audio_in_mode_ext__mask 0x20

#define ma_audio_in_mode_ext__shift 0x05

#define ma_audio_in_mode_ext__reset 0x00

//------------------------------------------------------------------eh_clear---

// flip to clear error registers

#define ma_eh_clear__a 45

#define ma_eh_clear__len 1

#define ma_eh_clear__mask 0x04

#define ma_eh_clear__shift 0x02

#define ma_eh_clear__reset 0x00

//----------------------------------------------------------thermal_compr_en---

// enable otw-contr. input compression?

#define ma_thermal_compr_en__a 45

#define ma_thermal_compr_en__len 1

#define ma_thermal_compr_en__mask 0x20

#define ma_thermal_compr_en__shift 0x05

#define ma_thermal_compr_en__reset 0x01

//---------------------------------------------------------------system_mute---

// 1 = mute system, 0 = normal operation

#define ma_system_mute__a 45

#define ma_system_mute__len 1

#define ma_system_mute__mask 0x40

#define ma_system_mute__shift 0x06

#define ma_system_mute__reset 0x00

//------------------------------------------------------thermal_compr_max_db---

// audio limiter max thermal reduction

#define ma_thermal_compr_max_db__a 46

#define ma_thermal_compr_max_db__len 3

#define ma_thermal_compr_max_db__mask 0x07

#define ma_thermal_compr_max_db__shift 0x00

#define ma_thermal_compr_max_db__reset 0x04

//---------------------------------------------------------audio_proc_enable---

// enable audio proc, bypass if not enabled

#define ma_audio_proc_enable__a 53

#define ma_audio_proc_enable__len 1

#define ma_audio_proc_enable__mask 0x08

#define ma_audio_proc_enable__shift 0x03

#define ma_audio_proc_enable__reset 0x00

//--------------------------------------------------------audio_proc_release---

// 00:slow, 01:normal, 10:fast

#define ma_audio_proc_release__a 53

#define ma_audio_proc_release__len 2

#define ma_audio_proc_release__mask 0x30

#define ma_audio_proc_release__shift 0x04

#define ma_audio_proc_release__reset 0x00

//---------------------------------------------------------audio_proc_attack---

// 00:slow, 01:normal, 10:fast

#define ma_audio_proc_attack__a 53

#define ma_audio_proc_attack__len 2

#define ma_audio_proc_attack__mask 0xc0

#define ma_audio_proc_attack__shift 0x06

#define ma_audio_proc_attack__reset 0x00

//----------------------------------------------------------------i2s_format---

// i2s basic data format, 000 = std. i2s, 001 = left justified (default)

#define ma_i2s_format__a 53

#define ma_i2s_format__len 3

#define ma_i2s_format__mask 0x07

#define ma_i2s_format__shift 0x00

#define ma_i2s_format__reset 0x01

//--------------------------------------------------audio_proc_limiterenable---

// 1: enable limiter, 0: disable limiter

#define ma_audio_proc_limiterenable__a 54

#define ma_audio_proc_limiterenable__len 1

#define ma_audio_proc_limiterenable__mask 0x40

#define ma_audio_proc_limiterenable__shift 0x06

#define ma_audio_proc_limiterenable__reset 0x00

//-----------------------------------------------------------audio_proc_mute---

// 1: mute, 0: unmute

#define ma_audio_proc_mute__a 54

#define ma_audio_proc_mute__len 1

#define ma_audio_proc_mute__mask 0x80

#define ma_audio_proc_mute__shift 0x07

#define ma_audio_proc_mute__reset 0x00

//---------------------------------------------------------------i2s_sck_pol---

// i2s sck polarity cfg. 0 = rising edge data change

#define ma_i2s_sck_pol__a 54

#define ma_i2s_sck_pol__len 1

#define ma_i2s_sck_pol__mask 0x01

#define ma_i2s_sck_pol__shift 0x00

#define ma_i2s_sck_pol__reset 0x01

//-------------------------------------------------------------i2s_framesize---

// i2s word length. 00 = 32bit, 01 = 24bit

#define ma_i2s_framesize__a 54

#define ma_i2s_framesize__len 2

#define ma_i2s_framesize__mask 0x18

#define ma_i2s_framesize__shift 0x03

#define ma_i2s_framesize__reset 0x00

//----------------------------------------------------------------i2s_ws_pol---

// i2s ws polarity. 0 = low first

#define ma_i2s_ws_pol__a 54

#define ma_i2s_ws_pol__len 1

#define ma_i2s_ws_pol__mask 0x02

#define ma_i2s_ws_pol__shift 0x01

#define ma_i2s_ws_pol__reset 0x00

//-----------------------------------------------------------------i2s_order---

// i2s word bit order. 0 = msb first

#define ma_i2s_order__a 54

#define ma_i2s_order__len 1

#define ma_i2s_order__mask 0x04

#define ma_i2s_order__shift 0x02

#define ma_i2s_order__reset 0x00

//------------------------------------------------------------i2s_rightfirst---

// i2s l/r word order; 0 = left first

#define ma_i2s_rightfirst__a 54

#define ma_i2s_rightfirst__len 1

#define ma_i2s_rightfirst__mask 0x20

#define ma_i2s_rightfirst__shift 0x05

#define ma_i2s_rightfirst__reset 0x00

//-------------------------------------------------------------vol_db_master---

// master volume db

#define ma_vol_db_master__a 64

#define ma_vol_db_master__len 8

#define ma_vol_db_master__mask 0xff

#define ma_vol_db_master__shift 0x00

#define ma_vol_db_master__reset 0x18

//------------------------------------------------------------vol_lsb_master---

// master volume lsb 1/4 steps

#define ma_vol_lsb_master__a 65

#define ma_vol_lsb_master__len 2

#define ma_vol_lsb_master__mask 0x03

#define ma_vol_lsb_master__shift 0x00

#define ma_vol_lsb_master__reset 0x00

//----------------------------------------------------------------vol_db_ch0---

// volume channel 0

#define ma_vol_db_ch0__a 66

#define ma_vol_db_ch0__len 8

#define ma_vol_db_ch0__mask 0xff

#define ma_vol_db_ch0__shift 0x00

#define ma_vol_db_ch0__reset 0x18

//----------------------------------------------------------------vol_db_ch1---

// volume channel 1

#define ma_vol_db_ch1__a 67

#define ma_vol_db_ch1__len 8

#define ma_vol_db_ch1__mask 0xff

#define ma_vol_db_ch1__shift 0x00

#define ma_vol_db_ch1__reset 0x18

//----------------------------------------------------------------vol_db_ch2---

// volume channel 2

#define ma_vol_db_ch2__a 68

#define ma_vol_db_ch2__len 8

#define ma_vol_db_ch2__mask 0xff

#define ma_vol_db_ch2__shift 0x00

#define ma_vol_db_ch2__reset 0x18

//----------------------------------------------------------------vol_db_ch3---

// volume channel 3

#define ma_vol_db_ch3__a 69

#define ma_vol_db_ch3__len 8

#define ma_vol_db_ch3__mask 0xff

#define ma_vol_db_ch3__shift 0x00

#define ma_vol_db_ch3__reset 0x18

//---------------------------------------------------------------vol_lsb_ch0---

// volume channel 1 - 1/4 steps

#define ma_vol_lsb_ch0__a 70

#define ma_vol_lsb_ch0__len 2

#define ma_vol_lsb_ch0__mask 0x03

#define ma_vol_lsb_ch0__shift 0x00

#define ma_vol_lsb_ch0__reset 0x00

//---------------------------------------------------------------vol_lsb_ch1---

// volume channel 3 - 1/4 steps

#define ma_vol_lsb_ch1__a 70

#define ma_vol_lsb_ch1__len 2

#define ma_vol_lsb_ch1__mask 0x0c

#define ma_vol_lsb_ch1__shift 0x02

#define ma_vol_lsb_ch1__reset 0x00

//---------------------------------------------------------------vol_lsb_ch2---

// volume channel 2 - 1/4 steps

#define ma_vol_lsb_ch2__a 70

#define ma_vol_lsb_ch2__len 2

#define ma_vol_lsb_ch2__mask 0x30

#define ma_vol_lsb_ch2__shift 0x04

#define ma_vol_lsb_ch2__reset 0x00

//---------------------------------------------------------------vol_lsb_ch3---

// volume channel 3 - 1/4 steps

#define ma_vol_lsb_ch3__a 70

#define ma_vol_lsb_ch3__len 2

#define ma_vol_lsb_ch3__mask 0xc0

#define ma_vol_lsb_ch3__shift 0x06

#define ma_vol_lsb_ch3__reset 0x00

//----------------------------------------------------------------thr_db_ch0---

// thr_db channel 0

#define ma_thr_db_ch0__a 71

#define ma_thr_db_ch0__len 8

#define ma_thr_db_ch0__mask 0xff

#define ma_thr_db_ch0__shift 0x00

#define ma_thr_db_ch0__reset 0x18

//----------------------------------------------------------------thr_db_ch1---

// thr db ch1

#define ma_thr_db_ch1__a 72

#define ma_thr_db_ch1__len 8

#define ma_thr_db_ch1__mask 0xff

#define ma_thr_db_ch1__shift 0x00

#define ma_thr_db_ch1__reset 0x18

//----------------------------------------------------------------thr_db_ch2---

// thr db ch2

#define ma_thr_db_ch2__a 73

#define ma_thr_db_ch2__len 8

#define ma_thr_db_ch2__mask 0xff

#define ma_thr_db_ch2__shift 0x00

#define ma_thr_db_ch2__reset 0x18

//----------------------------------------------------------------thr_db_ch3---

// threshold db ch3

#define ma_thr_db_ch3__a 74

#define ma_thr_db_ch3__len 8

#define ma_thr_db_ch3__mask 0xff

#define ma_thr_db_ch3__shift 0x00

#define ma_thr_db_ch3__reset 0x18

//---------------------------------------------------------------thr_lsb_ch0---

// thr lsb ch0

#define ma_thr_lsb_ch0__a 75

#define ma_thr_lsb_ch0__len 2

#define ma_thr_lsb_ch0__mask 0x03

#define ma_thr_lsb_ch0__shift 0x00

#define ma_thr_lsb_ch0__reset 0x00

//---------------------------------------------------------------thr_lsb_ch1---

// thr lsb ch1

#define ma_thr_lsb_ch1__a 75

#define ma_thr_lsb_ch1__len 2

#define ma_thr_lsb_ch1__mask 0x0c

#define ma_thr_lsb_ch1__shift 0x02

#define ma_thr_lsb_ch1__reset 0x00

//---------------------------------------------------------------thr_lsb_ch2---

// thr lsb ch2 1/4 db step

#define ma_thr_lsb_ch2__a 75

#define ma_thr_lsb_ch2__len 2

#define ma_thr_lsb_ch2__mask 0x30

#define ma_thr_lsb_ch2__shift 0x04

#define ma_thr_lsb_ch2__reset 0x00

//---------------------------------------------------------------thr_lsb_ch3---

// threshold lsb ch3

#define ma_thr_lsb_ch3__a 75

#define ma_thr_lsb_ch3__len 2

#define ma_thr_lsb_ch3__mask 0xc0

#define ma_thr_lsb_ch3__shift 0x06

#define ma_thr_lsb_ch3__reset 0x00

//-----------------------------------------------------------dcu_mon0.pm_mon---

// power mode monitor channel 0

#define ma_dcu_mon0__pm_mon__a 96

#define ma_dcu_mon0__pm_mon__len 2

#define ma_dcu_mon0__pm_mon__mask 0x03

#define ma_dcu_mon0__pm_mon__shift 0x00

#define ma_dcu_mon0__pm_mon__reset 0x00

//-----------------------------------------------------dcu_mon0.freqmode_mon---

// frequence mode monitor channel 0

#define ma_dcu_mon0__freqmode_mon__a 96

#define ma_dcu_mon0__freqmode_mon__len 3

#define ma_dcu_mon0__freqmode_mon__mask 0x70

#define ma_dcu_mon0__freqmode_mon__shift 0x04

#define ma_dcu_mon0__freqmode_mon__reset 0x00

//-------------------------------------------------------dcu_mon0.pps_passed---

// dcu0 pps completion indicator

#define ma_dcu_mon0__pps_passed__a 96

#define ma_dcu_mon0__pps_passed__len 1

#define ma_dcu_mon0__pps_passed__mask 0x80

#define ma_dcu_mon0__pps_passed__shift 0x07

#define ma_dcu_mon0__pps_passed__reset 0x00

//----------------------------------------------------------dcu_mon0.ocp_mon---

// ocp monitor channel 0

#define ma_dcu_mon0__ocp_mon__a 97

#define ma_dcu_mon0__ocp_mon__len 1

#define ma_dcu_mon0__ocp_mon__mask 0x01

#define ma_dcu_mon0__ocp_mon__shift 0x00

#define ma_dcu_mon0__ocp_mon__reset 0x00

//--------------------------------------------------------dcu_mon0.vcfly1_ok---

// cfly1 protection monitor channel 0.

#define ma_dcu_mon0__vcfly1_ok__a 97

#define ma_dcu_mon0__vcfly1_ok__len 1

#define ma_dcu_mon0__vcfly1_ok__mask 0x02

#define ma_dcu_mon0__vcfly1_ok__shift 0x01

#define ma_dcu_mon0__vcfly1_ok__reset 0x00

//--------------------------------------------------------dcu_mon0.vcfly2_ok---

// cfly2 protection monitor channel 0.

#define ma_dcu_mon0__vcfly2_ok__a 97

#define ma_dcu_mon0__vcfly2_ok__len 1

#define ma_dcu_mon0__vcfly2_ok__mask 0x04

#define ma_dcu_mon0__vcfly2_ok__shift 0x02

#define ma_dcu_mon0__vcfly2_ok__reset 0x00

//----------------------------------------------------------dcu_mon0.pvdd_ok---

// dcu0 pvdd monitor

#define ma_dcu_mon0__pvdd_ok__a 97

#define ma_dcu_mon0__pvdd_ok__len 1

#define ma_dcu_mon0__pvdd_ok__mask 0x08

#define ma_dcu_mon0__pvdd_ok__shift 0x03

#define ma_dcu_mon0__pvdd_ok__reset 0x00

//-----------------------------------------------------------dcu_mon0.vdd_ok---

// dcu0 vdd monitor

#define ma_dcu_mon0__vdd_ok__a 97

#define ma_dcu_mon0__vdd_ok__len 1

#define ma_dcu_mon0__vdd_ok__mask 0x10

#define ma_dcu_mon0__vdd_ok__shift 0x04

#define ma_dcu_mon0__vdd_ok__reset 0x00

//-------------------------------------------------------------dcu_mon0.mute---

// dcu0 mute monitor

#define ma_dcu_mon0__mute__a 97

#define ma_dcu_mon0__mute__len 1

#define ma_dcu_mon0__mute__mask 0x20

#define ma_dcu_mon0__mute__shift 0x05

#define ma_dcu_mon0__mute__reset 0x00

//------------------------------------------------------------dcu_mon0.m_mon---

// m sense monitor channel 0

#define ma_dcu_mon0__m_mon__a 98

#define ma_dcu_mon0__m_mon__len 8

#define ma_dcu_mon0__m_mon__mask 0xff

#define ma_dcu_mon0__m_mon__shift 0x00

#define ma_dcu_mon0__m_mon__reset 0x00

//-----------------------------------------------------------dcu_mon1.pm_mon---

// power mode monitor channel 1

#define ma_dcu_mon1__pm_mon__a 100

#define ma_dcu_mon1__pm_mon__len 2

#define ma_dcu_mon1__pm_mon__mask 0x03

#define ma_dcu_mon1__pm_mon__shift 0x00

#define ma_dcu_mon1__pm_mon__reset 0x00

//-----------------------------------------------------dcu_mon1.freqmode_mon---

// frequence mode monitor channel 1

#define ma_dcu_mon1__freqmode_mon__a 100

#define ma_dcu_mon1__freqmode_mon__len 3

#define ma_dcu_mon1__freqmode_mon__mask 0x70

#define ma_dcu_mon1__freqmode_mon__shift 0x04

#define ma_dcu_mon1__freqmode_mon__reset 0x00

//-------------------------------------------------------dcu_mon1.pps_passed---

// dcu1 pps completion indicator

#define ma_dcu_mon1__pps_passed__a 100

#define ma_dcu_mon1__pps_passed__len 1

#define ma_dcu_mon1__pps_passed__mask 0x80

#define ma_dcu_mon1__pps_passed__shift 0x07

#define ma_dcu_mon1__pps_passed__reset 0x00

//----------------------------------------------------------dcu_mon1.ocp_mon---

// ocp monitor channel 1

#define ma_dcu_mon1__ocp_mon__a 101

#define ma_dcu_mon1__ocp_mon__len 1

#define ma_dcu_mon1__ocp_mon__mask 0x01

#define ma_dcu_mon1__ocp_mon__shift 0x00

#define ma_dcu_mon1__ocp_mon__reset 0x00

//--------------------------------------------------------dcu_mon1.vcfly1_ok---

// cfly1 protcetion monitor channel 1

#define ma_dcu_mon1__vcfly1_ok__a 101

#define ma_dcu_mon1__vcfly1_ok__len 1

#define ma_dcu_mon1__vcfly1_ok__mask 0x02

#define ma_dcu_mon1__vcfly1_ok__shift 0x01

#define ma_dcu_mon1__vcfly1_ok__reset 0x00

//--------------------------------------------------------dcu_mon1.vcfly2_ok---

// cfly2 protection monitor channel 1

#define ma_dcu_mon1__vcfly2_ok__a 101

#define ma_dcu_mon1__vcfly2_ok__len 1

#define ma_dcu_mon1__vcfly2_ok__mask 0x04

#define ma_dcu_mon1__vcfly2_ok__shift 0x02

#define ma_dcu_mon1__vcfly2_ok__reset 0x00

//----------------------------------------------------------dcu_mon1.pvdd_ok---

// dcu1 pvdd monitor

#define ma_dcu_mon1__pvdd_ok__a 101

#define ma_dcu_mon1__pvdd_ok__len 1

#define ma_dcu_mon1__pvdd_ok__mask 0x08

#define ma_dcu_mon1__pvdd_ok__shift 0x03

#define ma_dcu_mon1__pvdd_ok__reset 0x00

//-----------------------------------------------------------dcu_mon1.vdd_ok---

// dcu1 vdd monitor

#define ma_dcu_mon1__vdd_ok__a 101

#define ma_dcu_mon1__vdd_ok__len 1

#define ma_dcu_mon1__vdd_ok__mask 0x10

#define ma_dcu_mon1__vdd_ok__shift 0x04

#define ma_dcu_mon1__vdd_ok__reset 0x00

//-------------------------------------------------------------dcu_mon1.mute---

// dcu1 mute monitor

#define ma_dcu_mon1__mute__a 101

#define ma_dcu_mon1__mute__len 1

#define ma_dcu_mon1__mute__mask 0x20

#define ma_dcu_mon1__mute__shift 0x05

#define ma_dcu_mon1__mute__reset 0x00

//------------------------------------------------------------dcu_mon1.m_mon---

// m sense monitor channel 1

#define ma_dcu_mon1__m_mon__a 102

#define ma_dcu_mon1__m_mon__len 8

#define ma_dcu_mon1__m_mon__mask 0xff

#define ma_dcu_mon1__m_mon__shift 0x00

#define ma_dcu_mon1__m_mon__reset 0x00

//--------------------------------------------------------dcu_mon0.sw_enable---

// dcu0 switch enable monitor

#define ma_dcu_mon0__sw_enable__a 104

#define ma_dcu_mon0__sw_enable__len 1

#define ma_dcu_mon0__sw_enable__mask 0x40

#define ma_dcu_mon0__sw_enable__shift 0x06

#define ma_dcu_mon0__sw_enable__reset 0x00

//--------------------------------------------------------dcu_mon1.sw_enable---

// dcu1 switch enable monitor

#define ma_dcu_mon1__sw_enable__a 104

#define ma_dcu_mon1__sw_enable__len 1

#define ma_dcu_mon1__sw_enable__mask 0x80

#define ma_dcu_mon1__sw_enable__shift 0x07

#define ma_dcu_mon1__sw_enable__reset 0x00

//------------------------------------------------------------hvboot0_ok_mon---

// hvboot0_ok for test/debug

#define ma_hvboot0_ok_mon__a 105

#define ma_hvboot0_ok_mon__len 1

#define ma_hvboot0_ok_mon__mask 0x40

#define ma_hvboot0_ok_mon__shift 0x06

#define ma_hvboot0_ok_mon__reset 0x00

//------------------------------------------------------------hvboot1_ok_mon---

// hvboot1_ok for test/debug

#define ma_hvboot1_ok_mon__a 105

#define ma_hvboot1_ok_mon__len 1

#define ma_hvboot1_ok_mon__mask 0x80

#define ma_hvboot1_ok_mon__shift 0x07

#define ma_hvboot1_ok_mon__reset 0x00

//-----------------------------------------------------------------error_acc---

// accumulated errors, at and after triggering

#define ma_error_acc__a 109

#define ma_error_acc__len 8

#define ma_error_acc__mask 0xff

#define ma_error_acc__shift 0x00

#define ma_error_acc__reset 0x00

//-------------------------------------------------------------i2s_data_rate---

// detected i2s data rate: 00/01/10 = x1/x2/x4

#define ma_i2s_data_rate__a 116

#define ma_i2s_data_rate__len 2

#define ma_i2s_data_rate__mask 0x03

#define ma_i2s_data_rate__shift 0x00

#define ma_i2s_data_rate__reset 0x00

//---------------------------------------------------------audio_in_mode_mon---

// audio input mode monitor

#define ma_audio_in_mode_mon__a 116

#define ma_audio_in_mode_mon__len 3

#define ma_audio_in_mode_mon__mask 0x1c

#define ma_audio_in_mode_mon__shift 0x02

#define ma_audio_in_mode_mon__reset 0x00

//------------------------------------------------------------------msel_mon---

// msel[2:0] monitor register

#define ma_msel_mon__a 117

#define ma_msel_mon__len 3

#define ma_msel_mon__mask 0x07

#define ma_msel_mon__shift 0x00

#define ma_msel_mon__reset 0x00

//---------------------------------------------------------------------error---

// current error flag monitor reg - for app. ctrl.

#define ma_error__a 124

#define ma_error__len 8

#define ma_error__mask 0xff

#define ma_error__shift 0x00

#define ma_error__reset 0x00

//----------------------------------------------------audio_proc_limiter_mon---

// b7-b4: channel 3-0 limiter active

#define ma_audio_proc_limiter_mon__a 126

#define ma_audio_proc_limiter_mon__len 4

#define ma_audio_proc_limiter_mon__mask 0xf0

#define ma_audio_proc_limiter_mon__shift 0x04

#define ma_audio_proc_limiter_mon__reset 0x00

//-------------------------------------------------------audio_proc_clip_mon---

// b3-b0: channel 3-0 clipping monitor

#define ma_audio_proc_clip_mon__a 126

#define ma_audio_proc_clip_mon__len 4

#define ma_audio_proc_clip_mon__mask 0x0f

#define ma_audio_proc_clip_mon__shift 0x00

#define ma_audio_proc_clip_mon__reset 0x00

#endif /* Tue Nov 14 13:36:42 2017*/相关文章:

【005_音频开发_基础篇_ALSA_Codec_驱动-MA120x0P功放】

005_音频开发_基础篇_ALSA_Codec_驱动-MA120x0P功放 文章目录 005_音频开发_基础篇_ALSA_Codec_驱动-MA120x0P功放创作背景MA120X0P输出模式BTLSEPBTLSEBTL 硬件配置方式/硬件Limiter限幅器限幅器作用过程 主要寄存器操作指令 ma120x0p.cma120x0p.h 创作背景 学历代表过去、能…...

2、FreeCAD模块与核心架构总结

FreeCAD作为一个开源的3D建模软件,其内部架构由多个模块组成,这些模块共同协作以支持软件的各种功能。本总结将基于提供的参考文档,对FreeCAD的核心模块、架构特性以及启动过程进行翻译和详细阐述。 核心模块概览 FreeCAD的核心模块主要包括…...

MySQL为什么默认引擎是InnoDB?

因为InnoDB特别强大,其支持很多东西 1.支持事务: 意味着对于一个复杂的SQL语句要么全部执行成功,要么全部失败,因为其底层是原子性的 2.支持并发(行级并发) 意味着面对高并发,多个用户可以同时访问一个表的不同行,不同行之间上锁,而不是给一个表上锁,这样就提高了高并发的性能和…...

)

K8s: Helm搭建mongodb集群(1)

mongodb 集群搭建 mongdb 部署前 需要创建 pvc, pv 和 sc,如果在云上会自动创建helm 应用中心: https://artifacthub.io 1 )Helm 安装 mongodb A. 无本地存储配置,重启数据消失 在 https://artifacthub.io/packages/helm/bitnami/mongodb…...

应用分层和企业规范

目录 一、应用分层 1、介绍 (1)为什么需要应用分层? (2)如何分层?(三层架构) MVC 和 三层架构的区别和联系 高内聚: 低耦合: 2、代码重构 controlle…...

Flutter笔记:Widgets Easier组件库(1)使用各式边框

Flutter笔记 Widgets Easier组件库(1):使用边框 - 文章信息 - Author: 李俊才 (jcLee95) Visit me at CSDN: https://jclee95.blog.csdn.netMy WebSite:http://thispage.tech/Email: 291148484163.com. Shenzhen ChinaAddress o…...

OpenHarmony实战开发-上传文件

Web组件支持前端页面选择文件上传功能,应用开发者可以使用onShowFileSelector()接口来处理前端页面文件上传的请求。 下面的示例中,当用户在前端页面点击文件上传按钮,应用侧在onShowFileSelector()接口中收到文件上传请求,在此接…...

外贸企业邮箱是什么?做外贸企业邮箱哪个好?

外贸企业邮箱是什么?外贸企业在进行跨国沟通时必不可少的工具就是外贸企业邮箱,外贸企业邮箱需要具备的条件就是海外邮件抵达率高、安全稳定、多语言沟通。而我们又怎么选择一个适合的外贸企业邮箱呢?小编今天带您一起了解。 一、外贸企业邮…...

写一个简单的程序

思路分析: 1. 导入必要的库 首先,确保你的项目中包含了AWT或Swing库,因为我们将使用它们来创建图形界面。 import javax.swing.*; import java.awt.*; import java.awt.event.ActionEvent; import java.awt.event.ActionListener; import j…...

CentOS安装Docker指南

Docker安装与配置教程 Docker作为一种轻量级的虚拟化技术,在现代软件开发和运维中扮演着重要的角色。下面,我将以技术博主的身份,向大家详细介绍如何在Linux系统上安装和配置Docker,特别是如何设置Docker的监听地址和端口&#x…...

python绘图(pandas)

matplotlib绘图 import pandas as pd abs_path rF:\Python\learn\python附件\pythonCsv\data.csv df pd.read_csv(abs_path, encodinggbk) # apply根据多列生成新的一个列的操作,用apply df[new_score] df.apply(lambda x : x.数学 x.语文, axis1)# 最后几行 …...

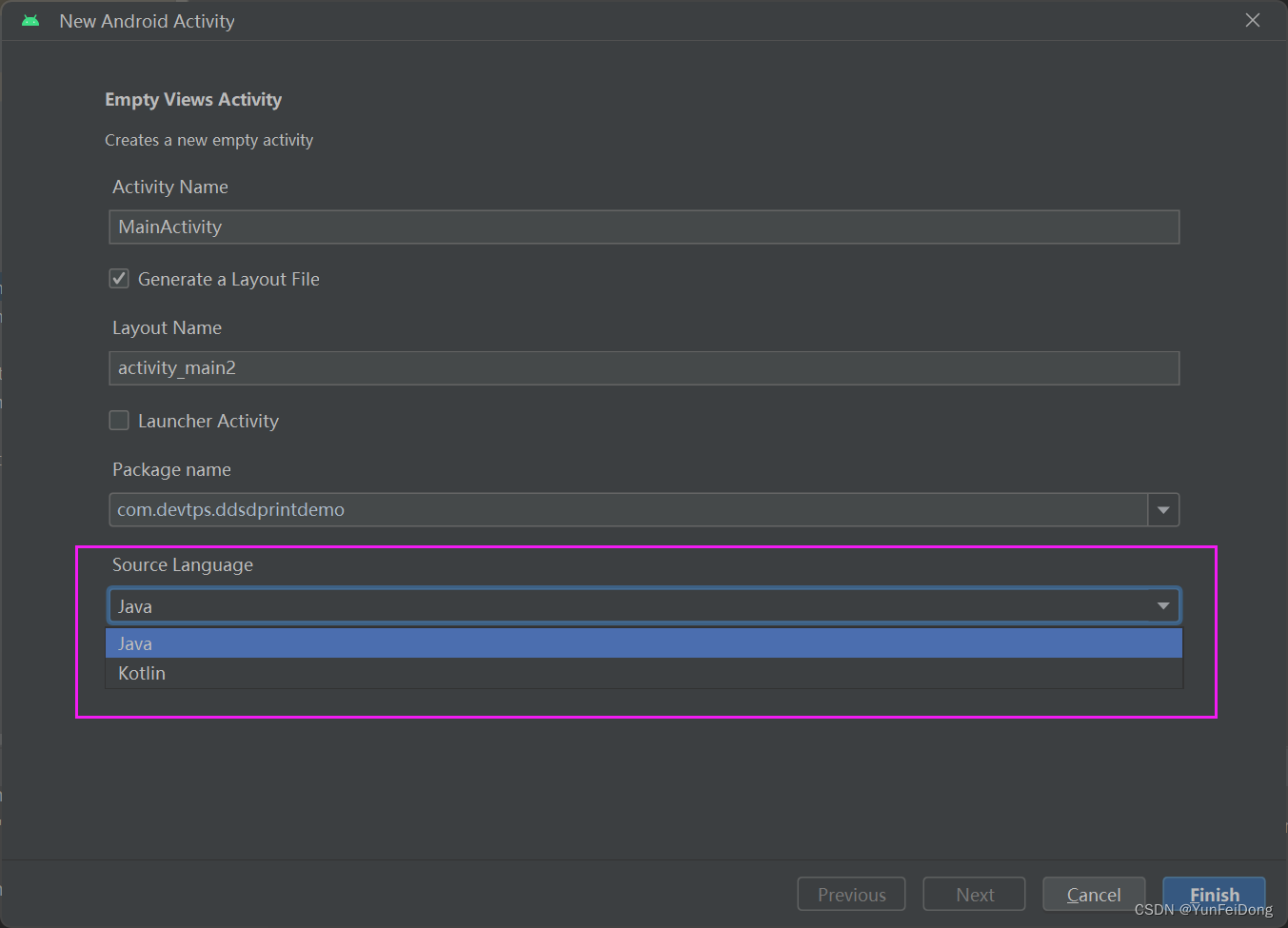

Android(Java)项目支持Kotlin语言开发

Android(Java)项目通过相关Kotlin设置后,允许同时使用Java语言和Kotlin语言进行开发代码的。 示例环境: Android Studio Giraffe | 2022.3.1 Patch 3 Java 8 Kotlin 1.9.20 设置Kotlin选项: 第一步:在项…...

Terraform创建模块

模块就是包含一组Terraform代码的文件夹,可以通过模块直接使用别人编写好的Terraform代码来创建资源。 Terraform模块是编写高质量Terraform代码,提升代码复用性的重要手段,可以说,一个成熟的生产环境应该是由数个可信成熟的模块组…...

《华为鸿蒙:从备胎到主角的崛起之路》

华为鸿蒙操作系统的发展历程可以追溯到 2012 年,当时华为开始规划自有操作系统鸿蒙 OS。然而,直到 2019 年 5 月,鸿蒙才正式进入开发阶段。 2019 年 8 月 9 日,华为正式发布了鸿蒙操作系统。 鸿蒙系统的首个版本是于 2019 年推出…...

——Verilog语法及ModelSim使用)

FPGA学习笔记(2)——Verilog语法及ModelSim使用

1.1 语法 1、赋值语句 和 < 为阻塞赋值,当该语句结束时,下一个语句才开始执行,串行执行 < 为非阻塞幅值,该语句和整个语句块同时执行,并行执行 1.2 ModelSim使用 1、修改源文件路径:File -> …...

2024年十大AI工具,让你的工作学习效率飞跃

在这个迅速变化的数字时代,人工智能技术正在以前所未有的速度发展和革新。AI技术不仅深入科研、医疗和教育等领域,还广泛应用于日常生活和商业活动中。本文梳理了2024年十款最好用的AI工具,它们各有特色,能极大提升工作效率和生活…...

linux之NAMP

linux之NAMP Nmap(Network Mapper)是一个开源的网络扫描和安全审计工具。它被设计用来快速地扫描大型网络,尽管它也可以对单个主机进行有效的扫描。Nmap利用原始IP数据包以多种方式探测目标网络上的主机、服务(应用程序名称和版本…...

uniapp 禁止截屏(应用内,保护隐私)插件 Ba-ScreenShot

禁止截屏(应用内,保护隐私) Ba-ScreenShot 简介(下载地址) Ba-ScreenShot 是一款uniapp禁止应用内截屏的插件,保护隐私,支持禁止截屏、放开截屏 截图展示 也可关注博客,实时更新最…...

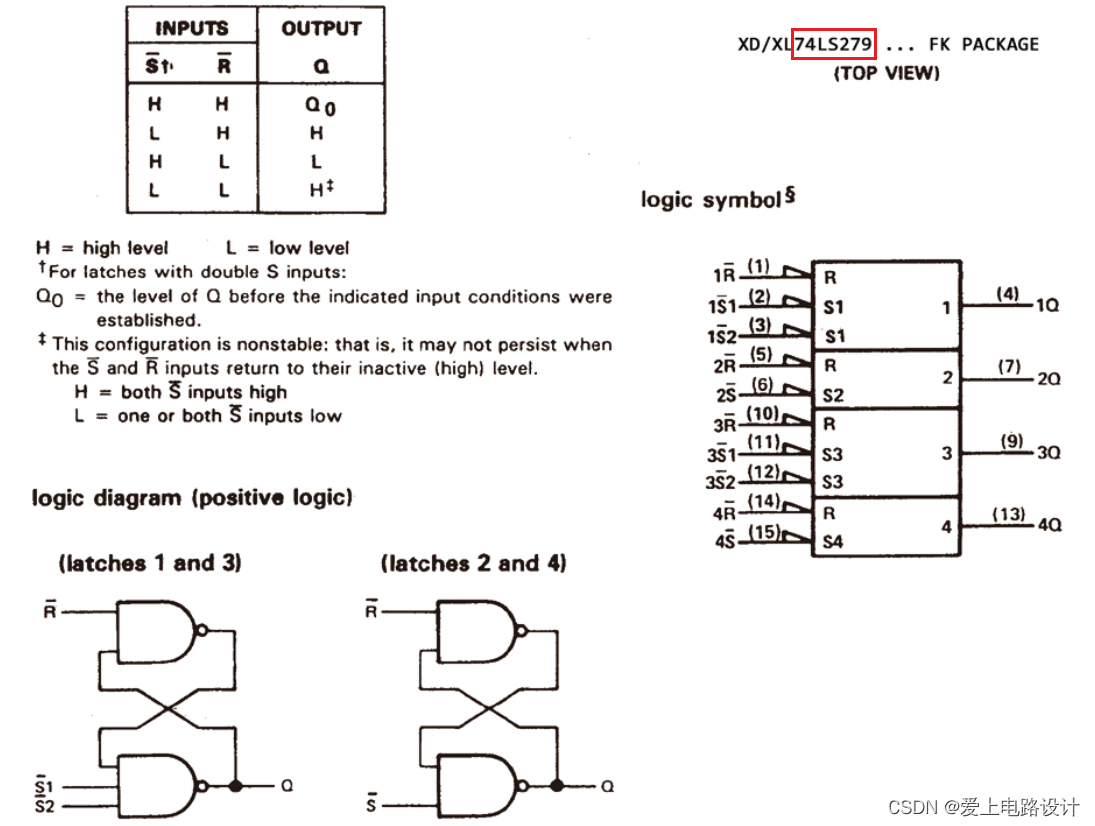

数字电路-5路呼叫显示电路和8路抢答器电路

本内容涉及两个电路,分别为5路呼叫显示电路和8路抢答器电路,包含Multisim仿真原文件,为掌握FPGA做个铺垫。紫色文字是超链接,点击自动跳转至相关博文。持续更新,原创不易! 目录: 一、5路呼叫显…...

C++中的函数签名

前言: 很多C初学者会发现函数签名这一概念在C的学习过程中经常出现,然而很多人往往不太了解函数签名包括些什么,本文章将从一个初学者的角度出发,详细解释函数签名这一概念。 在C中,函数签名用于唯一地识别函数重载。…...

实战指南:为spring boot项目快速配置最优jdk环境,助力应用高效部署

最近在准备一个Spring Boot项目时,发现JDK环境配置这个看似简单的环节其实藏着不少学问。特别是当项目需要兼顾开发效率和生产环境稳定性时,合理的JDK配置方案就显得尤为重要。今天就来分享下我的实战经验,以及如何利用工具快速搞定这些配置。…...

FPGA新手避雷指南:你的第一个呼吸灯项目可能卡在这几个Vivado仿真和引脚分配问题上

FPGA新手避雷指南:从仿真到引脚分配的完整呼吸灯实战 第一次在FPGA上实现呼吸灯效果,本该是充满成就感的时刻。但当你按照教程一步步操作,点击"Generate Bitstream"后,板子上的LED却毫无反应——这种挫败感我太熟悉了。…...

Vivado MIG IP核实战:DDR3控制器配置与仿真全流程解析

1. Vivado MIG IP核与DDR3控制器基础认知 第一次接触DDR3控制器时,我被那些密密麻麻的时序图吓得不轻。直到发现Xilinx的MIG(Memory Interface Generator)IP核,才明白原来FPGA开发可以这么"偷懒"。这个IP核就像个贴心的…...

方案)

打破系统壁垒:从 Android 到 macOS,打造全平台统一终端管理(MDM)方案

目录 什么是统一设备管理? 一、引言 二、为什么跨平台设备管理至关重要 三、统一设备管理平台的核心功能 3.1 多平台生态整合 3.2 全设备生命周期管理 3.3 统一策略配置 3.4 广泛的行业适用性 四、实施统一设备管理的优势 五、企业设备管理的未来趋势 六…...

别只盯着协议!用TC8测试案例深度解读车载网络中的ARP与ICMP:安全与稳定的隐藏关卡

车载以太网底层协议实战:从TC8测试案例看ARP与ICMP的安全设计 当一辆现代汽车以100km/h行驶时,其车载网络每秒需要处理超过5000条网络报文。这些报文中的绝大多数,都由ARP和ICMP这样的基础协议承载。在传统IT领域被视为"简单"的协议…...

工程仿真平台OpenRocket:从物理试验到数字孪生的技术跃迁

工程仿真平台OpenRocket:从物理试验到数字孪生的技术跃迁 【免费下载链接】openrocket Model-rocketry aerodynamics and trajectory simulation software 项目地址: https://gitcode.com/GitHub_Trending/op/openrocket 在现代工程设计领域,物理…...

ComfyUI-FramePackWrapper功能选择指南:如何根据资源控制与使用便捷性选择最优方案

ComfyUI-FramePackWrapper功能选择指南:如何根据资源控制与使用便捷性选择最优方案 【免费下载链接】ComfyUI-FramePackWrapper 项目地址: https://gitcode.com/gh_mirrors/co/ComfyUI-FramePackWrapper ComfyUI-FramePackWrapper作为一款高效的AI视频生成插…...

6大维度深度测评:如何挑选最可靠的开源付费墙绕过工具?

6大维度深度测评:如何挑选最可靠的开源付费墙绕过工具? 【免费下载链接】bypass-paywalls-chrome-clean 项目地址: https://gitcode.com/GitHub_Trending/by/bypass-paywalls-chrome-clean 在数字阅读时代,优质内容的付费壁垒逐渐形成…...

)

保姆级教程:在OBBDetection项目中为DOTA数据集定制检测结果可视化(mmdetection 2.2)

深度定制OBBDetection检测结果可视化:DOTA数据集高级实践指南 在旋转目标检测领域,DOTA数据集因其复杂的航拍场景和多角度目标特性,对结果可视化提出了独特挑战。本文将带您从零构建一套完整的可视化解决方案,涵盖从基础配置到高级…...

从云端到指尖:巧用Aspose组件实现Office/PDF文档秒级HTML预览,攻克移动端大文件访问瓶颈

1. 移动端大文件预览的痛点与解决思路 最近接手一个企业级项目时,遇到了一个非常典型的场景:用户通过PC端上传各种办公文档(Word、Excel、PPT、PDF),需要在移动端随时查看。但当文件体积较大时(比如超过50M…...