Xilinx FPGA:vivado关于真双端口的串口传输数据的实验

一、实验内容

用一个真双端RAM,端口A和端口B同时向RAM里写入数据0-99,A端口读出单数并存入单端口RAM1中,B端口读出双数并存入但端口RAM2中,当检测到按键1到来时将RAM1中的单数读出显示到PC端,当检测到按键2到来时,将RAM2中的双数显示到pc端。

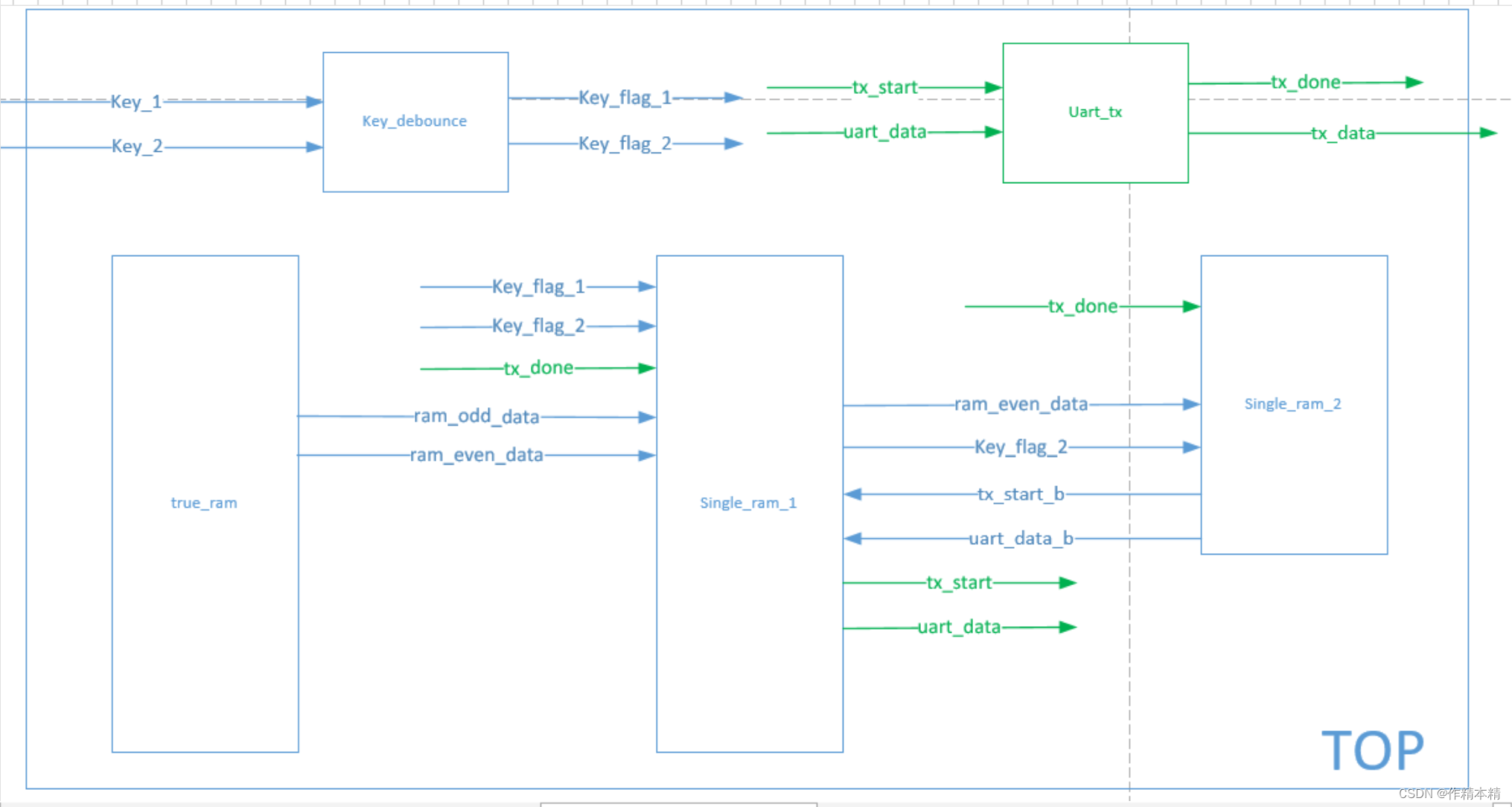

二、信号流向图

TIPS:这里我本来想将single_ram_1和single_ram_2分成两个单独的模块,但是经过实验后发现,如果分成两个单独的模块的话会导致:

①两个单端RAM模块的tx_start(0或1)都会有值给uart_tx模块,即使是RAM1给【1】,RAM2中没有值【0】,uart_tx模块是无法判断 tx_start 到底来自于哪个模块,所以此时uart_tx模块只是能接收到一个tx_start的脉冲信号,但是无法判断信号来自哪个RAM模块,无法获取到相应的uart_data ,最终导致tx_flag都无法变成高电平,那就更不会返回给RAM模块tx_done信号了。

②如果单独为了正确信号能赋值给tx_start而重新去写一个ctrl模块的话,那么在ctrl模块中将无法使用判断条件,因为我们将状态作为了赋值条件而不仅仅是key_flag信号。

那么我的解决方法就是把single_ram_2例化到single_ram_1当中,将single_ram_2输出的数据(uart_data_b及tx_start_b)和single_ram_1输出的数据(douta即tx_start_a)全部放在一个模块即single_ram_1中去做判断,但是我们仍然无法将single_ram_2的状态作为赋值的条件,所以只能采用这种比较粗暴的方式,也就是除了( cur_state == REG || cur_state == READ )时候tx_start <= tx_start_a ;那么其他情况就是tx_start <= tx_start_b ; uart_data的处理也是同样。详见后面程序。

其实最好的方式是将single_ram_2和single_ram_1写在同一个模块中,程序放在文章最后了。

三、程序设计

(1)按键消抖模块:

这里注意key1和key2不能使用同一个计数器,不然在同一个模块中也会判断出问题。

`timescale 1ns / 1ps

module key_debounce(input sys_clk ,input rst_n ,input key1 ,input key2 ,output key_flag_1 ,output key_flag_2);

// parameter delay = 100_000_0 ; //20msparameter delay = 100;// 测试用reg[19:0] cnt1 ;reg[19:0] cnt2 ;key_flag_1 always@(posedge sys_clk )if(!rst_n)cnt1 <= 0 ;else if ( key1 == 0 )beginif ( cnt1 == delay -1 )cnt1 <= cnt1 ;else cnt1 <= cnt1 +1 ;endelsecnt1 <= 0 ;assign key_flag_1 = ( cnt1 == delay -2 )?1:0 ;///key_flag_2always@(posedge sys_clk )if(!rst_n)cnt2 <= 0 ;else if ( key2 == 0 )beginif ( cnt2 == delay -1 )cnt2 <= cnt2 ;else cnt2 <= cnt2 +1 ;endelsecnt2 <= 0 ;assign key_flag_2 = ( cnt2 == delay -2 )?1:0 ; endmodule

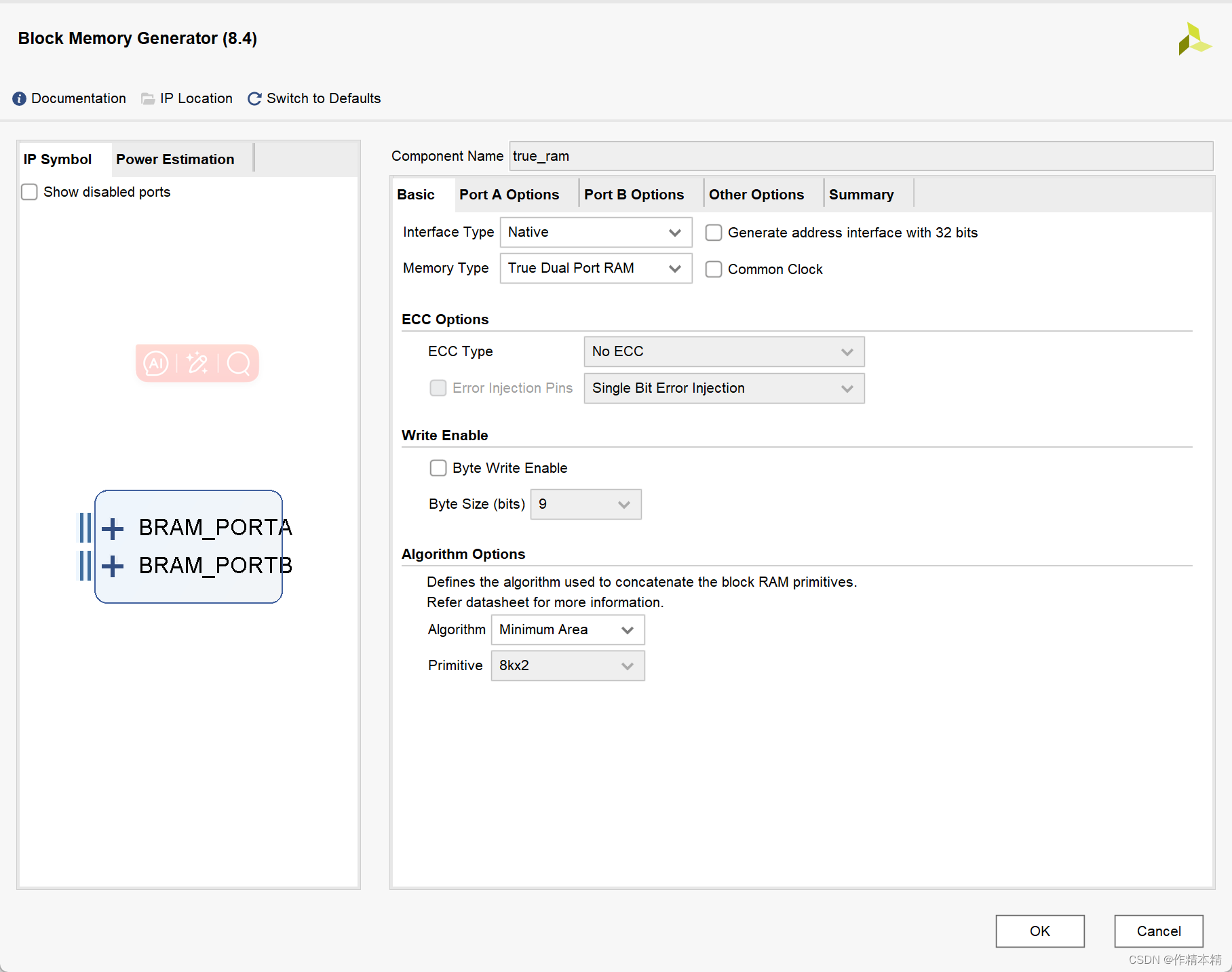

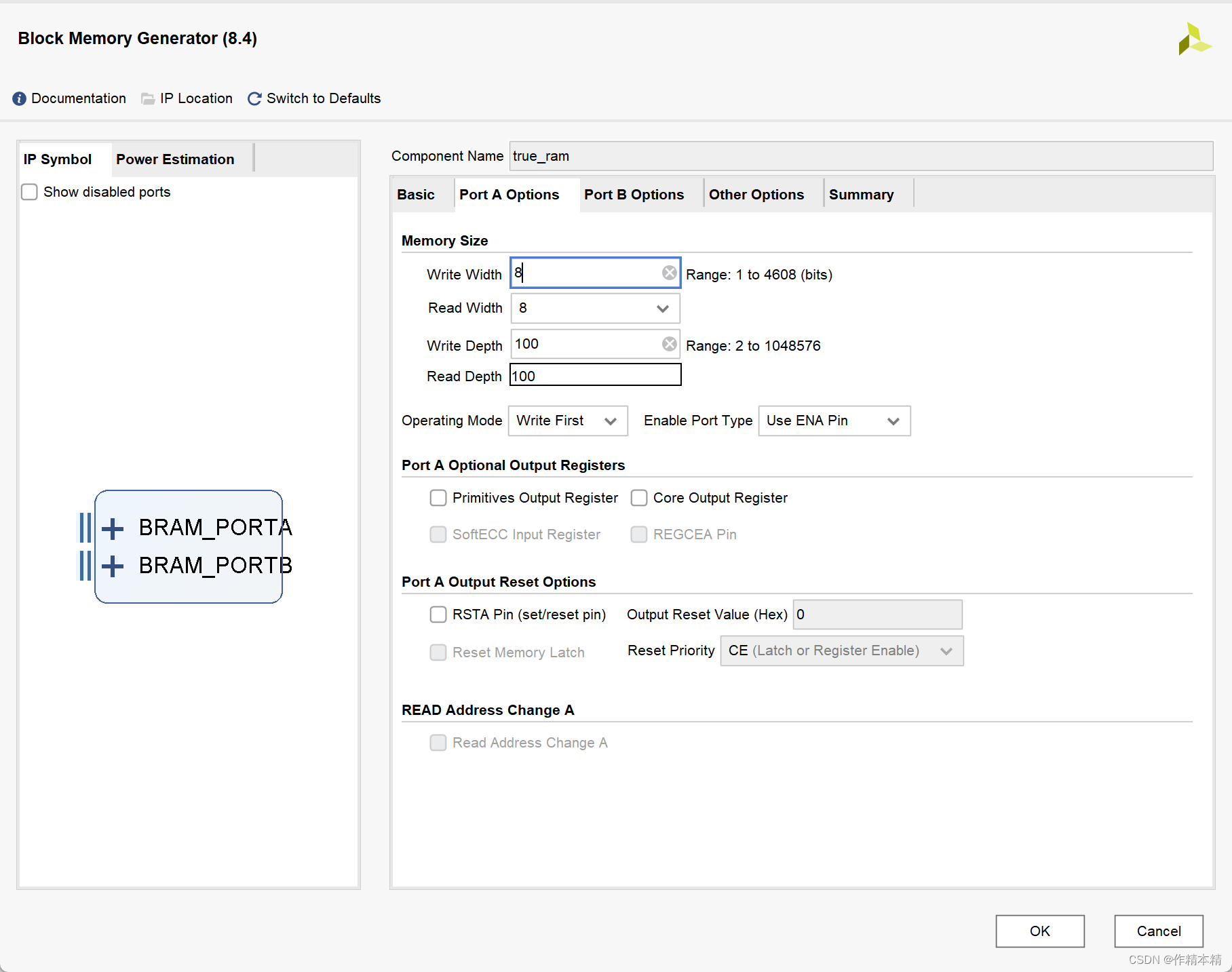

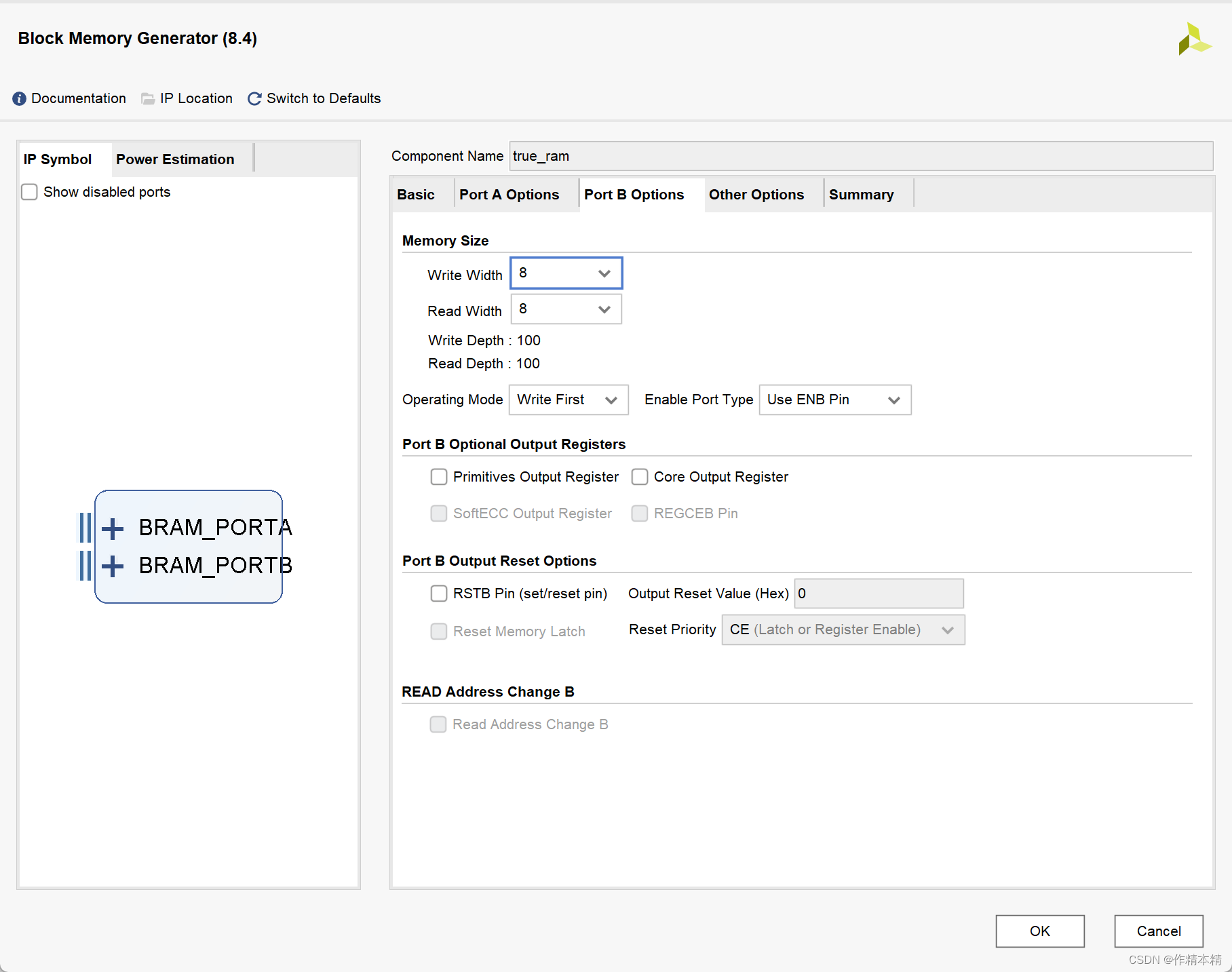

(2)真双端模块:

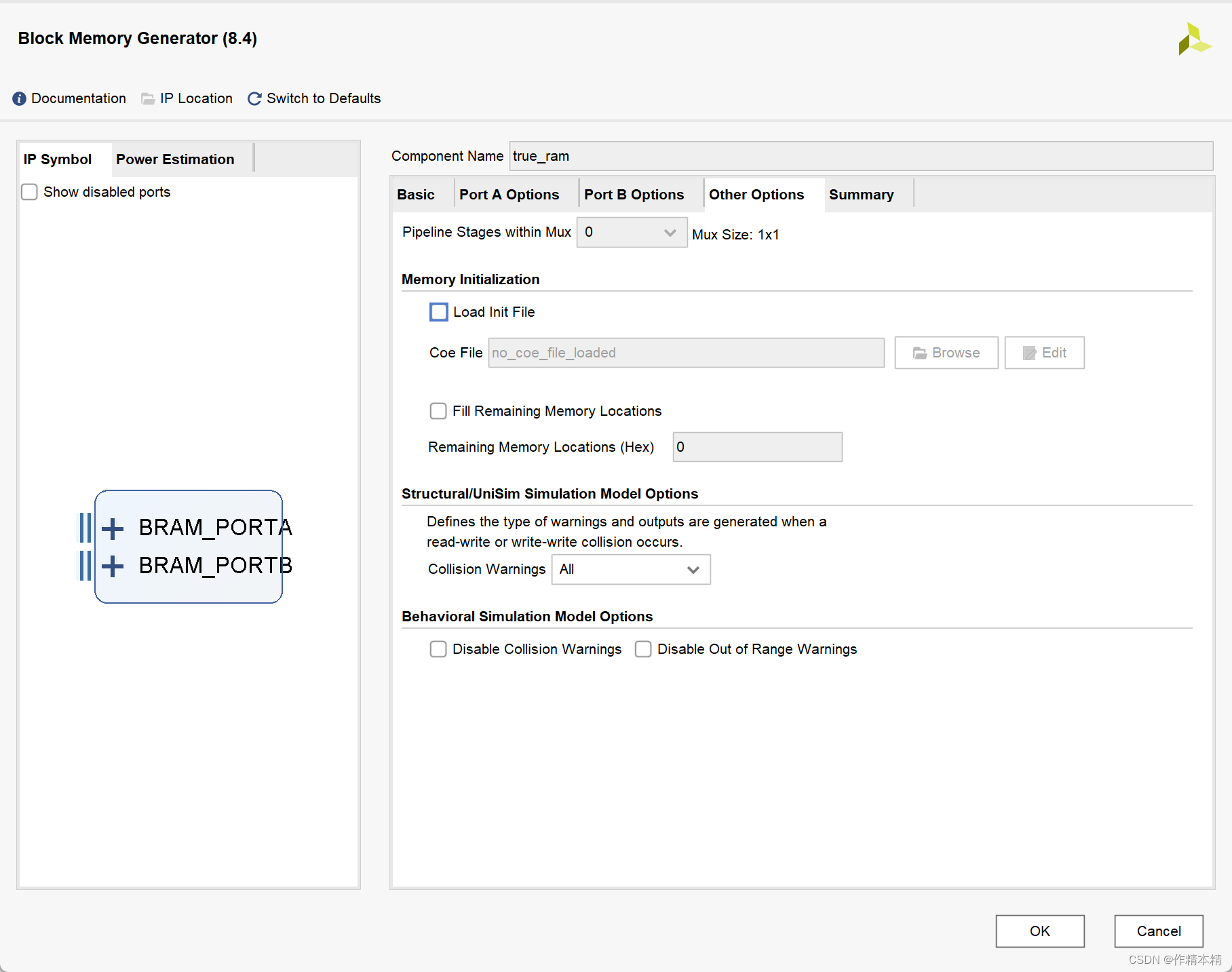

IP参数:

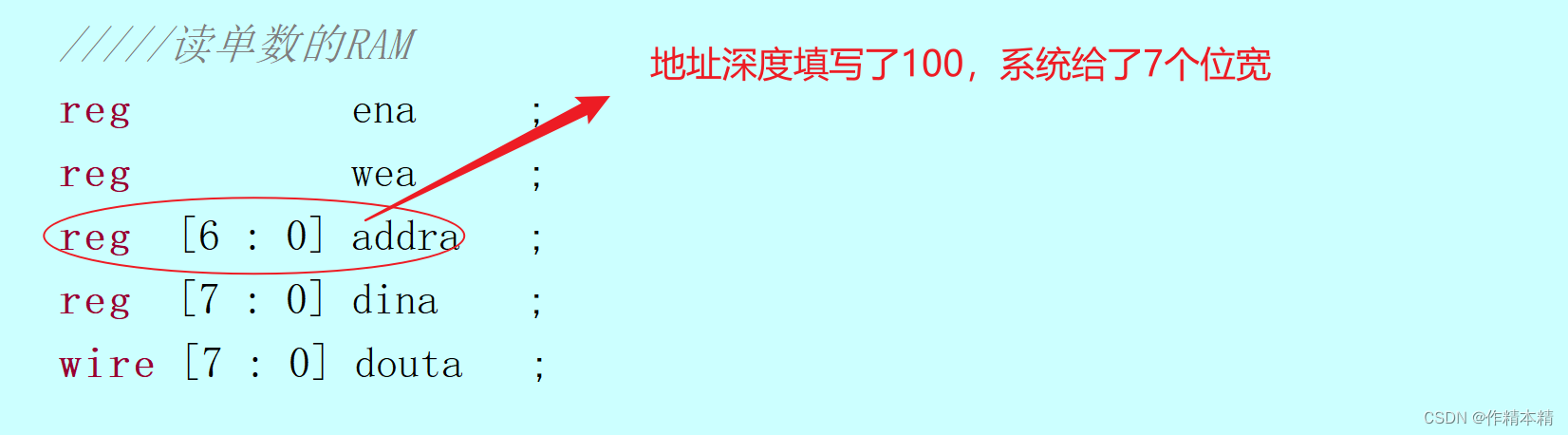

`timescale 1ns / 1ps

module the_true_ram(input sys_clk ,input rst_n ,output [7:0] ram_odd_data ,output [7:0] ram_even_data);A端口reg wea ;reg [6 : 0] addra ;reg [7 : 0] dina ;wire [7 : 0] douta ;always@(posedge sys_clk )if(!rst_n)wea <= 0 ;else if ( addra >= 99 )wea <= 0 ;elsewea <= 1 ;always@(posedge sys_clk )if(!rst_n)addra <= 0 ;else if ( addra >= 99 )addra <= 99 ;elseaddra <= addra +1 ;always@(posedge sys_clk )if(!rst_n)dina <= 0 ;else if (dina >= 99)dina <= 99 ;elsedina <= dina +1 ;wire [7:0] data_a ;assign data_a = douta ;assign ram_odd_data = (data_a%2 == 1)?data_a : ram_odd_data ;///b端口reg web ; reg [6 : 0] addrb ;reg [7 : 0] dinb ;wire [7 : 0] doutb ;always@(posedge sys_clk )if(!rst_n)web <= 0 ;else if ( addrb >= 99 )web <= 0 ;elseweb <= 1 ;always@(posedge sys_clk )if(!rst_n)addrb <= 0 ;else if ( addrb >= 99 )addrb <= 99 ;elseaddrb <= addrb +1 ;always@(posedge sys_clk )if(!rst_n)dinb <= 0 ;else if ( dinb >= 99 )dinb <= 99 ;elsedinb <= dinb +1 ;wire[7:0] data_b ;assign data_b = doutb ;assign ram_even_data = (data_b %2 == 0 )? data_b : ram_even_data ;//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

true_ram your_instance_name (.clka(sys_clk ), // input wire clka.ena(1), // input wire ena.wea(wea), // input wire [0 : 0] wea.addra(addra), // input wire [6 : 0] addra.dina(dina), // input wire [7 : 0] dina.douta(douta), // output wire [7 : 0] douta.clkb(sys_clk ), // input wire clkb.enb(1), // input wire enb.web(web), // input wire [0 : 0] web.addrb(addrb), // input wire [6 : 0] addrb.dinb(dinb), // input wire [7 : 0] dinb.doutb(doutb) // output wire [7 : 0] doutb

);

// INST_TAG_END ------ End INSTANTIATION Template ---------endmodule

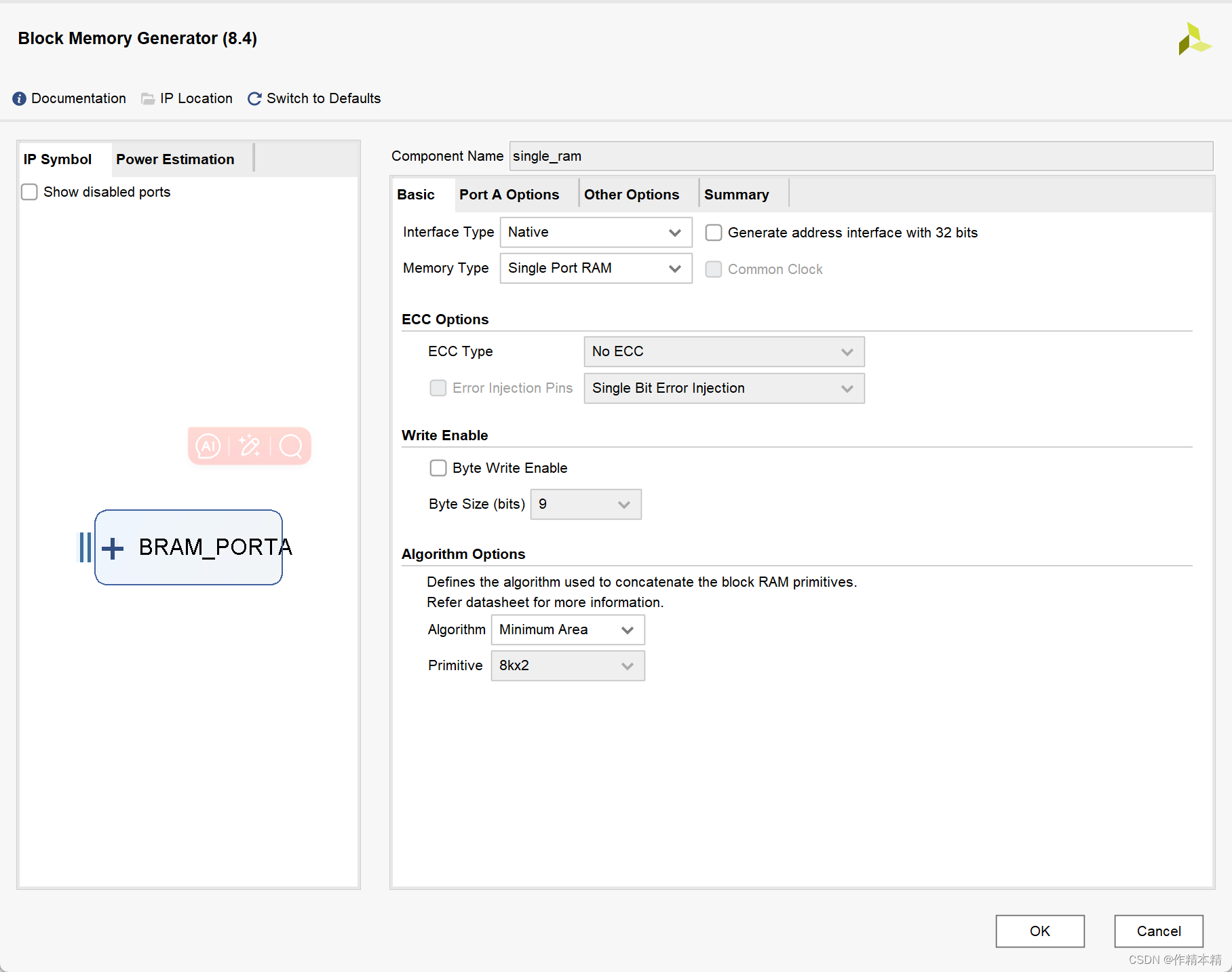

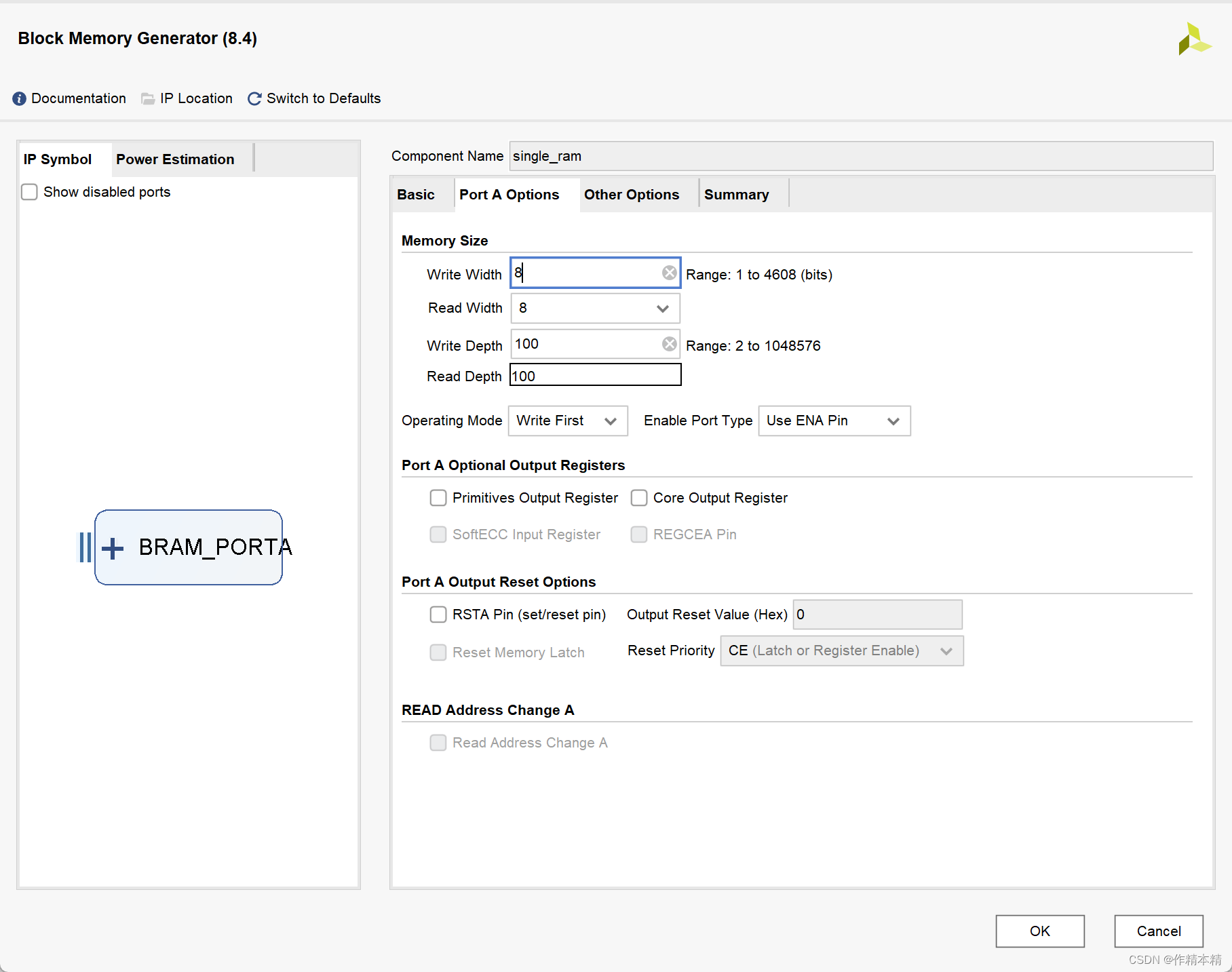

(3)单端RAM2模块:

但其实深度在50就够用了。(100里面的奇数和偶数50)

`timescale 1ns / 1ps

module single_ram_2_FMS(input sys_clk ,input rst_n ,input key_flag_2 ,input tx_done ,input [7:0] ram_even_data ,output reg tx_start_b ,output reg[7:0] uart_data_b);存双数的RAMreg ena ;reg [0 : 0] wea ;reg [6 : 0] addra ;reg [7 : 0] dina ;wire [7 : 0] douta ;//先写再读出localparam IDLE = 3'd0 ;localparam WRITE = 3'd1 ;localparam REG = 3'd2 ;localparam READ = 3'd3 ;reg[2:0] cur_state ;reg[2:0] next_state ;//state1always@(posedge sys_clk )if(!rst_n)cur_state <= IDLE ;else cur_state <= next_state ;//state2always@(*)case(cur_state)IDLE :beginnext_state = WRITE ;endWRITE :beginif ( key_flag_2 )next_state = REG ;elsenext_state = cur_state ;endREG :beginnext_state = READ ;endREAD :beginif(addra == 49)next_state = IDLE ;elsenext_state <= cur_state ;enddefault:;endcase//state3always@(posedge sys_clk )if(!rst_n)beginena <= 0 ;wea <= 0 ;addra <= 0 ;dina <= 0 ;tx_start_b <= 0 ;endelsecase(cur_state)IDLE :beginena <= 0 ;wea <= 0 ;addra <= 0 ;dina <= ram_even_data ;endWRITE :beginena <= 1 ;wea <= 1 ;if(addra == 49)addra <= 49 ;elseaddra <= addra +1 ;dina <= ram_even_data ;endREG :beginaddra <= 0 ;ena <= 0 ;wea <= 0 ;dina <= 0 ;tx_start_b <= 1 ;endREAD :beginena <= 1 ;wea <= 0 ;dina<= 0 ;if(tx_done)begintx_start_b <= 1 ;addra <= addra +1 ;endelse begintx_start_b <= 0 ;addra <= addra ;endenddefault:;endcase//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

single_ram ram2 (.clka(sys_clk ), // input wire clka.ena(ena), // input wire ena.wea(wea), // input wire [0 : 0] wea.addra(addra), // input wire [6 : 0] addra.dina(dina), // input wire [7 : 0] dina .douta(douta) // output wire [7 : 0] douta

);

// INST_TAG_END ------ End INSTANTIATION Template ---------always@(posedge sys_clk )if(!rst_n)uart_data_b <= 0 ;else if ( cur_state == READ )uart_data_b <= douta ;elseuart_data_b <= uart_data_b ;always@(posedge sys_clk )if(!rst_n)tx_start_b <= 0 ;else if ( cur_state == REG || cur_state == READ )tx_start_b <= 1 ;elsetx_start_b <= tx_start_b ; endmodule

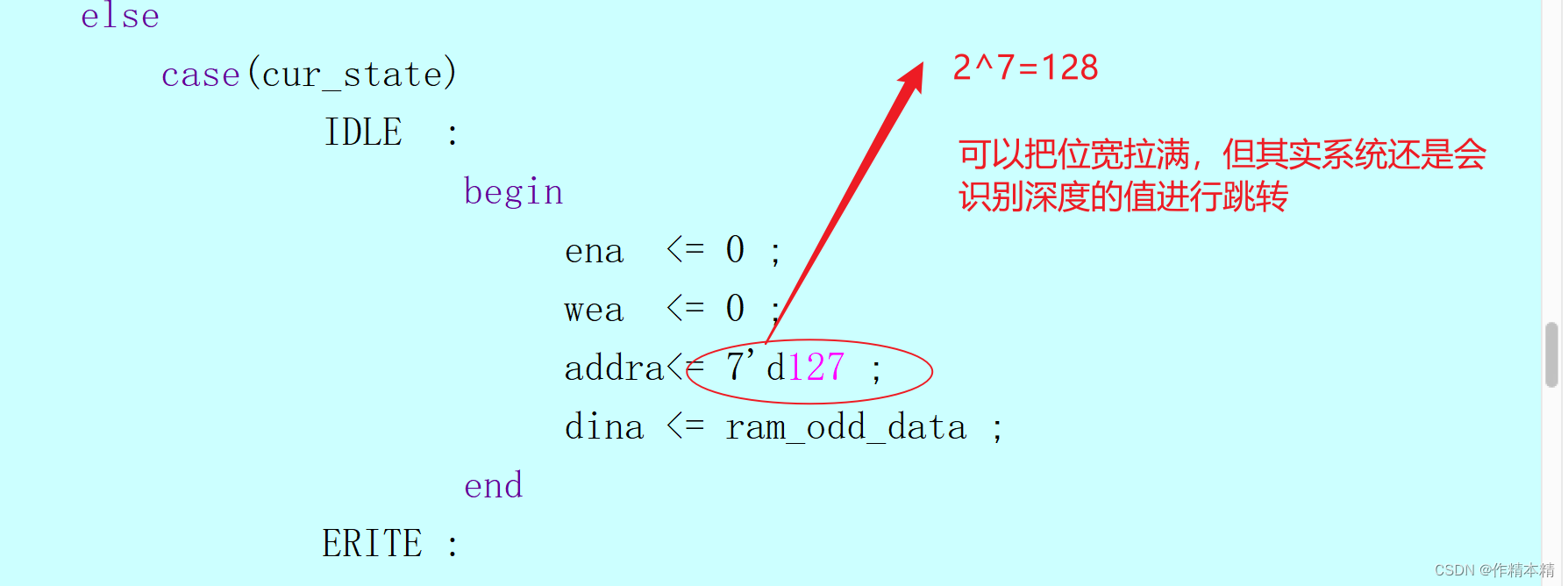

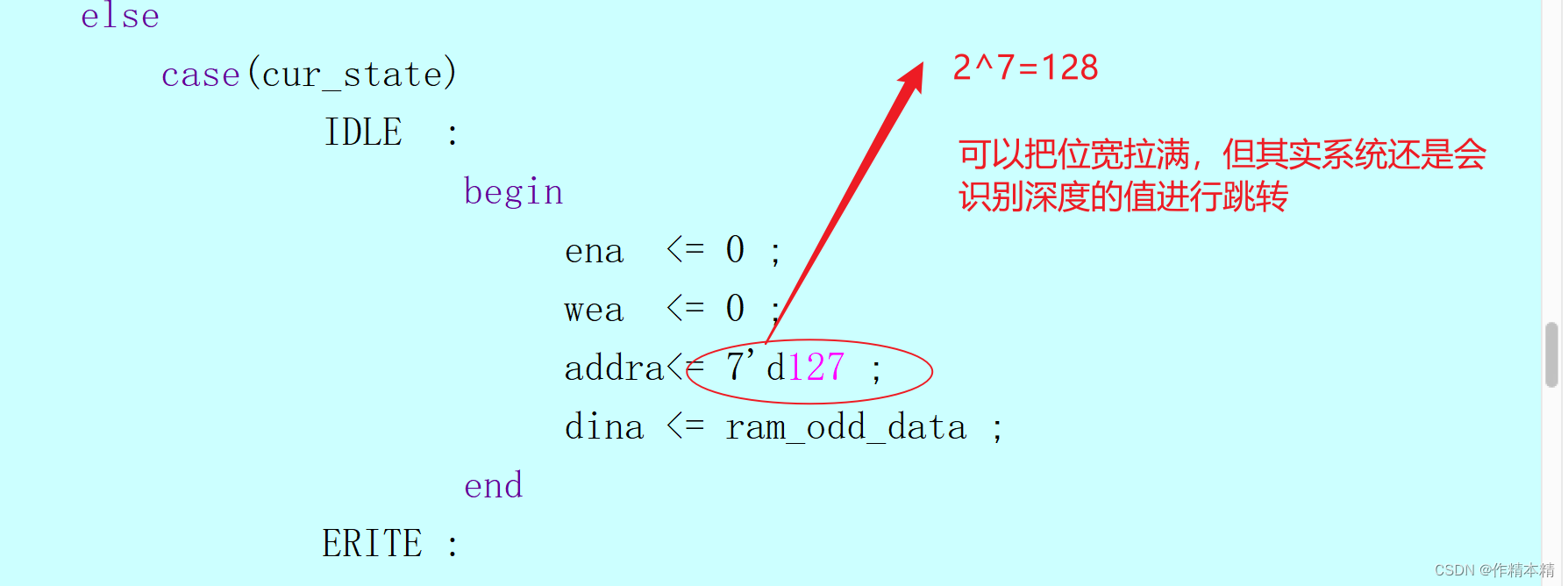

(4)单端RAM1模块

配置和前面一样

`timescale 1ns / 1ps

module single_ram_1_FMS(input sys_clk ,input rst_n ,input key_flag_1 ,input key_flag_2 ,input tx_done ,input[7:0] ram_odd_data ,input[7:0] ram_even_data,output reg tx_start ,output reg[7:0] uart_data );/读单数的RAMreg ena ; reg wea ;reg [6 : 0] addra ;reg [7 : 0] dina ;wire [7 : 0] douta ;reg tx_start_a ;wire tx_start_b ; wire[7:0] uart_data_b ; 先写再读出localparam IDLE = 3'd0 ;localparam ERITE = 3'd1 ;localparam REG = 3'd2 ;localparam READ = 3'd3 ;reg[2:0] cur_state ;reg[2:0] next_state ;//state1always@(posedge sys_clk )if(!rst_n)cur_state <= IDLE ;elsecur_state <= next_state ;//state2always@(*)case(cur_state)IDLE :beginnext_state = ERITE ;endERITE :beginif(key_flag_1)next_state = REG ;elsenext_state <= cur_state ;endREG :beginnext_state = READ ;//用来发送tx_startendREAD :beginif(addra == 49)//100内的单数是50next_state = IDLE ;elsenext_state = cur_state ;enddefault:;endcase//state3always@(posedge sys_clk )if(!rst_n)beginena <= 0 ;wea <= 0 ;addra<= 127 ;dina <= 0 ;tx_start_a <= 0 ;endelsecase(cur_state)IDLE :beginena <= 0 ;wea <= 0 ;addra<= 7'd127 ;dina <= ram_odd_data ;endERITE :beginena <= ~ena ;wea <= ~wea ;if( addra == 49 && wea)addra <= 49 ;else if(wea)addra <= addra +1 ;dina <= ram_odd_data ;endREG :beginena <= 0 ; wea <= 0 ; addra<= 0 ; dina <= 0 ; tx_start_a <= 1 ; endREAD :beginena <= 1 ;wea <= 0 ;dina<= 0 ;if(tx_done)begintx_start_a <= 1 ;addra <= addra +1 ;endelse begintx_start_a <= 0 ;addra <= addra ;endenddefault:;endcase//----------- Begin Cut here for INSTANTIATION Template ---// INST_TAG

single_ram ram1 (.clka(sys_clk ), // input wire clka.ena(ena), // input wire ena.wea(wea), // input wire [0 : 0] wea.addra(addra), // input wire [6 : 0] addra.dina(dina), // input wire [7 : 0] dina.douta(douta) // output wire [7 : 0] douta

);

// INST_TAG_END ------ End INSTANTIATION Template ---------always@(posedge sys_clk )if(!rst_n)uart_data <= 0;else if ( cur_state == READ )uart_data <= douta ;elseuart_data <= uart_data_b ;always@(posedge sys_clk )if(!rst_n)tx_start <= 0 ;else if ( cur_state == REG || cur_state == READ )tx_start <= tx_start_a ;elsetx_start <= tx_start_b ; 例化ram2 single_ram_2_FMS single_ram_2_FMS_u(. sys_clk (sys_clk ) ,. rst_n (rst_n ) ,. key_flag_2 (key_flag_2 ) ,. tx_done (tx_done ) ,. ram_even_data (ram_even_data) ,. tx_start_b (tx_start_b ) ,. uart_data_b (uart_data_b )); endmodule

(5)uart_tx模块:

`timescale 1ns / 1ps

module uart_tx(input sys_clk ,input rst_n ,input wire[7:0] uart_data ,input rx_done , output reg tx_data , output reg tx_done);parameter SYSCLK = 50_000_000 ;parameter Baud = 115200 ;parameter COUNT = SYSCLK/Baud ;//434 传输1比特所需要的时钟周期parameter MID = COUNT/2 ;wire start_flag ;reg tx_flag ;reg tx_reg1 ;reg tx_reg2 ;reg[4:0] cnt_bit ;reg[10:0] cnt ;//tx_startalways@(posedge sys_clk)if(!rst_n)begintx_reg1 <= 0 ;tx_reg2 <= 0 ;endelse begintx_reg1 <= rx_done ;tx_reg2 <= tx_reg1 ;endassign start_flag = tx_reg1 & ~tx_reg2 ;///tx_flagalways@(posedge sys_clk)if(!rst_n)tx_flag <= 0 ;else if ( start_flag == 1 )tx_flag <= 1 ;else if ( cnt == COUNT -1 && cnt_bit == 10)

// else if ( cnt == MID -1 && cnt_bit == 10)tx_flag <= 0 ;elsetx_flag <= tx_flag ;///计时器// cnt 434 always@(posedge sys_clk )if(!rst_n)cnt <= 0;else if ( tx_flag == 1 )beginif ( cnt == COUNT -1) ///一定要减一,如果不减一,实际会计到435次,反算回去波特率就不是115200了cnt <= 0;elsecnt <= cnt +1 ;endelsecnt <= 0 ;// /计数器always@(posedge sys_clk )if(!rst_n)cnt_bit <= 0 ;else if ( tx_flag )beginif ( cnt == COUNT -1)beginif(cnt_bit == 10)///0123456789 10cnt_bit <= 0 ;elsecnt_bit <= cnt_bit +1 ;endelsecnt_bit <= cnt_bit ;endelsecnt_bit <= 0 ;parameter MODE_CHECK = 0 ;always@(posedge sys_clk )if(!rst_n)tx_data <= 1 ; //表示没有数据else if ( tx_flag )beginif ( cnt_bit > 0 && cnt_bit < 9 )///cnt_bit 0 12345678 9 ///tx_data 0123456789///uart_data 01234567tx_data <= uart_data [cnt_bit-1]; //这里uart_data是不断随着cnt_bit变化的,只有在第九位的时候才有正确的最终值else if(cnt_bit == 0)tx_data <= 0 ;else if(cnt_bit == 9)tx_data <= (MODE_CHECK == 0)? ^uart_data: ~^uart_data;/*MODE_CHECK == 0是偶校验,假如uart_data是1110_0000,其异或的结果是1,将异或的结果作为校验位,让数据位和校验位异或的结果为0,满足偶校验。假如uart_data是1110_1000,其异或的结果是0,将异或的结果作为校验位,让数据位和校验位异或的结果为0,满足偶校验。奇校验则相反。*/else if (cnt_bit == 10)///停止位tx_data <= 1 ;elsetx_data <= tx_data ;endelsetx_data <= 1 ;always@(posedge sys_clk )if(!rst_n) tx_done <= 0 ;else if (tx_flag)beginif ( cnt_bit == 10 && cnt == COUNT -1)

// if ( cnt_bit == 10 && cnt == MID/2 -1)tx_done <= 1 ;elsetx_done <= 0 ; endelsetx_done <= 0 ;

endmodule四、仿真模块

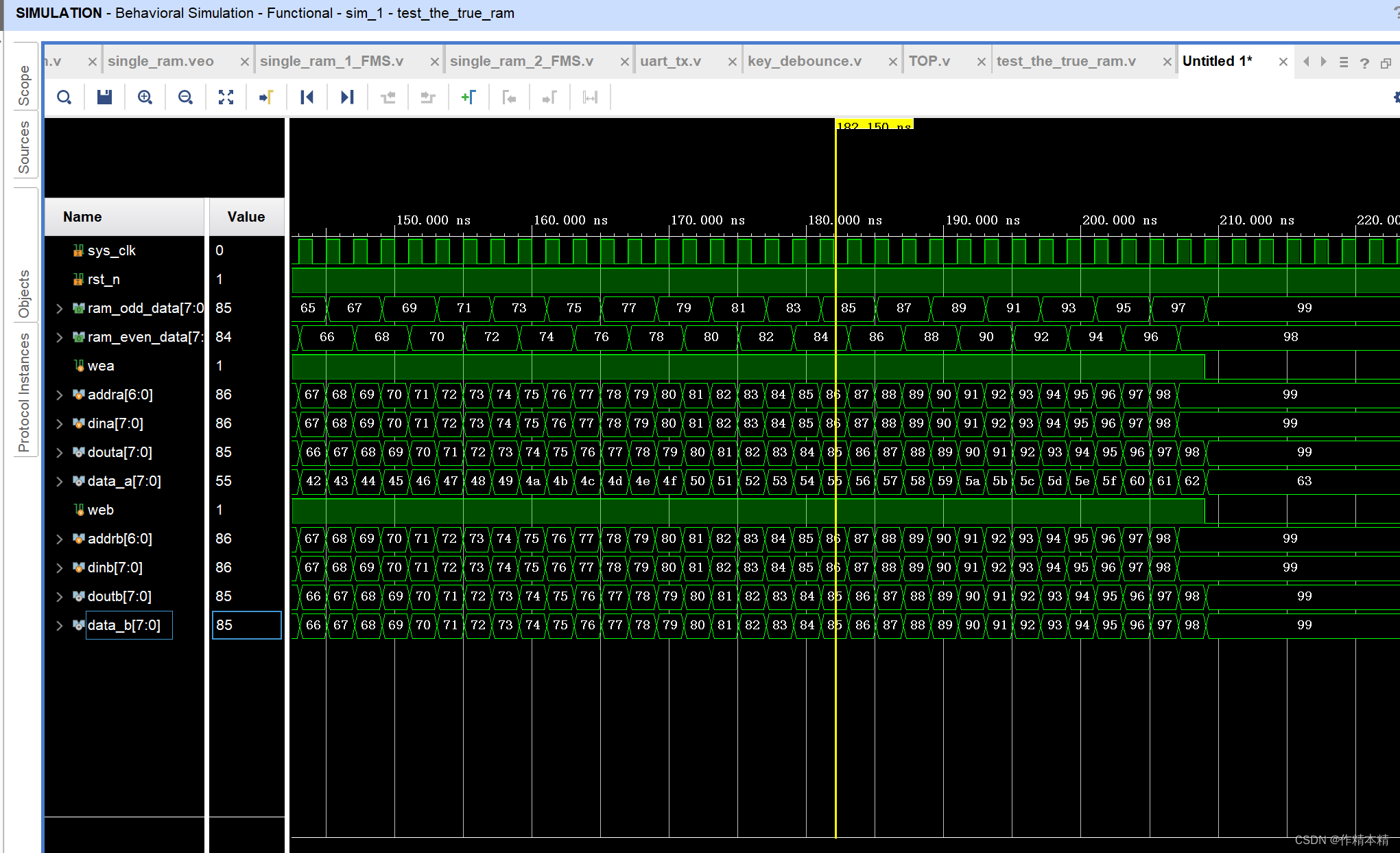

(1)仿真true_ram模块

代码:

`timescale 1ns / 1ps

module test_the_true_ram( );reg sys_clk ;reg rst_n ;wire [7:0] ram_odd_data ;wire [7:0] ram_even_data ;initialbeginsys_clk = 0 ;rst_n = 0 ;#10 rst_n = 1 ;endalways #1 sys_clk = ~sys_clk ; the_true_ram the_true_ram_1(. sys_clk (sys_clk ) ,. rst_n (rst_n ) ,. ram_odd_data (ram_odd_data ) ,. ram_even_data (ram_even_data));endmodule

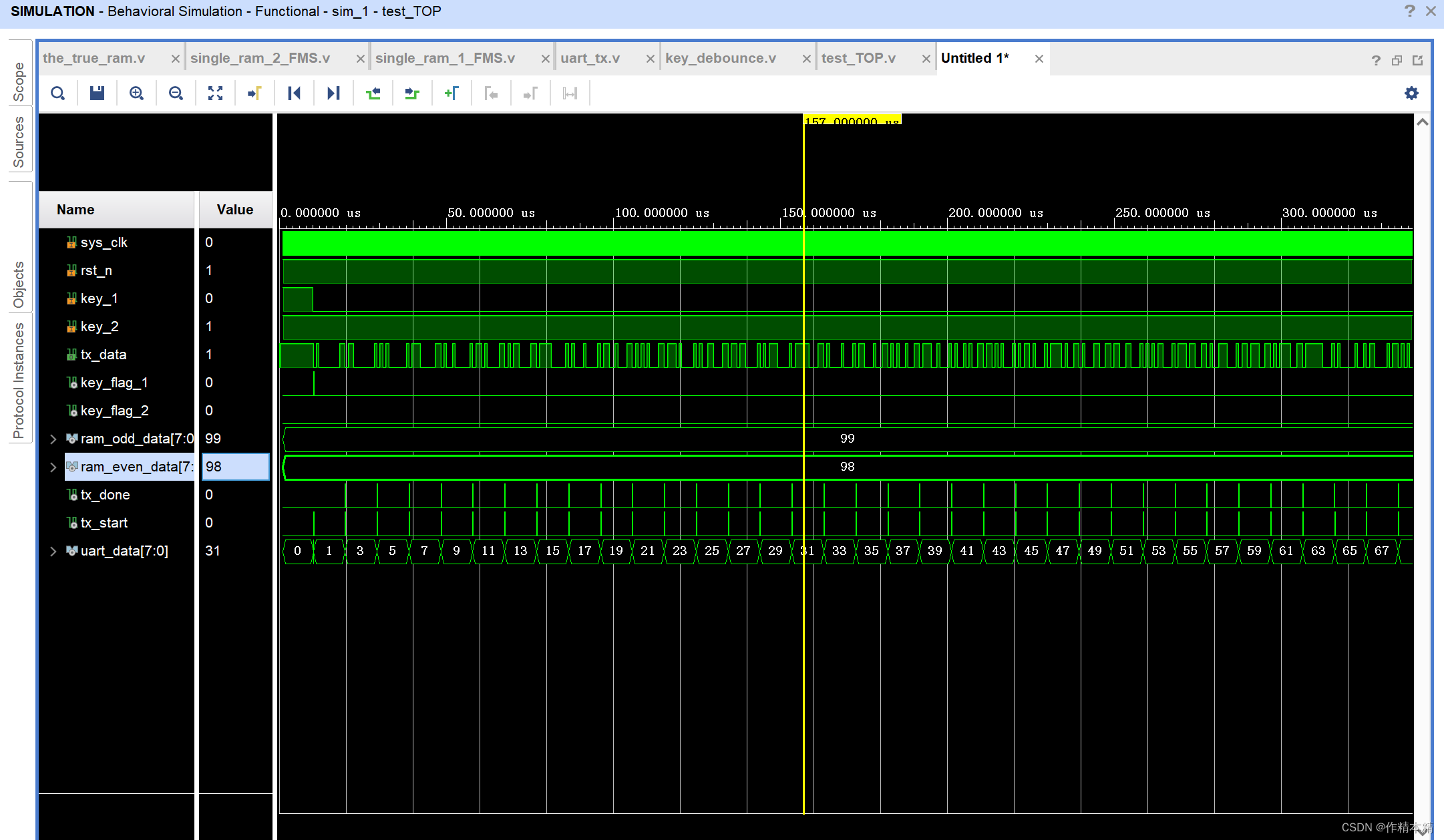

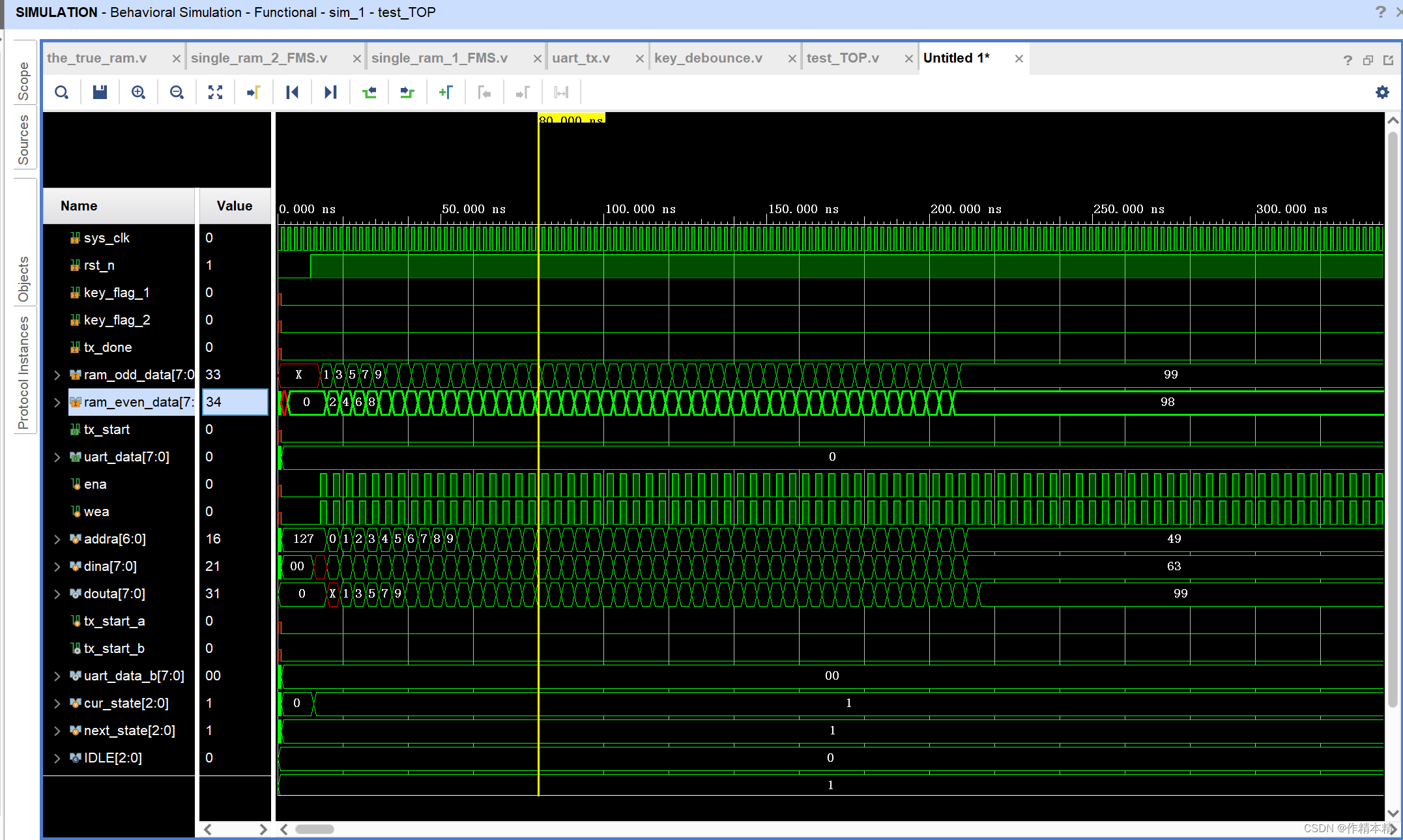

仿真结果:

(2)仿真TOP:

代码:

`timescale 1ns / 1ps

module test_TOP( );reg sys_clk ;reg rst_n ;reg key_1 ;reg key_2 ;wire tx_data ;initialbeginsys_clk = 0 ;rst_n = 0 ;key_1 = 1 ;key_2 = 1 ;#10rst_n = 1 ;#10000key_1 = 0 ;endalways #1 sys_clk = ~sys_clk ;TOP TOP_1(. sys_clk (sys_clk) ,. rst_n (rst_n ) ,. key_1 (key_1 ) ,. key_2 (key_2 ) ,. tx_data (tx_data) );endmodule

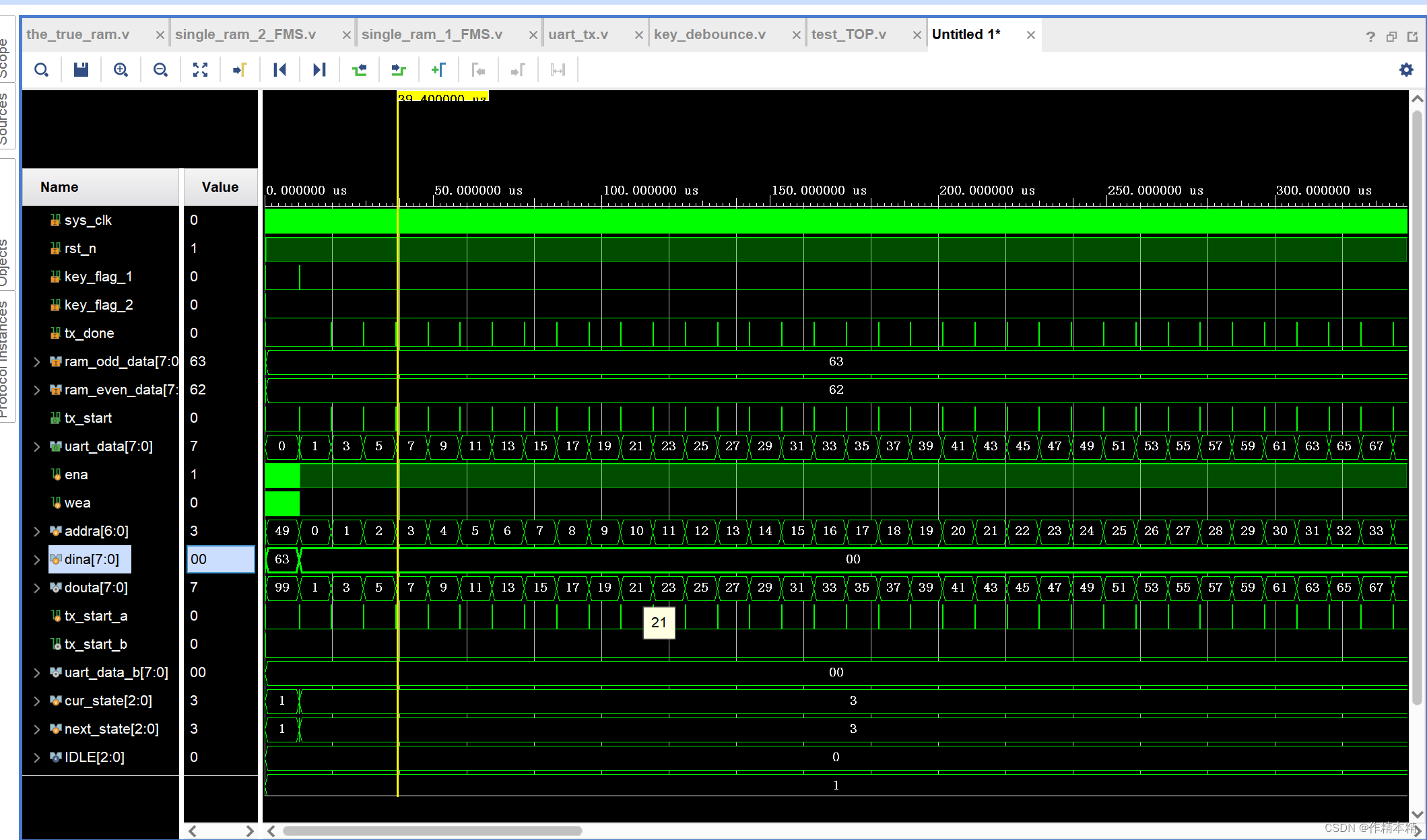

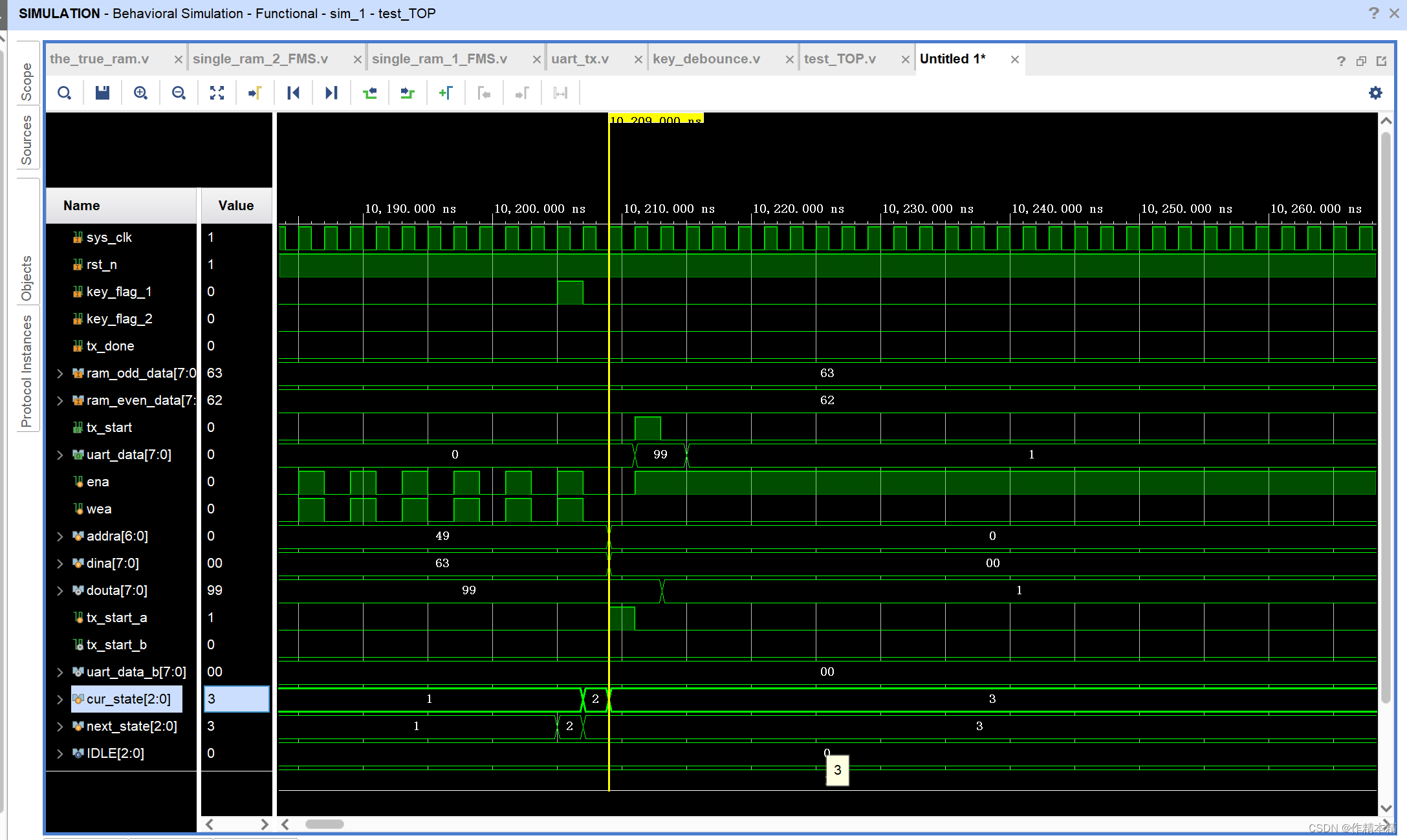

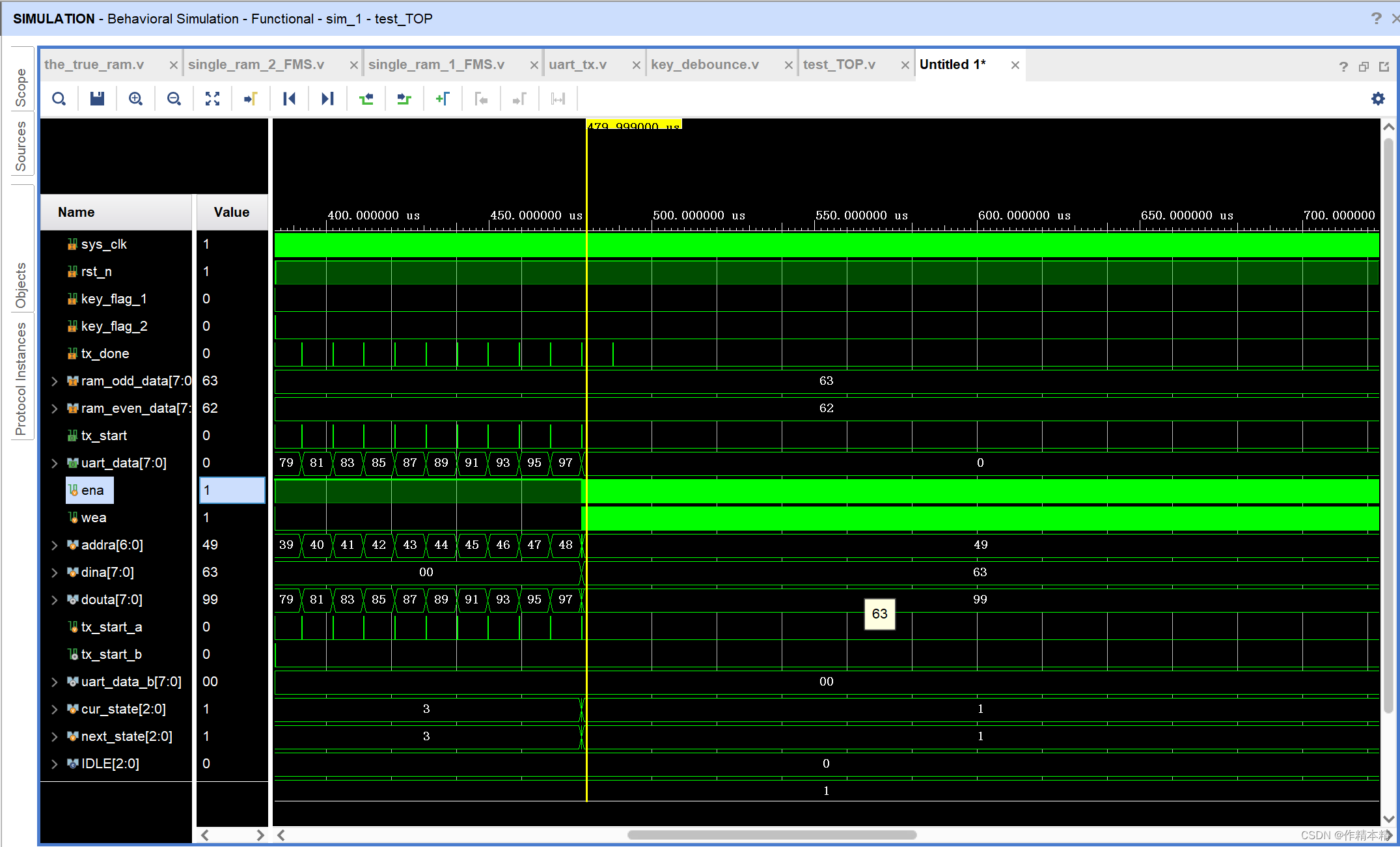

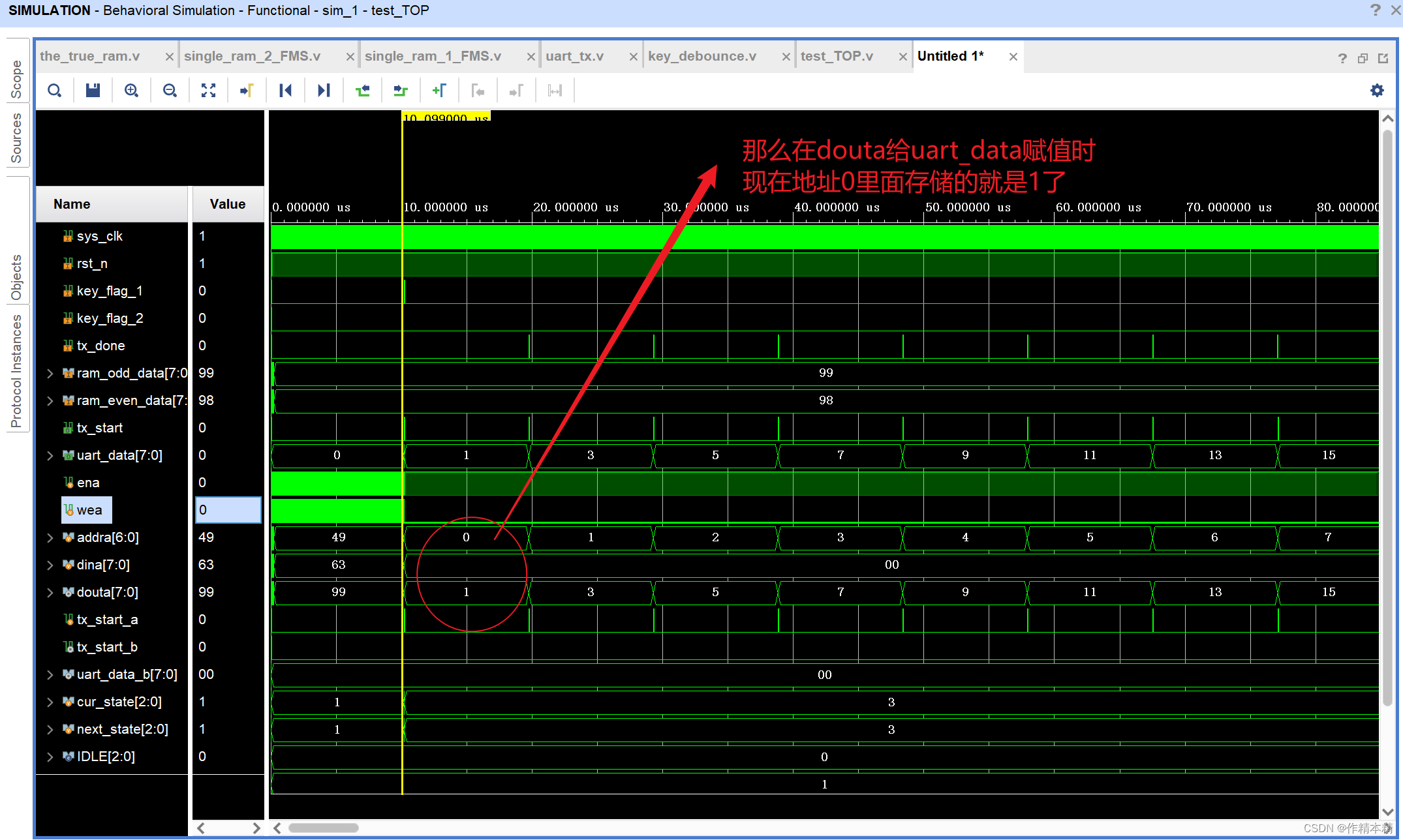

仿真结果:

TOP:

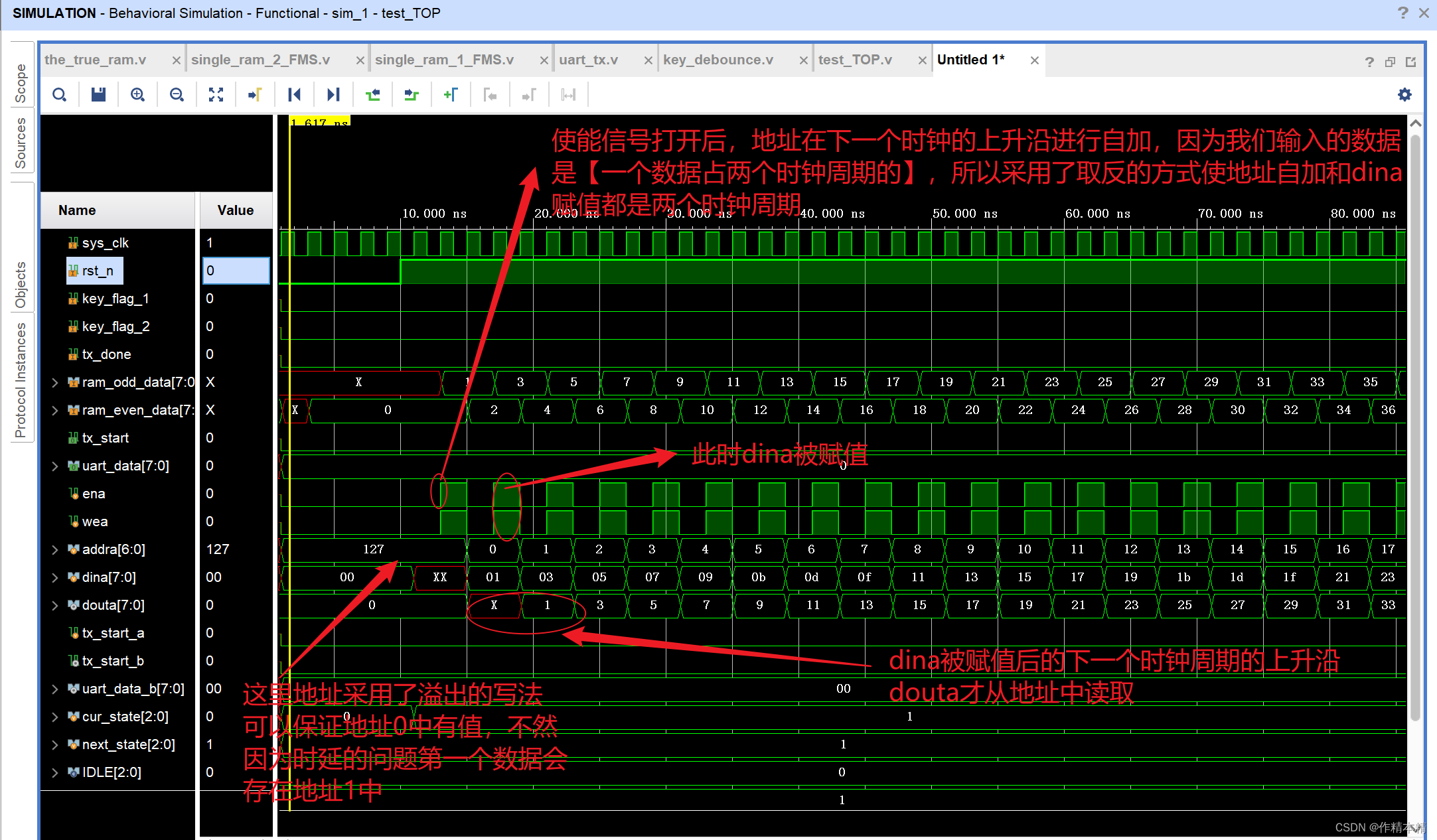

single_ram_1 :

五、需要注意的一些问题

(1)

(2)

(3)控制模块最好这么写

`timescale 1ns / 1ps

module single_ram_2(input sysclk ,input rst_n ,input key_flag1 ,input key_flag2 ,input tx_done ,input [7:0] ram_odd_data , //单数input [7:0] ram_even_data , //双数output reg tx_start ,output reg [7:0] uart_data );

//存单数的RAM

reg wea ;

reg ena ;

reg [6:0] addra ;

reg [7:0] dina ;

wire [7:0] douta ;

///先写再读出

localparam IDLE = 3'd0;

localparam WRITE = 3'd1; 地址加1

localparam REG = 3'd2; ///缓冲状态 地址清零

localparam READ = 3'd3;

reg [2:0] cur_state,next_state;

reg tx_start_a ;

always@(posedge sysclk)if(!rst_n)cur_state <= IDLE;elsecur_state <= next_state;

always@(*)case(cur_state)IDLE : beginif(key_flag1)next_state = WRITE;elsenext_state = cur_state;end WRITE :beginif(addra >= 49)next_state = REG;elsenext_state = cur_state; endREG :beginnext_state = READ;endREAD :beginif(addra >= 49)next_state = IDLE;elsenext_state = cur_state; enddefault:;endcase

always@(posedge sysclk)if(!rst_n)beginaddra <= 0;wea <= 0;ena <= 0;dina <= 0;tx_start_a <= 0;endelsecase(cur_state)IDLE :beginaddra <= 0;wea <= 0;ena <= 0;dina <= ram_odd_data; 维持2个endWRITE :begin ///99/48ena <= ~ena; ///wea <= ~wea; ///if(addra >= 49)addra <= 49;else if(wea)addra <= addra + 1; dina <= ram_odd_data;endREG :beginaddra <= 0;ena <= 0;wea <= 0;dina <= 0;tx_start_a <= 1; ///发送第一个数据endREAD :begin ena <= 1;wea <= 0;dina <= 0;if(tx_done)begintx_start_a <= 1;addra <= addra + 1;endelse begintx_start_a <= 0;addra <= addra;end enddefault:; endcaseblk_mem_gen_2 ram_a (.clka(sysclk), // input wire clka.ena(ena), // input wire ena.wea(wea), // input wire [0 : 0] wea.addra(addra), // input wire [6 : 0] addra.dina(dina), // input wire [7 : 0] dina.douta(douta) // output wire [7 : 0] douta

);

/b端口 存双数

reg web ;

reg enb ;

reg [6:0] addrb ;

reg [7:0] dinb ;

wire [7:0] doutb;

//状态机

///先写再读出

localparam RD_IDLE = 3'd4;

localparam RD_WRITE = 3'd5;

localparam RD_REG = 3'd6; ///缓冲状态

localparam RD_READ = 3'd7;

reg [2:0] rd_cur_state,rd_next_state;

reg tx_start_b ;

always@(posedge sysclk)if(!rst_n)rd_cur_state <= RD_IDLE;elserd_cur_state <= rd_next_state;

always@(*)case(rd_cur_state)RD_IDLE : beginif(key_flag2)rd_next_state = RD_WRITE;elserd_next_state = rd_cur_state;end RD_WRITE :beginif(addrb >= 49)rd_next_state = RD_REG;elserd_next_state = rd_cur_state; endRD_REG :beginrd_next_state = RD_READ;endRD_READ :beginif(addrb >= 49)rd_next_state = RD_IDLE;elserd_next_state = rd_cur_state; enddefault:;endcase

always@(posedge sysclk)if(!rst_n)beginaddrb <= 0;web <= 0;enb <= 0;dinb <= 0;tx_start_b <= 0;endelsecase(rd_cur_state)RD_IDLE :beginaddrb <= 0;web <= 0;enb <= 0;dinb <= ram_even_data; ///020406endRD_WRITE :beginenb <= ~enb; web <= ~web;if(addrb >= 49)addrb <= 49;else if(web)addrb <= addrb + 1; dinb <= ram_even_data;endRD_REG :beginaddrb <= 0;enb <= 0;web <= 0;dinb <= 0;tx_start_b <= 1;endRD_READ :begin enb <= 1;web <= 0;dinb <= 0;if(tx_done)begintx_start_b <= 1;addrb <= addrb + 1;endelse begintx_start_b <= 0;addrb <= addrb;end enddefault:; endcase

blk_mem_gen_2 ram_b (.clka(sysclk), // input wire clka.ena(enb), // input wire ena.wea(web), // input wire [0 : 0] wea.addra(addrb), // input wire [6 : 0] addra.dina(dinb), // input wire [7 : 0] dina.douta(doutb) // output wire [7 : 0] douta

);

always@(posedge sysclk)if(!rst_n)uart_data <= 0;else if(cur_state == READ )uart_data <= douta ;else if(rd_cur_state == RD_READ )uart_data <= doutb ;elseuart_data <= uart_data;always@(posedge sysclk)if(!rst_n)tx_start <= 0;else if(cur_state == REG || cur_state == READ)tx_start <= tx_start_a;else if(rd_cur_state == RD_REG || rd_cur_state == RD_READ)tx_start <= tx_start_b;elsetx_start <= tx_start;endmodule

相关文章:

Xilinx FPGA:vivado关于真双端口的串口传输数据的实验

一、实验内容 用一个真双端RAM,端口A和端口B同时向RAM里写入数据0-99,A端口读出单数并存入单端口RAM1中,B端口读出双数并存入但端口RAM2中,当检测到按键1到来时将RAM1中的单数读出显示到PC端,当检测到按键2到来时&…...

RedisTemplate 中序列化方式辨析

在Spring Data Redis中,RedisTemplate 是操作Redis的核心类,它提供了丰富的API来与Redis进行交互。由于Redis是一个键值存储系统,它存储的是字节序列,因此在使用RedisTemplate时,需要指定键(Key)…...

数据结构与算法基础篇--二分查找

必要前提:有序数组 算法简述:通过不断取中间值和目标target值进行比较(中间值:mid (left right) / 2) 如果目标值等于中间位置的值,则找到目标,返回中间位置如果目标值小于中间位置的值&…...

python xlsx 导出表格超链接

该Python脚本用于从Excel文件中的第一列提取所有超链接并保存到一个文本文件中。首先,脚本导入必要的库并定义输入和输出文件的路径。然后,它确保输出文件的目录存在。接着,脚本加载Excel文件并选择活动工作表。通过遍历第一列的所有单元格&a…...

Data Guard高级玩法:failover备库后,通过闪回恢复DG备库

作者介绍:老苏,10余年DBA工作运维经验,擅长Oracle、MySQL、PG、Mongodb数据库运维(如安装迁移,性能优化、故障应急处理等) 公众号:老苏畅谈运维 欢迎关注本人公众号,更多精彩与您分享…...

【Unity2D 2022:NPC】制作任务系统

一、接受任务 1. 编辑NPC对话脚本: (1)创建静态布尔变量用来判断ruby是否接受到任务 public class NPCDialog : MonoBehaviour {// 创建全局变量用来判断ruby是否接到任务public static bool receiveTask false; } (2ÿ…...

【C++深度学习】多态(概念虚函数抽象类)

✨ 疏影横斜水清浅,暗香浮动月黄昏 🌏 📃个人主页:island1314 🔥个人专栏:C学习 🚀 欢迎关注:👍点赞 &…...

Ubuntu 安装CGAL

一、什么是CGAL CGAL(Computational Geometry Algorithms Library)是一个广泛使用的开源库,主要用于计算几何算法的实现。该库提供了一系列高效、可靠和易于使用的几何算法和数据结构,适用于各种应用领域。以下是 CGAL 的主要功能…...

netfilter框架)

RK3568平台开发系列讲解(网络篇)netfilter框架

🚀返回专栏总目录 文章目录 一、Netfilter 介绍二、netfilter 简单案例三、防火墙功能一、Netfilter 介绍 Linux内核自2.4版本开始引入了Netfilter框架,这是一项重要的网络功能增强。Netfilter框架由Linux内核防火墙和网络维护者 Rusty Russell 所提出和实现。这个作者还基于…...

检测音视频文件的声压

FFmpeg使用 ebur128 滤镜检测声压,EBU R128 是欧洲广播联盟(European Broadcasting Union,简称 EBU)推荐的音频响度测量和归一化标准。 ffmpeg -i input_video.mp4 -filter_complex ebur128peaktrue -f null --f null -ÿ…...

计算机网络-HTTP常见面试题

目录 1. HTTP是什么?2. HTTP常见的状态码?3. HTTP 常见的字段有哪些?4. GET和POST有什么区别:5. GET 和POST方法都是安全和幂等的吗?6. HTTP缓存技术7. HTTP/1.1相比HTTP/1.0提高了什么性能?8. HTTP/2做了什…...

LNMP搭建Discuz和Wordpress

1、LNMP L:linux操作系统 N:nginx展示前端页面web服务 M:mysql数据库,保存用户和密码,以及论坛相关的内容 P:php动态请求转发的中间件 数据库的作用: 登录时验证用户名和密码 创建用户和密码 发布和…...

java中的构造器

Java 中的构造器(也称为构造方法)是一种特殊的方法,用于初始化对象的状态。在创建 Java 类的实例时,构造器会被自动调用。 构造器的定义: 构造器的名称必须与类名完全相同。构造器没有返回值类型,甚至不包括…...

机器学习筑基篇,Ubuntu 24.04 快速安装 PyCharm IDE 工具,无需激活!

[ 知识是人生的灯塔,只有不断学习,才能照亮前行的道路 ] Ubuntu 24.04 快速安装 PyCharm IDE 工具 描述:虽然在之前我们安装了VScode,但是其对于使用Python来写大型项目以及各类配置还是比较复杂的,所以这里我们还是推…...

从0开始基于transformer进行股价预测(pytorch版本)

目录 数据阶段两个问题开始利用我们的代码进行切分 backbone网络训练效果 感觉还行,没有调参数。源码比较长,如果需要我后续会发(因为太长了!!) 数据阶段 !!!注意&#…...

【多GPU训练方法】

一、数据并行 这是最常用的方法。整个模型复制到每个GPU上。训练数据被均匀分割,每个GPU处理一部分数据。所有GPU上的梯度被收集并求平均。通常使用NCCL(NVIDIA Collective Communications Library)等通信库实现。参数更新 使用同步后的梯度…...

2024年PMP考试备考经验分享

PMP是项目管理领域最重要的认证之一,本身是IT行业比较流行的证书,近几年在临床试验领域也渐渐流行起来,是我周围临床项PM几乎人手一个的证书。 考试时间:PMP认证考试形式为180道选择题,考试时间为3小时50分。 考试计划ÿ…...

MT3046 愤怒的象棚

思路: a[]存愤怒值;b[i]存以i结尾的,窗口里的最大值;c[i]存以i结尾的,窗口里面包含✳的最大值。 (✳为新大象的位置) 例:1 2 3 4 ✳ 5 6 7 8 9 则ans的计算公式b3b4c4c5c6b7b8b9…...

深入了解代理IP常见协议:区别与选择

代理服务器在网络使用中扮演着重要的角色,是您设备和互联网之间的中间层。它不仅可以增强网络访问的安全性和隐私保护,还可以提供许多灵活的应用。使用代理时,不同的协议类型对数据交换具有不同的规则和特征。常见的代理协议包括HTTP代理、HT…...

【Linux 线程】线程的基本概念、LWP的理解

文章目录 一、ps -L 指令🍎二、线程控制 一、ps -L 指令🍎 🐧 使用 ps -L 命令查看轻量级进程信息;🐧 pthread_self() 用于获取用户态线程的 tid,而并非轻量级进程ID;🐧 getpid() 用…...

Amlogic S9XXX Armbian刷机完全指南:从入门到进阶的5个关键问题

Amlogic S9XXX Armbian刷机完全指南:从入门到进阶的5个关键问题 【免费下载链接】amlogic-s9xxx-armbian Supports running Armbian on Amlogic, Allwinner, and Rockchip devices. Support a311d, s922x, s905x3, s905x2, s912, s905d, s905x, s905w, s905, s905l,…...

手把手教程:在CSDN星图一键部署LFM2.5轻量模型,低配电脑也能跑AI

手把手教程:在CSDN星图一键部署LFM2.5轻量模型,低配电脑也能跑AI 还在为本地跑不动大模型而烦恼吗?今天我要分享一个好消息:即使你的电脑配置不高,也能轻松部署一个实用的AI文本生成模型。LFM2.5-1.2B-Thinking-GGUF就…...

Kook Zimage 真实幻想 Typora文档集成方案

Kook Zimage 真实幻想 Typora文档集成方案 1. 引言 技术文档写作最头疼的是什么?文字描述得再生动,也不如一张直观的图片来得有说服力。传统的文档创作流程中,我们需要先在专门的AI绘图工具中生成图片,然后下载保存,…...

格式化字符串漏洞利用的5种常见手法:以CTFshow题目为例

格式化字符串漏洞实战:5种高级利用手法与CTFshow案例分析 格式化字符串漏洞(Format String Vulnerability)是二进制安全领域中最经典也最危险的漏洞类型之一。这种漏洞源于程序员错误地将用户输入直接作为格式化字符串参数传递给printf、spri…...

Ubuntu22.04微信依赖冲突的终极解决方案

1. 问题现象与原因分析 最近在Ubuntu 22.04上安装微信时,很多朋友都遇到了依赖冲突的问题。具体表现是当你尝试通过命令行安装微信时,系统会提示类似这样的错误信息: 下列软件包有未满足的依赖关系: libldap-2.4-2 : 依赖: libsas…...

Asian Beauty Z-Image Turbo基础教程:如何修改默认提示词实现‘旗袍少女’‘水墨仕女’风格

Asian Beauty Z-Image Turbo基础教程:如何修改默认提示词实现‘旗袍少女’‘水墨仕女’风格 想用AI画出充满东方韵味的“旗袍少女”或“水墨仕女”,但试了很多模型,出来的效果总是不对味?要么人物五官太西化,要么画面…...

Ostrakon-VL-8B零售AI创新:用像素游戏化设计提升一线员工使用意愿

Ostrakon-VL-8B零售AI创新:用像素游戏化设计提升一线员工使用意愿 1. 项目背景与设计理念 在零售和餐饮行业,一线员工使用AI工具的意愿往往不高。传统工业级UI界面过于复杂,操作流程繁琐,导致员工抵触新技术。Ostrakon-VL-8B团队…...

Axelspace 太空公司牵头联合体入选日本太空战略基金项目 “提升下一代地球观测卫星能力技术”

—— 通过卫星星座与航空器开展特定排放源二氧化碳排放与吸收监测,打造气候解决方案,开拓全新市场机遇 Axelspace 太空公司、明星电气株式会社、全日空控股株式会社及 JIJ 株式会社联合宣布,各方共同申报的技术研发项目成功入选日本宇宙航空…...

【读书笔记】《如何做到爱孩子也被孩子爱》

《如何做到爱孩子也被孩子爱》作者:法国著名心理学家(著有《你好,焦虑分子》)核心框架:爱、理性与逻辑 本书提出教养孩子的三大抓手,缺一不可: 爱 → 带来丰富情感与能量,让孩子将来…...

Go AI 生态实战:从单机 RAG 到分布式智能服务架构演进

Go AI 生态实战:从单机 RAG 到分布式智能服务架构演进 摘要:本文面向具备后端与架构背景的技术人员,系统讲透 Go 在 AI 应用落地中的工程化方法。文章不再停留在“调用一个模型接口”的层面,而是从 RAG 原理、服务拆分、索引构建、高并发治理、缓存策略、容错机制、可观测性…...