FPGA设计中的流水线 -分割大的计算电路可以更快的处理数据。

FPGA(现场可编程门阵列)设计中的流水线优化是一种提高设计性能的技术,它通过将设计分解为多个阶段或步骤来实现。每个阶段可以并行执行,从而提高整体的吞吐量和效率。以下是流水线优化的一些关键概念和作用:

意思:

- 流水线(Pipeline):将一个复杂的过程分解成一系列有序的阶段,每个阶段完成特定的任务。

- 阶段(Stage):流水线中的每一个独立的处理步骤。

- 数据依赖性:不同阶段之间数据的依赖关系,这可能限制流水线的并行度。

作用:

- 提高吞吐量:通过并行处理多个数据元素,流水线可以显著提高设计的数据处理能力。

- 减少延迟:在某些情况下,流水线可以减少从输入到输出的总延迟,因为它允许在前一个操作完成之前开始新的操作。

- 资源利用率:通过优化设计,流水线可以更有效地使用FPGA上的资源,如查找表(LUTs)、寄存器等。

- 性能可预测性:流水线的设计通常可以提供更可预测的性能,因为它减少了设计中不同部分之间的相互依赖。

- 灵活性:流水线技术允许设计者根据需要调整每个阶段的处理能力,以适应不同的性能要求。

- 可扩展性:随着需求的增长,可以通过增加更多的阶段来扩展流水线,以处理更大的数据量或更复杂的任务。

注意事项:

- 资源消耗:流水线可能会增加FPGA资源的消耗,因为需要更多的寄存器来存储中间结果。

- 设计复杂性:流水线设计可能会增加设计的复杂性,需要仔细规划数据流和时序。

- 时序约束:流水线需要严格的时序约束,以确保数据在正确的时间到达正确的阶段。

流水线优化是FPGA设计中的一种强大工具,但需要仔细的规划和设计,以确保最优的性能和资源利用率。

以一个包含差分数据平方和的计算为例

不加流水线:

在 Verilog 中,直接进行浮点运算和平方根计算比较复杂,因为 Verilog 是一种硬件描述语言,主要用于描述和实现硬件逻辑。Verilog 本身不提供对浮点运算的直接支持,需要使用专门的浮点运算库或模块来实现。

以下是一个简化的 Verilog 代码示例,它将实现一个计算输入序列差值平方和的模块,但不包括平方根计算部分。对于平方根和浮点运算,您需要使用专门的 IP 核或模块来实现。

Verilog 示例代码

module Poincare_SD1_calculate (input wire clk,input wire reset,input wire [31:0] in, // 假设输入为 32 位定点数,实际应为浮点数input wire [15:0] len,output reg [31:0] SD1 // 假设输出为 32 位定点数,实际应为浮点数

);reg [31:0] sum_diff;reg [15:0] i;reg [31:0] diff;// 状态机typedef enum reg [1:0] {IDLE,CALC,DONE} state_t;state_t state;always @(posedge clk or posedge reset) beginif (reset) beginsum_diff <= 0;i <= 0;SD1 <= 0;state <= IDLE;end else begincase (state)IDLE: beginif (len > 1) beginsum_diff <= 0;i <= 0;state <= CALC;end else beginstate <= DONE;endendCALC: beginif (i < len - 1) begindiff <= in[i] - in[i+1];sum_diff <= sum_diff + diff * diff;i <= i + 1;end else beginstate <= DONE;endendDONE: begin// 需要一个外部模块来计算 sqrt(sum_diff / (len - 1)) / sqrt(2)// 这里假设已经计算了该值,并赋值给 SD1SD1 <= sum_diff; // 占位符,实际应为计算结果state <= IDLE;endendcaseendend

endmodule

解释

-

模块接口:

- 输入

clk和reset:时钟和复位信号。 - 输入

in:输入序列(假设为定点数,实际应为浮点数)。 - 输入

len:输入序列的长度。 - 输出

SD1:计算结果(假设为定点数,实际应为浮点数)。

- 输入

-

状态机:

IDLE状态:等待开始计算。CALC状态:计算差值平方和。DONE状态:计算完成,输出结果。

-

主要计算逻辑:

- 在

CALC状态中,循环遍历输入序列,计算相邻元素差值的平方和。 - 在

DONE状态中,假设已经计算了最终结果(实际需要外部模块进行平方根计算),并输出结果。

- 在

注意事项

- 浮点运算:Verilog 不支持原生的浮点运算,需要使用浮点运算 IP 核或自定义模块来实现。

- 平方根计算:类似地,平方根计算也需要专门的模块来实现。

- 输入输出格式:实际设计中,输入输出可能需要使用 IEEE 754 浮点数格式,或者使用定点数格式。

这个示例提供了一个基本的算法Verlog电路描述,核心算法没有被分割,需要计算完,才能进行下一个步骤。

流水线优化

为了进行流水线优化,我们需要将计算过程分解为多个步骤,每个步骤在一个时钟周期内完成,从而提高系统的吞吐量。Verilog 中的流水线设计通常包括多个寄存器级,用于存储中间结果。对于您的模块,我们可以将计算过程分为以下几个阶段:

- 计算差值 (

diff) - 计算差值的平方 (

diff * diff) - 累加平方值 (

sum_diff) - 最终计算 (

sqrt(sum_diff / (len - 1)) / sqrt(2))

请注意,最终的平方根计算 (sqrt) 需要外部模块或库的支持,Verilog本身没有原生的浮点运算支持。

优化后的Verilog代码

module Poincare_SD1_calculate (input wire clk,input wire reset,input wire [31:0] in, // 假设输入为 32 位定点数,实际应为浮点数input wire [15:0] len,output reg [31:0] SD1 // 假设输出为 32 位定点数,实际应为浮点数

);reg [31:0] sum_diff;reg [15:0] i;reg [31:0] diff;reg [31:0] diff_sq;// 状态机typedef enum reg [1:0] {IDLE,CALC_DIFF,CALC_SQ,ACCUM,DONE} state_t;state_t state;always @(posedge clk or posedge reset) beginif (reset) beginsum_diff <= 0;i <= 0;SD1 <= 0;state <= IDLE;end else begincase (state)IDLE: beginif (len > 1) beginsum_diff <= 0;i <= 0;state <= CALC_DIFF;end else beginstate <= DONE;endendCALC_DIFF: beginif (i < len - 1) begindiff <= in[i] - in[i+1];state <= CALC_SQ;end else beginstate <= DONE;endendCALC_SQ: begindiff_sq <= diff * diff;state <= ACCUM;endACCUM: beginsum_diff <= sum_diff + diff_sq;i <= i + 1;state <= CALC_DIFF;endDONE: begin// 需要一个外部模块来计算 sqrt(sum_diff / (len - 1)) / sqrt(2)// 这里假设已经计算了该值,并赋值给 SD1SD1 <= sum_diff; // 占位符,实际应为计算结果state <= IDLE;endendcaseendend

endmodule

解释

-

状态机增加了更多状态:

CALC_DIFF:计算当前差值。CALC_SQ:计算差值的平方。ACCUM:累加平方值。

-

流水线操作:

- 在每个时钟周期内,状态机会从一个状态转移到下一个状态,使得每个操作在不同的周期内完成,这样可以实现流水线操作。

-

中间寄存器:

diff和diff_sq用于存储中间计算结果,从而实现操作分离。

注意事项

- 平方根计算:最终的平方根计算和浮点运算需要一个外部模块实现。

- 定点数与浮点数:假设输入为定点数,实际应用中可能需要浮点数运算,这需要额外的浮点数运算模块。

通过上述优化,模块的计算过程被拆分成多个流水线阶段,每个阶段在不同的时钟周期内完成,提高了系统的吞吐量。

相关文章:

FPGA设计中的流水线 -分割大的计算电路可以更快的处理数据。

FPGA(现场可编程门阵列)设计中的流水线优化是一种提高设计性能的技术,它通过将设计分解为多个阶段或步骤来实现。每个阶段可以并行执行,从而提高整体的吞吐量和效率。以下是流水线优化的一些关键概念和作用: 意思&…...

GNU/Linux - U-BOOT的GPIO command

在嵌入式Linux开发中,先运行的是u-boot,然后再加载Linux内核。 启动时如果设置了u-boot等待时间,在等待时间内,按任意键就会进入u-boot命令行环境。 在u-boot命令行环境下,可以使用gpio命令来操作GPIO。 Synopsis gpi…...

35.UART(通用异步收发传输器)-RS232(2)

(1)RS232接收模块visio框图: (2)接收模块Verilog代码编写: /* 常见波特率: 4800、9600、14400、115200 在系统时钟为50MHz时,对应计数为: (1/4800) * 10^9 /20 -1 10416 …...

OpenLayers学习笔记-点位聚合

需求 用户点击行政区划等操作后,从后台获取区域内的点位数据,在地图上聚合显示。用户手动取消聚合,点位直接渲染在地图上。 实现过程 使用后台返回的点位数据,通过new ol.source.Vector({features})创建矢量数据源。使用new ol.source.Cluster({source})创建聚合标注数据…...

flutter实现语言的国际化

目录 前言 一、GetX实现国际化(推荐) 1.安装Getx 2.创建国际化的文件 3.使用国际化字符串 4.配置GetMaterialApp 5.更改语言 6.系统语言 编辑 7.原生工程配置 1.iOS工程配 1.打开iOS工程,在Project的info里面添加语言 2.创建String File文件 2.andr…...

服务端正常启动了,但是客户端请求不到

服务端正常启动了,但是客户端请求不到有哪些原因?如何排查? 如果客户端请求的接口没有响应,排查的方式: 检查接口IP地址是否正确,ping一下接口地址。 检查被测接口端口号是否正确,可以在本机Telnet接口的IP和端口号…...

鸿蒙开发 -本地数据库操作

// 1导入模块 import relationalStore from @ohos.data.relationalStore;export class AthUserDbManager{//2.获取RdbStore实例,要注意的是,此处的getContext(this)用于获取应用上下文:getcreatDbtable(dbname:string){//配置数据库信息:const STORE_CONFIG :relationalStor…...

主机安全-进程、命令攻击与检测

目录 概述反弹shell原理nc/dev/xxx反弹shell下载不落地反弹Shell各种语言反弹shell linux提权sudosuid提权mysql提权 Dnslog参考 概述 本文更新通过在主机(不含容器)上直接执行命令或启动进程来攻击的场景。检测方面以字节跳动的开源HIDS elkeid举例。每…...

FPGA FIR fdatool filter designer MATLAB

位数问题 fdatool 先确定输入信号的位宽,比如17位在fdatool中,选set quantization parameters 选input/output 设置input word length 为17bit(not confirmed) fir compiler implementation 注意: 当设置输入位宽为16位时,ip核…...

水表数字识别2:Pytorch DBNet实现水表数字检测(含训练代码和数据集)

水表数字识别2:Pytorch DBNet实现水表数字检测(含训练代码和数据集) 目录 水表数字识别2:Pytorch DBNet实现水表数字检测(含训练代码和数据集) 1.前言 2. 水表数字识别的方法 3. 水表数字识别数据集 4. 水表数字分割模型训练 (1&#x…...

Windows 点云生成二维栅格图 [附C++完整代码实现]

点云压缩-2D栅格图 一、点云压缩(二维栅格图)二、算法流程三、代码实现四、结果可视化一、点云压缩(二维栅格图) 点云压缩:点云是海量点的集合,其数据量通常非常庞大。直接存储这些未经压缩的点云数据会消耗大量的存储空间,特别是在处理大规模的点云数据时,这个问题变得…...

SpringBoot结合ip2region实现博客评论显示IP属地

你好呀,我是小邹。 在现代的Web应用中,特别是博客和论坛类网站,为用户提供地理定位服务(如显示用户所在地理位置)可以极大地增强用户体验。本文将详细探讨如何使用Java和相关技术栈来实现在博客评论中显示用户的地址信…...

)

设计模式使用场景实现示例及优缺点(行为型模式——策略模式)

在遥远的王国里,有三个重要的角色:国王策略模式、他的皇家顾问算法家族,以及年轻的骑士接口。国王策略模式统治着整个王国,他的职责是确保每一个编程问题都能找到最合适的解决方案。 有一天,王国遇到了一场危机。编程王…...

ReactRouter v6升级的步骤

React Router v6 引入了一个 Routes 组件,它有点像 Switch ,但功能要强大得多。与 Switch 相比, Routes 的主要优势在于: <Routes> 中的所有 <Route> 和 <Link> 都是相对的。这导致在 <Route path> 和 &…...

【JVM实战篇】内存调优:内存问题诊断+案例实战

文章目录 诊断内存快照在内存溢出时生成内存快照MAT分析内存快照MAT内存泄漏检测的原理支配树介绍如何在不内存溢出情况下生成堆内存快照?MAT查看支配树MAT如何根据支配树发现内存泄漏 运行程序的内存快照导出和分析快照**大文件的处理** 案例实战案例1:…...

专业条码二维码扫描设备和手机二维码扫描软件的区别?

条码二维码技术已广泛应用于我们的日常生活中,从超市结账到公交出行,再到各类活动的入场验证,条码二维码的便捷性不言而喻,而在条码二维码的扫描识别读取过程中,专业扫描读取设备和手机二维码扫描软件成为了两大主要工…...

基于嵌入式Linux的高性能车载娱乐系统设计与实现 —— 融合Qt、FFmpeg和CAN总线技术

随着汽车智能化的发展,车载娱乐系统已成为现代汽车的标配。本文介绍了一个基于Linux的车载娱乐系统的设计与实现过程。该系统集成了音视频娱乐、导航、车辆信息显示等功能,旨在提供安全、便捷、丰富的驾驶体验。 1. 项目概述 随着汽车智能化的发展&…...

探索IP形象设计:快速掌握设计要点

随着市场竞争的加剧,越来越多的企业开始关注品牌形象的塑造和推广。在品牌形象中,知识产权形象设计是非常重要的方面。在智能和互联网的趋势下,未来的知识产权形象设计可能会更加关注数字和社交网络。通过数字技术和社交媒体平台,…...

泛微Ecology8明细表对主表赋值

文章目录 [toc]1.需求及效果1.1 需求1.2 效果2.思路与实现3.结语 1.需求及效果 1.1 需求 在明细表中的项目经理,可以将值赋值给主表中的项目经理来作为审批人员 1.2 效果 在申请人保存或者提交后将明细表中的人名赋值给主表中对应的值2.思路与实现 在通过js测…...

opencv—常用函数学习_“干货“_5

目录 十五、图像分割 简单阈值分割 (threshold) 自适应阈值分割 (adaptiveThreshold) 颜色范围分割 (inRange) 分水岭算法 (watershed) 泛洪填充 (floodFill) GrabCut算法 (grabCut) 距离变换 (distanceTransform) 最大稳定极值区域检测 (MSER) 均值漂移滤波 (pyrMean…...

k8s从入门到放弃之Ingress七层负载

k8s从入门到放弃之Ingress七层负载 在Kubernetes(简称K8s)中,Ingress是一个API对象,它允许你定义如何从集群外部访问集群内部的服务。Ingress可以提供负载均衡、SSL终结和基于名称的虚拟主机等功能。通过Ingress,你可…...

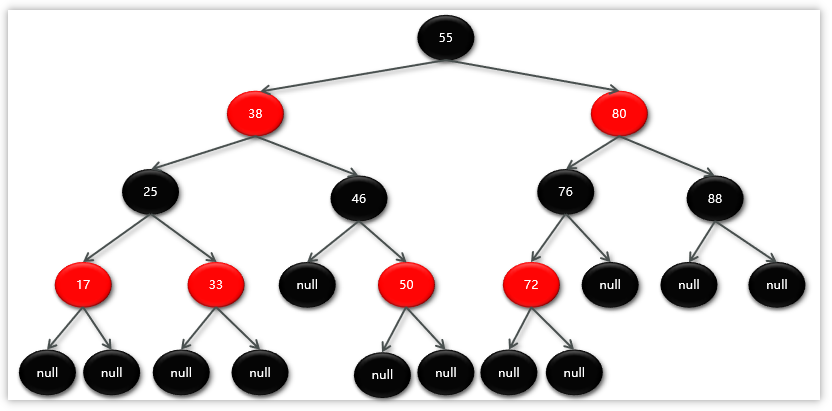

Map相关知识

数据结构 二叉树 二叉树,顾名思义,每个节点最多有两个“叉”,也就是两个子节点,分别是左子 节点和右子节点。不过,二叉树并不要求每个节点都有两个子节点,有的节点只 有左子节点,有的节点只有…...

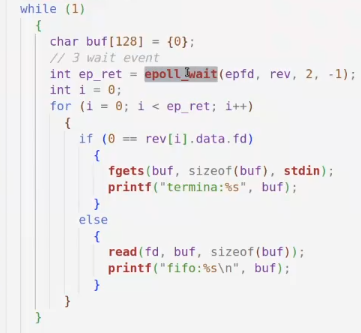

day36-多路IO复用

一、基本概念 (服务器多客户端模型) 定义:单线程或单进程同时监测若干个文件描述符是否可以执行IO操作的能力 作用:应用程序通常需要处理来自多条事件流中的事件,比如我现在用的电脑,需要同时处理键盘鼠标…...

redis和redission的区别

Redis 和 Redisson 是两个密切相关但又本质不同的技术,它们扮演着完全不同的角色: Redis: 内存数据库/数据结构存储 本质: 它是一个开源的、高性能的、基于内存的 键值存储数据库。它也可以将数据持久化到磁盘。 核心功能: 提供丰…...

如何配置一个sql server使得其它用户可以通过excel odbc获取数据

要让其他用户通过 Excel 使用 ODBC 连接到 SQL Server 获取数据,你需要完成以下配置步骤: ✅ 一、在 SQL Server 端配置(服务器设置) 1. 启用 TCP/IP 协议 打开 “SQL Server 配置管理器”。导航到:SQL Server 网络配…...

鸿蒙HarmonyOS 5军旗小游戏实现指南

1. 项目概述 本军旗小游戏基于鸿蒙HarmonyOS 5开发,采用DevEco Studio实现,包含完整的游戏逻辑和UI界面。 2. 项目结构 /src/main/java/com/example/militarychess/├── MainAbilitySlice.java // 主界面├── GameView.java // 游戏核…...

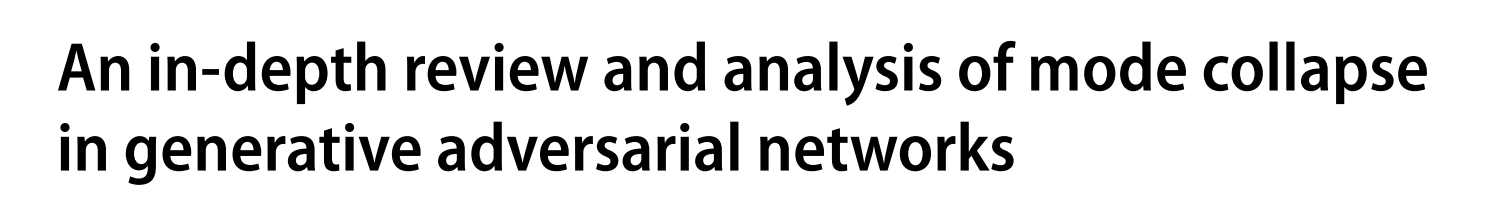

GAN模式奔溃的探讨论文综述(一)

简介 简介:今天带来一篇关于GAN的,对于模式奔溃的一个探讨的一个问题,帮助大家更好的解决训练中遇到的一个难题。 论文题目:An in-depth review and analysis of mode collapse in GAN 期刊:Machine Learning 链接:...

js 设置3秒后执行

如何在JavaScript中延迟3秒执行操作 在JavaScript中,要设置一个操作在指定延迟后(例如3秒)执行,可以使用 setTimeout 函数。setTimeout 是JavaScript的核心计时器方法,它接受两个参数: 要执行的函数&…...

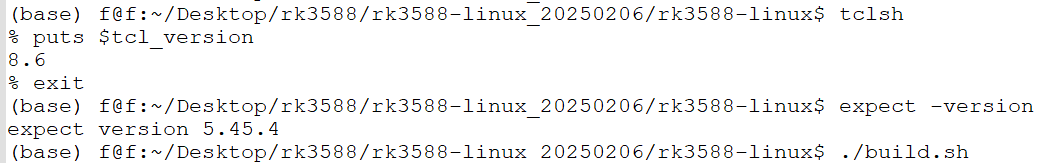

ubuntu中安装conda的后遗症

缘由: 在编译rk3588的sdk时,遇到编译buildroot失败,提示如下: 提示缺失expect,但是实测相关工具是在的,如下显示: 然后查找借助各个ai工具,重新安装相关的工具,依然无解。 解决&am…...

HTML中各种标签的作用

一、HTML文件主要标签结构及说明 1. <!DOCTYPE html> 作用:声明文档类型,告知浏览器这是 HTML5 文档。 必须:是。 2. <html lang“zh”>. </html> 作用:包裹整个网页内容,lang"z…...