Artix7系列FPGA实现SDI视频编解码+图像缩放+多路视频拼接,基于GTP高速接口,提供4套工程源码和技术支持

目录

- 1、前言

- 工程概述

- 免责声明

- 2、相关方案推荐

- 本博已有的 SDI 编解码方案

- 本博已有的FPGA图像缩放方案

- 本博已有的已有的FPGA视频拼接叠加融合方案

- 本方案的无缩放应用

- 本方案在Xilinx--Kintex系列FPGA上的应用

- 本方案在Xilinx--Zynq系列FPGA上的应用

- 3、详细设计方案

- 设计原理框图

- SDI 输入设备

- Gv8601a 均衡器

- GTP 高速接口-->解串与串化

- SMPTE SD/HD/3G SDI IP核

- BT1120转RGB

- 纯Verilog图像缩放模块详解

- 纯Verilog图像缩放模块使用

- FDMA多路视频拼接算法

- FDMA图像缓存

- 视频读取控制

- HDMI输出

- RGB转BT1120

- Gv8500 驱动器

- SDI转HDMI盒子

- 工程源码架构

- 4、工程源码1详解-->2路视频缩放拼接,HDMI输出版本

- 5、工程源码2详解-->4路视频缩放拼接,HDMI输出版本

- 6、工程源码3详解-->2路视频缩放拼接,3G-SDI输出版本

- 7、工程源码4详解-->4路视频缩放拼接,3G-SDI输出版本

- 8、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 9、上板调试验证

- 准备工作

- 2路SDI视频缩放拼接-->输出视频演示

- 4路SDI视频缩放拼接-->输出视频演示

- 10、福利:工程代码的获取

Artix7系列FPGA实现SDI视频编解码+图像缩放+多路视频拼接,基于GTP高速接口,提供4套工程源码和技术支持

1、前言

目前FPGA实现SDI视频编解码有两种方案:一是使用专用编解码芯片,比如典型的接收器GS2971,发送器GS2972,优点是简单,比如GS2971接收器直接将SDI解码为并行的YCrCb422,GS2972发送器直接将并行的YCrCb422编码为SDI视频,缺点是成本较高,可以百度一下GS2971和GS2972的价格;另一种方案是使用FPGA逻辑资源部实现SDI编解码,利用Xilinx系列FPGA的GTP/GTX资源实现解串,利用Xilinx系列FPGA的SMPTE SDI资源实现SDI编解码,优点是合理利用了FPGA资源,GTP/GTX资源不用白不用,缺点是操作难度大一些,对FPGA开发者的技术水平要求较高。有意思的是,这两种方案在本博这里都有对应的解决方案,包括硬件的FPGA开发板、工程源码等等。

工程概述

本设计基于Xilinx的Artix7系列FPGA开发板实现SDI视频编解码,输入源为一个3G-SDI相机或者HDMI转3G-SDI盒子,也可以使用HD-SDI或者SD-SDI相机,因为本设计是三种SDI视频自适应的;同轴的SDI视频通过同轴线连接到FPGA开发板的BNC座子,然后同轴视频经过板载的Gv8601a芯片实现单端转差分和均衡EQ的功能;然后差分SDI视频信号进入FPGA内部的GTP高速资源,实现数据高速串行到并行的转换,本博称之为解串;解串后的并行视频再送入Xilinx系列FPGA特有的SMPTE SD/HD/3G SDI IP核,进行SDI视频解码操作并输出BT1120视频,至此,SDI视频解码操作已经完成,可以进行常规的图像处理操作了;

本设计的目的是做图像缩放后输出解码的SDI视频,针对目前市面上的主流项目需求,本博设计了两种输出方式,一种是HDMI输出,另一种是3G-SDI输出,这两种方式都需要对解码BT1120视频进行转RGB和图像缓存操作和图像缩放操作;图像缩放方案采用纯verilog方案;本设计使用BT1120转RGB模块实现视频格式转换;图像缩放采用纯verilog代码实现的图像缩放架构实现SDI的图像缩放操作,将原始的1920x1080分辨率的SDI视频缩小为960x540,当然,读者也可以缩放为其他分辨率;纯verilog多路视频拼接+图像缓存使用FDMA架构,该架构简单灵活,输入接口为VGA视频时序,即用VS、DE、RGB数据,将不同的视频写入不同的内存地址再统一读出来,以达到拼接效果,FDMA架构的视频既可以缓存介质为DDR3;图像从DDR3读出后,进入HDMI发送模块输出HDMI显示器,这是HDMI输出方式;或者经过RGB转BT1120模块实现视频格式转换,然后视频进入SMPTE SD/HD/3G SDI IP核,进行SDI视频编码操作并输出SDI视频,再经过FPGA内部的GTP高速资源,实现并行数据到高速串行的转换,本博称之为串化,差分高速信号再进入板载的Gv8500芯片实现差分转单端和驱动增强的功能,SDI视频通过FPGA开发板的BNC座子输出,通过同轴线连接到SDI转HDMI盒子连接到HDMI显示器,这是SDI输出方式;本博客提供4套工程源码,具体如下:

现对上述4套工程源码做如下解释,方便读者理解:

工程源码1

开发板FPGA型号为Xilinx–>Xilinx-Artix7-100T–xc7a100tfgg484-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTP将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;再经过2路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为960x540;再经过自研的2路FPGA图像缓存方案将视频写入DDR3,其中一路FDMA配置为读写,另一路FDMA配置为单写;将不同的视频写入不同的内存地址再统一读出来,以达到拼接效果;然后将拼接视频送入RGB转HDMI模块,将RGB888视频转换为HDMI视频,输出分辨率为1920x1080@60Hz背景下叠加显示2路960x540的有效图像,即2分屏,详细显示效果请看文章末尾的输出演示视频;最后通过HDMI显示器显示图像;该工程需要缓存,适用于Xilinx的Artix7低端系列FPGA实现SDI转HDMI场景;

工程源码2

开发板FPGA型号为Xilinx–>Xilinx-Artix7-100T–xc7a100tfgg484-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTP将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;然后将2路视频分别复制1份得到4路视频,以模拟4路输入(如果你的开发板有4路输入,则无需此操作);再经过4路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为960x540;再经过自研的4路FPGA图像缓存方案将视频写入DDR3,其中三路FDMA配置为读写,另一路FDMA配置为单写;将不同的视频写入不同的内存地址再统一读出来,以达到拼接效果;然后将拼接视频送入RGB转HDMI模块,将RGB888视频转换为HDMI视频,输出分辨率为1920x1080@60Hz背景下叠加显示4路960x540的有效图像,即4分屏,详细显示效果请看文章末尾的输出演示视频;最后通过HDMI显示器显示图像;该工程需要缓存,适用于Xilinx的Artix7低端系列FPGA实现SDI转HDMI场景;

工程源码3

开发板FPGA型号为Xilinx–>Xilinx-Artix7-100T–xc7a100tfgg484-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTP将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;再经过2路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为960x540;再经过自研的2路FPGA图像缓存方案将视频写入DDR3,其中一路FDMA配置为读写,另一路FDMA配置为单写;将不同的视频写入不同的内存地址再统一读出来,以达到拼接效果;然后将视频送RGB转BT1120模块,将RGB888视频转换为BT1120视频;再经过SMPTE SD/HD/3G SDI IP核,将BT1120视频编码为SDI视频;再经过FPGA内部的GTP高速资源,将SDI并行数据转换为高速串行信号;再经过板载的Gv8500芯片实现差分转单端和驱动增强后输出,输出分辨率为1920x1080@60Hz背景下叠加显示2路960x540的有效图像,即2分屏,最后使用SDI转HDMI盒子连接到HDMI显示器显示;详细显示效果请看文章末尾的输出演示视频;该工程需要缓存,适用于Xilinx的Artix7低端系列FPGA实现SDI转SDI场景;

工程源码4

开发板FPGA型号为Xilinx–>Xilinx-Artix7-100T–xc7a100tfgg484-2;输入源有两个,一个是3G-SDI相机,分辨率为1920x1080@60Hz,另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机,分辨率为1920x1080@60Hz;两路输入视频经过板载的2个Gv8601a芯片实现单端转差分和均衡EQ后送入FPGA;再经过2路GTP将SDI视频解串为并行数据;再经过2路SMPTE SDI IP核将SDI解码为2路BT1120数据;再经过2路BT1120转RGB模块将BT1120转换为RGB888视频;然后将2路视频分别复制1份得到4路视频,以模拟4路输入(如果你的开发板有4路输入,则无需此操作);再经过4路自研的纯verilog实现的、支持任意比例缩放的图像缩放模块,将输入视频由1920x1080缩放为960x540;再经过自研的4路FPGA图像缓存方案将视频写入DDR3,其中三路FDMA配置为读写,另一路FDMA配置为单写;将不同的视频写入不同的内存地址再统一读出来,以达到拼接效果;然后将视频送RGB转BT1120模块,将RGB888视频转换为BT1120视频;再经过SMPTE SD/HD/3G SDI IP核,将BT1120视频编码为SDI视频;再经过FPGA内部的GTP高速资源,将SDI并行数据转换为高速串行信号;再经过板载的Gv8500芯片实现差分转单端和驱动增强后输出,输出分辨率为1920x1080@60Hz背景下叠加显示4路960x540的有效图像,即4分屏,最后使用SDI转HDMI盒子连接到HDMI显示器显示;详细显示效果请看文章末尾的输出演示视频;该工程需要缓存,适用于Xilinx的Artix7低端系列FPGA实现SDI转SDI场景;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

2、相关方案推荐

本博已有的 SDI 编解码方案

我的博客主页开设有SDI视频专栏,里面全是FPGA编解码SDI的工程源码及博客介绍;既有基于GS2971/GS2972的SDI编解码,也有基于GTP/GTX资源的SDI编解码;既有HD-SDI、3G-SDI,也有6G-SDI、12G-SDI等;专栏地址链接如下:

点击直接前往

本博已有的FPGA图像缩放方案

我的主页目前有FPGA图像缩放专栏,改专栏收录了我目前手里已有的FPGA图像缩放方案,从实现方式分类有基于HSL实现的图像缩放、基于纯verilog代码实现的图像缩放;从应用上分为单路视频图像缩放、多路视频图像缩放、多路视频图像缩放拼接;从输入视频分类可分为OV5640摄像头视频缩放、SDI视频缩放、MIPI视频缩放等等;以下是专栏地址:

点击直接前往

本博已有的已有的FPGA视频拼接叠加融合方案

我的主页目前有FPGA视频拼接叠加融合专栏,改专栏收录了我目前手里已有的FPGA视频拼接叠加融合方案,从实现方式分类有基于HSL实现的视频拼接、基于纯verilog代码实现的视频拼接;从应用上分为单路、2路、3路、4路、8路、16路视频拼接;视频缩放+拼接;视频融合叠加;从输入视频分类可分为OV5640摄像头视频拼接、SDI视频拼接、CameraLink视频拼接等等;以下是专栏地址:

点击直接前往

本方案的无缩放应用

本方案有无缩放版本的应用,只做SDI视频编解码,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

本方案在Xilinx–Kintex系列FPGA上的应用

本方案在Xilinx–Kintex系列FPGA上的也有应用,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

本方案在Xilinx–Zynq系列FPGA上的应用

本方案在Xilinx–Zynq系列FPGA上的也有应用,之前专门写过一篇博客,博客地址链接如下:

点击直接前往

3、详细设计方案

设计原理框图

设计原理框图如下:

注意!!!!

注意!!!!

紫色箭头:3G-SDI输出路径

红色箭头:HDMI输出路径

SDI 输入设备

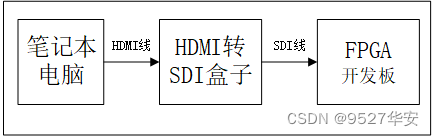

SDI 输入设备有两个,分别接入FPGA开发板的2路SDI视频输入接口;一个是3G-SDI相机,分辨率为1920x1080@60Hz,也可以使用HD-SDI或者SD-SDI相机,因为本设计是三种SDI视频自适应的;另一个HDMI转3G-SDI盒子,盒子外接笔记本电脑以模拟SDI相机;SDI相机相对比较贵,预算有限的朋友可以考虑用HDMI转SDI盒子模拟SDI相机,这种盒子某宝一百块左右;当使用HDMI转SDI盒子时,输入源可以用笔记本电脑,即用笔记本电脑通过HDMI线连接到HDMI转SDI盒子的HDMI输入接口,再用SDI线连接HDMI转SDI盒子的SDI输出接口到FPGA开发板,如下:

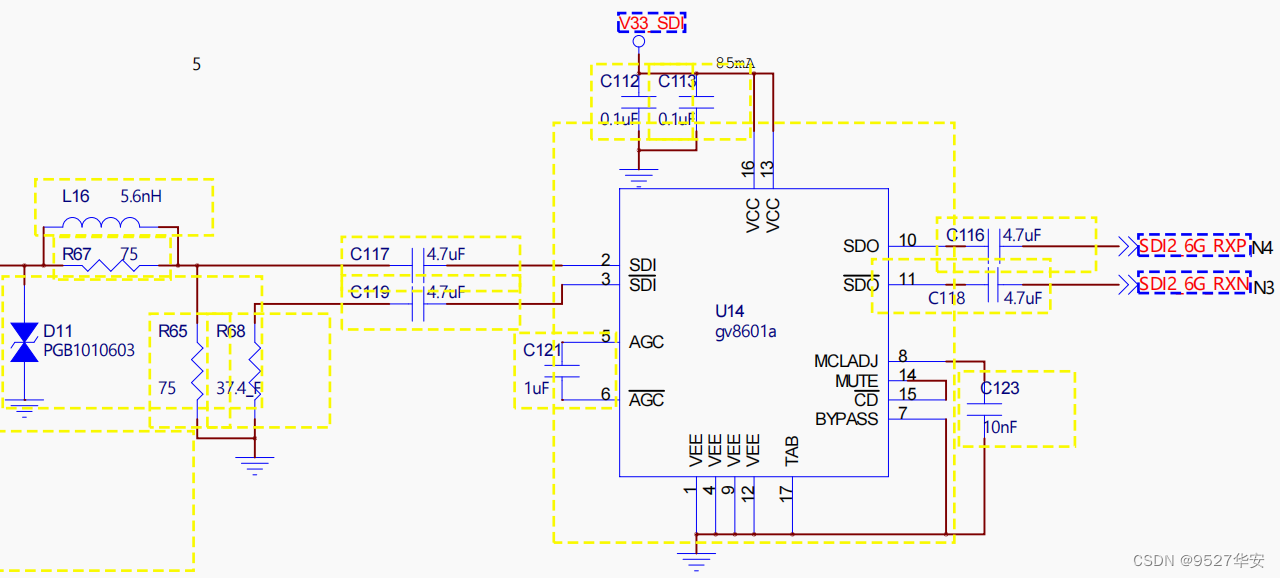

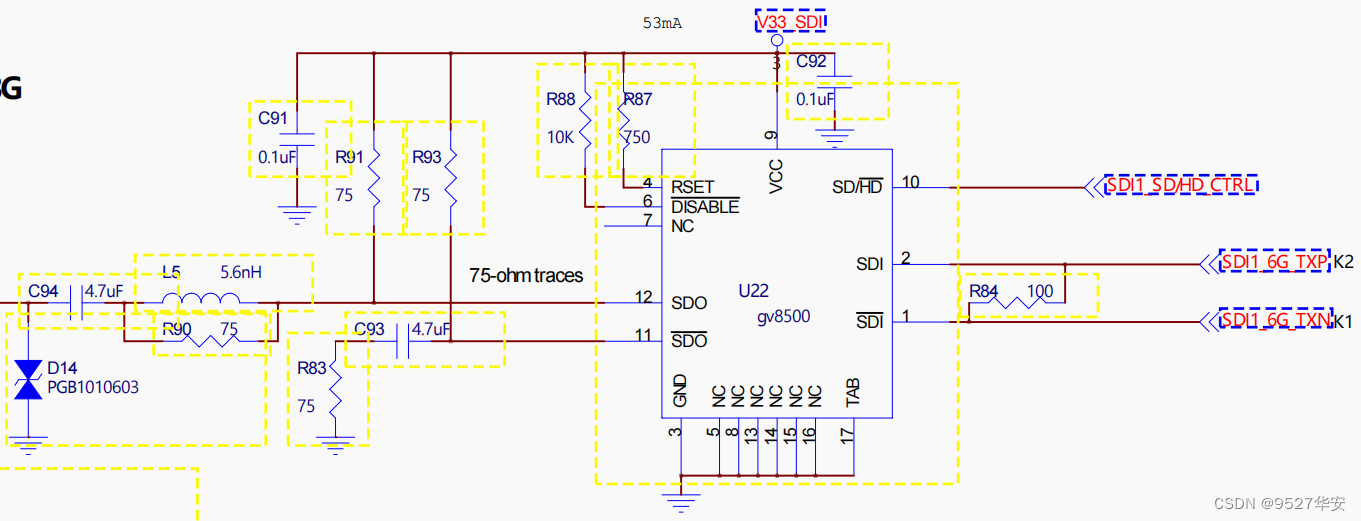

Gv8601a 均衡器

Gv8601a芯片实现单端转差分和均衡EQ的功能,这里选用Gv8601a是因为借鉴了了Xilinx官方的方案,当然也可以用其他型号器件。Gv8601a均衡器原理图如下:

GTP 高速接口–>解串与串化

本设计使用Xilinx特有的GTP高速信号处理资源实现SDI差分视频信号的解串与串化,对于SDI视频接收而言,GTP起到解串的作用,即将输入的高速串行的差分信号解为并行的数字信号;对于SDI视频发送而言,GTP起到串化的作用,即将输入的并行的数字信号串化为高速串行的差分信号;GTP的使用一般需要例化GTP IP核,通过vivado的UI界面进行配置,但本设计需要对SD-SDI、HD-SDI、3G-SDI视频进行自动识别和自适应处理,所以需要使得GTP具有动态改变线速率的功能,该功能可通过DRP接口配置,也可通过GTP的rate接口配置,所以不能使用vivado的UI界面进行配置,而是直接例化GTP的GTPE2_CHANNEL和GTPE2_COMMON源语直接使用GTP资源;此外,为了动态配置GTP线速率,还需要GTP控制模块,该模块参考了Xilinx的官方设计方案,具有动态监测SDI模式,动态配置DRP等功能;该方案参考了Xilinx官方的设计;GTP 解串与串化模块代码架构如下:

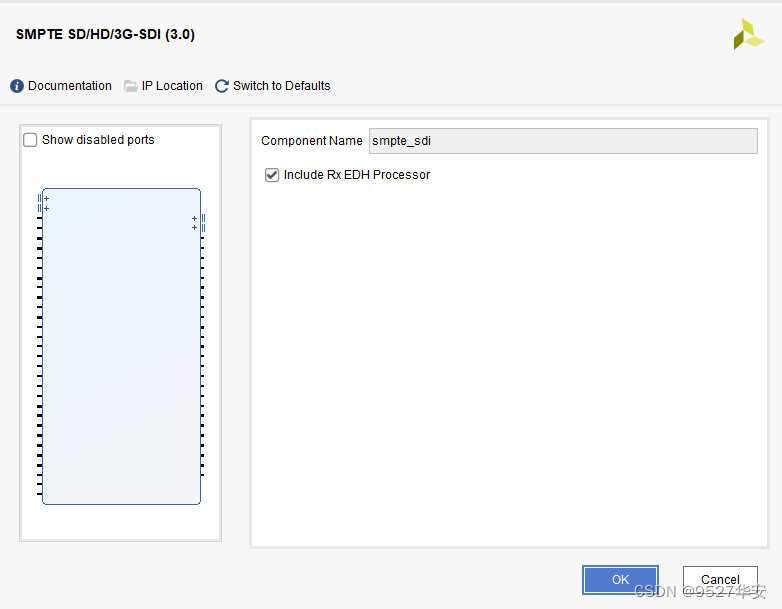

SMPTE SD/HD/3G SDI IP核

SMPTE SD/HD/3G SDI IP核是Xilinx系列FPGA特有的用于SDI视频编解码的IP,该IP配置使用非常简单,vivado的UI界面如下:

SMPTE SD/HD/3G SDI IP核必须与GTP配合才能使用,对于SDI视频接收而言,该IP接收来自于GTP的数据,然后将SDI视频解码为BT1120视频输出,对于SDI视频发送而言,该IP接收来自于用户侧的的BT1120视频数据,然后将BT1120视频编码为SDI视频输出;该方案参考了Xilinx官方的设计;SMPTE SD/HD/3G SDI IP核代码架构如下:

BT1120转RGB

BT1120转RGB模块的作用是将SMPTE SD/HD/3G SDI IP核解码输出的BT1120视频转换为RGB888视频,它由BT1120转CEA861模块、YUV422转YUV444模块、YUV444转RGB888三个模块组成,该方案参考了Xilinx官方的设计;BT1120转RGB模块代码架构如下:

纯Verilog图像缩放模块详解

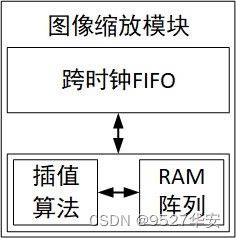

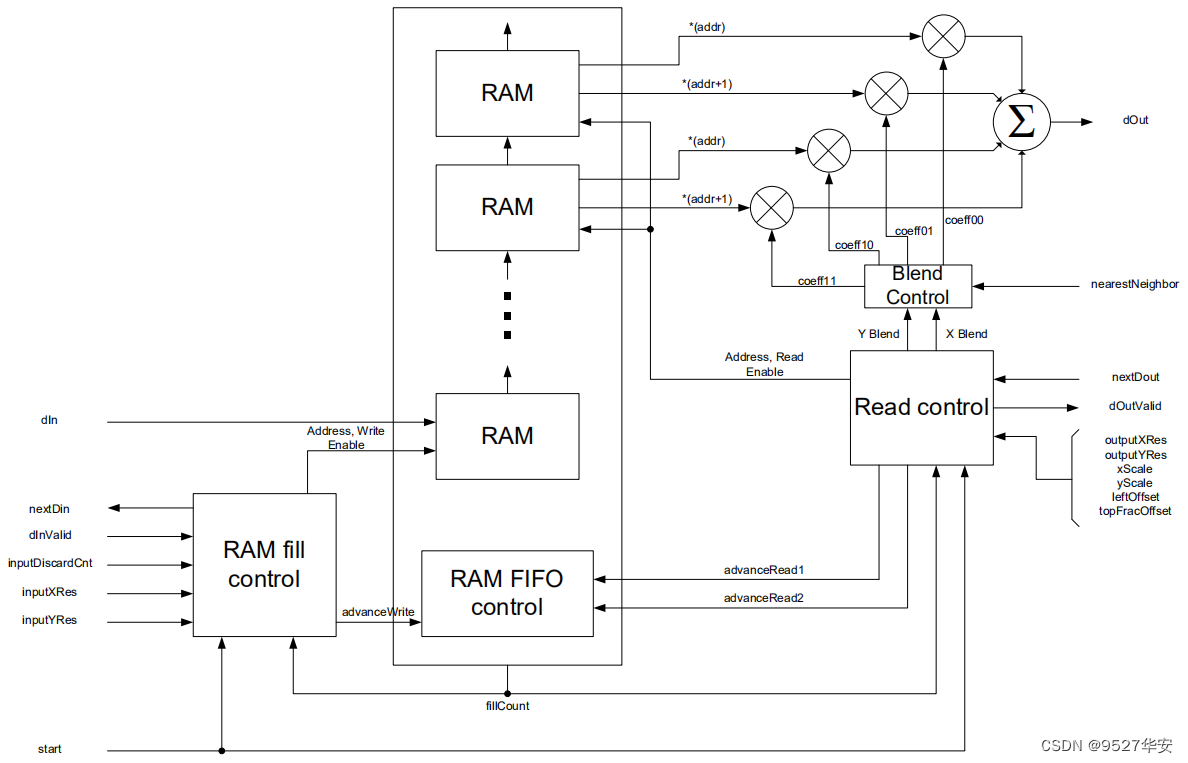

工程源码1、2的图像缩放模块使用纯Verilog方案,功能框图如下,由跨时钟FIFO、插值+RAM阵列构成,跨时钟FIFO的目的是解决跨时钟域的问题,比如从低分辨率视频放大到高分辨率视频时,像素时钟必然需要变大,这是就需要异步FIFO了,插值算法和RAM阵列具体负责图像缩放算法层面的实现;

插值算法和RAM阵列以ram和fifo为核心进行数据缓存和插值实现,设计架构如下:

图像缩放模块代码架构如下:模块的例化请参考工程源码的顶层代码;

图像缩放模块FIFO的选择可以调用工程对应的vivado工具自带的FIFO IP核,也可以使用纯verilog实现的FIFO,可通过接口参数选择,图像缩放模块顶层接口如下:

module helai_video_scale #(//---------------------------Parameters----------------------------------------parameter FIFO_TYPE = "xilinx", // "xilinx" for xilinx-fifo ; "verilog" for verilog-fifoparameter DATA_WIDTH = 8 , //Width of input/output dataparameter CHANNELS = 1 , //Number of channels of DATA_WIDTH, for color imagesparameter INPUT_X_RES_WIDTH = 11 //Widths of input/output resolution control signals

)(input i_reset_n , // 输入--低电平复位信号input [INPUT_X_RES_WIDTH-1:0] i_src_video_width , // 输入视频--即缩放前视频的宽度input [INPUT_X_RES_WIDTH-1:0] i_src_video_height, // 输入视频--即缩放前视频的高度input [INPUT_X_RES_WIDTH-1:0] i_des_video_width , // 输出视频--即缩后前视频的宽度input [INPUT_X_RES_WIDTH-1:0] i_des_video_height, // 输出视频--即缩后前视频的高度input i_src_video_pclk , // 输入视频--即缩前视频的像素时钟input i_src_video_vs , // 输入视频--即缩前视频的场同步信号,必须为高电平有效input i_src_video_de , // 输入视频--即缩前视频的数据有效信号,必须为高电平有效input [DATA_WIDTH*CHANNELS-1:0] i_src_video_pixel , // 输入视频--即缩前视频的像素数据input i_des_video_pclk , // 输出视频--即缩后视频的像素时钟,一般为写入DDR缓存的时钟output o_des_video_vs , // 输出视频--即缩后视频的场同步信号,高电平有效output o_des_video_de , // 输出视频--即缩后视频的数据有效信号,高电平有效output [DATA_WIDTH*CHANNELS-1:0] o_des_video_pixel // 输出视频--即缩后视频的像素数据

);

FIFO_TYPE选择原则如下:

1:总体原则,选择"xilinx"好处大于选择"verilog";

2:当你的FPGA逻辑资源不足时,请选"xilinx";

3:当你图像缩放的视频分辨率较大时,请选"xilinx";

4:当你的FPGA没有FIFO IP或者FIFO IP快用完了,请选"verilog";

5:当你向自学一下异步FIFO时,,请选"verilog";

6:不同FPGA型号对应的工程FIFO_TYPE参数不一样,但选择原则一样,具体参考代码;

2种插值算法的整合与选择

本设计将常用的双线性插值和邻域插值算法融合为一个代码中,通过输入参数选择某一种算法;

具体选择参数如下:

input wire i_scaler_type //0-->bilinear;1-->neighbor

通过输入i_scaler_type 的值即可选择;

输入0选择双线性插值算法;

输入1选择邻域插值算法;

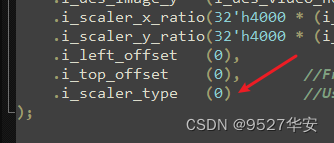

代码里的配置如下:

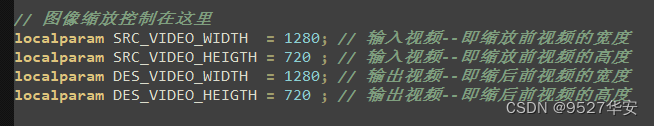

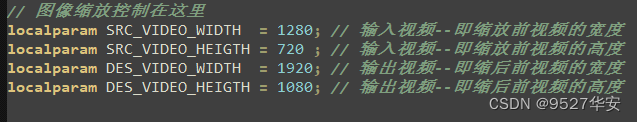

纯Verilog图像缩放模块使用

图像缩放模块使用非常简单,顶层代码里设置了四个参数,举例如下:

上图视频通过图像缩放模块但不进行缩放操作,旨在掌握图像缩放模块的用法;如果需要将图像放大到1080P,则修改为如下:

当然,需要修改的不仅仅这一个地方,FDMA的配置也需要相应修改,详情请参考代码,但我想要证明的是,图像缩放模块使用非常简单,你都不需要知道它内部具体怎么实现的,上手就能用;

FDMA多路视频拼接算法

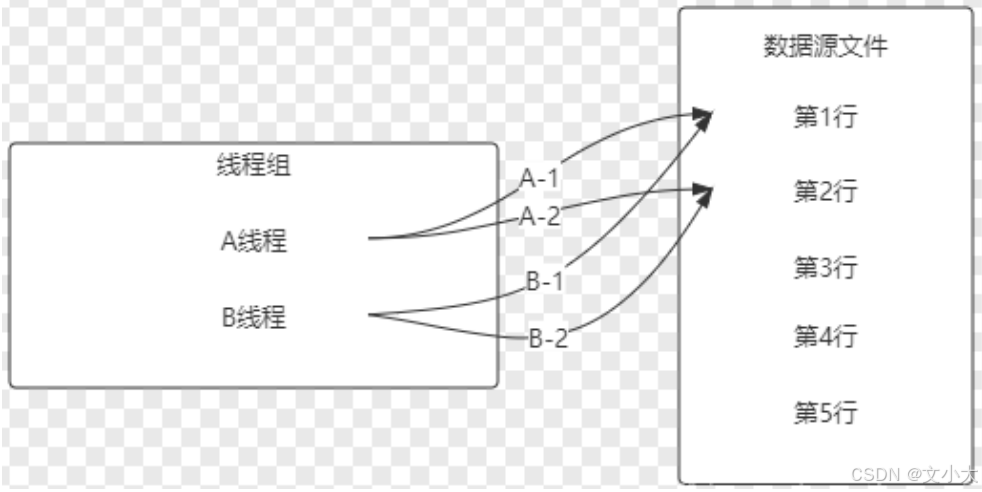

纯verilog多路视频拼接方案如下:以4路视频拼接为例;

输出屏幕分辨率为1920X1080;

需要拼接的4路视频分辨率为960X540;

4路输入刚好可以占满整个屏幕;

多路视频的拼接显示原理如下:

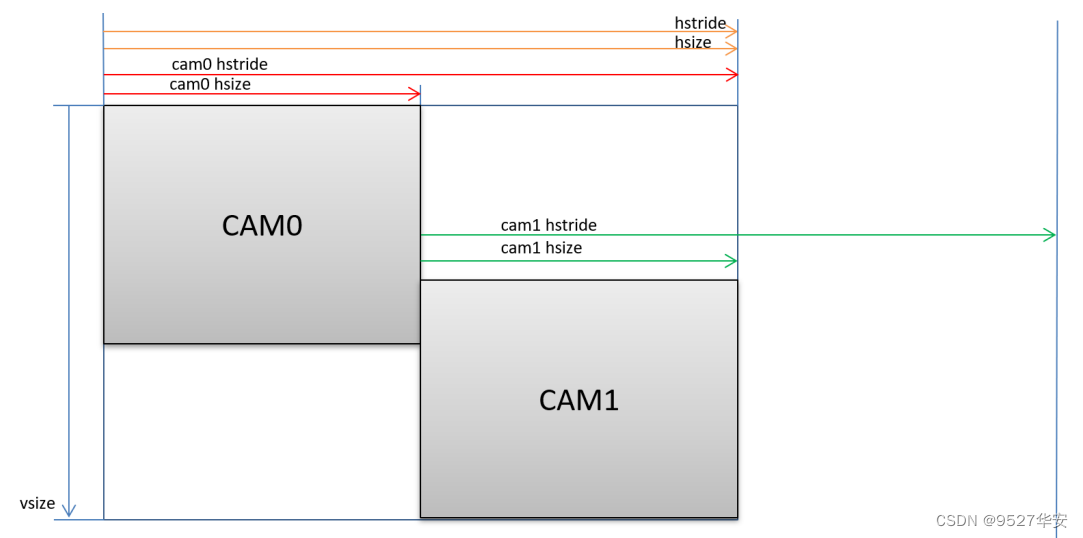

以把 2 个摄像头 CAM0 和 CAM1 输出到同一个显示器上为列,为了把 2 个图像显示到 1 个显示器,首先得搞清楚以下关系:

hsize:每 1 行图像实际在内存中占用的有效空间,以 32bit 表示一个像素的时候占用内存大小为 hsize X 4;

hstride:用于设置每行图像第一个像素的地址,以 32bit 表示一个像素的时候 v_cnt X hstride X 4;

vsize:有效的行;

因此很容易得出 cam0 的每行第一个像素的地址也是 v_cnt X hstride X 4;

同理如果我们需要把 cam1 在 hsize 和 vsize 空间的任何位置显示,我们只要关心 cam1 每一行图像第一个像素的地址,可以用以下公式 v_cnt X hstride X 4 + offset;

uifdma_dbuf 支持 stride 参数设置,stride 参数可以设置输入数据 X(hsize)方向每一行数据的第一个像素到下一个起始像素的间隔地址,利用 stride 参数可以非常方便地摆放输入视频到内存中的排列方式。

关于uifdma_dbuf,可以参考我之前写的文章点击查看:FDMA实现视频数据三帧缓存

根据以上铺垫,每路摄像头缓存的基地址如下:

CAM0:ADDR_BASE=0x80000000;

CAM1:ADDR_BASE=0x80000000+(1920-960)X4;

CAM2:ADDR_BASE=0x80000000+(1080-540)X1920X4;

CAM3:ADDR_BASE=0x80000000+(1080-540)X1920X4+(1920-960)X4;

地址设置完毕后基本就完事儿了;

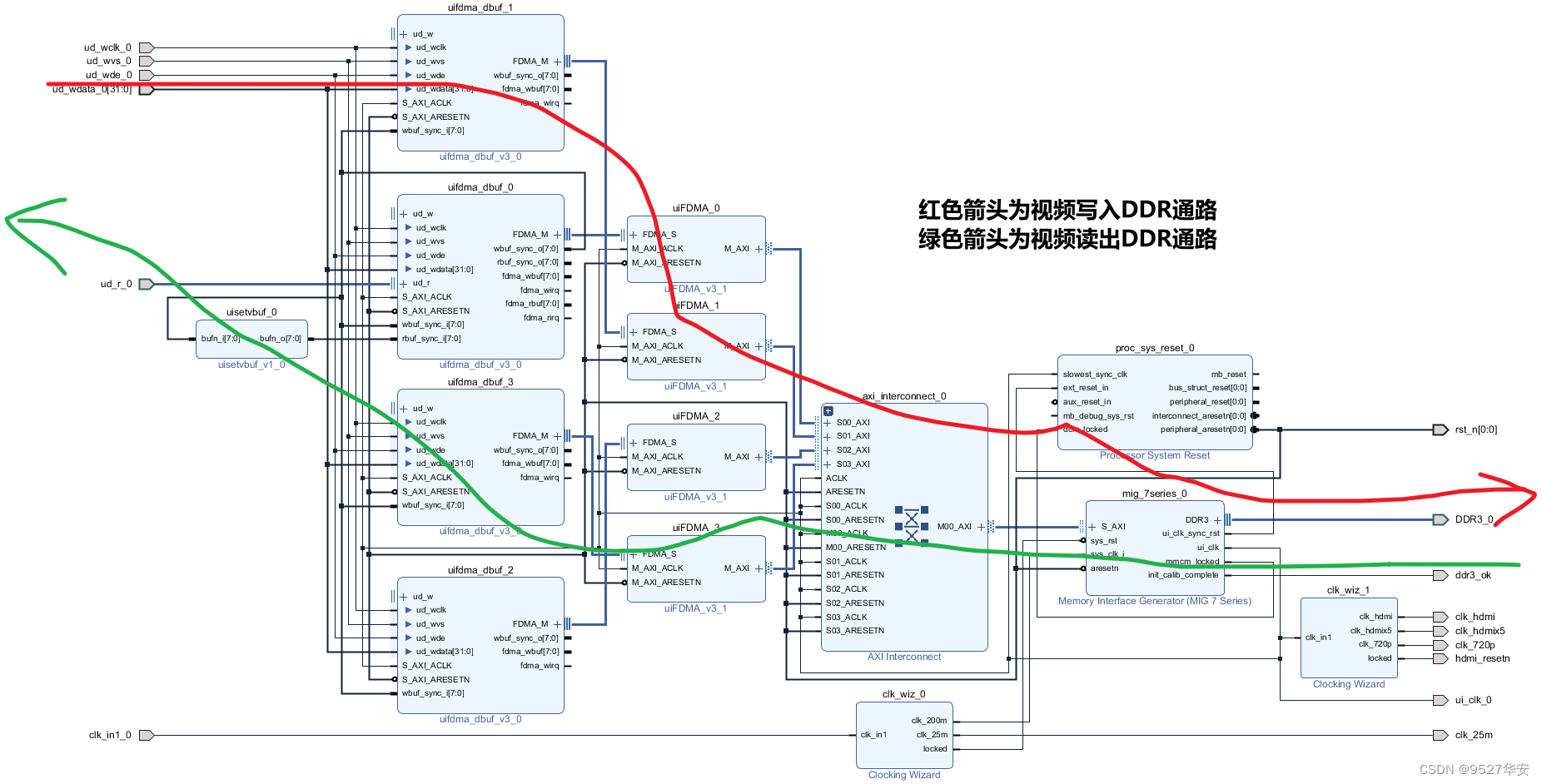

FDMA图像缓存

使用本博常用的FDMA图像缓存架构实现图像3帧缓存,缓存介质为板载的DDR3;FDMA图像缓存架构由FDMA、FDMA控制器、缓存帧选择器构成、Xilinx MIG IP核构成;图像缓存使用Xilinx vivado的Block Design设计,他的作用是将图像送入DDR中做3帧缓存再读出显示,目的是匹配输入输出的时钟差和提高输出视频质量,关于FDMA,请参考我之前的博客,博客地址:点击直接前往

FDMA图像缓存架构如下图所示:截图为4路视频拼接,其他多路视频拼接与之类似;

这里多路视频拼接时,调用多路FDMA进行缓存,具体讲就是每一路视频调用1路FDMA,以4路视频拼接为例:

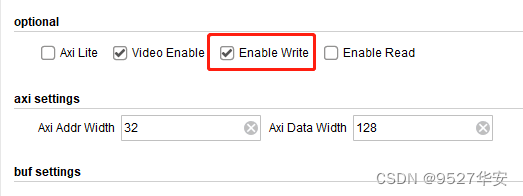

调用4路FDMA,其中三路配置为写模式,因为这三路视频在这里只需要写入DDR3,读出是由另一个FDMA完成,配置如下:

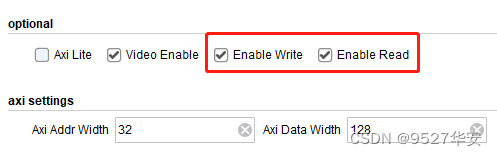

另外1路FDMA配置为读写模式,因为4路视频需要同时一并读出,配置如下:

视频拼接的关键点在于4路视频在DDR3中缓存地址的不同,还是以4路视频拼接为例,4路FDMA的写地址以此为:

第一路视频缓存写基地址:0x80000000;

第二路视频缓存写基地址:0x80000f00;

第三路视频缓存写基地址:0x803f4800;

第四路视频缓存写基地址:0x803f5700;

视频缓存读基地址:0x80000000;

视频读取控制

FDMA图像缓存架构使用VGA时序模块完成视频读取控制,VGA时序模块负责产生VGA时序,他有两个作用,一是控制FDMA控制器从DDR3中读出缓存的视频,二是将同步后的VGA视频送入下一级模块,在HDMI输出方式下VGA时序模块的像素时钟由用户提供;在SDI输出方式下VGA时序模块的像素时钟由SMPTE SD/HD/3G SDI IP核的发送用户时钟提供,在不同的SDI模式下像素时钟不同,比如在3G-SDI模式下像素时钟为148.5M,在HD-SDI的720P@60Hz模式下像素时钟为74.25M;HDMI输出方式下的VGA时序模块代码架构如下:

SDI输出方式下的VGA时序模块代码架构如下:

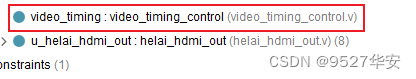

HDMI输出

在HDMI输出方式下,使用HDMI输出模块将RGB视频编码为HDMI差分信号,HDMI输出模块采用verilog代码手写,可以用于FPGA的HDMI发送应用,代码如下:

关于这个模块,请参考我之前的博客,博客地址:点击直接前往

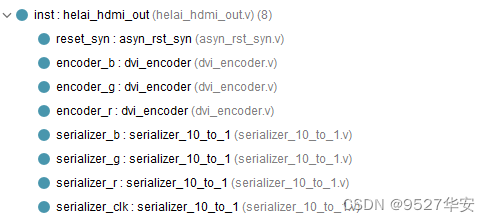

RGB转BT1120

在SDI输出方式下需要使用该模块;RGB转BT1200模块的作用是将用户侧的RGB视频转换为BT1200视频输出给SMPTE SD/HD/3G SDI IP核;RGB转BT1120模块由RGB888转YUV444模块、YUV444转YUV422模块、SDI视频编码模块、数据嵌入模块组成,该方案参考了Xilinx官方的设计;BT1120转RGB模块代码架构如下:

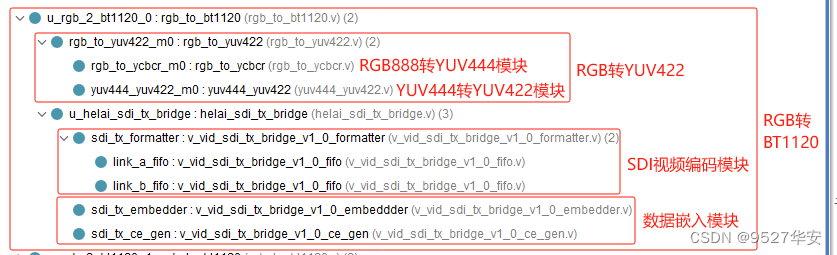

Gv8500 驱动器

Gv8500芯片实现差分转单端和增强驱动的功能,这里选用Gv8500是因为借鉴了了Xilinx官方的方案,当然也可以用其他型号器件。Gv8500驱动器原理图如下:

SDI转HDMI盒子

在SDI输出方式下需要使用到SDI转HDMI盒子,因为我手里的显示器没有SDI接口,只有HDMI接口,为了显示SDI视频,只能这么做,当然,如果你的显示器有SDI接口,则可直接连接显示,我的SDI转HDMI盒子在某宝购买,不到100块;

工程源码架构

本博客提供4套工程源码,以工程源码1为例,vivado Block Design设计如下,其他工程与之类似,Block Design设计为图像缓存架构的部分:

以工程源码1为例,使工程源码架构如下,其他工程与之类似:

4、工程源码1详解–>2路视频缩放拼接,HDMI输出版本

开发板FPGA型号:Xilinx-Artix7-100T–xc7a100tfgg484-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz;

输出:HDMI ,1920x1080@60Hz背景下叠加显示2路拼接的960x540的有效图像;

SDI视频解串方案:Xilinx–GTP高速接口解串;

SDI视频解码方案:Xilinx–SMPTE SD/HD/3G SDI解码;

图像缩放方案:自研纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到960x540;

图像缓存方案:自研FDMA方案;

图像缓存介质:DDR3;

视频拼接方案:自研FDMA方案;

视频拼接应用:2路视频拼接;

工程作用:此工程目的是让读者掌握Xilinx–Artix7低端系列FPGA实现SDI转HDMI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

5、工程源码2详解–>4路视频缩放拼接,HDMI输出版本

开发板FPGA型号:Xilinx-Artix7-100T–xc7a100tfgg484-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz;

输出:HDMI ,1920x1080@60Hz背景下叠加显示4路拼接的960x540的有效图像;

SDI视频解串方案:Xilinx–GTP高速接口解串;

SDI视频解码方案:Xilinx–SMPTE SD/HD/3G SDI解码;

图像缩放方案:自研纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到960x540;

图像缓存方案:自研FDMA方案;

图像缓存介质:DDR3;

视频拼接方案:自研FDMA方案;

视频拼接应用:4路视频拼接;

工程作用:此工程目的是让读者掌握Xilinx–Artix7低端系列FPGA实现SDI转HDMI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

6、工程源码3详解–>2路视频缩放拼接,3G-SDI输出版本

开发板FPGA型号:Xilinx-Artix7-100T–xc7a100tfgg484-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz;

输出:3G-SDI,1920x1080@60Hz背景下叠加显示2路拼接的960x540的有效图像;

SDI视频解串方案:Xilinx–GTP高速接口解串;

SDI视频解码方案:Xilinx–SMPTE SD/HD/3G SDI解码;

图像缩放方案:自研纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到960x540;

图像缓存方案:自研FDMA方案;

图像缓存介质:DDR3;

视频拼接方案:自研FDMA方案;

视频拼接应用:2路视频拼接;

工程作用:此工程目的是让读者掌握Xilinx–Artix7低端系列FPGA实现SDI转3G-SDI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

7、工程源码4详解–>4路视频缩放拼接,3G-SDI输出版本

开发板FPGA型号:Xilinx-Artix7-100T–xc7a100tfgg484-2;

开发环境:Vivado2019.1;

输入1:3G-SDI相机,分辨率1920x1080@60Hz;

输入2:HDMI转SDI盒子(外接笔记本电脑),分辨率1920x1080@60Hz;

输出:3G-SDI,1920x1080@60Hz背景下叠加显示4路拼接的960x540的有效图像;

SDI视频解串方案:Xilinx–GTP高速接口解串;

SDI视频解码方案:Xilinx–SMPTE SD/HD/3G SDI解码;

图像缩放方案:自研纯Verilog图像缩放;

图像缩放实例:1920x1080缩放到960x540;

图像缓存方案:自研FDMA方案;

图像缓存介质:DDR3;

视频拼接方案:自研FDMA方案;

视频拼接应用:4路视频拼接;

工程作用:此工程目的是让读者掌握Xilinx–Artix7低端系列FPGA实现SDI转3G-SDI的设计能力,以便能够移植和设计自己的项目;

工程Block Design和工程代码架构请参考第3章节的《工程源码架构》小节内容;

工程的资源消耗和功耗如下:

8、工程移植说明

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

9、上板调试验证

准备工作

需要准备的器材如下:

FPGA开发板;

SDI摄像头或HDMI转SDI盒子;

SDI转HDMI盒子;

HDMI显示器;

我的开发板了连接如下:

2路SDI视频缩放拼接–>输出视频演示

2路SDI视频缩放拼接,输出如下:

Zynq-SDI-2路视频拼接

4路SDI视频缩放拼接–>输出视频演示

4路SDI视频缩放拼接,输出如下:

Zynq-SDI-4路视频拼接

10、福利:工程代码的获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

此外,有很多朋友给本博主提了很多意见和建议,希望能丰富服务内容和选项,因为不同朋友的需求不一样,所以本博主还提供以下服务:

相关文章:

Artix7系列FPGA实现SDI视频编解码+图像缩放+多路视频拼接,基于GTP高速接口,提供4套工程源码和技术支持

目录 1、前言工程概述免责声明 2、相关方案推荐本博已有的 SDI 编解码方案本博已有的FPGA图像缩放方案本博已有的已有的FPGA视频拼接叠加融合方案本方案的无缩放应用本方案在Xilinx--Kintex系列FPGA上的应用本方案在Xilinx--Zynq系列FPGA上的应用 3、详细设计方案设计原理框图S…...

HTTP 状态码详细介绍

超文本传输协议(Hypertext Transfer Protocol,HTTP)是一个简单的请求-响应协议,它通常运行在TCP之上。它指定了客户端可能发送给服务器什么样的消息以及得到什么样的响应。请求和响应消息的头以ASCII形式给出;而消息内…...

React前端面试每日一试 5.什么是受控组件和非受控组件?

在React中,受控组件和非受控组件是两种处理表单数据的方式。理解这两种方式对于管理和维护表单状态非常重要。 受控组件(Controlled Components) 受控组件是指那些表单数据完全由React组件的状态控制的组件。也就是说,表单元素的…...

代码随想录打卡第四十四天

代码随想录–动态规划部分 day 44 动态规划第11天 文章目录 代码随想录--动态规划部分一、力扣1143--最长公共子序列二、力扣1035--不相交的线三、力扣53--最大子数组和四、力扣392--判断子序列 一、力扣1143–最长公共子序列 代码随想录题目链接:代码随想录 给定…...

【JAVA】枚举类的使用:通过枚举类名称得到对应值进行输出

枚举类其实就是一个特殊的class。 /*** ClassName: CardType* Description:数字卡类型对应的文字卡类型*/ public enum CardType {NORMAL_CARD("金普卡"),BUSINESS_CARD("商务卡"),PRIVATE_CARD("黑金无限卡");private String cardName;CardTyp…...

20240731软考架构------软考6-10答案解析

每日打卡题6-10答案 6、【2012年真题】 难度:一般 若系统中的某子模块需要为其他模块提供访问不同数据库系统的功能,这些数据库系统提供的访问接口有一定的差异,但访问过程却都是相同的,例如,先连接数据库,…...

学习记录——day25 多线程编程 临界资源 临界区 竞态 线程的同步互斥机制(用于解决竟态)

目录 编辑 一、多进程与多线程对比 二、 临界资源 临界区 竞态 例1:临界资源 实现 输入输出 例2:对临界资源 进行 减减 例子3:临界资源抢占使用 三、线程的同步互斥机制(用于解决竟态) 3.1基本概念 3.2线…...

[RK3566]linux下使用upgrade_tool报错

linux下使用upgrade_tool报错Creating Comm Object failed! Rockusb>uf /home/zhuhongxi/RK3566_AOSP_SDK/rockdev/Image-rk3566_tspi/update.img Loading firmware... Support Type:RK3568 FW Ver:b.0.00 FW Time:2024-08-03 12:00:09 Loader ver:1.01 Loader Time:…...

)

系统架构师(每日一练13)

每日一练 答案与解析 1.应用系统构建中可以采用多种不同的技术,()可以将软件某种形式的描述转换为更高级的抽象表现形式,而利用这些获取的信息,()能够对现有系统进行修改或重构,从而产生系统的一个新版本。答案与解析 问题1 A.逆…...

Error: No module factory available for dependency type: CssDependency

本篇主要用来记录VUE打包的问题点,今天使用npm run build:prod 打包VUE出现如下问题: Error: No module factory available for dependency type: CssDependency 因为测试和预发布都挺正常的,正式环境竟然出问题,废话不多说&…...

【langchain学习】使用Langchain生成多视角查询

使用Langchain生成多视角查询 导入所需库: from langchain.prompts import ChatPromptTemplate from langchain_core.output_parsers import StrOutputParser from langchain_core.runnables import RunnablePassthrough from config import llm设置提示模板&#x…...

ASPCMS 漏洞详细教程

一.后台修改配置文件拿shell 登录后台 如下操作 保存并抓包 将slideTextStatus的值修改为1%25><%25Eval(Request(chr(65)))25><%25 放包(连接密码是a) 然后用工具连接 成功连接...

二维码生成原理及解码原理

☝☝☝二维码配图 二维码 二维码(Quick Response Code,简称QR码)是一种广泛使用的二维条形码技术,由日本公司Denso Wave在1994年开发。二维码能有效地存储和传递信息,广泛应用于商品追溯、支付、广告等多个领域。二维…...

云计算实训20——mysql数据库安装及应用(增、删、改、查)

一、mysql安装基本步骤 1.下载安装包 wget https://downloads.mysql.com/archives/get/p/23/file/mysql-8.0.33-1.el7.x86_64.rpm-bundle.tar 2.解压 tar -xf mysql-8.0.33-1.el7.x86_64.rpm-bundle.tar 3.卸载mariadb yum -y remove mariadb 查看解压后的包 [rootmysq…...

24年电赛——自动行驶小车(H题)基于 CCS Theia -陀螺仪 JY60 代码移植到 MSPM0G3507(附代码)

前言 只要搞懂 M0 的代码结构和 CCS 的图形化配置方法,代码移植就会变的很简单。因为本次电赛的需要,正好陀螺仪部分代码的移植是我完成的。(末尾附全部代码) 一、JY60 陀螺仪 JY60特点 1.模块集成高精度的陀螺仪、加速度计&…...

数组的增删查查改

1、增 1.Cpp #include <iostream> using namespace std; #include "add.h"int main() {//初始化数组int arr[5];//前四个元素为1,2,3,4for (int i 0; i < 4; i){arr[i] i1;}//数组第5个赋值为100arr[4] 100;for (int…...

设计模式——动态代理

设计模式——动态代理 动态代理的基本概念动态代理的实现步骤总结 在Java中,动态代理是一种强大的机制,它允许在运行时创建一个代理对象,这个代理对象可以代表另一个实际对象,它允许你在不直接操作原始对象的情况下,通…...

的this.$notify的具体使用)

vue(element-ui组件) 的this.$notify的具体使用

getNotify() {this.noClose();let message "";message this.itemData.map((ele) > {const text "任务" ele.title "新增" ele.num "条言论";return this.$createElement("el-tooltip",{props: {content: text,pla…...

c++ - 模拟实现set、map

文章目录 前言一、set模拟实现二、map模拟实现 前言 在C标准库中,std::set 和 std::map都是非常常用的容器,它们提供了基于键值对的存储和快速查找能力。然而,关于它们的底层实现,C标准并没有强制规定具体的数据结构,只…...

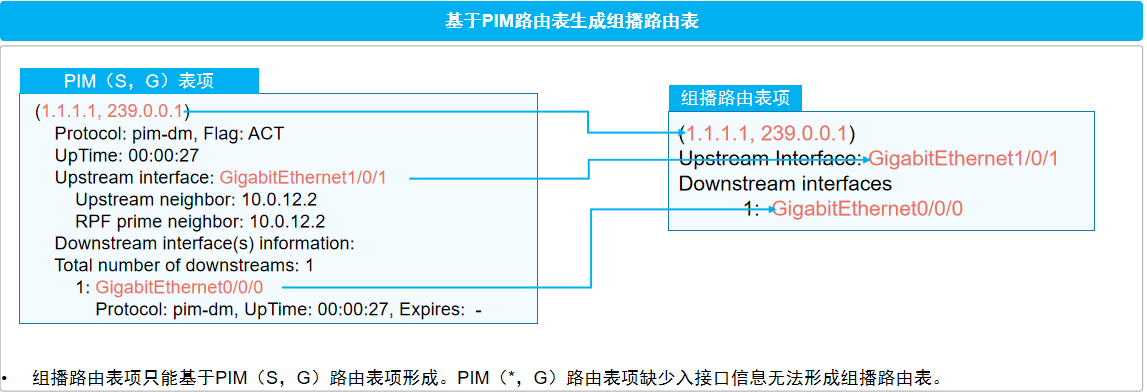

计算机网络-PIM协议基础概念

一、PIM基础概念 组播网络回顾: 组播网络从网络结构上大体可以分为三个部分: 源端网络:将组播源产生的组播数据发送至组播网络。 组播转发网络:形成无环的组播转发路径,该转发路径也被称为组播分发树(Multi…...

【网络】每天掌握一个Linux命令 - iftop

在Linux系统中,iftop是网络管理的得力助手,能实时监控网络流量、连接情况等,帮助排查网络异常。接下来从多方面详细介绍它。 目录 【网络】每天掌握一个Linux命令 - iftop工具概述安装方式核心功能基础用法进阶操作实战案例面试题场景生产场景…...

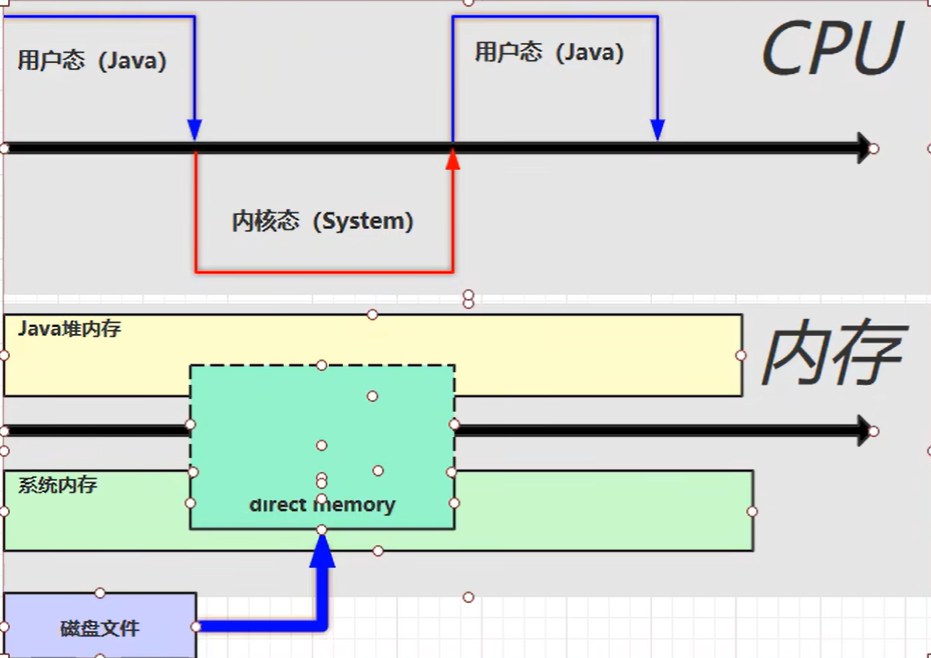

【JVM】- 内存结构

引言 JVM:Java Virtual Machine 定义:Java虚拟机,Java二进制字节码的运行环境好处: 一次编写,到处运行自动内存管理,垃圾回收的功能数组下标越界检查(会抛异常,不会覆盖到其他代码…...

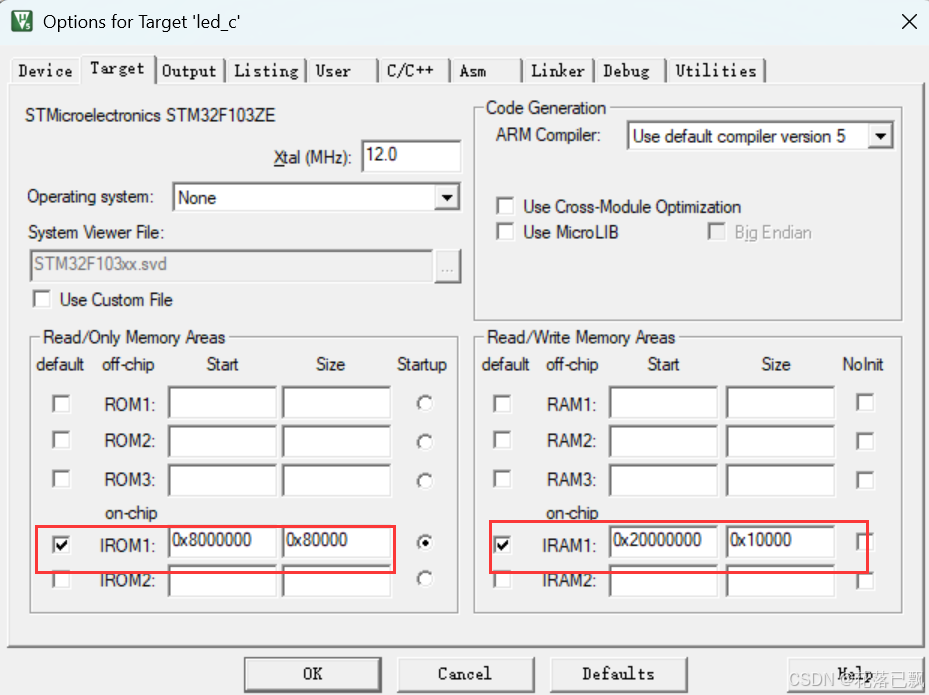

Keil 中设置 STM32 Flash 和 RAM 地址详解

文章目录 Keil 中设置 STM32 Flash 和 RAM 地址详解一、Flash 和 RAM 配置界面(Target 选项卡)1. IROM1(用于配置 Flash)2. IRAM1(用于配置 RAM)二、链接器设置界面(Linker 选项卡)1. 勾选“Use Memory Layout from Target Dialog”2. 查看链接器参数(如果没有勾选上面…...

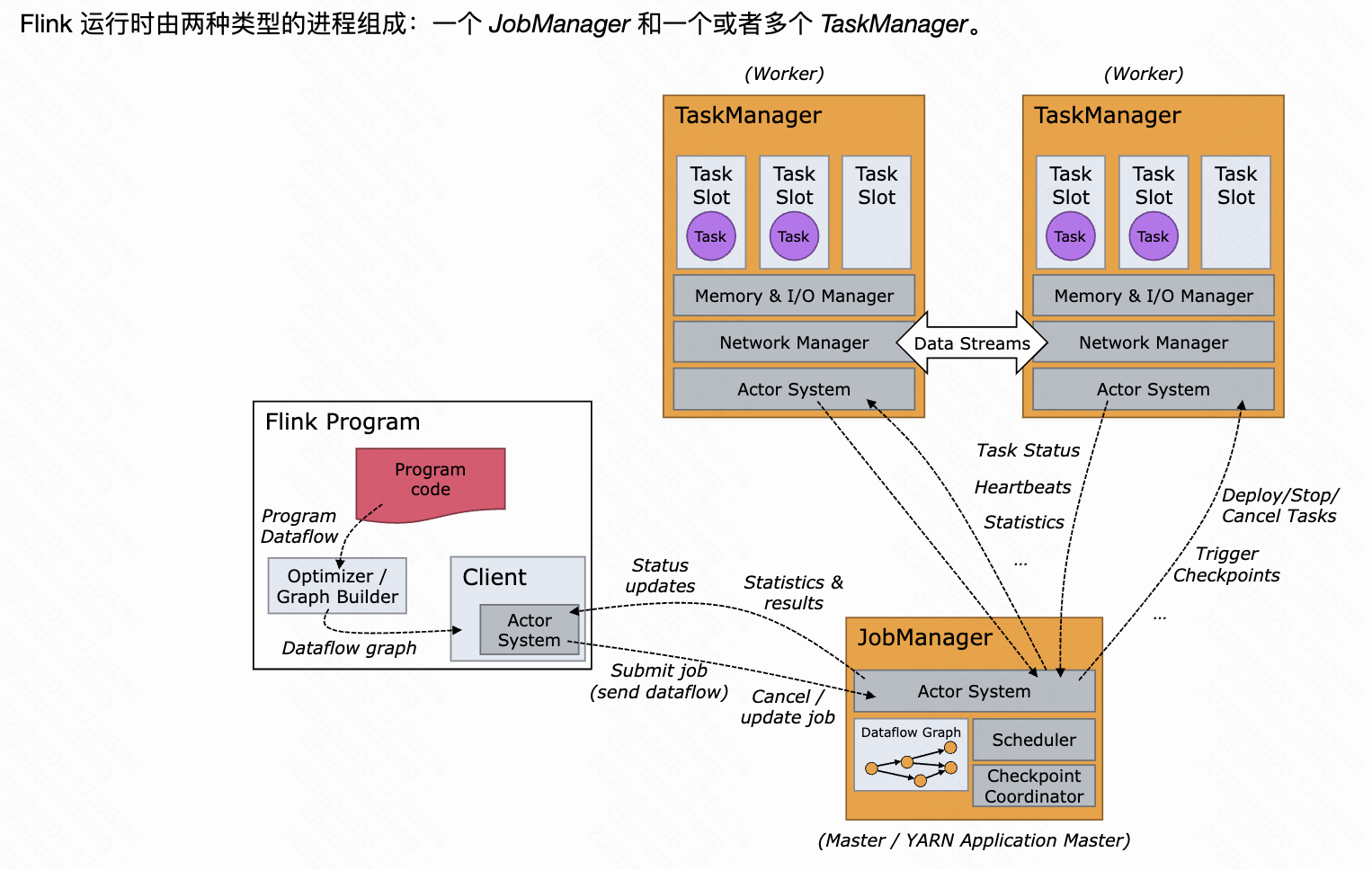

《基于Apache Flink的流处理》笔记

思维导图 1-3 章 4-7章 8-11 章 参考资料 源码: https://github.com/streaming-with-flink 博客 https://flink.apache.org/bloghttps://www.ververica.com/blog 聚会及会议 https://flink-forward.orghttps://www.meetup.com/topics/apache-flink https://n…...

【学习笔记】深入理解Java虚拟机学习笔记——第4章 虚拟机性能监控,故障处理工具

第2章 虚拟机性能监控,故障处理工具 4.1 概述 略 4.2 基础故障处理工具 4.2.1 jps:虚拟机进程状况工具 命令:jps [options] [hostid] 功能:本地虚拟机进程显示进程ID(与ps相同),可同时显示主类&#x…...

QT3D学习笔记——圆台、圆锥

类名作用Qt3DWindow3D渲染窗口容器QEntity场景中的实体(对象或容器)QCamera控制观察视角QPointLight点光源QConeMesh圆锥几何网格QTransform控制实体的位置/旋转/缩放QPhongMaterialPhong光照材质(定义颜色、反光等)QFirstPersonC…...

)

C++课设:简易日历程序(支持传统节假日 + 二十四节气 + 个人纪念日管理)

名人说:路漫漫其修远兮,吾将上下而求索。—— 屈原《离骚》 创作者:Code_流苏(CSDN)(一个喜欢古诗词和编程的Coder😊) 专栏介绍:《编程项目实战》 目录 一、为什么要开发一个日历程序?1. 深入理解时间算法2. 练习面向对象设计3. 学习数据结构应用二、核心算法深度解析…...

PostgreSQL——环境搭建

一、Linux # 安装 PostgreSQL 15 仓库 sudo dnf install -y https://download.postgresql.org/pub/repos/yum/reporpms/EL-$(rpm -E %{rhel})-x86_64/pgdg-redhat-repo-latest.noarch.rpm# 安装之前先确认是否已经存在PostgreSQL rpm -qa | grep postgres# 如果存在࿰…...

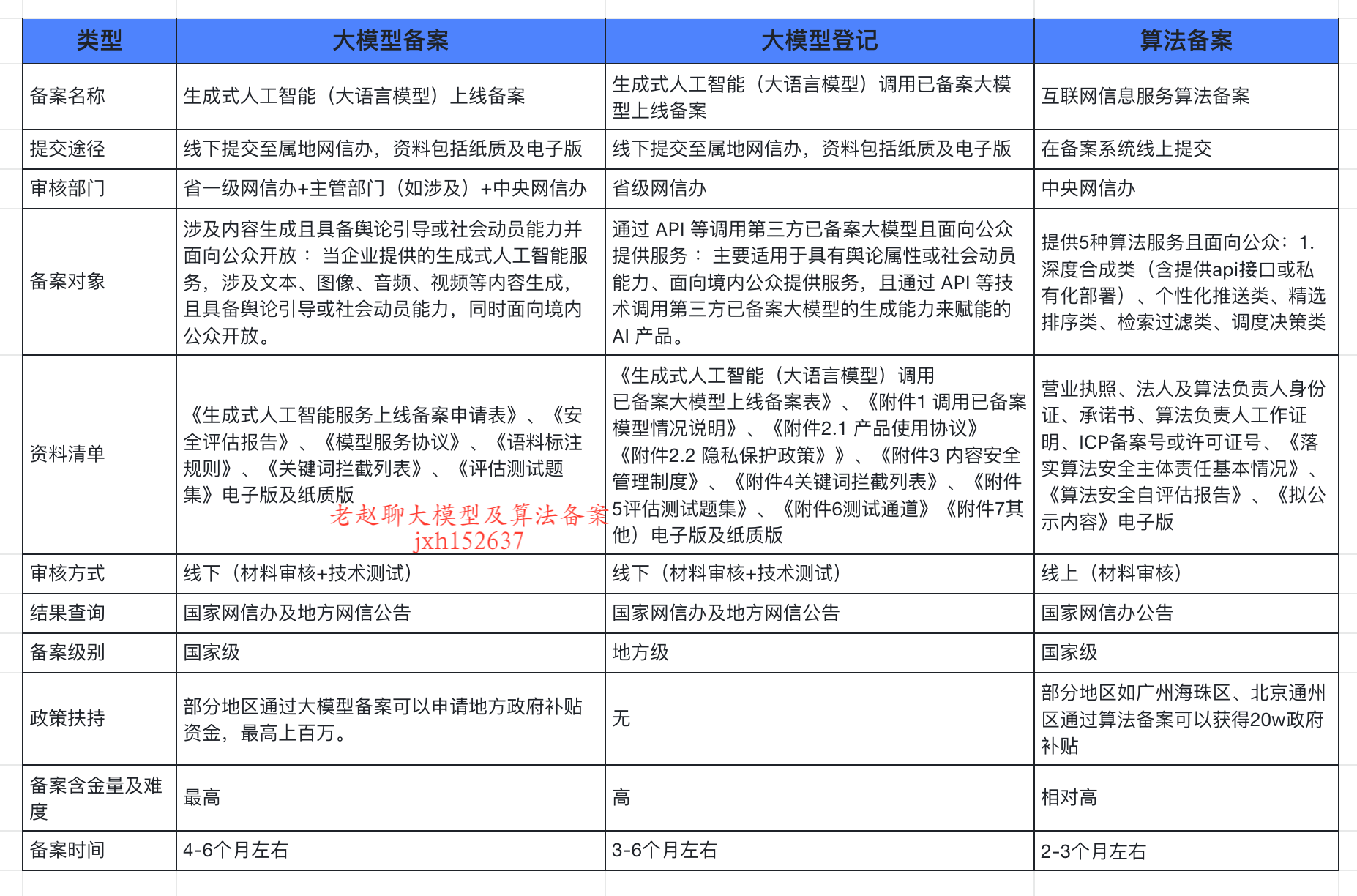

企业大模型服务合规指南:深度解析备案与登记制度

伴随AI技术的爆炸式发展,尤其是大模型(LLM)在各行各业的深度应用和整合,企业利用AI技术提升效率、创新服务的步伐不断加快。无论是像DeepSeek这样的前沿技术提供者,还是积极拥抱AI转型的传统企业,在面向公众…...

五、jmeter脚本参数化

目录 1、脚本参数化 1.1 用户定义的变量 1.1.1 添加及引用方式 1.1.2 测试得出用户定义变量的特点 1.2 用户参数 1.2.1 概念 1.2.2 位置不同效果不同 1.2.3、用户参数的勾选框 - 每次迭代更新一次 总结用户定义的变量、用户参数 1.3 csv数据文件参数化 1、脚本参数化 …...