IIC 随机写+多次写 可以控制写几次

```verilog

module icc_tx#(parameter SIZE = 2 , //用来控制写多少次 比如地址是0000 一个地址只能存放8bit数据 超出指针就会到下一个地址0001parameter CLK_DIV= 50_000_000 ,parameter SPEED = 100_000 ,parameter LED = 50

)( input wire clk ,//系统层input wire rst_n ,inout wire sda ,//物理侧output wire scl ,input wire valid ,//用户侧(写使能)input wire [15:0] addr ,input wire [8*SIZE-1:0] data ,output wire led ,output wire a //ASK状态 1的时候就是该状态否则不是该状态

);

reg scl_r ;

reg sda_o ;

reg sda_i ;

reg [5:0] state ;

reg [((SIZE+3)*8-1):0] data_r ;//SIZE+1 因为还有带上地址加写命令0 不减一是为了产生空白的位不然移位会多移一位

reg [9:0] cunt_0 ;//开始位的计数器 记到500 start

reg [9:0] cunt_1 ;//BUSY与ASK的计数器 用来产生时钟 也方便cunt_2也就是cunt_bit计数

reg [9:0] cunt_2 ;//每一bit数据维持的时间 只在BUSY状态下计数

reg [3:0] cunt_3 ;// 每一次应答加一 计数发了多少数据

reg [30:0] cunt_4 ;//计数小灯点亮时间 1s

reg [9:0] cunt_5 ;

parameter CUNT_MAX=CLK_DIV/SPEED ;

parameter ADDR =7'b101_0000 ;//地址

parameter IDEL =6'b000_001 ;

parameter START =6'b000_010 ;

parameter BUSY =6'b000_100 ;

parameter ASK =6'b001_000 ;

parameter ERROR =6'b010_000 ;

parameter STOP =6'b100_000 ;assign scl=scl_r ;

assign a =(state==ASK)?1'b1:1'b0 ;

assign sda=(state==ASK)?1'bz:sda_o;

//assign sda = sda_o;

//错误状态下led一直亮

assign led=(state==ERROR)?1:0 ;//

always @(posedge clk ) beginif(state==ASK&&cunt_1==(CUNT_MAX/4*3))sda_i<=sda;elsesda_i<=sda_i;end

//数据的缓存 加移位

always @(posedge clk ) begin if(state==IDEL&&valid==1)data_r<={ADDR,1'b0,addr,data}; //单次写else if(cunt_1==4&&state==BUSY) ///data_r<=(data_r<<1); //先赋值再移位了elsedata_r<=data_r;

end

//开始位的 start计数器 记到500

always @(posedge clk ) beginif(state==START)cunt_0<=cunt_0+1;elsecunt_0<=0;

end

//cunt_1

always @(posedge clk ) beginif(state==BUSY||state==ASK)beginif(cunt_1==CUNT_MAX-1)cunt_1<=0;elsecunt_1<=cunt_1+1;endelsecunt_1<=0;

end

//cunt_2

always @(posedge clk ) beginif(state==BUSY)beginif(cunt_1==CUNT_MAX-1)cunt_2<=cunt_2+1;else cunt_2<=cunt_2;endelsecunt_2<=0;

end

//cunt_3 计数发送了几个bit数据

always @(posedge clk ) beginif(state==ASK)beginif(cunt_1==66)cunt_3<=cunt_3+1;elsecunt_3<=cunt_3;endelse if(state==BUSY)cunt_3<=cunt_3;elsecunt_3<=0;

end

//cunt_4

always @(posedge clk ) beginif(state==ERROR)cunt_4<=cunt_4+1;elsecunt_4<=0;

end

//结束位计数 cunt_5

always @(posedge clk ) beginif(state==STOP)cunt_5<=cunt_5+1;elsecunt_5<=0;

end

//状态的转移

always @(posedge clk or negedge rst_n) beginif(!rst_n)state<=IDEL;else begincase (state)IDEL :beginif(valid==1)state<=START;elsestate<=state;endSTART:beginif(cunt_0==CUNT_MAX-1)state<=BUSY;elsestate<=state;endBUSY : beginif(cunt_2==10'd7&&cunt_1==CUNT_MAX-1)state<=ASK;elsestate<=state;endASK :beginif(cunt_1==CUNT_MAX-1)beginif(sda_i==0)beginif(cunt_3==(SIZE+3))state<=STOP;elsestate<=BUSY;endelsestate<=ERROR;endelsestate<=state;endERROR :beginif(cunt_4==LED)state<=IDEL;elsestate<=state;endSTOP :beginif(cunt_5==CUNT_MAX-1)state<=IDEL;elsestate<=state;enddefault: state<=state;endcaseend

end

//时钟线scl的描述

always @(posedge clk ) beginif(state == IDEL || state == START)scl_r <= 1'b1;else if(state == BUSY || state == ASK)beginif(cunt_1 >=0 && cunt_1 <= (CUNT_MAX / 2)) scl_r <= 1'b0;else scl_r <= 1'b1;endelse if(state == STOP)beginscl_r <= 1'b1;endelse scl_r <= 1'b1;

end

//数据线sda的描述

always @(posedge clk ) begincase (state)IDEL : sda_o<=1'b1;START: beginif(cunt_0<CUNT_MAX/2) //也可以起始位状态直接置低置低时间就是cunt_0==250 sda_o<=1;elsesda_o<=0;endBUSY :beginif(cunt_1==1) ///一定要等于0//*************sda_o<=data_r[((SIZE+3)*8-1)];elsesda_o<=sda_o;endASK :beginif(cunt_1==CUNT_MAX-1)sda_o<=1'b0; //给0才可以 因为busy中的保持导致给1会在结束位sda也是一个脉冲1elsesda_o<=1'bz;endERROR:sda_o<=1'b1;STOP :beginif(cunt_5<CUNT_MAX/2)sda_o<=1'b0;elsesda_o<=1'b1;enddefault: sda_o<=1'b1;endcase

end

endmodule

仿真

`timescale 1ns / 1psmodule tb_icc_tx();

reg clk ;///

reg rst_n;///

wire sda ;

wire scl ;

reg valid;///

reg [15:0] data ;///

wire led ;

wire a ;

reg [15:0] addr ;

initial beginclk =1;rst_n<=0;valid<=0;data <=0;#100rst_n<=1;#100valid<=1;data <=16'b1111_0000_0000_1111; addr <=16'b1111_0000_0000_0000;#20valid<=0;data <=0;

endassign sda= (a==1)?1'b0:1'bz;//从机发的

always #10 clk=~clk;

icc_tx#(/*parameter */. SIZE (2 ),/*parameter */. CLK_DIV(50_000_000 ),/*parameter */. SPEED (100_000 ),/*parameter */. LED (50 )

)u_icc_tx( /*input wire */ .clk (clk ),//系统层/*input wire */ .rst_n(rst_n),/*inout wire */ .sda (sda ),//物理侧/*output wire */ .scl (scl ),/*input wire */ .valid(valid),//用户侧/*input wire [8*SIZE-1:0] */ .data (data ),/*output wire */ .led (led ),/*input wire [15:0] */ .addr (addr ) ,/*output wire */ .a (a ) //ASK状态 1的时候就是该状态否则不是该状态

);

endmodule

相关文章:

IIC 随机写+多次写 可以控制写几次

verilog module icc_tx#(parameter SIZE 2 , //用来控制写多少次 比如地址是0000 一个地址只能存放8bit数据 超出指针就会到下一个地址0001parameter CLK_DIV 50_000_000 ,parameter SPEED 100_000 ,parameter LED 50 )( input wire c…...

controller中的参数注解@Param @RequestParam和@RequestBody的不同

现在controller中有个方法:(LoginUserRequest是一个用户类对象) PostMapping("/test/phone")public Result validPhone(LoginUserRequest loginUserRequest) {return Result.success(loginUserRequest);}现在讨论Param("login…...

手搓人工智能-最优化算法(1)最速梯度下降法,及推导过程

“Men pass away, but their deeds abide.” 人终有一死,但是他们的业绩将永存。 ——奥古斯坦-路易柯西 目录 前言 简单函数求极值 复杂函数梯度法求极值 泰勒展开 梯度,Nabla算子 Cauchy-Schwarz不等式 梯度下降算法 算法流程 梯度下降法…...

多目标优化算法——多目标粒子群优化算法(MOPSO)

Handling Multiple Objectives With Particle Swarm Optimization(多目标粒子群优化算法) 一、摘要: 本文提出了一种将帕累托优势引入粒子群优化算法的方法,使该算法能够处理具有多个目标函数的问题。与目前其他将粒子群算法扩展…...

Swift——自动引用计数ARC

ARC ARC是swift使用的一种管理应用程序内存的机制,对于C语言我们知道,当我们申请一块空间,通常需要手动释放,不然会造成空间浪费,而有了ARC机制,你无需考虑内存的管理,因为ARC会在类的实例不再…...

)

【Quarkus】基于CDI和拦截器实现AOP功能(进阶版)

Quarkus 基于CDI和拦截器实现AOP功能(进阶版) 拦截器的属性成员拦截器的重复使用基于属性成员和重复使用的拦截器的发消息案例 本节来了解一下拦截器高级特性(拦截器的重复使用和属性成员),官网说明:https:…...

【踩坑日记】【教程】如何在ubuntu服务器上配置公钥登录以及bug解决

前言 在日常开发和运维中,为了提高服务器登录的安全性,我们通常会选择使用 SSH 密钥认证 来替代传统的密码登录。然而,在配置 SSH 公钥登录的过程中,可能会遇到各种坑和 Bug。本文将从零开始,手把手教你如何在 Ubuntu…...

insmod一个ko提供基础函数供后insmod的ko使用的方法

一、背景 在内核模块开发时,多个不同的内核模块,有时候可能需要都共用一些公共的函数,比如申请一些平台性的公共资源。但是,这些公共的函数又不方便去加入到内核镜像里,这时候就需要把这些各个内核模块需要用到的一些…...

七、传统循环神经网络(RNN)

传统循环神经网络 RNN 前言一、RNN 是什么?1.1 RNN 的结构1.2 结构举例 二、RNN 模型的分类2.1 按照 输入跟输出 的结构分类2.2 按照 内部结构 分类 三、传统 RNN 模型3.1 RNN内部结构图3.2 内部计算公式3.3 其中 tanh 激活函数的作用3.4 传统RNN优缺点 四、代码演示…...

LeetCode:19.删除链表倒数第N个节点

跟着carl学算法,本系列博客仅做个人记录,建议大家都去看carl本人的博客,写的真的很好的! 代码随想录 LeetCode:19.删除链表倒数第N个节点 给你一个链表,删除链表的倒数第 n 个结点,并且返回链表…...

【RISC-V CPU debug 专栏 2 -- Debug Module (DM), non-ISA】

文章目录 调试模块(DM)功能必须支持的功能可选支持的功能兼容性要求规模限制Debug Module Interface (DMI)总线类型地址与操作地址空间控制机制Debug Module Interface Signals请求信号响应信号信号流程Reset Control复位控制方法全局复位 (`ndmreset`)Hart 复位 (`hartreset…...

单片机学习笔记 11. 外部中断

更多单片机学习笔记:单片机学习笔记 1. 点亮一个LED灯单片机学习笔记 2. LED灯闪烁单片机学习笔记 3. LED灯流水灯单片机学习笔记 4. 蜂鸣器滴~滴~滴~单片机学习笔记 5. 数码管静态显示单片机学习笔记 6. 数码管动态显示单片机学习笔记 7. 独立键盘单片机学习笔记 8…...

基于stm32的智能教室管理系统/智能家居系统

基于stm32的智能教室管理系统/智能家居系统 持续更新,欢迎关注!!! ** 基于stm32的智能教室管理系统/智能家居系统 ** 目前,物联网已广泛应用在我们的生活中。智慧校园是将校园中的生活、学习、工作等相关的资源联系在一起,实现管理的智能化…...

基于 Qt 和 GStreamer 的环境中构建播放器

一、功能与需求分析 功能描述 播放本地视频文件(如 MP4、MKV)。 支持基本控制功能(播放、暂停、停止、跳转)。 提供音量调节功能。 在 Windows 环境下使用 Visual Studio 2022 编译。 技术选型 Qt:用于构建用户界面。 GStreamer:负责视频解码和播放。 Visual Studio 202…...

windows docker 入门

这个教程将指导你如何安装Docker、运行第一个容器以及理解一些基本概念。 第一步:安装Docker Desktop for Windows 系统要求: Windows 10 64位版本(专业版、企业版或教育版)。启用Hyper-V和Windows Subsystem for Linux (WSL 2)。…...

baomidou Mabatis plus引入异常

1 主要异常信息 Error creating bean with name dataSource 但是有个重要提示 dynamic-datasource Please check the setting of primary 解决方法: <dependency><groupId>com.baomidou</groupId><artifactId>dynamic-datasource-spring…...

深度学习中的正则化模型是什么意思?

一、定义 在深度学习中,正则化是一种用于防止过拟合的技术。过拟合是指模型在训练数据上表现非常好,但在新的、未见过的数据(测试数据)上表现很差的情况。正则化模型就是通过在损失函数中添加额外的项来约束模型的复杂度…...

修改IDEA配置导致Spring Boot项目读取application.properties中文乱码问题

之前很多配置都是放在nacos里面,然后这次同事有个配置写在application.properties中,这个配置含有中文,启动之后发现拿到的中文值会乱码,然后就帮忙看了一下问题。 排查问题 经过不停的百度、排查发现,spring读取app…...

Flink 热存储维表 使用 Guava Cache 减轻访问压力

目录 背景 Guava Cache 简介 实现方案 1. 项目依赖 2. Guava Cache 集成到 Flink (1) 定义 Cache (2) 使用 Cache 优化维表查询 3. 应用运行效果 (1) 维表查询逻辑优化 (2) 减少存储压力 Guava Cache 配置优化 总结 背景 在实时计算场景中,Flink 应用中…...

深入探索SenseVoiceSmall:高效多语言语音识别与处理模型

引言 随着人工智能技术的飞速发展,语音识别技术已经广泛应用于智能助手、客户服务、智能家居等多个领域。然而,现有的语音识别模型往往存在资源消耗大、多语言支持不足等问题。今天,我们要介绍的是来自ModelScope平台的SenseVoiceSmall模型&…...

java_网络服务相关_gateway_nacos_feign区别联系

1. spring-cloud-starter-gateway 作用:作为微服务架构的网关,统一入口,处理所有外部请求。 核心能力: 路由转发(基于路径、服务名等)过滤器(鉴权、限流、日志、Header 处理)支持负…...

)

Java 语言特性(面试系列1)

一、面向对象编程 1. 封装(Encapsulation) 定义:将数据(属性)和操作数据的方法绑定在一起,通过访问控制符(private、protected、public)隐藏内部实现细节。示例: public …...

DockerHub与私有镜像仓库在容器化中的应用与管理

哈喽,大家好,我是左手python! Docker Hub的应用与管理 Docker Hub的基本概念与使用方法 Docker Hub是Docker官方提供的一个公共镜像仓库,用户可以在其中找到各种操作系统、软件和应用的镜像。开发者可以通过Docker Hub轻松获取所…...

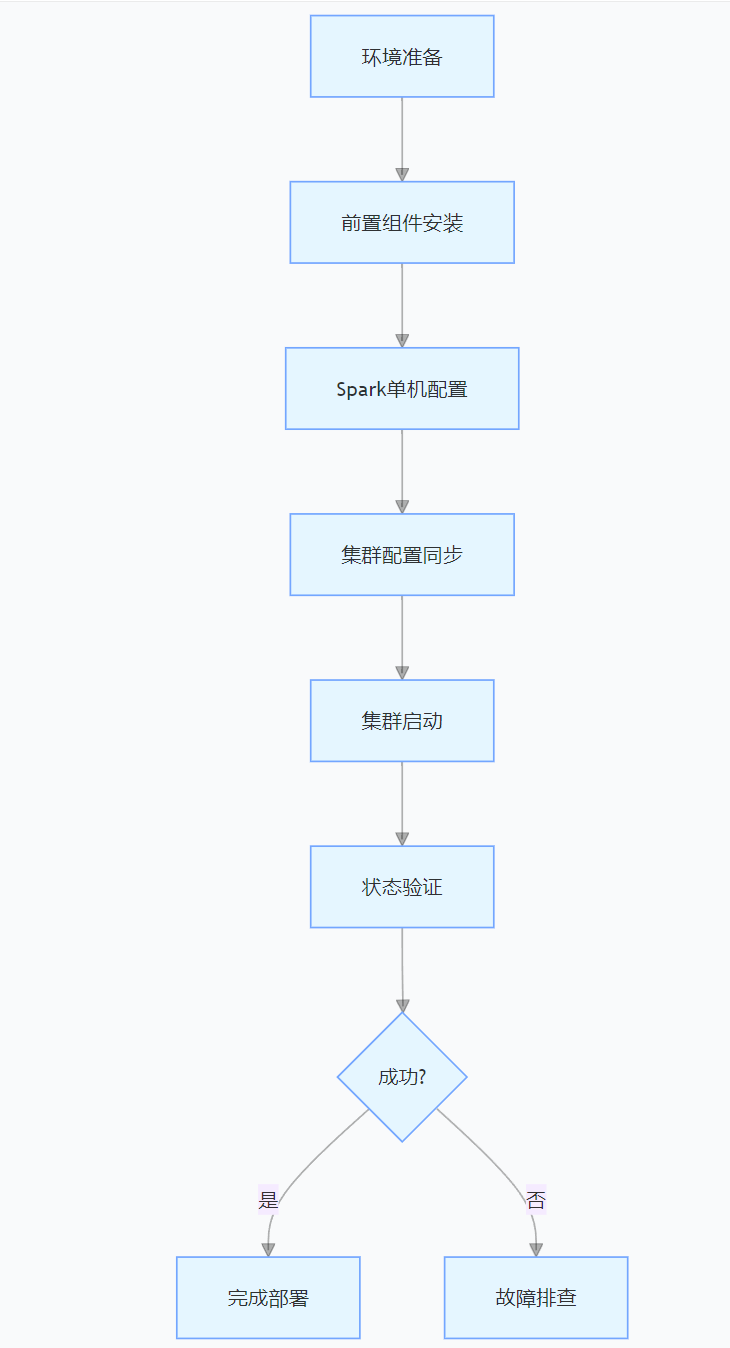

CentOS下的分布式内存计算Spark环境部署

一、Spark 核心架构与应用场景 1.1 分布式计算引擎的核心优势 Spark 是基于内存的分布式计算框架,相比 MapReduce 具有以下核心优势: 内存计算:数据可常驻内存,迭代计算性能提升 10-100 倍(文档段落:3-79…...

基于数字孪生的水厂可视化平台建设:架构与实践

分享大纲: 1、数字孪生水厂可视化平台建设背景 2、数字孪生水厂可视化平台建设架构 3、数字孪生水厂可视化平台建设成效 近几年,数字孪生水厂的建设开展的如火如荼。作为提升水厂管理效率、优化资源的调度手段,基于数字孪生的水厂可视化平台的…...

c#开发AI模型对话

AI模型 前面已经介绍了一般AI模型本地部署,直接调用现成的模型数据。这里主要讲述讲接口集成到我们自己的程序中使用方式。 微软提供了ML.NET来开发和使用AI模型,但是目前国内可能使用不多,至少实践例子很少看见。开发训练模型就不介绍了&am…...

安装docker)

Linux离线(zip方式)安装docker

目录 基础信息操作系统信息docker信息 安装实例安装步骤示例 遇到的问题问题1:修改默认工作路径启动失败问题2 找不到对应组 基础信息 操作系统信息 OS版本:CentOS 7 64位 内核版本:3.10.0 相关命令: uname -rcat /etc/os-rele…...

学习一下用鸿蒙DevEco Studio HarmonyOS5实现百度地图

在鸿蒙(HarmonyOS5)中集成百度地图,可以通过以下步骤和技术方案实现。结合鸿蒙的分布式能力和百度地图的API,可以构建跨设备的定位、导航和地图展示功能。 1. 鸿蒙环境准备 开发工具:下载安装 De…...

使用SSE解决获取状态不一致问题

使用SSE解决获取状态不一致问题 1. 问题描述2. SSE介绍2.1 SSE 的工作原理2.2 SSE 的事件格式规范2.3 SSE与其他技术对比2.4 SSE 的优缺点 3. 实战代码 1. 问题描述 目前做的一个功能是上传多个文件,这个上传文件是整体功能的一部分,文件在上传的过程中…...

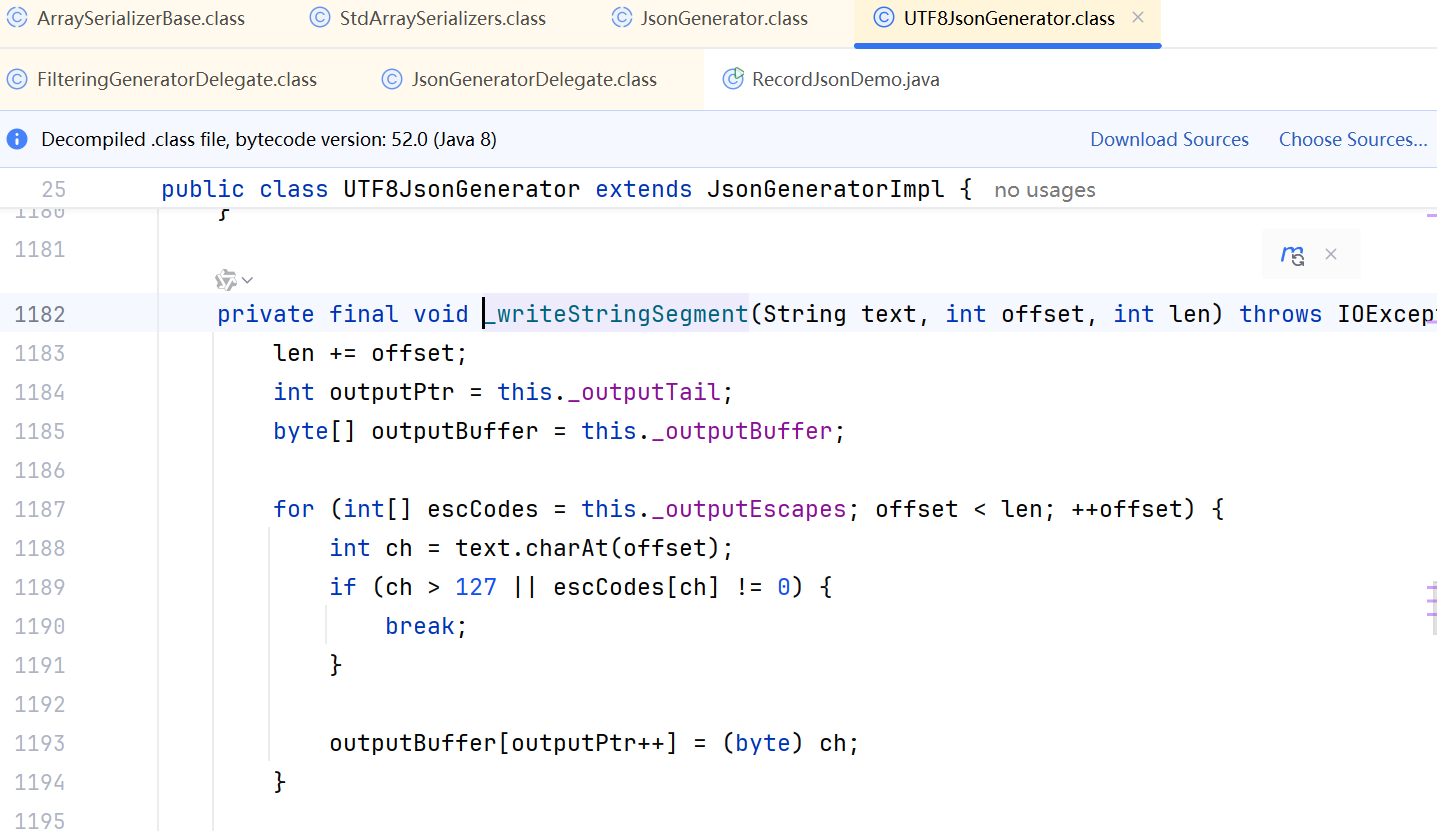

JDK 17 序列化是怎么回事

如何序列化?其实很简单,就是根据每个类型,用工厂类调用。逐个完成。 没什么漂亮的代码,只有有效、稳定的代码。 代码中调用toJson toJson 代码 mapper.writeValueAsString ObjectMapper DefaultSerializerProvider 一堆实…...