I.MX6U 裸机开发20. DDR3 内存知识

I.MX6U 裸机开发20. DDR3 内存知识

- 一、DDR3内存简介

- 1. DDR发展历程

- SRAM

- SDRAM

- DDR1

- DDR2

- DDR3

- DDR4

- DDR5

- 2. 开发板资源

- 3. DDR3的时间参数

- 1. 传输速率

- 2. tRCD

- 3. CL 参数

- 作用

- 取值范围

- 工作原理

- 4. tRC参数

- 原理

- 单位与取值

- 5. tRAS

- 重要性及作用

- 二、I.MX6U MMDC 控制器

- 1. MMDC简介

- (1)主要组成部分

- (2)支持的存储类型及特性

- (3)时钟频率与数据速率

- (4)校准程序

- (5)其他特性

- 2. 时钟源

- 3. 开发板原理图

- 三、DDR3初始化与测试

- 1. ddr_stres_tester简介

- xlsx 文件

- 2. 下载配置信息

- (1)直接进行超频测试

- (2)校准

- (3)超频测试

- 四、DCD数据

- 1. 打开 《【正点原子】I.MX6U嵌入式Linux驱动开发指南V1.81.pdf》

一、DDR3内存简介

1. DDR发展历程

SRAM

SRAM(Static Random - Access Memory)即静态随机存取存储器,是一种半导体存储器。

SRAM 存储单元通常由 6 个晶体管组成(CMOS 工艺)。这种结构可以在不进行刷新操作的情况下保持数据的存储状态,容量小、价格高、速度快。

在传统的51单片机、STM32中,会有芯片内部RAM,即SRAM。在高级一点单片机,可以使用外扩RAM。

以 IS62WV51216 SRAM为例,这是一个1M Byte存储器,从数据手册可以看到其功能框图:

其中:

- A0-A18:19根地址线

- I/O0-7, I/O8-15:数据低字节、高字节

- CS:片选

- OE:读使能

- WE:写使能

- UB:低电平:访问高字节

- LB:低平平:访问低字节

SDRAM

SDRAM(Synchronous Dynamic Random Access Memory)是一种同步动态随机存取存储器,SDRAM需要时钟线,常见的频率有100MHz、133MHz、166MHz、200MHz,相对于SRAM价格低、速率低。

以W9825G6KH为例,其功能框图:

引脚介绍:

-

CLK:时钟线

-

CKE:时钟使能信号,SRAM没有CKE。

-

CS:片选

-

RAS:行选通信号

-

CAS:列选通信号

-

WE:写使能信号

-

A10:地址线&自动预充电

-

A0~A12:地址线

-

BS0:BANK0选择信号线

-

BS1:BANK1选择信号线

-

D0~D15:数据线

其容量:

行 2 13 ∗ 列 2 9 ∗ 4 个 B a n k ∗ 2 字节位宽 = 32 M B y t e 行 2^{13} * 列 2{^9} * 4个Bank * 2字节位宽 = 32MByte 行213∗列29∗4个Bank∗2字节位宽=32MByte

DDR1

DDR1由三星公司于1996年提出,1998年12月,联合电子设备工程委员会(JEDEC)正式确定了DDR内存与DDR内存部件的规范。它是在SDRAM内存基础上发展而来,其诞生是为了对抗Intel提倡的Rambus标准.

DDR1沿用了SDRAM的生产体系,但采用了更加先进的双倍数据速度技术,即DDR1内存在每个时钟周期预取2位数据,这样DDR1在每个时钟周期的上升沿和下降沿都进行数据传输,使得数据传输速率是传统SDRAM的两倍。

DDR1初始频率为200MHz,后来发展到DDR-266、DDR-333和主流的DDR-400,数据传输速度相比SDRAM有了显著提升 。从外形上看,DDR1内存条有184个引脚,金手指中有一个缺口,而SDRAM内存条是168个引脚,并且有两个缺口。

DDR1的容量范围,最初只有单通道,容量从128MB增加到1GB。

DDR2

DDR2是由JEDEC进行开发的一种新内存技术标准,于2003年正式发布。DDR2内存均采用FBGA封装形式,拥有240个引脚,电气性能与散热性更好,有利于内存的稳定工作与未来频率的发展。与DDR1相比,DDR2的预读取能力是DDR1的两倍,在每个时钟脉冲周期内都能以四倍外部总线的速度读/写数据,并且能够以内部控制总线四倍的速度运行。

DDR2采用1.8V电压,相比DDR1的2.5V降低了功耗。

DDR2容量从256MB起步,最大支持到4GB。

DDR3

DDR3是一种使用SSTL15接口的计算机内存规格,于2007年发布。与DDR2相比,它拥有更高的运行效能与更低的电压,同时更省电、传输效率更快。

DDR3突发长度增加了4bit突发突变模式,能够提供更灵活的突发传输控制;寻址时序的CL周期有所提高,并提供了0CL-1和CL-2三种AL选项,同时还新增加了写入延迟这一时序参数;专门准备了一个引脚实现重置功能,能够让DDR3内存停止所有操作,并切换至最少量活动状态,从而节约电力;还新增了ZQ引脚,能够对导通电阻和ODT电阻进行重新校准.

DDR3核心电压降低到1.5V,预取从4-bit变成了8-bit,提供了更高的带宽,频率从800MHz起步,一般能买到的最高频率为2400MHz,常见的容量是512MB到8GB,也有单条16GB的DDR3内存,但较为稀少。

正点原子的开发板上使用的是 NT5CC256M16ER-EK,其接口结构与其它厂家相同规格芯片 相同,下图是MT41K256M16结构框图:

其引脚说明:

- A0~A14:地址线,行线15根, A0 ~ A9 10列。

- BA[2:0]:BANK选择线,共8个BANK。

容量 : 2 15 ∗ 2 10 ∗ 8 ∗ 2 = 512 M B y t e 2^{15} * 2^{10} * 8 * 2 = 512MByte 215∗210∗8∗2=512MByte

DDR4

2011年1月4日三星电子发布了第一款DDR4标准的内存条,首批样品采用30nm级工艺制造而成,2014年开始广泛应用。

DDR4采用16bit的预取机制,在同样内核频率下理论速度是DDR3的两倍;采用更可靠的传输规范,进一步提升数据的可靠性;工作电压降为1.2V。

DDR4 频率范围从DDR4-1600到DDR4-3200,理论上每根DIMM模块能达到512GiB的容量,而DDR3每个DIMM模块的理论最大容量仅128GiB。

DDR5

2020年开始投入市场,带来了全新的架构,改进的功能使实际带宽相比DDR4有了显著提高,即使在3200MT/s和4800MT/s速度开始,与DDR4-3200相比,实际带宽将高出87%。引入了on-die ECC,提高了数据的可靠性和准确性。

DDR5工作电压进一步降低至1.1V,并支持更高的频率和更大的单条内存容量,初始频率为4800MHz,单条内存可以达到128GB,使用2DPC的主板时,总内存容量可达512GB。

2. 开发板资源

在开发板上有 DDR3 的RAM芯片,正点原子提供的核心板有256M和512M两款内存规格的开发板,对于ARM A系列芯片来说,要运行的程序是要加截到内存中运行。

本系列文章基于正点原子 I.MX6U-MINI开发板,使用的内存是 : NT5CC256M16ER-EK。

3. DDR3的时间参数

1. 传输速率

-

基本概念

- DDR3在一个时钟周期的上升沿和下降沿都可以传输数据,这就是所谓的“双倍数据速率”。它的传输速率通常用每秒传输的数据量来衡量,单位有MT/s(兆次传输每秒)或Mbps(兆位每秒)。1MT/s = 8Mbps,因为1字节(Byte)等于8位(bit)。

-

速率标准

- DDR3内存的初始标准传输速率从800MT/s开始,对应的带宽为6.4GB/s(800MT/s×64bit/8)。这里的64bit是DDR3内存的数据总线宽度。

- 之后还有更高的标准,如1066MT/s、1333MT/s、1600MT/s等。以1600MT/s为例,其带宽为12.8GB/s(1600MT/s×64bit/8)。这些不同的传输速率可以满足不同性能需求的计算机系统。

- 更高端的DDR3甚至可以达到2133MT/s,带宽可达17GB/s左右,能够为高性能计算(如游戏电脑、工作站等)提供更快速的数据传输,让CPU能更快地读取和写入内存中的数据,从而提升系统的整体性能。

本系列文章使用的开发板的内存支持速率如下图所示:

不同的速率的时序有所不同。

2. tRCD

tRCD(RAS to CAS Delay)主要用于描述内存工作过程中的延迟时间。

- 工作原理背景

- 在计算机内存系统中,数据的读取和写入是一个复杂的过程。当内存控制器(通常位于CPU或芯片组中)发出读取或写入命令后,内存芯片需要按照一定的顺序和时间间隔来执行这些操作。tRCD主要涉及从行地址选通(RAS - Row Address Strobe)到列地址选通(CAS - Column Address Strobe)之间的延迟。

- 以读取数据为例,首先内存控制器要激活某一行(通过RAS信号),然后才能指定列地址来读取具体的数据单元。tRCD就是这个行激活和列选择之间的延迟时间。

- 具体含义

- tRCD以时钟周期(Clock Cycle)为单位进行衡量。例如,如果内存的时钟频率是100MHz,一个时钟周期就是10ns(纳秒)。假设tRCD的值为3个时钟周期,那么在这种情况下,tRCD的实际延迟时间就是30ns。

- 这个延迟时间对于内存性能有重要影响。较小的tRCD值意味着内存能够更快地从行激活状态转换到列选择状态,从而可以更快地读取或写入数据。相反,较大的tRCD值会导致内存操作的延迟增加,降低数据访问速度。

3. CL 参数

CL是CAS Latency的缩写,即列选通潜伏期,具体来说,CL是指从内存控制器发出读命令到内存开始输出第一个数据之间的延迟时间,以时钟周期为单位。

作用

- 衡量内存性能:CL值越小,内存响应速度越快,数据传输延迟越低,内存性能也就越高。比如在相同内存主频下,CL值为5的DDR3内存性能要优于CL值为7的内存。

- 影响系统整体性能:内存的CL参数与CPU的配合对系统性能有重要影响。如果CL值过大,会导致CPU等待数据从内存中传输的时间过长,从而降低CPU的执行效率,影响整个系统的运行速度。

取值范围

DDR3内存的CL值一般在5-11之间,常见的有7、8、9、10、11等。如DDR3-1066的CL值通常为7,DDR3-1333的CL值一般为8,DDR3-1600的CL值常为9。

工作原理

在内存读写操作中,当内存控制器发出行地址激活命令后,需要经过一段时间的延迟,这段延迟包含行地址到列地址的延迟(TRCD)和列选通潜伏期(CL)等。CL是其中关键的一部分,它决定了从列地址选通到数据开始输出的时间间隔。以DDR3-1600 CL=9为例,在内存接收到读命令后,经过9个时钟周期,才会将第一个数据输出到数据总线上.

4. tRC参数

DDR3的tRC参数是指同一bank内两个ACTIVE命令之间的最小延迟周期,也可以是ACTIVE命令到REFRESH命令之间的周期。tRC参数用于限制对同一bank的访问频率,确保内存操作的稳定性和数据的正确传输。它规定了在同一bank内,两次激活操作之间必须间隔的最短时间。

原理

- DDR3内存的存储单元是以bank为单位进行组织的,每个bank包含多个行和列。当对内存进行读写操作时,需要先激活相应的bank和行,然后才能进行列地址的选择和数据传输.

- 如果在tRC时间内对同一bank再次发出ACTIVE命令,可能会导致数据冲突、信号干扰等问题,从而影响内存的正常工作。因此,tRC参数的设置是为了给内存足够的时间来完成当前操作,并为下一次操作做好准备。

单位与取值

- tRC的单位通常是纳秒(ns)或时钟周期数。在DDR3的数据手册中,一般会给出tRC的具体数值,例如NT5CC256M16EP-EK的tRC值为47.91ns.

- 不同频率和型号的DDR3内存,其tRC参数的取值可能会有所不同。通常情况下,tRC的取值范围在几十到上百纳秒之间,具体数值取决于内存的规格和性能等级 。

5. tRAS

DDR3的tRAS(Row Active Time to Precharge Delay)是指从ACTIVE命令到PRECHARGE命令之间的最小时间间隔,即行激活时间到预充电延迟 。它表示在DDR3内存中,从行地址被激活(ACTIVE命令发出)开始,到可以对该行发出预充电命令(PRECHARGE命令)之间所必须经过的最短时间。

- 当内存控制器发出ACTIVE命令后,相应的行被激活,数据的读取或写入操作会在该行上进行。在操作完成后,需要经过tRAS时间才能对该行进行预充电操作,以便为下一次的访问做好准备。如果在tRAS时间未结束时就对该行进行预充电,可能会导致数据丢失或损坏,因为此时该行的数据可能还处于不稳定状态。

重要性及作用

- 确保数据完整性:tRAS的存在是为了给内存足够的时间来完成数据的传输和稳定存储。在数据读写操作期间,内存芯片内部的各种电路和存储单元需要一定的时间来处理和保持数据,如果过早地进行预充电操作,可能会干扰数据的稳定存储,从而导致数据错误.

- 影响内存性能:tRAS的值会影响内存的整体性能。一般来说,tRAS时间越短,内存的访问速度就越快,因为可以更快地进入下一次的行激活和数据传输操作。然而,如果tRAS设置得过短,可能会导致数据不稳定,从而引发系统错误或性能下降。相反,如果tRAS设置得过长,虽然可以保证数据的稳定性,但会增加内存的访问延迟,降低内存的带宽利用率.

二、I.MX6U MMDC 控制器

I.MX6U的MMDC控制器是一款多模式DDR控制器,主要负责管理和控制与DDR内存的交互,以实现高效的数据存储和读取操作,满足系统对内存的需求。在《IMX6ULL 参考手册》 P2203,有对其详细介绍。

1. MMDC简介

(1)主要组成部分

- MMDC CORE 内核:内核承担着通过AXI接口与系统进行通信的重要任务,负责生成DDR命令,并对这些命令进行优化处理,同时还管理着读/写数据路径,确保数据能够准确、高效地在系统与内存之间传输。

- MMDC PHY:PHY则专注于时序调整和校准工作。它运用特殊的校准机制,保障数据能够在400MHz的时钟频率下被准确捕获,从而保证了数据传输的稳定性和可靠性。

(2)支持的存储类型及特性

- 支持的存储类型:MMDC支持16位宽的DDR3/DDR3L以及LPDDR2,不支持LPDDR1、MDDR和DDR2等其他类型的内存。

- 存储容量范围:能够支持单片256Mbit~8Gbit容量的DDR内存,其列地址范围为8-12位,行地址范围为11-16位,并且配备2个片选信号,可通过配置CS0、CS1来达到4Gbyte的地址空间.

- 突发访问支持:对于DDR3,最大支持8bit的突发访问;而对于LPDDR2则最大支持4bit的突发访问。

(3)时钟频率与数据速率

- MMDC的最大频率为400MHz,对应的数据速率能够达到800MT/S,为系统提供了高速的数据传输通道,满足了处理器对内存数据快速读写的要求。

(4)校准程序

- MMDC支持各种校准程序,包括自动和手动运行方式,还支持ZQ校准外部DDR设备、校准DDR I/O引脚以及校准DDR驱动能力等,通过这些校准操作,可以确保内存系统的稳定性和性能表现。

(5)其他特性

- 优先级与优化机制:支持实时优先级,并具备不同优先级的重新排序机制,能够对实时、延时敏感和正常优先级的任务进行合理调度。同时,还针对页面碰撞错过、连续读写访问等情况进行了优化,进一步提高了内存访问效率。

- 深度请求队列与预测功能:支持深度读写请求队列,能够更好地管理和调度内存访问请求,并且还支持bank预测以及bank交叉等功能,提升了内存系统的并行处理能力和整体性能。

- 特殊访问优化:在ddr3模式下的非对齐换行访问情况下,也有特殊优化措施,确保数据能够准确、快速地传输,减少因数据对齐问题而导致的性能损失。

2. 时钟源

时钟源我们使用PLL2-PFD2=396MHz,MMDC_CLK_ROOT最大支持 396MHz。

- CBDMR[PERIPH2_CLK2_SEL](bit22,bit21),设置为01,设置PLL_PFD2作为 pre_periph2时钟源;

- CBCDR[PERIPH2_CLK_SEL] (bit26),设置为0,设置PLL2作为 MMDC 时钟源;

- CBCDR[PABRIC_MMDC_PODF] ,(bit5-3),设置为0,1分频。

3. 开发板原理图

三、DDR3初始化与测试

1. ddr_stres_tester简介

ddr_stress_tester_v2.90 是NXP提供的一个DDR压测工具,在本文对应的开源仓库中已经放了这个工具。

使用方法:

xlsx 文件

打开 I.MX6UL_DDR3_Script_Aid_V0.02.xlsx 文件:

复制生成的 ReView.inc 放到软件目录里。

2. 下载配置信息

打开 DDR_Tester.exe,加载初始化脚本 :

开发板需要外置供电,使用 USB_OTG 连接电脑,启动方式拨码开关选择 USB 启动,另外要把SD卡取出。

点击Download,有以下输出:

(1)直接进行超频测试

填写频率 400MHz~600MHz, 输出测试失败。这是因为没在进行校准操作。

(2)校准

校准内容如下:

MMDC registers updated from calibration Write leveling calibrationMMDC_MPWLDECTRL0 ch0 (0x021b080c) = 0x00000000MMDC_MPWLDECTRL1 ch0 (0x021b0810) = 0x001F001FRead DQS Gating calibrationMPDGCTRL0 PHY0 (0x021b083c) = 0x013C013CMPDGCTRL1 PHY0 (0x021b0840) = 0x00000000Read calibrationMPRDDLCTL PHY0 (0x021b0848) = 0x40403236Write calibrationMPWRDLCTL PHY0 (0x021b0850) = 0x4040382ESuccess: DDR calibration completed!!!根据校准值,对 ALIENTEK_512MB.inc 进行修改,没找到的不用改,下面是修改示例:

修改后保存文件,重新打开 DDR_Tester.exe。

(3)超频测试

一般在400MHz基础能超频20%,硬件开发板设计就算正常。

四、DCD数据

1. 打开 《【正点原子】I.MX6U嵌入式Linux驱动开发指南V1.81.pdf》

在P342,如下图所示:

可以看到 CCGR0地址是在 0x020C4068,

打开 imxdownload.h , 可以找到该位置:

DDR相关的初始化,位置是在0X020E04B4:

而这个地址值,与 ALIENTEK_512MB.inc里 这个位置相对应:

直到位置:

所以imxdownload里的 dcd表的值,要与校准后的值相对应 。

相关文章:

I.MX6U 裸机开发20. DDR3 内存知识

I.MX6U 裸机开发20. DDR3 内存知识 一、DDR3内存简介1. DDR发展历程SRAMSDRAMDDR1DDR2DDR3DDR4DDR5 2. 开发板资源3. DDR3的时间参数1. 传输速率2. tRCD3. CL 参数作用取值范围工作原理4. tRC参数原理单位与取值5. tRAS重要性及作用 二、I.MX6U MMDC 控制器1. MMDC简介…...

【R安装】VSCODE安装及R语言环境配置

目录 VSCODE下载及安装VSCODE上配置R语言环境参考 Visual Studio Code(简称“VSCode” )是Microsoft在2015年4月30日Build开发者大会上正式宣布一个运行于 Mac OS X、Windows和 Linux 之上的,针对于编写现代Web和云应用的跨平台源代码编辑器&…...

ES更新问题 Failed to close the XContentBuilder异常

问题描述 使用RestHighLevelClient对文档进行局部更新的时候报错如下: Suppressed: java.lang.IllegalStateException: Failed to close the XContentBuilderat org.elasticsearch.common.xcontent.XContentBuilder.close(XContentBuilder.java:1011)at org.elast…...

svn-git下载

windows: svn 客户端:-------------- TortoiseSVN 安装 下载地址:https://tortoisesvn.net/downloads.html, 页面里有语言包补丁的下载链接。 目前最新版为 1.11.0 下载地址: https://osdn.net/projects/tortoisesvn/storage/1.…...

10个Word自动化办公脚本

在日常工作和学习中,我们常常需要处理Word文档(.docx)。 Python提供了强大的库,如python-docx,使我们能够轻松地进行文档创建、编辑和格式化等操作。本文将分享10个使用Python编写的Word自动化脚本,帮助新…...

)

Paddle Inference部署推理(十八)

十八:Paddle Inference推理 (C)API详解 3. 使用 CPU 进行预测 注意: 在 CPU 型号允许的情况下,进行预测库下载或编译试尽量使用带 AVX 和 MKL 的版本 可以尝试使用 Intel 的 MKLDNN 进行 CPU 预测加速,默…...

Redis开发02:redis.windows-service.conf 默认配置文件解析与注解

文件位置:redis安装目录下的 redis.windows-service.conf ,存放了redis服务的相关配置,下面列举出默认配置的含义: 配置项含义bind 127.0.0.1限制 Redis 只监听本地回环地址,意味着只能从本地连接 Redis。protected-m…...

redis大key和热key

redis中大key、热key 什么是大key大key可能产生的原因大key可能会造成什么影响如何检测大key如何优化删除大key时可能的问题删除大key的策略 热key热key可能导致的问题解决热key的方法 什么是大key 大key通常是指占用内存空间过大或包含大量元素的键值对。 数据量大ÿ…...

)

Dubbo 最基础的 RPC 应用(使用 ZooKeeper)

看国内的一些项目时 Dubbo 这个词经常闪现,一直也不以为然,未作搜索,当然也不知道它是做什么用的。直到最近阅读关于大型网站架构相关的书中反复提到 Dubbo 后,觉得不能再对它视而不见。Google 了一下,它是在阿里巴巴创…...

科技赋能:企业如何通过新技术提升竞争力的策略与实践

引言 在当今瞬息万变的商业环境中,科技的迅猛发展正在重新定义行业的游戏规则。无论是小型企业还是跨国巨头,都感受到数字化转型的迫切需求。过去,企业竞争力更多依赖于成本控制、资源调配或市场覆盖,而如今,新技术的引…...

从0开始深度学习(33)——循环神经网络的简洁实现

本章使用Pytorch的API实现RNN上的语言模型训练 0 导入库 import torch import torch.nn as nn import torch.nn.functional as F from torch.utils.data import Dataset, DataLoader from collections import Counter import re import math from tqdm import tqdm1 准备数据 …...

【FAQ】HarmonyOS SDK 闭源开放能力 — 公共模块

1.问题描述: 文档哪里能找到所有的权限查看该权限是用户级的还是系统级的。 解决方案: 您好,可以看一下下方链接是否可以解决问题: https://developer.huawei.com/consumer/cn/doc/harmonyos-guides-V5/permissions-for-all-V…...

百度 文心一言 vs 阿里 通义千问 哪个好?

背景介绍: 在当前的人工智能领域,随着大模型技术的快速发展,市场上涌现出了众多的大规模语言模型。然而,由于缺乏统一且权威的评估标准,很多关于这些模型能力的文章往往基于主观测试或自行设定的排行榜来评价模型性能…...

内网不出网上线cs

一:本地正向代理目标 如下,本地(10.211.55.2)挂好了基于 reGeorg 的 http 正向代理。代理为: Socks5 10.211.55.2 1080python2 reGeorgSocksProxy.py -l 0.0.0.0 -p 1080 -u http://10.211.55.3:8080/shiro/tunnel.jsp 二:虚拟机配置proxifer 我们是…...

ubuntu22开机自动登陆和开机自动运行google浏览器自动打开网页

一、开机自动登陆 1、打开settings->点击Users 重启系统即可自动登陆桌面 二、开机自动运行google浏览器自动打开网页 1、安装google浏览器 sudo wget https://dl.google.com/linux/direct/google-chrome-stable_current_amd64.deb sudo dpkg -i ./google-chrome-stable…...

企业建站高性能的内容管理系统

AnQiCMS 是一款高性能的内容管理系统,基于Go语言开发。它支持多站点、多语言管理,提供灵活的内容发布和模板管理功能,同时,系统内置丰富的利于SEO操作的功能,支持包括自定义字段、文档分类、批量导入导出等功能 AnQiC…...

【爬虫框架:feapder,管理系统 feaplat】

github:https://github.com/Boris-code/feapder 爬虫管理系统 feaplat:http://feapder.com/#/feapder_platform/feaplat 爬虫在线工具库 :http://www.spidertools.cn :https://www.kgtools.cn/1、feapder 简介 对于学习 Python…...

faiss库中ivf-sq(ScalarQuantizer,标量量化)代码解读-5

训练过程 通过gdb调试得到这个ivfsq的训练过程,我尝试对这个内容具体训练过程进行解析,对每个调用栈里面的逻辑和代码进行解读。 步骤函数名称调用位置说明1faiss::IndexIVF::train/faiss/IndexIVF.cpp:1143开始训练,判断是否需要训练第一级…...

代码随想录算法训练营第六十天|Day60 图论

Bellman_ford 队列优化算法(又名SPFA) https://www.programmercarl.com/kamacoder/0094.%E5%9F%8E%E5%B8%82%E9%97%B4%E8%B4%A7%E7%89%A9%E8%BF%90%E8%BE%93I-SPFA.html 本题我们来系统讲解 Bellman_ford 队列优化算法 ,也叫SPFA算法…...

在嵌入式Linux下如何用QT开发UI

在嵌入式 Linux 环境下使用 Qt 开发用户界面 (UI) 是一个常见的选择。Qt 提供了丰富的功能、跨平台支持以及优秀的图形界面开发能力,非常适合用于嵌入式系统。以下是开发流程的详细步骤: 1. 准备开发环境 硬件环境 一块运行嵌入式 Linux 的开发板&…...

:手搓截屏和帧率控制)

Python|GIF 解析与构建(5):手搓截屏和帧率控制

目录 Python|GIF 解析与构建(5):手搓截屏和帧率控制 一、引言 二、技术实现:手搓截屏模块 2.1 核心原理 2.2 代码解析:ScreenshotData类 2.2.1 截图函数:capture_screen 三、技术实现&…...

Cursor实现用excel数据填充word模版的方法

cursor主页:https://www.cursor.com/ 任务目标:把excel格式的数据里的单元格,按照某一个固定模版填充到word中 文章目录 注意事项逐步生成程序1. 确定格式2. 调试程序 注意事项 直接给一个excel文件和最终呈现的word文件的示例,…...

iPhone密码忘记了办?iPhoneUnlocker,iPhone解锁工具Aiseesoft iPhone Unlocker 高级注册版分享

平时用 iPhone 的时候,难免会碰到解锁的麻烦事。比如密码忘了、人脸识别 / 指纹识别突然不灵,或者买了二手 iPhone 却被原来的 iCloud 账号锁住,这时候就需要靠谱的解锁工具来帮忙了。Aiseesoft iPhone Unlocker 就是专门解决这些问题的软件&…...

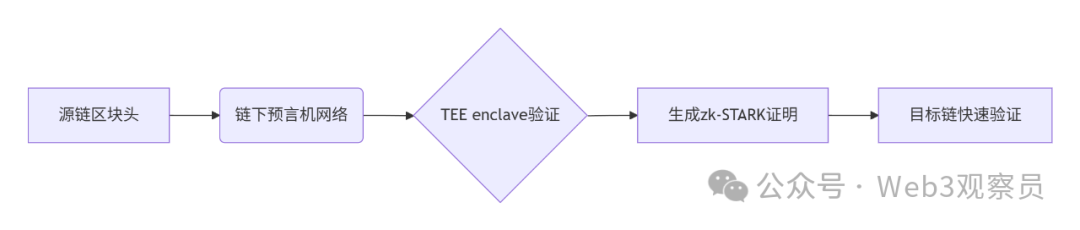

跨链模式:多链互操作架构与性能扩展方案

跨链模式:多链互操作架构与性能扩展方案 ——构建下一代区块链互联网的技术基石 一、跨链架构的核心范式演进 1. 分层协议栈:模块化解耦设计 现代跨链系统采用分层协议栈实现灵活扩展(H2Cross架构): 适配层…...

NFT模式:数字资产确权与链游经济系统构建

NFT模式:数字资产确权与链游经济系统构建 ——从技术架构到可持续生态的范式革命 一、确权技术革新:构建可信数字资产基石 1. 区块链底层架构的进化 跨链互操作协议:基于LayerZero协议实现以太坊、Solana等公链资产互通,通过零知…...

高防服务器能够抵御哪些网络攻击呢?

高防服务器作为一种有着高度防御能力的服务器,可以帮助网站应对分布式拒绝服务攻击,有效识别和清理一些恶意的网络流量,为用户提供安全且稳定的网络环境,那么,高防服务器一般都可以抵御哪些网络攻击呢?下面…...

Reasoning over Uncertain Text by Generative Large Language Models

https://ojs.aaai.org/index.php/AAAI/article/view/34674/36829https://ojs.aaai.org/index.php/AAAI/article/view/34674/36829 1. 概述 文本中的不确定性在许多语境中传达,从日常对话到特定领域的文档(例如医学文档)(Heritage 2013;Landmark、Gulbrandsen 和 Svenevei…...

Xen Server服务器释放磁盘空间

disk.sh #!/bin/bashcd /run/sr-mount/e54f0646-ae11-0457-b64f-eba4673b824c # 全部虚拟机物理磁盘文件存储 a$(ls -l | awk {print $NF} | cut -d. -f1) # 使用中的虚拟机物理磁盘文件 b$(xe vm-disk-list --multiple | grep uuid | awk {print $NF})printf "%s\n"…...

LangChain知识库管理后端接口:数据库操作详解—— 构建本地知识库系统的基础《二》

这段 Python 代码是一个完整的 知识库数据库操作模块,用于对本地知识库系统中的知识库进行增删改查(CRUD)操作。它基于 SQLAlchemy ORM 框架 和一个自定义的装饰器 with_session 实现数据库会话管理。 📘 一、整体功能概述 该模块…...

省略号和可变参数模板

本文主要介绍如何展开可变参数的参数包 1.C语言的va_list展开可变参数 #include <iostream> #include <cstdarg>void printNumbers(int count, ...) {// 声明va_list类型的变量va_list args;// 使用va_start将可变参数写入变量argsva_start(args, count);for (in…...