基于ZYNQ-7000系列的FPGA学习笔记3——开发环境搭建点亮一个LED

基于ZYNQ-7000系列的FPGA学习笔记3——开发环境搭建&点亮一个LED

- 1. 搭建开发环境

- 2. FPGA的开发流程

- 3. 点亮一个LED

- 3.1 实验要求

- 3.2 新建工程

- 3.3 原理图

- 3.4 绘制系统框图

- 3.5 绘制波形图

- 3.6 编写RTL代码

- 3.7 软件仿真

- 3.8 Vivado软件创建工程

- 3.9 分析与综合

- 3.10 设计实现

在上一期中,我们介绍了ZYNQ的相关内容,本期开始,我们正式开启FPGA的开发,首先先来搭建开发环境和尝试点亮一个LED灯

1. 搭建开发环境

所谓工欲善其事,必先利其器,想要丝滑的开发FPGA,首先需要的就是一个好用的开发环境,我们需要的环境主要由以下几个部分组成

- FPGA开发软件的安装

由于我们使用的是Xilinx的ZYNQ-7010芯片进行开发,所以我们需要安装 Vivado ,如果是Altera公司的芯片则可以安装 QUartus II ,其他公司的芯片按照要求安装对应的开发软件即可。

Vivado 设计套件,是 FPGA 厂商赛灵思(Xilinx)公司于 2012 年发布的全新的集成设计环境,以提升生产力、缩短产品上市时间、实现可编程系统集成等为目的而设计的软件。Vivado 设计套件实现 FPGA 部分的设计和开发,实现 RTL 到比特流的设计流程。

下载连接:https://www.xilinx.com/support/download.html

安装教程:赛灵思Vivado 2020.2安装教程超详细,同样适用vivado2018版本(注意本教程仅供学习使用)

- Modelsim安装

Modelsim 是 Mentor 公司的设计的业界最优秀的语言仿真工具,是单一内核支持 VHDL 与 Verilog 混合仿真的仿真工具,具有编译仿真速度快、编译的代码与平台无关等特性。

Modelsim 有几种常见的版本:SE(System Edition)、PE(Personal Edition)和 OEM(Orignal Equipment Manufactuce,即原始设备制造商),其中 SE 是最高级的版本,而集成在 Altera、Xilinx 以及 Lattice 等 FPGA厂商设计工具中的均是 OEM 版本。我们这里选择使用的是功能最全的 SE 版本。

安装教程:modelsim 2020.4SE安装教程超详细(仅供学习使用)

- Visio 软件的安装

Visio 是 Microsoft Office 软件中的一员,是一款画图软件。在 FPGA 开发的过程中,通过 Visio 软件绘制系统框图、波形图和流程图,便于读者理解程序设计的思路和编写代码。

安装教程:Visio2021安装破解教程

- MindMaster 软件的安装

MindMaster 思维导图是一种比较好的思维管理工具,在整理工作思路,简化工作流程,做好会议记录,进行任务管理、时间管理等方面都非常的实用。在 FPGA 开发过程中,通过思维导图软件绘制程序设计思维脑图,便于读者整理设计的思路。

- Notepad++软件的安装

Notepad++软件是 Windos 操作系统下的一套文档编辑器,除了可以用来制作一般的纯文字说明文件,也十分适合编写计算机程序代码。Notepad++软件不仅有语法高亮度显示,也有语法折叠功能,并且支持宏以及扩充基本功能的外挂模组。Don HO 公司每年都会对 Notepad++软件进行更新,各个版本之间除界面以及其它性能的优化之外,基本的使用功能都是一样的。

【注】:后面三个软件可以不安装,不影响FPGA的开发,但是为了更好的使用体验,所以还是建议安装一下。

下面是一些安装时的注意事项

- 开始安装软件前,关闭电脑的杀毒软件以及防火墙

- 开始安装软件前,检查个人电脑账户名称是否是中文或特殊字符,如果含有这两个其中任意的一个,会导致软件安装失败或者安装完成也不能正常工作

- 安装文件存在的路径也不要有中文或特殊字符,否则也会有错误

- 如果使用安装包进行安装,建议离线安装

- 安装软件的路径可以自定义,但是自定义的路径不能出现中文还有特殊字符,否则会导致软件安装失败

- FPGA 开发工具安装时比较耗时,需要耐心等待,中间不能出现强行终止或者意外中断,否则只能重新进行安装

2. FPGA的开发流程

在开始点灯之前,我们先来了解一下FPGA的开发流程:

- 需求分析:根据项目需求,分析项目实现需要什么功能

- 系统设计:根据项目需求设计系统框架,将系统划分为若干模块,数据流和控制流走向,评估系统运行的带宽和工作频率等

- 硬件选型:根据系统架构分析结果,我们就可以来选择合适规模和性能的 FPGA 芯片

- 绘制系统框图:确定系统内各个子模块的结构层次,梳理系统对外的输入输出信号和子模块之间的交互信号

- 绘制波形图::根据该模块的功能并且结合芯片的数据手册或者接口协议,确定模块接口信号的时序关系,然后使用绘图软件绘制各个模块的时序波形图

- 编写RTL代码:使用代码编辑软件严格按照上面的波形图编写各模块的代码

- 软件仿真:首先按照 RTL 代码的输入激励需求,编写对应的仿真代码,然后使用仿真工具对编写的RTL 代码进行仿真,然后观察仿真的波形图是否与我们绘制的时序波形一致,如果两者一致,则进行下一步新建工程,否则需要修改RTL代码

- 新建工程:使用 FPGA 开发平台新建工程并添加我们前面编写的 RTL 代码

- 分析和综合::对工程进行综合编译,通过观察综合编译生成的报告可以帮助避免最常见的设计错误,以便对设计进行分析和改进

- 约束输入:在 FPGA 开发平台对工程引脚进行约束,引脚约束完成后就可以进行布局布线与生成下载文件

- 设计实现:就是工程布局和布线的过程。它的作用是将综合生成的逻辑网表配置到具体的 FPGA 芯片上。布局布线完成后,就可以生成下载文件了,下载文件生成成功就可以进行下一步的上板验证

- 上板验证和调试:将生成的下载文件通过下载器下载到开发板,然后观察开发板的实物运行是否正常,如果上板实验现象正常,则说明前期设计与代码编写都正常;如果上板实验现象不正常,可以通过迭代前面设计的每一步来查找问题

【注】:由于我们是在正点原子领航者上实现的,所以前三步我们都不需要考虑,直接从绘制系统框图开始,当然如果不追求严谨的话,甚至可以直接从编写RTL代码开始(但是不推荐这么做)

下面我们根据上面的开发流程,介绍点亮一个LED的流程

3. 点亮一个LED

3.1 实验要求

- 通过按键控制LED的亮灭,当按键按下时,LED点亮,否则LED熄灭

3.2 新建工程

首先我们需要创建一个文件夹,存放工程代码(不要放在中文路径下),在文件夹下创建自己子文件夹,命名如下:

- doc:开发过程中使用的辅助文档文件(如绘图软件绘制的波形图文件等)

- prj:新建工程及产生的文件

- rtl:开发过程中的 RTL 代码文件

- sim:仿真工程和代码

3.3 原理图

下面是我截取的原理图

假设我们需要按键0来控制LED0的亮灭,根据上述原理图可知:按键按下为第电平,对应LED亮起为高电平;按键松开为高电平,对应LED熄灭为低电平。即按键与LED的电平时刻相反。

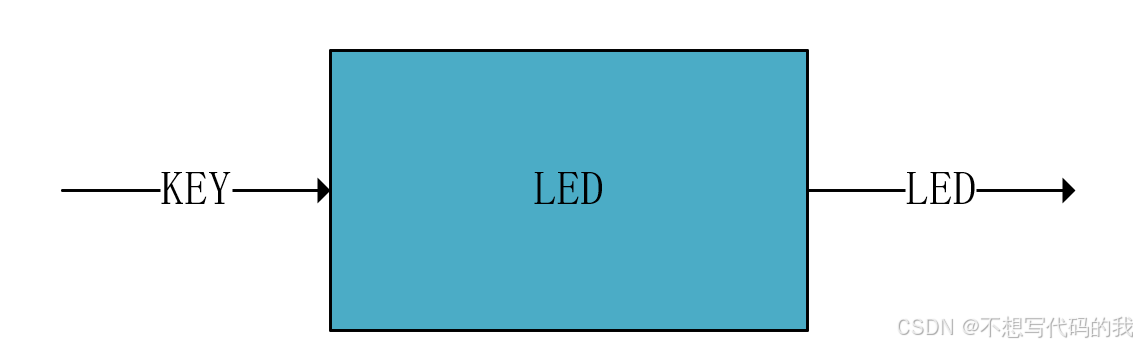

3.4 绘制系统框图

通过Viso创建系统框图,描述按键与LED之间的输入与输出关系如下:

3.5 绘制波形图

根据原理图分析的结果,绘制按键按下和松开时LED的波形变化,绘制成波形图:

3.6 编写RTL代码

这里需要通过Notepad++创建两个.v文件,分别命名为led.v(存放在rtl文件下) 和tb_led.v (存放在sim文件下)并开始编写,其中led.v为RTL实现的是按键控制LED亮灭的功能,tb_led.v是仿真文件,用来参数激励信号,测试led.v中的设计是否满足功能要求。

- led.v

//led模块

module led(input key, //输入按键,默认为高电平output led //输出LED,高电平点亮

);//当按键为高电平时,LED为1,反之为0

assign led = ~key;endmodule

- tb_led.v

`timescale 1ns/1ns //单位/精度//TB模块

module tb_led();//变量定义

reg key_in;

wire led_out;//key_in的初始化

initial beginkey_in <= 1'b1; //按键为高电平#200 //延时200nskey_in <=1'b0; //按键为低电平#200 //延时200nskey_in <=1'b1; //按键为高电平#200 //延时200nskey_in <=1'b0; //按键为低电平#200 //延时200nskey_in <=1'b1; //按键为高电平#200 //延时200nskey_in <=1'b0; //按键为低电平#200 //延时200nskey_in <=1'b1; //按键为高电平#200 //延时200nskey_in <=1'b0; //按键为低电平#200 //延时200nskey_in <=1'b1; //按键为高电平end

//模块的例化:相当于把key_in-》lkey;led-》led_out

led u_led(.key(key_in),.led(led_out)

);

endmodule

【注】:关于Notepad++的使用,这里不做介绍;这里使用的是Verilog语言,后面会详细介绍,这里之间复制即可。

3.7 软件仿真

通过Modelsim进行仿真,观察波形与预期是否一致。

【注】:Modelsim超级详细教程 手把手教一看就会 (Modelsim10.0 FPGA仿真软件 )

至此,我们就完成了软件的仿真,可以开始新建工程

3.8 Vivado软件创建工程

由于使用的是xilinx公司的芯片,所以我们这里新建工程通过vivado软件,关于vivado的使用,可以参考:【FPGA】Vivado软件使用教程

【注】:我们这里使用的芯片型号是:xc7z010clg400-1

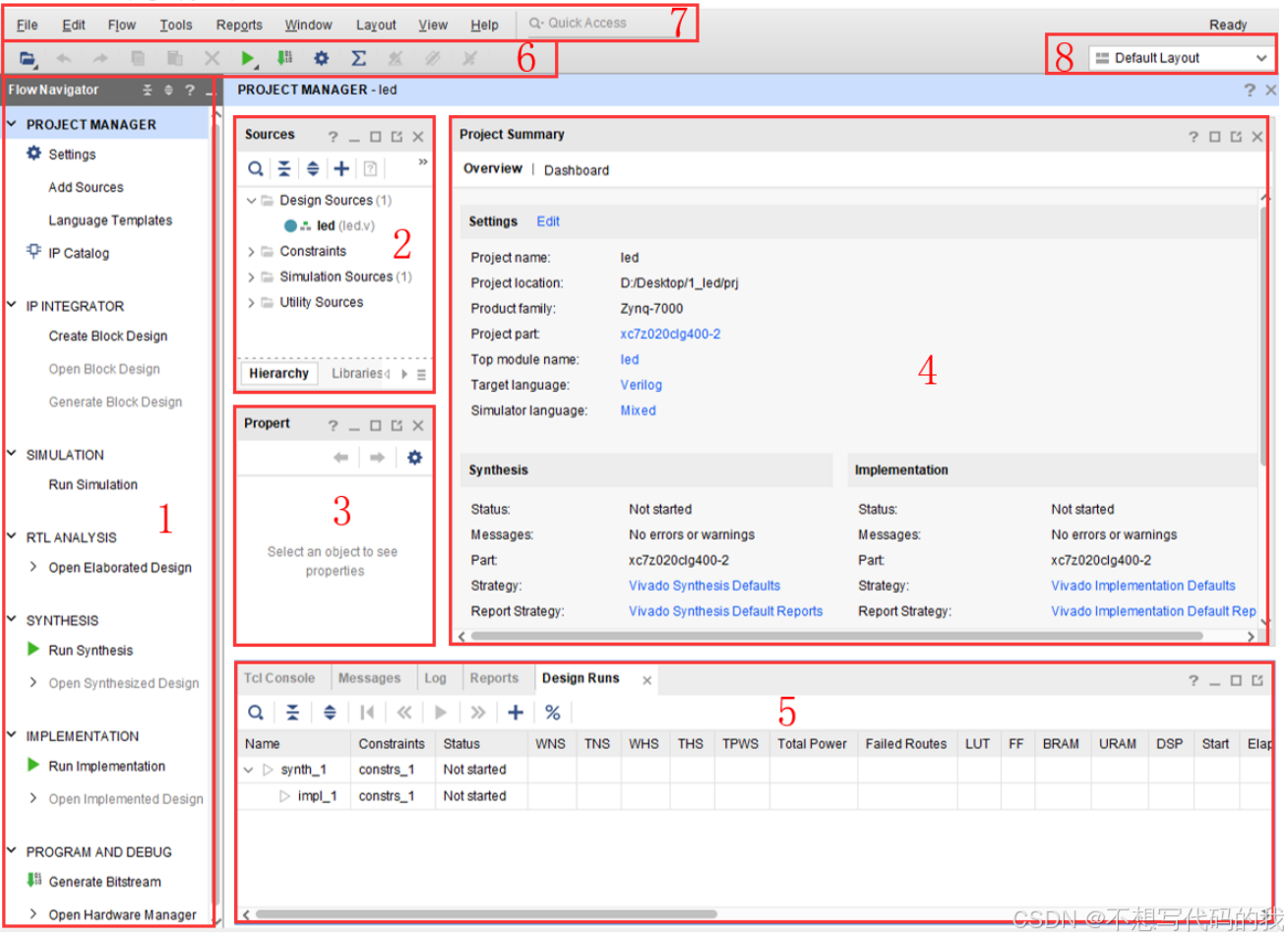

下面我们来介绍一下创建完之后的工程:

这里大致可以分为8个工作区

- Flow Navigator:Flow Navigator 提供对命令和工具的访问,其包含从设计输入到生成比特流的整个过程。 在点击了相应的命令时,整个 Vivado 工程主界面的各个子窗口可能会作出相应的更改。

- 数据窗口区域:默认情况下,Vivado IDE 的这个区域显示的是设计源文件和数据相关的信息。

- Sources 窗口:显示层次结构(Hierarchy)、IP 源文件(IP Sources)、库(Libraries)和编译顺序(Compile Order)的视图

- Netlist 窗口:提供分析后的(elaborated)或综合后的(synthesized)逻辑设计的分层视图

- Properties 窗口:显示有关所选逻辑对象或器件资源的特性信息

- 工作空间(Workspace):工作区显示了具有图形界面的窗口和需要更多屏幕空间的窗口,包括

- Project Summary。提供了当前工程的摘要信息,它在运行设计命令时动态地更新。

- 用于显示和编辑基于文本的文件和报告的 Text Editor

- 原理图(Schematic)窗口

- 器件(Device)窗口

- 封装(Package)窗口

- 结果窗口区域:在 Vivado IDE 中所运行的命令的状态和结果,显示在结果窗口区域中,这是一组子窗口的集合。在运行命令、生成消息、创建日志文件和报告文件时,相关信息将显示在此区域。默认情况下,此区域包括以下窗口:

- Tcl Console:允许您输入 Tcl 命令,并查看以前的命令和输出的历史记录

- Messages:显示当前设计的所有消息,按进程和严重性分类,包括“Error”、“Critical Warning”、“Warning”等等

- Log:显示由综合、实现和仿真 run 创建的日志文件。

- Reports:提供对整个设计流程中的活动 run 所生成的报告的快速访问。

- Designs Runs:管理当前工程的 runs。

- 主工具栏:主工具栏提供了对 Vivado IDE 中最常用命令的单击访问

- 主菜单:主菜单栏提供对 Vivado IDE 命令的访问。

- 窗口布局(Layout)选择器:Vivado IDE 提供预定义的窗口布局,以方便调用设计过程中的各种窗口。布局选择器使您能够轻松地更改窗口布局。或者,可以使用菜单栏中的“Layout”菜单来更改窗口布局。

3.9 分析与综合

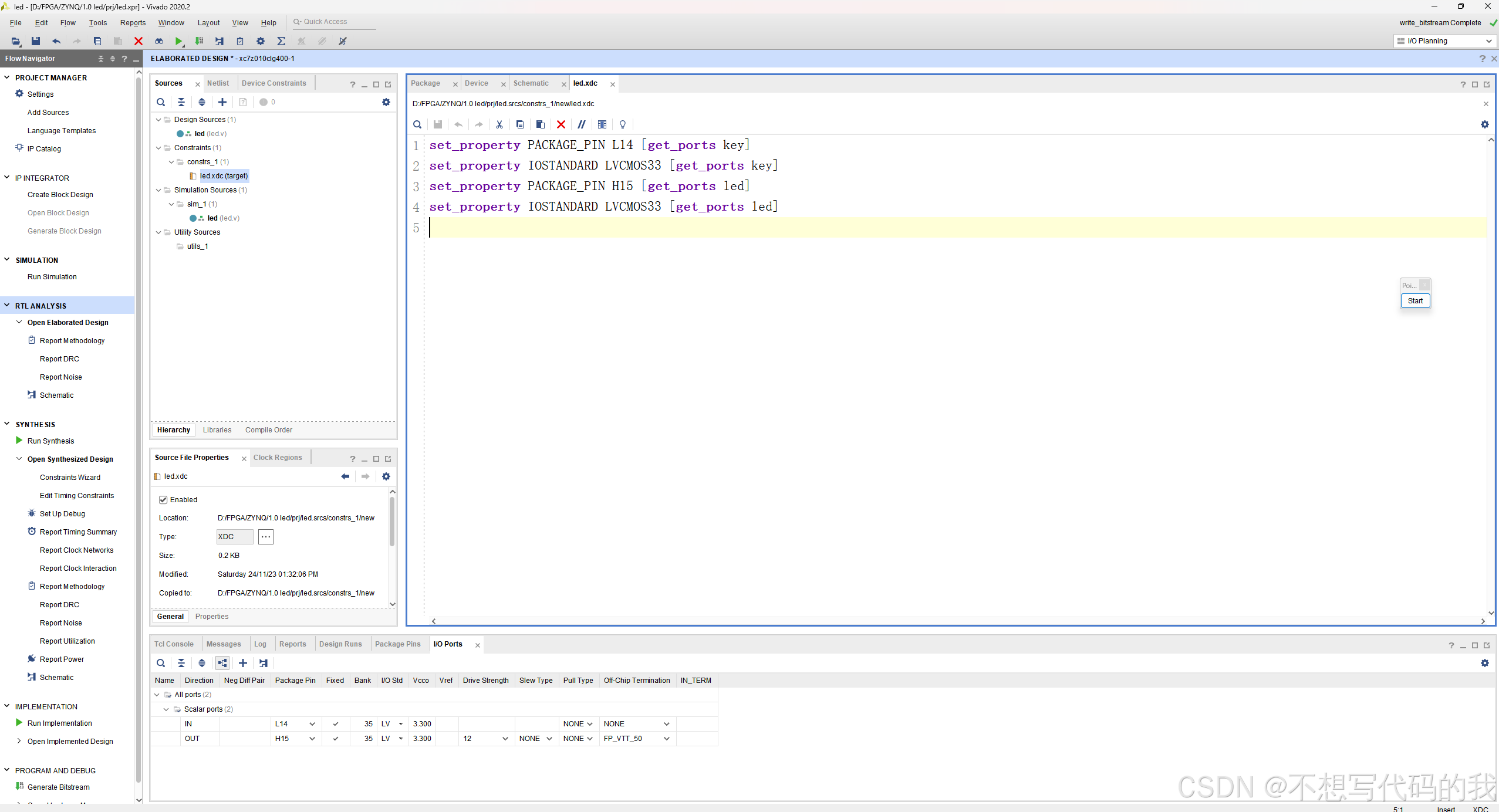

新建工程之后,需要对我们的代码进行分析与综合,点击Flow Navigator工作区的 RTLANALYSIS 下的Open Elaborated Design选项,确定后打开分析之后的界面:

可以看到这里是vidavo对编写好的RTL代码进行分析,根据我们代码中输入与输出的关系,生成对应的电路连接(这个只是理论上的,实际上还没有连接),下一步我们就需要把这种连接关系映射到FPGA的内部和芯片引脚上,首先第一步是连接芯片引脚:

在工作区8,将窗口切换为I/O Planing,修改 ZYNQ芯片的管脚属性如图中所示:

这里介绍一下IO的属性选项:

- Name:工程中顶层端口的名称

- Direction:说明管脚是输入还是输出

- Neg Diff Pair:负差分对,差分信号在 I/O Ports 窗口中只显示在一行里中(只会显示 P 端信号,N 端信号显示在 Neg Diff Pair 属性栏中)

- Package Pin:配置管脚封装

- Fixed:每一个端口都有 Fixed 属性,表明该逻辑端口是由用户赋值的。端口必须保持锁定状态,才能避免生成比特流时不会发生错误

- Bank,I/O Std,Vcco,Slew Type,Drive Strength:显示 I/O 端口的参数值

- Bank:显示管脚所在的 Bank

- I/O Std:配置管脚的电平标准,常用电平标准有 LVTTL 和 LVCMOS、SSTL、LVDS 与 HSTL 等

- Vcco:选择的管脚的电压值

- Vref:在我们的设计中,硬件上 VREF 引脚悬空。

- Drive Strength:驱动强度,默认 12mA

- Slew Type:指上升下降沿的快慢,设置快功耗会高一点

- Pull Type:管脚上下拉设置,有上拉、下拉、保持与不设置

- Off-Chip Termination:终端阻抗,默认 50Ω

- IN-TERM:是用于 input 的串联电阻

完成上述配置之后,保存生成对应的XDC文件(也叫约束文件),如下图:

【注】:除了上述产生XDC文件的方法之外,也可以通过写代码的方式自己编写,这里不做展示

接下来,需要对代码进行综合:点击“Flow Navigator”窗口中的“Run Synthesis”按钮后直接确认:

等待一会在弹出的窗口点击第二个选项,然后点击ok:

就可以看到代码和电路图的对应关系(其中输入和输出都在原来分析的基础上增加了一个缓冲区),到这里我们就完成了综合,下一步就是约束输入,但实际上,我们刚刚配置引脚信息,生成XDC文件的时候,就已经完成了初步的约束输入,所以下一步可以直接设计实现:

这里先补充一下 “Flow Navigator”窗口中除了“Run Synthesis”按钮,其他按键的意义:

- Constraints Wizard:约束向导。

- Edit Timing Constraints:编辑时间约束。

- Set Up Debug:引导创建在线调试。

- Report Timing Summary:报告时序摘要并运行时序分析。

- Report Clock Networks:时钟网络报告。

- Report Clock Interaction:时钟交互报告。

- Report Methodology:检查符合 UltraFast 设计方法的设计。

- Report DRC:设计规则检查。

- Report Noise:噪声分析报告。

- Report Utilization:资源利用率报告。

- Report Power:电源报告。

- Schematic:打开综合后的原理图设计。

3.10 设计实现

我们点击“Flow Navigator”窗口中的“Run Implementation”按钮,点击ok后等待一会,出现如下界面:

选择第一个选项,然后点击ok,出现如下界面:

可以看到出现的芯片内部的连接关系图,我们尝试放大看一下:

之后我们可以生成对应的比特流文件,点击“Flow Navigator”窗口中的“Generate Bitstream”按钮,直接点击ok,等待一会,在弹出的窗口,点击第二个选项:

连接好开发板的电源线和下载器,然后点击图片中中的Auto Connect 等待连接完成。

连接完成之后,点击相同位置的Program Device 选项,选择生成的.bit文件,下载到芯片中,即可以实现按键控制LED的亮灭(运行结构这里就不放了,不好展示)。至此,本篇内容结束,你已经成功入门,并且是一个和我一样合格的萌新!!!

【注】:下载完比特流后,如果开发板断电,程序会丢失。如果想要程序断电不丢失的话,需要将程序固化至开发板中,这个后面再介绍。

以上就是本期的所有内容,创造不易,点个关注再走呗。

相关文章:

基于ZYNQ-7000系列的FPGA学习笔记3——开发环境搭建点亮一个LED

基于ZYNQ-7000系列的FPGA学习笔记3——开发环境搭建&点亮一个LED 1. 搭建开发环境2. FPGA的开发流程3. 点亮一个LED3.1 实验要求3.2 新建工程3.3 原理图3.4 绘制系统框图3.5 绘制波形图3.6 编写RTL代码3.7 软件仿真3.8 Vivado软件创建工程3.9 分析与综合3.10 设计实现 在上…...

)

队列-链式描述(C++)

定义 使用链表描述队列时,通常包含以下几个基本要素: 队头指针(Front Pointer):指向队列中第一个(即最早进入队列的)元素的节点。队尾指针(Rear Pointer):指…...

Kali Linux使用Netdiscover工具的详细教程

Kali Linux使用Netdiscover工具的详细教程 引言 在网络安全和渗透测试的过程中,网络发现是一个至关重要的步骤。Netdiscover是Kali Linux中一个非常实用的网络发现工具,它可以帮助用户快速识别局域网中的活动设备。本文将详细介绍如何使用Netdiscover工…...

arkTS:使用ArkUI实现用户信息的持久化管理与自动填充(PersistentStorage)

arkUI:使用ArkUI实现用户信息的持久化管理与自动填充(PersistentStorage) 1 主要内容说明2 例子2.1 登录页2.1.1登陆页的相关说明2.1.1.1 持久化存储的初始化2.1.1.2 输入框2.1.1.3 记住密码选项2.1.1.4 登录按钮的逻辑2.1.1.5 注册跳转 2.1.…...

IntelliJ+SpringBoot项目实战(二十)--基于SpringSecurity实现Oauth2服务端和客户端

在前面的帖子中介绍了SpringSecurityJWT实现了认证和授权的功能。因为基于Oauth2的统一认证在项目需求中越来越多,所以有必要将OAuth2的解决方案也整合进来,这样我们的产品既可以作为一个业务系统,也可以作为一个独立的统一认证服务器。下面详…...

如何实现剪裁功能

文章目录 1 概念介绍2 使用方法2.1 ClipOval2.2 ClipRRect3 示例代码我们在上一章回中介绍了AspectRatio Widget相关的内容,本章回中将介绍剪裁类组件(Clip).闲话休提,让我们一起Talk Flutter吧。 1 概念介绍 我们在这里说的剪裁类组件主要是指对子组件进行剪裁操作,常用的…...

LeetCode 动态规划 爬楼梯

爬楼梯 假设你正在爬楼梯。需要 n 阶你才能到达楼顶。 每次你可以爬 1 或 2 个台阶。你有多少种不同的方法可以爬到楼顶呢? 示例 1: 输入:n 2 输出:2 解释:有两种方法可以爬到楼顶。 1 阶 1 阶 2 阶 示例 2ÿ…...

Java 工厂模式:深度解析与应用指南

在 Java 编程的广袤天地里,设计模式宛如璀璨星辰,照亮了开发者构建高效、灵活且可维护软件系统的道路。其中,工厂模式作为创建型设计模式的关键成员,在对象创建环节扮演着举足轻重的角色,极大地增强了代码的适应性与扩…...

-- SVG 集成详解)

HTML5系列(5)-- SVG 集成详解

前端技术探索系列:HTML5 SVG 集成详解 🎨 开篇寄语 👋 前端开发者们, 在前五篇文章中,我们探讨了 HTML5 的多个特性。今天,让我们深入了解 SVG 的魅力,看看如何创建可缩放的矢量图形。 一、…...

深度学习常见数据集处理方法

1、数据集格式转换(json转txt) import json import os 任务:实例分割,labelme的json文件, 转txt文件 Ultralytics YOLO format <class-index> <x1> <y1> <x2> <y2> ... <xn> <yn> # 类…...

1180 - 【入门】数字出现次数

题目描述 有50个数(0-19),求这50个数中相同数字出现的最多次数为几次? 输入 50个数字 输出 1个数字(即相同数字出现的最多次数) 样例 输入 复制 1 10 2 0 15 8 12 7 0 3 15 0 15 18 16 7 17 16 9 …...

C++20: 像Python一样split字符串

概要 Python 的字符串天生支持 split( ) 操作,支持单个字符或字符串作为分隔符。 C 在这方面显得很笨拙,但是在 C20 下经过一番尝试,还是能够提供类似的简洁调用。 Python 代码 s 0,11,336,23,370nums s.split(,) for n in nums:print(n…...

Unity3D UI 嵌套滚动视图

Unity3D 解决 UI 嵌套滚动视图滑动问题。 嵌套滚动视图 滑动问题 在游戏开发中,我们常常会遇到一种情况,在一个滚动视图列表中,每个 item 还包含了一个内嵌的滚动视图。 这样,当我们在滑动外层的滚动视图时,如果点…...

你还没有将 Siri 接入GPT对话功能吗?

由于各种原因,国内ios用户目前无缘自带 AI 功能,但是这并不代表国内 ios 无法接入 AI 功能,接下来手把手带你为iPhone siri 接入 gpt 对话功能。 siri 接入 chatGPT 暂时还无法下载 ChatGPT app,或者没有账号的读者可以直接跳到…...

_C#_串口助手_字符串拼接缺失问题(未知原理)

最近使用WPF开发串口助手时,遇到一个很奇怪的问题,无论是主线程、异步还是多线程,当串口接收速度达到0.016s一次以上,就会发生字符串缺失问题并且很卡。而0.016s就一切如常,仿佛0.015s与0.016s是天堑之隔。 同一份代码…...

浅析大数据时代下的网络安全

一、大数据时代下网络安全的现状 在全球化进程不断深入发展的情况下,互联网行业发展速度也更加迅猛,人们对网络信息的需求量不断增加,所以目前已经进入了大数据时代。 随着计算机技术的不断发展,我国互联网网络规模、网民数量、…...

Mysql数据库基础篇笔记

目录 sql语句 DDL——数据库定义语言(定义库,表,字段) 数据库操作: 表操作: DML 增删改语句 DQL 语法编写顺序: 条件查询 DCL 用户管理: 权限管理: 函数 常见字符串内置函…...

rabbitmq原理及命令

目录 一、RabbitMQ原理1、交换机(Exchange)fanoutdirecttopicheaders(很少用到) 2、队列Queue3、Virtual Hosts4、基础对象 二、RabbitMQ的一些基本操作:1、用户管理2、用户角色3、vhost4、开启web管理接口5、批量删除队列 一、Ra…...

)

React进阶面试题(四)

React 的 reconciliation(协调)算法 Reconciliation是React的diff算法,用于比较更新前后的虚拟DOM树差异,从而使用最小的代价将原始DOM按照新的状态、属性进行更新。其目的是找出两棵树的差异,原生方式直接比较复杂度…...

24/12/1 算法笔记<强化学习> 创建Maze交互

我们今天制作一个栅格的游戏。 我们直接上代码教学。 1.载入库和查找相应的函数版本 import numpy as np import time import sysif sys.version_info.major 2:import Tkinter as tk else:import tkinter as tk 2.设置长宽和单元格大小 UNIT 40 MAZE_H 4 MAZE_W 4 3.初始…...

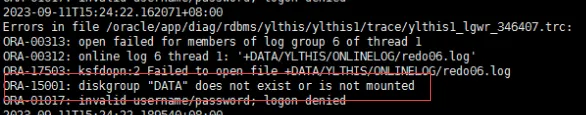

19c补丁后oracle属主变化,导致不能识别磁盘组

补丁后服务器重启,数据库再次无法启动 ORA01017: invalid username/password; logon denied Oracle 19c 在打上 19.23 或以上补丁版本后,存在与用户组权限相关的问题。具体表现为,Oracle 实例的运行用户(oracle)和集…...

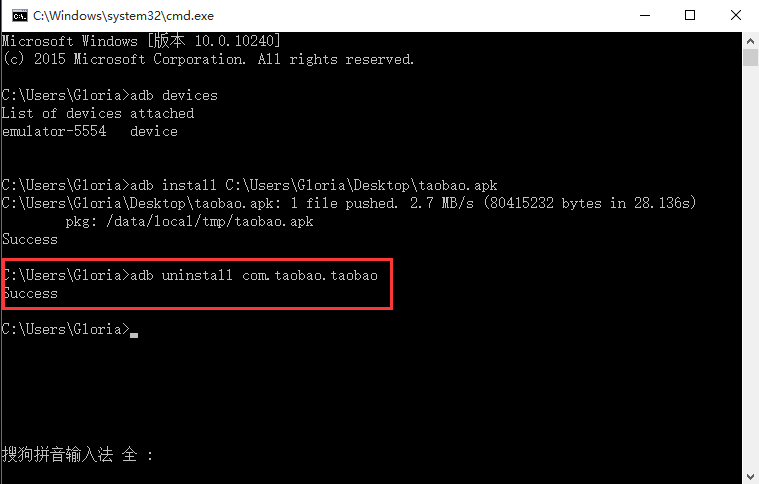

Appium+python自动化(十六)- ADB命令

简介 Android 调试桥(adb)是多种用途的工具,该工具可以帮助你你管理设备或模拟器 的状态。 adb ( Android Debug Bridge)是一个通用命令行工具,其允许您与模拟器实例或连接的 Android 设备进行通信。它可为各种设备操作提供便利,如安装和调试…...

Qt Widget类解析与代码注释

#include "widget.h" #include "ui_widget.h"Widget::Widget(QWidget *parent): QWidget(parent), ui(new Ui::Widget) {ui->setupUi(this); }Widget::~Widget() {delete ui; }//解释这串代码,写上注释 当然可以!这段代码是 Qt …...

智能仓储的未来:自动化、AI与数据分析如何重塑物流中心

当仓库学会“思考”,物流的终极形态正在诞生 想象这样的场景: 凌晨3点,某物流中心灯火通明却空无一人。AGV机器人集群根据实时订单动态规划路径;AI视觉系统在0.1秒内扫描包裹信息;数字孪生平台正模拟次日峰值流量压力…...

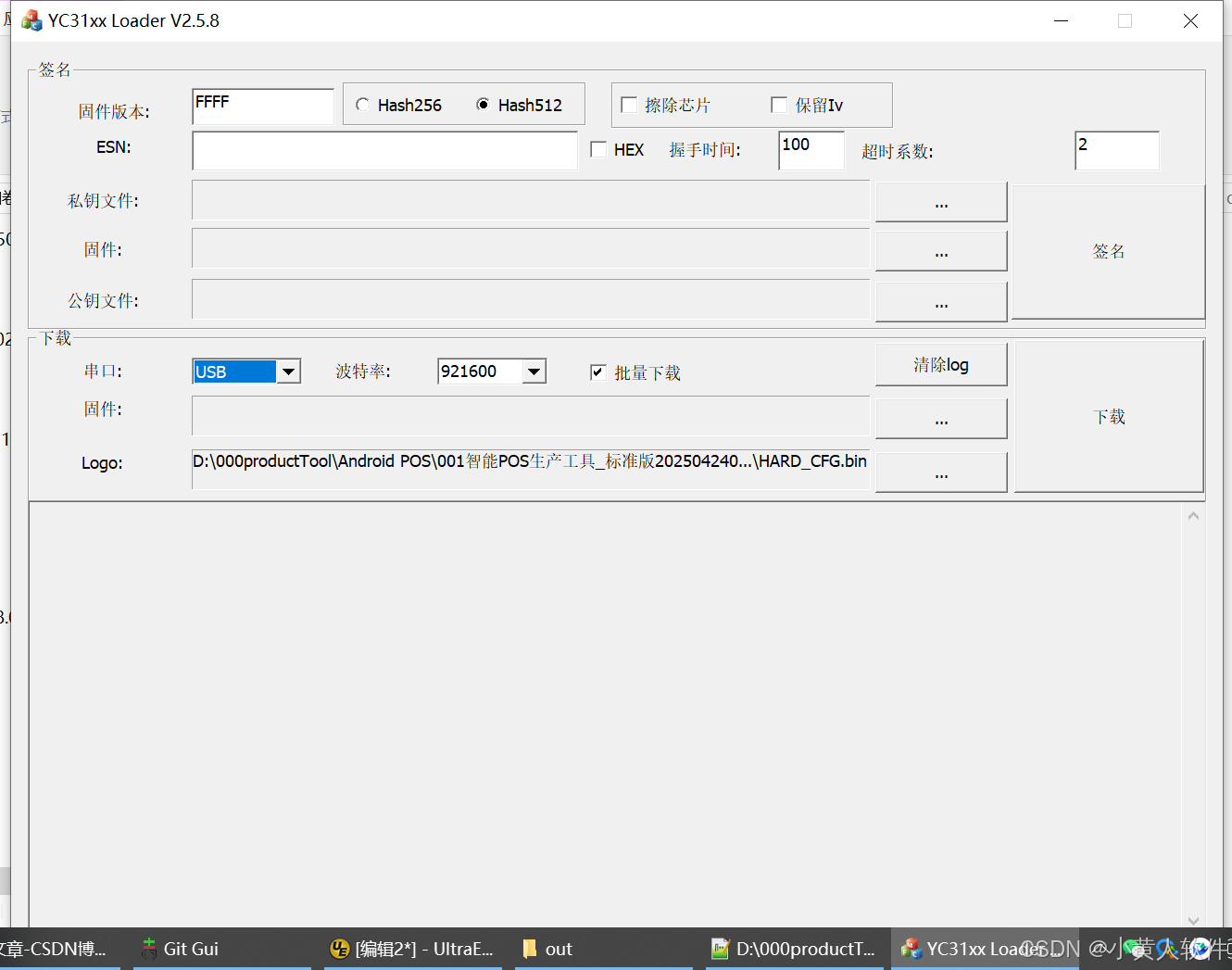

C++ Visual Studio 2017厂商给的源码没有.sln文件 易兆微芯片下载工具加开机动画下载。

1.先用Visual Studio 2017打开Yichip YC31xx loader.vcxproj,再用Visual Studio 2022打开。再保侟就有.sln文件了。 易兆微芯片下载工具加开机动画下载 ExtraDownloadFile1Info.\logo.bin|0|0|10D2000|0 MFC应用兼容CMD 在BOOL CYichipYC31xxloaderDlg::OnIni…...

)

.Net Framework 4/C# 关键字(非常用,持续更新...)

一、is 关键字 is 关键字用于检查对象是否于给定类型兼容,如果兼容将返回 true,如果不兼容则返回 false,在进行类型转换前,可以先使用 is 关键字判断对象是否与指定类型兼容,如果兼容才进行转换,这样的转换是安全的。 例如有:首先创建一个字符串对象,然后将字符串对象隐…...

《C++ 模板》

目录 函数模板 类模板 非类型模板参数 模板特化 函数模板特化 类模板的特化 模板,就像一个模具,里面可以将不同类型的材料做成一个形状,其分为函数模板和类模板。 函数模板 函数模板可以简化函数重载的代码。格式:templa…...

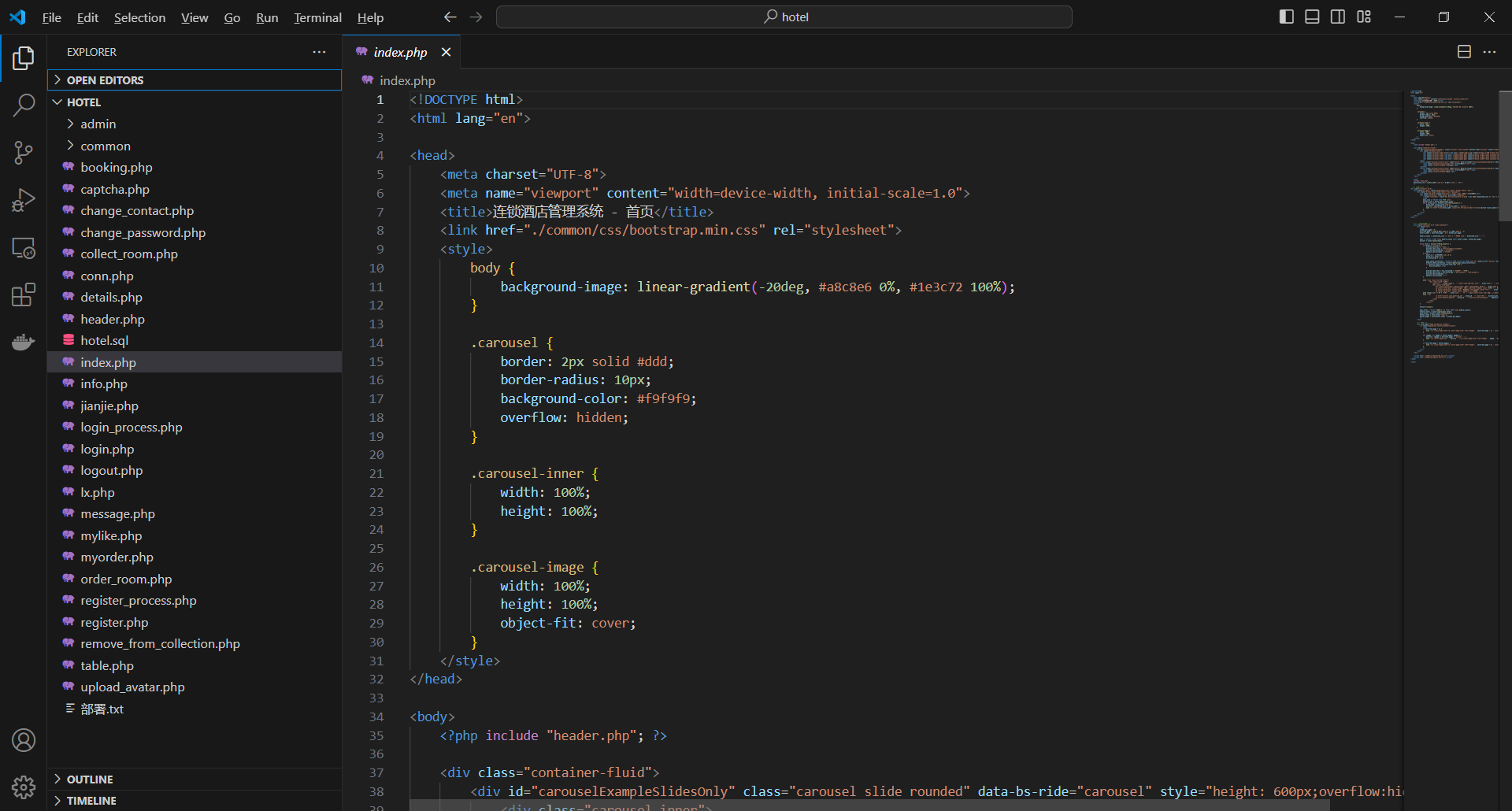

基于PHP的连锁酒店管理系统

有需要请加文章底部Q哦 可远程调试 基于PHP的连锁酒店管理系统 一 介绍 连锁酒店管理系统基于原生PHP开发,数据库mysql,前端bootstrap。系统角色分为用户和管理员。 技术栈 phpmysqlbootstrapphpstudyvscode 二 功能 用户 1 注册/登录/注销 2 个人中…...

微服务通信安全:深入解析mTLS的原理与实践

🔥「炎码工坊」技术弹药已装填! 点击关注 → 解锁工业级干货【工具实测|项目避坑|源码燃烧指南】 一、引言:微服务时代的通信安全挑战 随着云原生和微服务架构的普及,服务间的通信安全成为系统设计的核心议题。传统的单体架构中&…...

uni-app学习笔记三十五--扩展组件的安装和使用

由于内置组件不能满足日常开发需要,uniapp官方也提供了众多的扩展组件供我们使用。由于不是内置组件,需要安装才能使用。 一、安装扩展插件 安装方法: 1.访问uniapp官方文档组件部分:组件使用的入门教程 | uni-app官网 点击左侧…...