FPGA入门教程

引言

FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种灵活且强大的硬件设备,广泛应用于数字电路设计、信号处理、嵌入式系统等领域。与传统的ASIC(专用集成电路)不同,FPGA允许用户在硬件级别上重新配置逻辑电路,这使得它在快速原型设计、高性能计算和实时处理中具有独特的优势。

本文旨在为初学者提供一个全面的FPGA入门教程,涵盖FPGA的基本概念、开发流程、代码示例以及实际应用场景。通过本文的学习,读者将能够理解FPGA的工作原理,并掌握如何使用硬件描述语言(HDL)进行简单的FPGA设计。

1. FPGA基础概念

1.1 FPGA的架构

FPGA的核心由以下几个部分组成:

- 可编程逻辑单元(CLB):CLB是FPGA的基本构建块,包含查找表(LUT)、触发器和多路复用器等组件。CLB可以配置为执行各种逻辑功能。

- 可编程互连资源:FPGA内部的逻辑单元通过可编程互连资源连接在一起,形成复杂的电路。

- 输入/输出块(IOB):IOB用于与外部设备进行通信,支持多种电气标准和协议。

- 块存储器(BRAM):FPGA通常包含一定数量的块存储器,用于存储数据。

- 数字信号处理单元(DSP):一些FPGA还包含专用的DSP单元,用于高效执行乘法和累加操作。

1.2 FPGA与ASIC的区别

FPGA和ASIC都是用于实现数字电路的硬件设备,但它们之间存在显著差异:

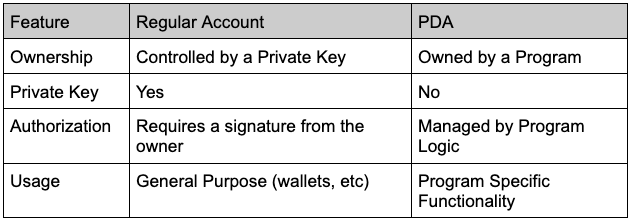

| 特性 | FPGA | ASIC |

|---|---|---|

| 灵活性 | 可重新编程 | 一旦制造完成,无法更改 |

| 开发周期 | 较短 | 较长 |

| 成本 | 较高(单件成本) | 较低(大规模生产时) |

| 性能 | 较低 | 较高 |

| 功耗 | 较高 | 较低 |

FPGA适用于需要快速原型设计和小批量生产的场景,而ASIC则更适合大规模生产和性能要求极高的应用。

2. FPGA开发流程

2.1 硬件描述语言(HDL)

FPGA设计通常使用硬件描述语言(HDL)进行。最常见的HDL包括Verilog和VHDL。本文将以Verilog为例进行讲解。

2.2 开发工具

FPGA开发通常需要使用厂商提供的开发工具,如Xilinx的Vivado或Intel的Quartus Prime。这些工具提供了从设计输入到综合、布局布线、仿真和下载的全流程支持。

2.3 开发流程概述

FPGA开发的基本流程如下:

- 设计输入:使用HDL编写设计代码。

- 综合:将HDL代码转换为逻辑网表。

- 布局布线:将逻辑网表映射到FPGA的物理资源上。

- 仿真:验证设计的正确性。

- 下载:将设计配置到FPGA芯片中。

3. Verilog代码示例

3.1 简单的组合逻辑电路

以下是一个简单的Verilog代码示例,实现了一个2输入与门。

module and_gate (input wire a,input wire b,output wire y

);assign y = a & b;

endmodule

代码说明:

module定义了一个模块,模块名为and_gate。input wire a和input wire b是输入端口。output wire y是输出端口。assign y = a & b;表示输出y是输入a和b的逻辑与结果。

3.2 时序逻辑电路

以下是一个简单的Verilog代码示例,实现了一个4位计数器。

module counter (input wire clk,input wire reset,output reg [3:0] count

);always @(posedge clk or posedge reset) beginif (reset)count <= 4'b0000;elsecount <= count + 1;end

endmodule

代码说明:

module定义了一个模块,模块名为counter。input wire clk是时钟信号。input wire reset是复位信号。output reg [3:0] count是一个4位寄存器,用于存储计数值。always @(posedge clk or posedge reset)表示在时钟上升沿或复位信号上升沿时执行块内的代码。if (reset)判断复位信号是否为高电平,如果是,则将计数器清零。else否则,计数器加1。

3.3 仿真测试

为了验证上述计数器的功能,我们可以编写一个简单的测试平台(testbench)。

module counter_tb;reg clk;reg reset;wire [3:0] count;// 实例化计数器模块counter uut (.clk(clk),.reset(reset),.count(count));// 生成时钟信号initial beginclk = 0;forever #5 clk = ~clk;end// 测试过程initial beginreset = 1;#20;reset = 0;#100;$finish;end

endmodule

代码说明:

module counter_tb;定义了一个测试平台模块。reg clk;和reg reset;是测试平台的输入信号。wire [3:0] count;是测试平台的输出信号。counter uut实例化了计数器模块。initial begin ... end块用于生成时钟信号和测试过程。forever #5 clk = ~clk;生成一个周期为10个时间单位的时钟信号。reset = 1;和reset = 0;分别用于初始化和释放复位信号。$finish;结束仿真。

4. 实际应用场景

4.1 数字信号处理

FPGA在数字信号处理(DSP)领域有着广泛的应用。例如,FPGA可以用于实现快速傅里叶变换(FFT)、滤波器、调制解调器等算法。由于FPGA的并行处理能力,它能够高效地处理大量的数据流。

4.2 嵌入式系统

FPGA常用于嵌入式系统中,作为协处理器或主处理器。例如,FPGA可以用于实现图像处理、视频编码、网络协议处理等功能。FPGA的灵活性和高性能使其在嵌入式系统中具有独特的优势。

4.3 通信系统

FPGA在通信系统中也扮演着重要角色。例如,FPGA可以用于实现无线通信中的基带处理、信道编码、调制解调等功能。FPGA的高性能和低延迟使其成为通信系统中的理想选择。

总结

本文介绍了FPGA的基本概念、开发流程以及Verilog代码示例。通过本文的学习,读者应该能够理解FPGA的工作原理,并掌握如何使用Verilog进行简单的FPGA设计。FPGA作为一种灵活且强大的硬件设备,在数字信号处理、嵌入式系统和通信系统等领域有着广泛的应用前景。希望本文能够为初学者提供一个良好的起点,帮助他们在FPGA开发的道路上迈出坚实的第一步。

相关文章:

FPGA入门教程

引言 FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种灵活且强大的硬件设备,广泛应用于数字电路设计、信号处理、嵌入式系统等领域。与传统的ASIC(专用集成电路)不同,FPGA允许用户…...

Liunx系统 : 进程间通信【IPC-Shm共享内存】

文章目录 System V共享内存创建共享内存shmget 控制共享内存shmctl shm特性 System V System V是Liunx中的重要的进程间通信机制,它包括(shm)共享内存,(msg)消息队列和(sem)信号量。…...

KafkaRocketMQ

Kafka 消息生产与消费流程 1. 消息生产 生产者创建消息: 指定目标 Topic、Key(可选)、Value。可附加 Header 信息(如时间戳、自定义元数据)。 选择分区(Partition): 若指定 Key&am…...

HarmonyOS Next 中的状态管理

在声明式UI编程框架中,UI是程序状态的运行结果,用户构建了一个UI模型,其中应用的运行时的状态是参数。当参数改变时,UI作为返回结果,也将进行对应的改变。这些运行时的状态变化所带来的UI的重新渲染,在ArkU…...

基于qiime2的16S数据分析全流程:从导入数据到下游分析一条龙

目录 创建metadata 把数据导入qiime2 去除引物序列 双端合并 (dada2不需要) 质控 (dada2不需要) 使用deblur获得特征序列 使用dada2生成代表序列与特征表 物种鉴定 可视化物种鉴定结果 构建进化树(ITS一般不构建进化树…...

)

【软件测试开发】:软件测试常用函数1.0(C++)

1. 元素的定位 web⾃动化测试的操作核⼼是能够找到⻚⾯对应的元素,然后才能对元素进⾏具体的操作。 常⻅的元素定位⽅式⾮常多,如id,classname,tagname,xpath,cssSelector 常⽤的主要由cssSelector和xpath…...

vue2项目修改浏览器显示的网页图标

1.准备一个新的图标文件,通常是. ico格式,也可以是. Png、. Svg等格式 2.将新的图标文件(例如:faviconAt.png)放入项目的public文件夹中。如下图 public文件夹中的所有文件都会在构建时原样复制到最终的输出目录(通常是dist) 3. 修改vue项目…...

开源、创新与人才发展:机器人产业的战略布局与稚晖君成功案例解析

目录 引言 一、开源:机器人产业的战略布局 促进技术进步和生态建设 吸引人才和合作伙伴 建立标准和网络效应 降低研发风险与成本 二、稚晖君:华为"天才少年计划"的成功典范 深厚的技术积累与动手能力 强烈的探索和创新意识 持续公开…...

线程相关作业

1.创建两个线程,分支线程1拷贝文件的前一部分,分支线程2拷贝文件的后一部分 #include "head.h"#define BUFFER_SIZE 1024// 线程参数结构体,包含文件名和文件偏移量 typedef struct {FILE *src_file;FILE *dest_file;long start_o…...

通义万相2.1开源版本地化部署攻略,生成视频再填利器

2025 年 2 月 25 日晚上 11:00 通义万相 2.1 开源发布,前两周太忙没空搞它,这个周末,也来本地化部署一个,体验生成效果如何,总的来说,它在国内文生视频、图生视频的行列处于领先位置,…...

【模拟CMOS集成电路设计】带隙基准(Bandgap)设计与仿真(基于运放的电流模BGR)

【模拟CMOS集成电路设计】带隙基准(Bandgap)设计与仿真 前言工程文件&部分参数计算过程,私聊~ 一、 设计指标指标分析: 二、 电路分析三、 仿真3.1仿真电路图3.2仿真结果(1)运放增益(2)基准温度系数仿真(3)瞬态启动仿真(4)静态…...

如何选择国产串口屏?

目录 1、迪文 2、淘晶驰 3、广州大彩 4、金玺智控 5、欣瑞达 6、富莱新 7、冠显 8、有彩 串口屏,顾名思义,就是通过串口通信接口(如RS232、RS485、TTL UART等)与主控设备进行通信的显示屏。其核心功能是显示信息和接收输入…...

Solana中的程序派生地址(PDAs):是什么,为什么,以及如何?

程序派生地址 (PDA) 在 Solana 中的应用:什么、为什么和如何? 在学习 Solana 时,你会经常听到关于 程序派生地址 (PDAs) 的讨论。它们就像这样 —— 强大、多功能,而且最重要的是,稍微被误解。如果你是一个开发者&…...

利用FatJar彻底解决Jar包冲突(一)

利用FatJar彻底解决Jar包冲突 序FatJar的加载与隔离⼀、 FatJar概念⼆、FatJar的加载三、FatJar的隔离四、隔离机制验证五、 FatJar的定位六、 打包注意点 序 今天整理旧电脑里的资料,偶然翻到大概10年前实习时写的笔记,之前经常遇到Java依赖冲突的问题…...

Spring MVC笔记

01 什么是Spring MVC Spring MVC 是 Spring 框架中的一个核心模块,专门用于构建 Web 应用程序。它基于经典的 MVC 设计模式(Model-View-Controller),但通过 Spring 的特性(如依赖注入、注解驱动)大幅简化了…...

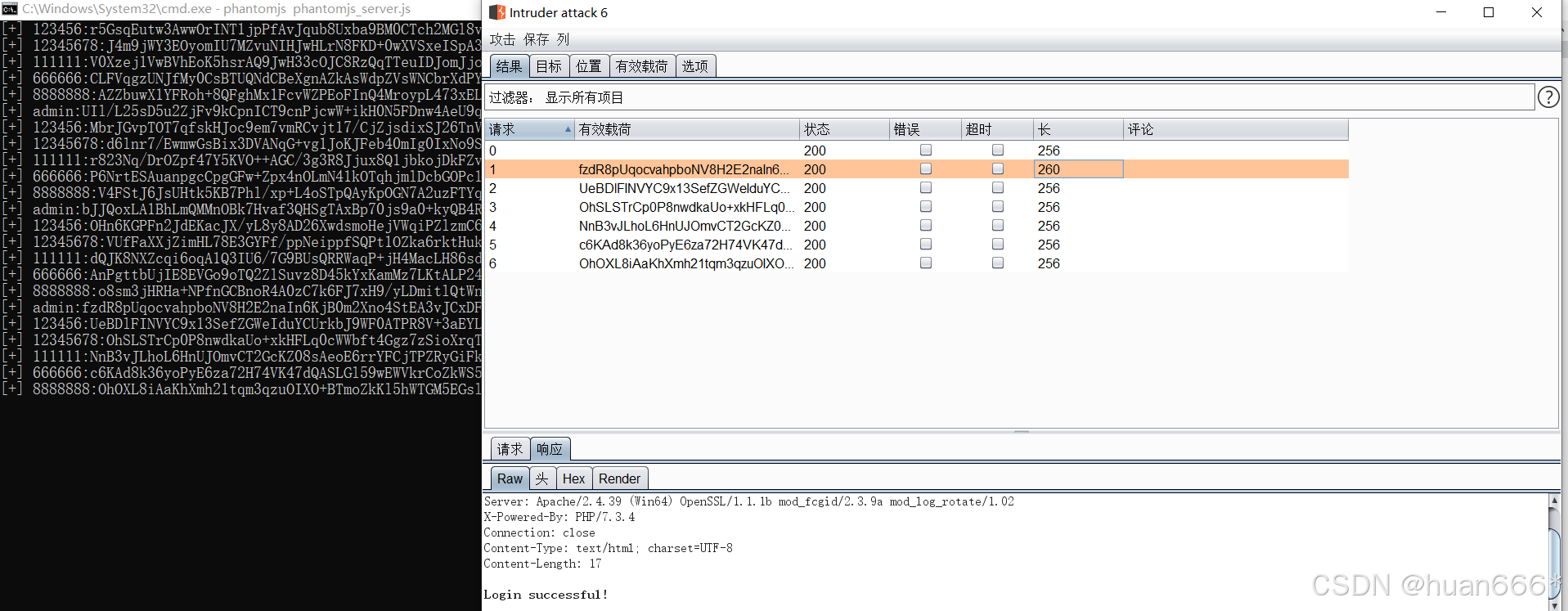

BurpSuite插件jsEncrypter使用教程

一、前言 在当今Web应用安全测试中,前端加密已成为开发者保护敏感数据的常用手段。然而,这也给安全测试人员带来了挑战,传统的抓包方式难以获取明文数据,测试效率大打折扣。BurpSuite作为一款强大的Web安全测试工具,其…...

【C#实现手写Ollama服务交互,实现本地模型对话】

前言 C#手写Ollama服务交互,实现本地模型对话 最近使用C#调用OllamaSharpe库实现Ollama本地对话,然后思考着能否自己实现这个功能。经过一番查找,和查看OllamaSharpe源码发现确实可以。其实就是开启Ollama服务后,发送HTTP请求&a…...

Android Glide 框架线程管理模块原理的源码级别深入分析

一、引言 在现代的 Android 应用开发中,图片加载是一个常见且重要的功能。Glide 作为一款广泛使用的图片加载框架,以其高效、灵活和易用的特点受到了开发者的青睐。其中,线程管理模块是 Glide 框架中至关重要的一部分,它负责协调…...

每天记录一道Java面试题---day32

MySQL索引的数据结构、各自优劣 回答重点 B树:是一个平衡的多叉树,从根节点到每个叶子节点的高度差不超过1,而且同层级的节点间有指针相互连接。在B树上的常规检索,从根节点到叶子节点的搜索效率基本相当,不会出现大…...

Vue3 Pinia 符合直觉的Vue.js状态管理库

Pinia 符合直觉的Vue.js状态管理库 什么时候使用Pinia 当两个关系非常远的组件,要传递参数时使用Pinia组件的公共参数使用Pinia...

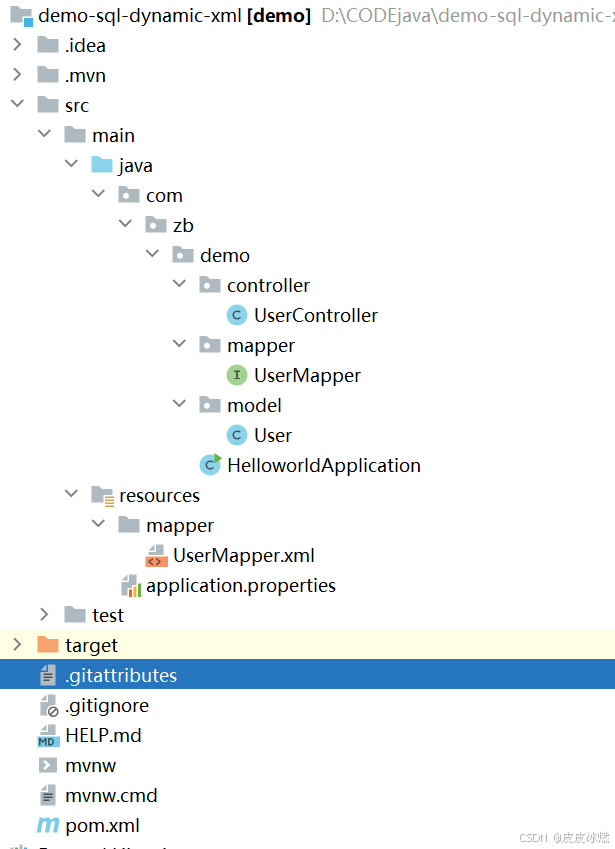

SpringBoot-17-MyBatis动态SQL标签之常用标签

文章目录 1 代码1.1 实体User.java1.2 接口UserMapper.java1.3 映射UserMapper.xml1.3.1 标签if1.3.2 标签if和where1.3.3 标签choose和when和otherwise1.4 UserController.java2 常用动态SQL标签2.1 标签set2.1.1 UserMapper.java2.1.2 UserMapper.xml2.1.3 UserController.ja…...

铭豹扩展坞 USB转网口 突然无法识别解决方法

当 USB 转网口扩展坞在一台笔记本上无法识别,但在其他电脑上正常工作时,问题通常出在笔记本自身或其与扩展坞的兼容性上。以下是系统化的定位思路和排查步骤,帮助你快速找到故障原因: 背景: 一个M-pard(铭豹)扩展坞的网卡突然无法识别了,扩展出来的三个USB接口正常。…...

华为云AI开发平台ModelArts

华为云ModelArts:重塑AI开发流程的“智能引擎”与“创新加速器”! 在人工智能浪潮席卷全球的2025年,企业拥抱AI的意愿空前高涨,但技术门槛高、流程复杂、资源投入巨大的现实,却让许多创新构想止步于实验室。数据科学家…...

【Oracle APEX开发小技巧12】

有如下需求: 有一个问题反馈页面,要实现在apex页面展示能直观看到反馈时间超过7天未处理的数据,方便管理员及时处理反馈。 我的方法:直接将逻辑写在SQL中,这样可以直接在页面展示 完整代码: SELECTSF.FE…...

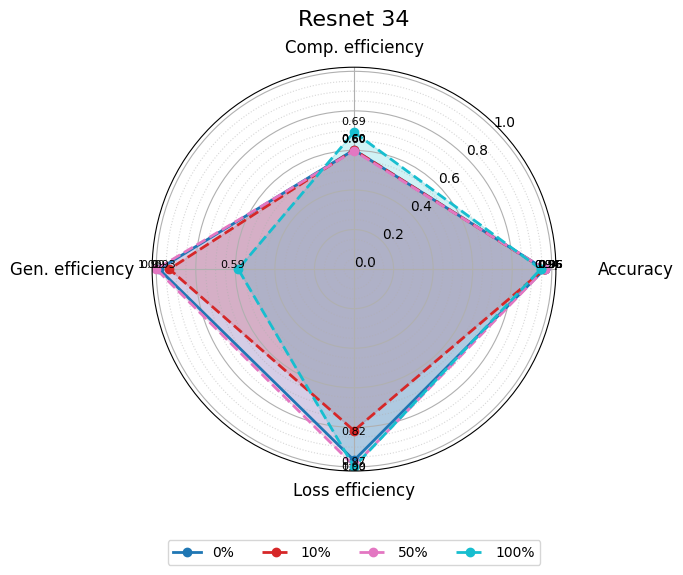

使用分级同态加密防御梯度泄漏

抽象 联邦学习 (FL) 支持跨分布式客户端进行协作模型训练,而无需共享原始数据,这使其成为在互联和自动驾驶汽车 (CAV) 等领域保护隐私的机器学习的一种很有前途的方法。然而,最近的研究表明&…...

解锁数据库简洁之道:FastAPI与SQLModel实战指南

在构建现代Web应用程序时,与数据库的交互无疑是核心环节。虽然传统的数据库操作方式(如直接编写SQL语句与psycopg2交互)赋予了我们精细的控制权,但在面对日益复杂的业务逻辑和快速迭代的需求时,这种方式的开发效率和可…...

Objective-C常用命名规范总结

【OC】常用命名规范总结 文章目录 【OC】常用命名规范总结1.类名(Class Name)2.协议名(Protocol Name)3.方法名(Method Name)4.属性名(Property Name)5.局部变量/实例变量(Local / Instance Variables&…...

条件运算符

C中的三目运算符(也称条件运算符,英文:ternary operator)是一种简洁的条件选择语句,语法如下: 条件表达式 ? 表达式1 : 表达式2• 如果“条件表达式”为true,则整个表达式的结果为“表达式1”…...

【Go】3、Go语言进阶与依赖管理

前言 本系列文章参考自稀土掘金上的 【字节内部课】公开课,做自我学习总结整理。 Go语言并发编程 Go语言原生支持并发编程,它的核心机制是 Goroutine 协程、Channel 通道,并基于CSP(Communicating Sequential Processes࿰…...

2023赣州旅游投资集团

单选题 1.“不登高山,不知天之高也;不临深溪,不知地之厚也。”这句话说明_____。 A、人的意识具有创造性 B、人的认识是独立于实践之外的 C、实践在认识过程中具有决定作用 D、人的一切知识都是从直接经验中获得的 参考答案: C 本题解…...