SOC FPGA之HPS模型设计(一)

目录

一、建立HPS硬件系统模型

1.1 GHRD

1.2 从0开始搭建HPS

1.2.1 FPGA Interfaces

1.2.1.1 General

1.2.1.2 AXI Bridge

1.2.1.3 FPGA-to-HPS SDRAM Interface

1.2.1.4 DMA Peripheral Request

1.2.1.5 Interrupts

1.2.1.6 EMAC ptp interface

1.2.2 Peripheral Pin Multiplexing

1.2.3 HPS Clocks

1.2.3.1 Input Clocks

1.2.3.2 Output Clocks

1.2.4 SDRAM

1.2.4.1 PHY Settings

1.2.4.2 Memory Parameters

1.2.4.3 Memory Timing

1.2.4.4 Board Settings

1.3 添加其他组件

1.4 产生Qsys系统

1.5 编译Quartus工程

1.6 硬件系统外设的输入/输出测试

1.7 相关代码

一、建立HPS硬件系统模型

建立HPS硬件模型有两种方式,一种是在GHRD中添加或修改,另外一种是从0开始搭建HPS

1.1 GHRD

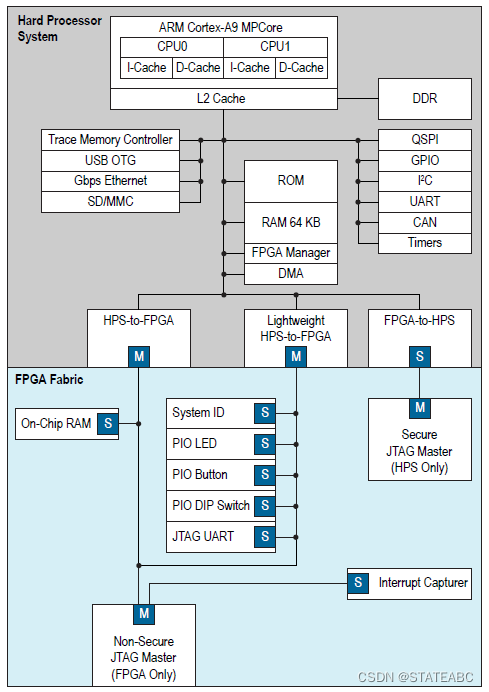

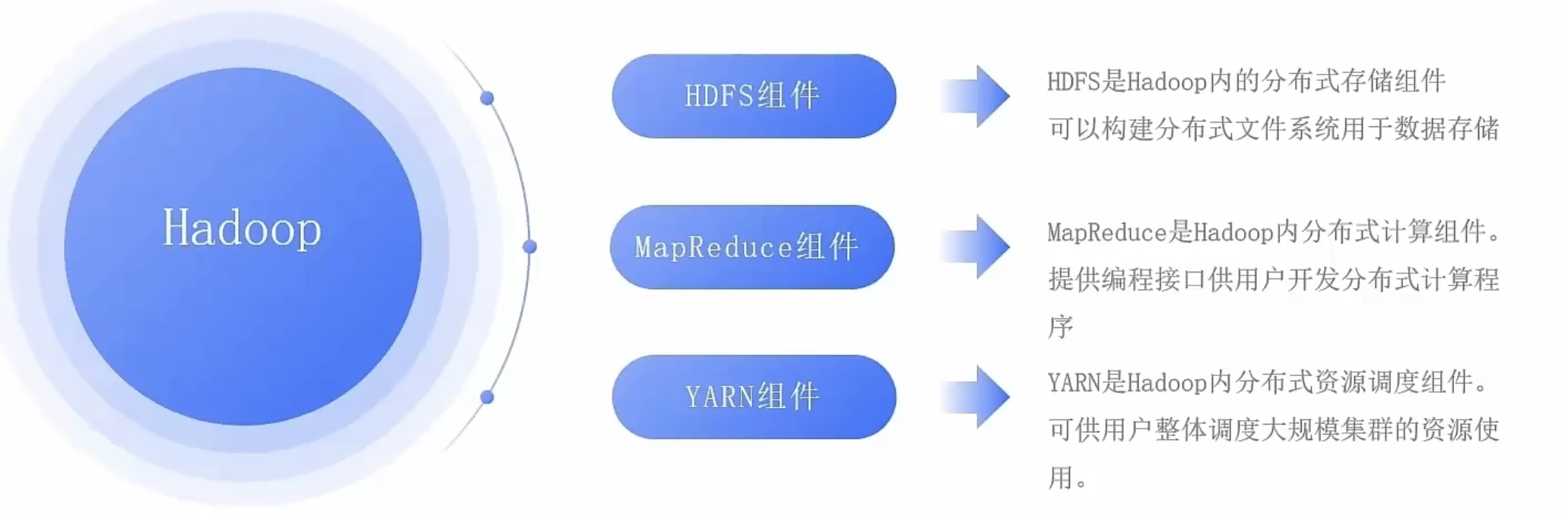

GSRD(Golden System Reference Design, 黄金系统参考设计)包含:

- GHRD(Golden Hardware Reference Design, 黄金硬件参考设计)

- 基于U-Boot的Bootloader参考

- Linux BSP参考

- Linux应用程序示例

其中GHRD包含 Cyclone V SoC / Arria V SoC Development Kit的完整HPS设计,如双核ARM Cortex-A9 MPCore HPS、用户按键输入(PIO Buttion)、用户拨码开关输入(PIO DIPSW)、LED输出(PIO LED)、64KB片上存储器、JTAG-to-Avalon主接口连接桥(JTAG Master)、JATG-UART调试模块、中断捕获器(Interrupt Capturer)及系统ID(SysID)等。使用时只需在其中添加或修改所需的内容即可。

1.2 从0开始搭建HPS

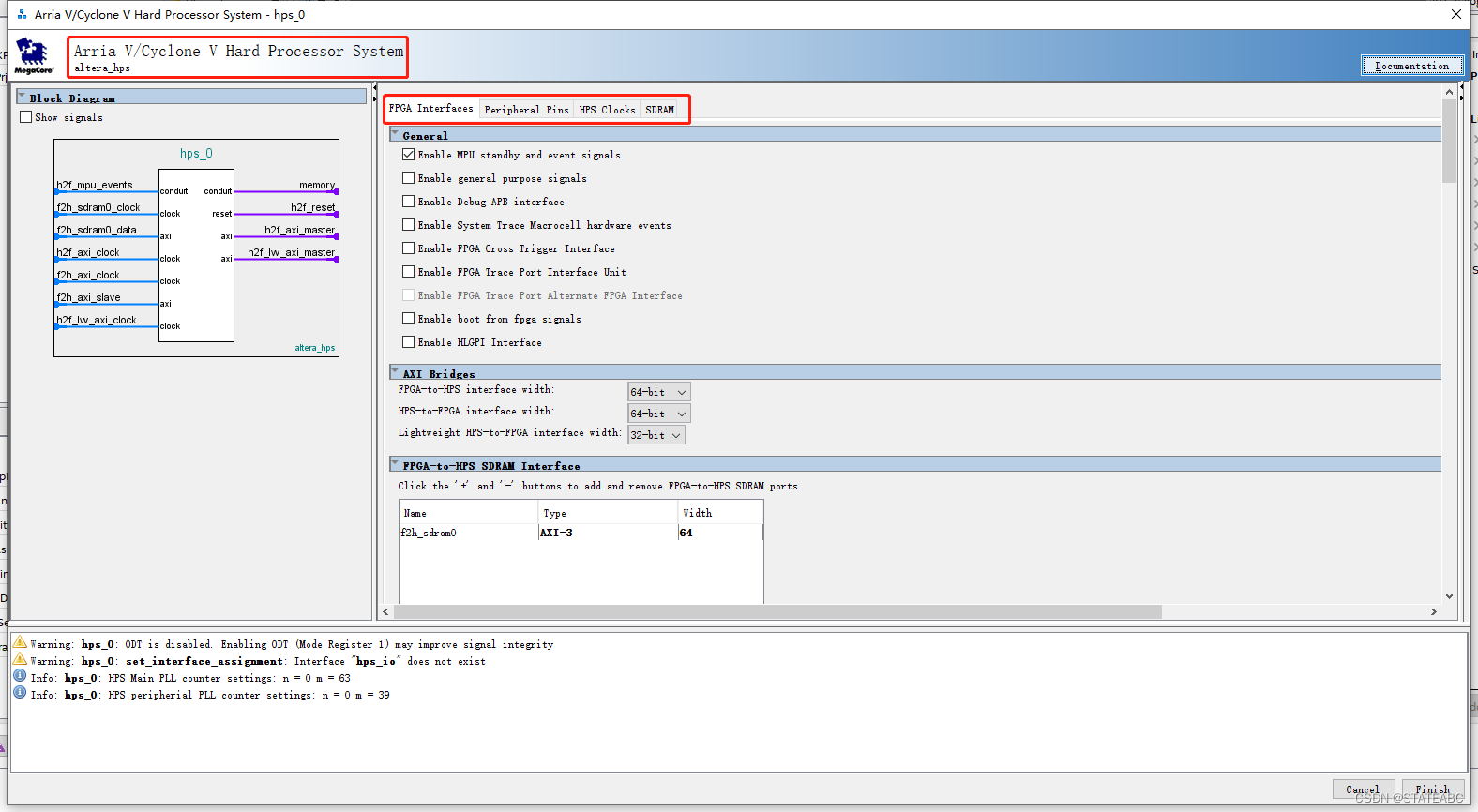

在Quartus中创建工程HPS_Qsys_Prj,进入Platform Designer,添加Hard Processor System组件

1.2.1 FPGA Interfaces

在FPGA Interfaces标签设置页有General、AXI Bridges、FPGA-to-HPS SDRAM Interface、Resets、DMA Peripheral Request、Interrupts、EMAC ptp Interface

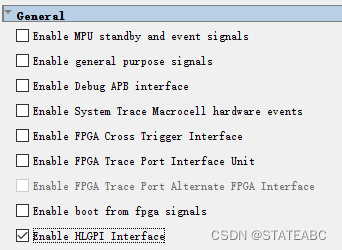

1.2.1.1 General

当General中某些选项被选中,相应的接口会出现在HPS模块中

| 参数名 | 描述 |

| Enable MPU standby and event signals | 通知FPGA接口微处理器单元(MPU)处于待机模式; 可以从等待事件(WFE)状态唤醒一个MPCore处理器 |

| Enable general purpose signals | 在SOC器件的HPS部分,启用FPGA与FPGA管理器之间的一组32位的单向普通目的接口 |

| Enable Debug APB interface | 启用对FPGA的调试接口,允许在HPS中访问调试组件 |

| Enable System Trace Macrocell hardware events | 启用系统跟踪单元(STM)硬件事件,允许FPGA中的逻辑向跟踪过程插入信息 |

| Enable FPGA Cross Trigger Interface | 启用交叉触发器接口(CTI),允许出发Source/Sink与出发的交叉触发(ECT)相连 |

| Enable FPGA Trace Port Interface Unit | 启用跟踪端口接口单元(TPIU)与FPGA逻辑之间的一个接口。TPIU是片上跟踪源与某个跟踪端口之间的桥梁 |

| Enable FPGA Trace Port Alternate FPGA Interface | 当启用跟踪端口时,会创建一个与Arria 10跟踪接口兼容的接口 |

| Enable boot from fpga signals | 启用HPS的一个输入信号,表明是否片上RAM中的preloader可以使用 |

| Enable HLGPI Interface | 启用HPS的GPIO |

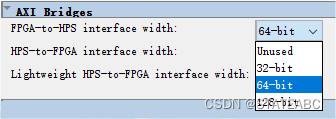

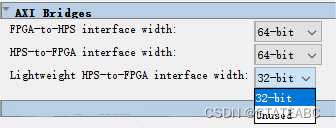

1.2.1.2 AXI Bridge

FPGA-to-HPS interface width和HPS-to-FPGA interface width可选Unused、32-bit、64-bit和128-bit,即FPGA2HPS接口位宽和HPS2FPGA接口位宽。

Lightweight HPS-to-FPGA interface width可选32-bit、Unused,即轻量级LWHPS2FPGA接口位宽。

1.2.1.3 FPGA-to-HPS SDRAM Interface

可以通过添加一个或多个SDRAM从端口(最多6个)让FPGA来访问HPS SDRAM子系统,其数据宽度可选32、64、128或256位,接口类型可选AXI-3、双向Avalon-MM、只写Avalon-MM、只读Avalon-MM。

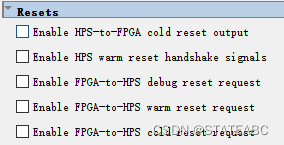

1.2.1.4 Resets

| 参数名 | 参数描述 |

| Enable HPS-to-FPGA cold reset output | 启用HPS2FPGA接口得冷启动输出 |

| Enable HPS warm reset handshake signals | 启用一组附加的复位握手信号,允许软件通知HPS在其安全时开启一个FPGA结构中的热复位信号 |

| Enable FPGA-to-HPS debug reset request | 启用FPGA2HPS调试复位请求接口 |

| Enable FPGA-to-HPS warm reset request | 启用FPGA2HPS热复位请求接口 |

| Enable FPGA-to-HPS cold reset request | 启用FPGA2HPS冷复位请求接口 |

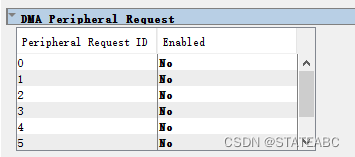

1.2.1.4 DMA Peripheral Request

单独启用每个DMA控制器外设请求ID(Peripheral Request ID),每个请求ID可以使能连接FPGA的8个逻辑DMA通道中对应的通道接口。外设请求ID[4-7]是与CAN控制器共用。

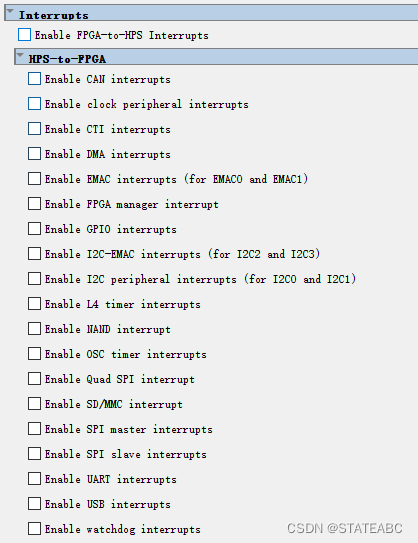

1.2.1.5 Interrupts

对不同中断使能,勾选Enable FPGA-to-HPS Interrupts则启用HPS中FPGA对MPU的中断信号,下方则是HPS中的每个外设提供给FPGA的中断信号

1.2.1.6 EMAC ptp interface

Enable EMAC Precision Time Protocol(PTP) FPGA Interface,启用EMACO精确时间协议 (PTP) FPGA接口,当EMAC通过Pinmux连接到HPS I/O时,可通过FPGA访问IEEE 1588精密时间协议(PTP)接口。当EMAC连接到FPGA时,PTP信号可用。

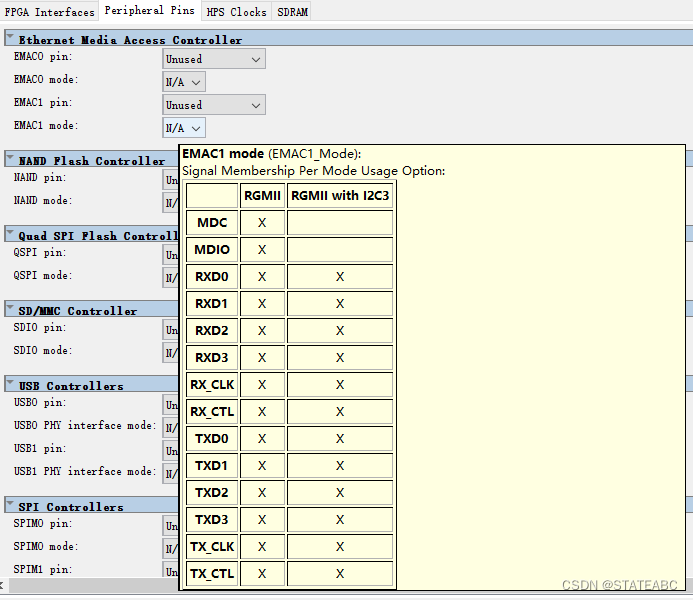

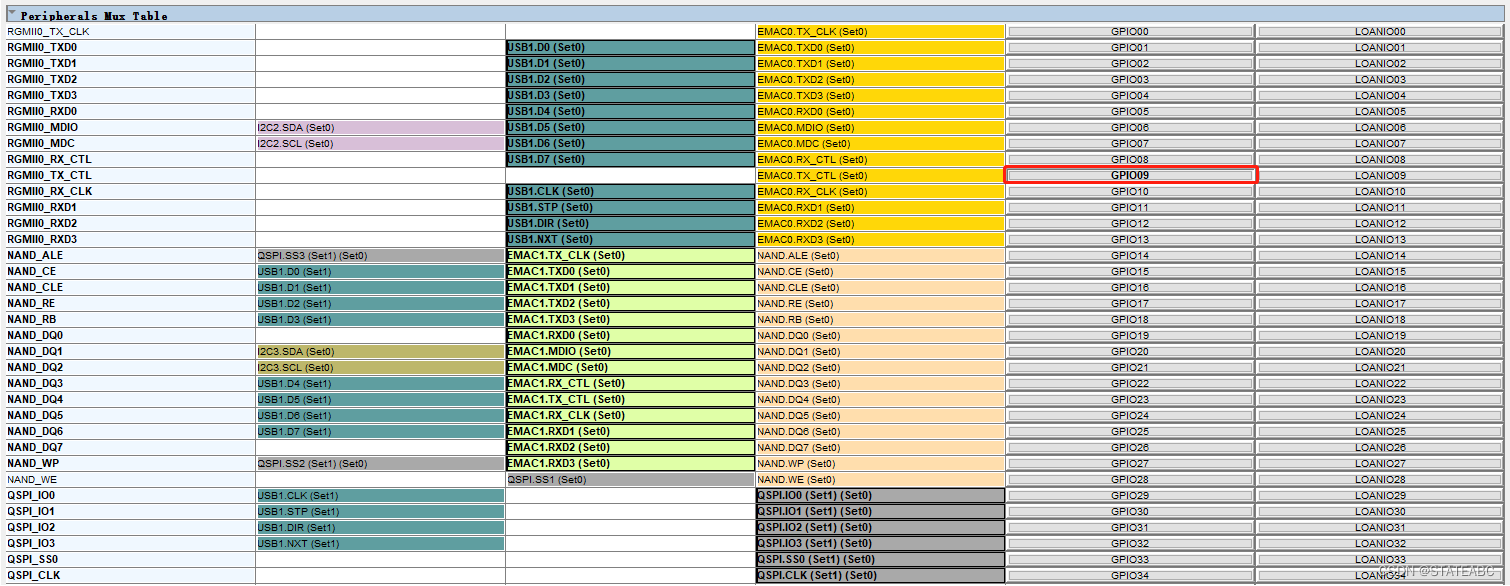

1.2.2 Peripheral Pin Multiplexing

Peripheral Pin Multiplexing标签页包含了HPS所有可用外设的参数设置,通过选择HPS I/O设置可用启用对应的外设。当启用某个外设时,还需要设置其相应的工作模式。将鼠标放到相应的外设模式(mode)设置选项位置几秒时间,即可出现一个下拉列表,下拉列表给出了外设工作模式下的引脚定义。引脚复用设置应该与所用SOC FPGA开发板上的实际外设连接相匹配。

在最下方的Peripherals Mux Table中列出了HPS外设的引脚分配情况,包括没有分配给任何外设的引脚,可以将其作为普通目的I/O(GPIO)使用,点击相对应的后面的GPIO即可。

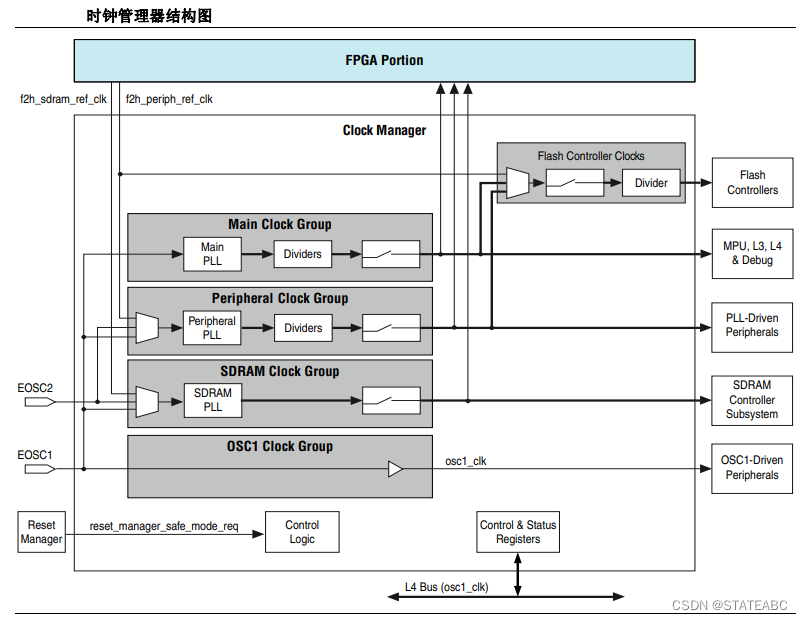

1.2.3 HPS Clocks

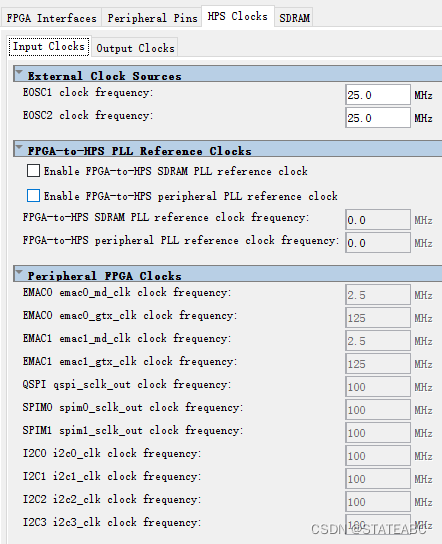

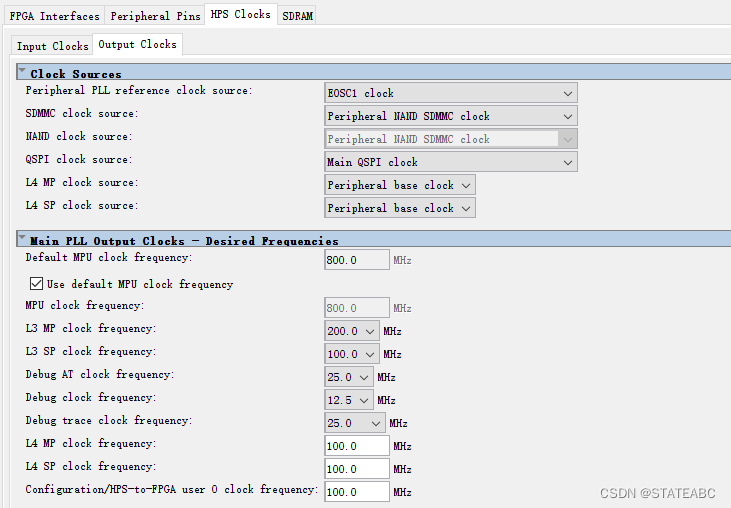

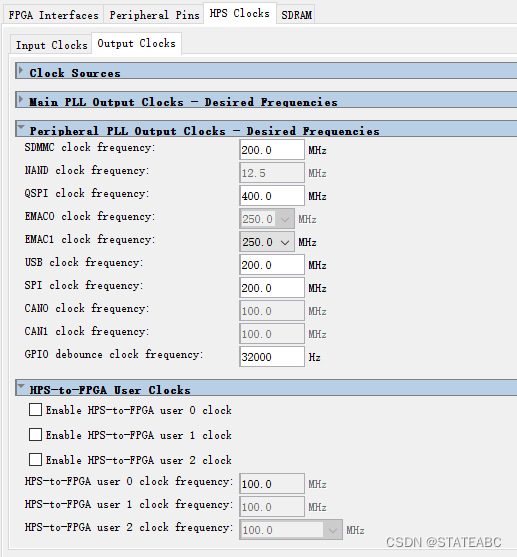

HPS Clocks包括Input Clocks和Output Clocks

注意:这里设置的时钟频率是指期望的最高频率,实际时钟频率可以通过MPU上的软件对寄存器的设置进行修改,这里设置的时钟频率将出现在Qsys产生的Synopsys设计约束文件(.sdc)中。

1.2.3.1 Input Clocks

External Clock Sources用于设置E0SC的时钟频率

FPGA-to-HPS PLL Reference Clocks用于启用HPS SDRAM PLL提供参考时钟的FPGA接口、启用HPS外设PLL提供参考时钟的FPGA接口

Peripheral FPGA Clocks用于设置HPS外设的时钟频率,但需要先设置HPS外设在FPGA可以(即相应外设的引脚复用选择FPGA)

1.2.3.2 Output Clocks

Clock Sources设置时钟源

Main PLL Output Clocks - Desired Frequencies主锁相环输出时钟-所需频率

Peripheral PLL Output Clocks - Desired frequencies外围锁相环输出时钟-所需频率

HPS-to-FPGA User Clocks,用户时钟

| 参数名称 | 参数描述 |

| Enable HPS-to-FPGA user 0 clock | 启用HPS到FPGA的主PLL |

| Enable HPS-to-FPGA user 1 clock | 启用HPS到FPGA的外设PLL |

| Enable HPS-to-FPGA user 2 clock | 启用HPS到FPGA的SDRAM PLL |

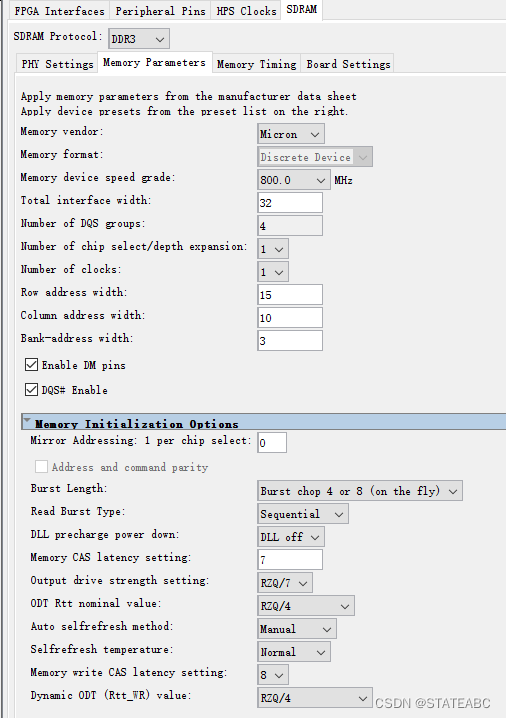

1.2.4 SDRAM

HPS支持DDR2、DDR3、LPDDR2协议的存储器接口

1.2.4.1 PHY Settings

Memory clock frequency设置存储器芯片的时钟频率,依据DDR3芯片手册设置

Supply Voltage电源电压,依据DDR3芯片手册选择

1.2.4.2 Memory Parameters

根据DDR3芯片手册中的参数设置Memory Parameters

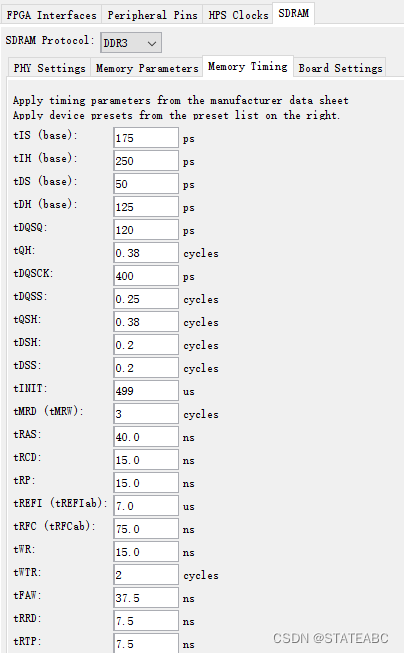

1.2.4.3 Memory Timing

根据DDR3芯片手册中的相关参数验证Memory Timing页面中的时序参数

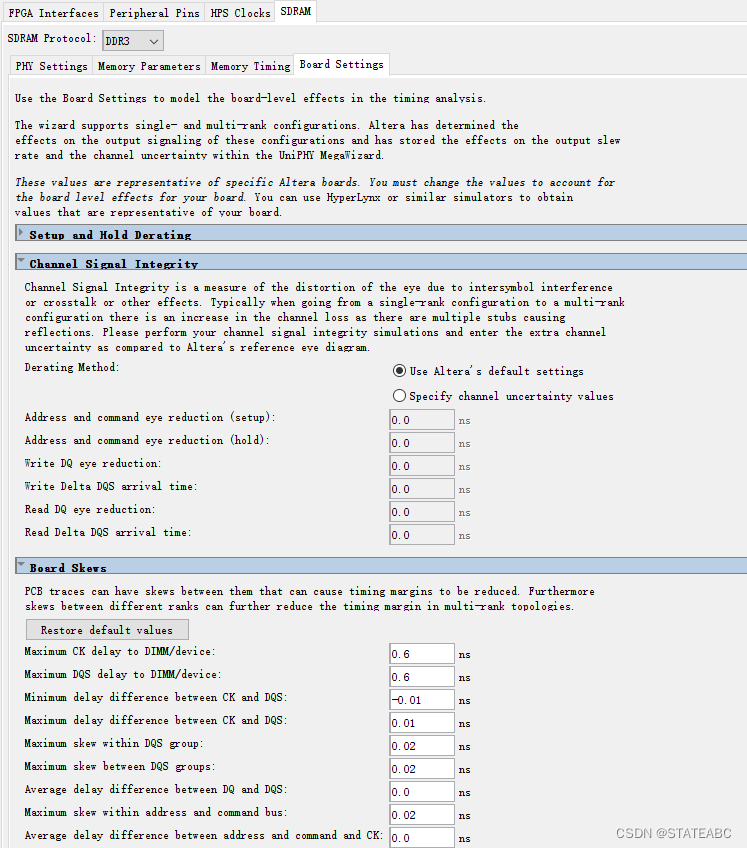

1.2.4.4 Board Settings

Setup and Hold Derating和Intersymbol Interference均可以选择Use Altera's default settings,也可以根据芯片手册中的相关参数进行设置

需要根据开发板参数设置Board Skews,SDRAM利用这些参数校准I/O延时以及FIFO设置来补偿板级、FPGA部分或存储器件的漂移时间

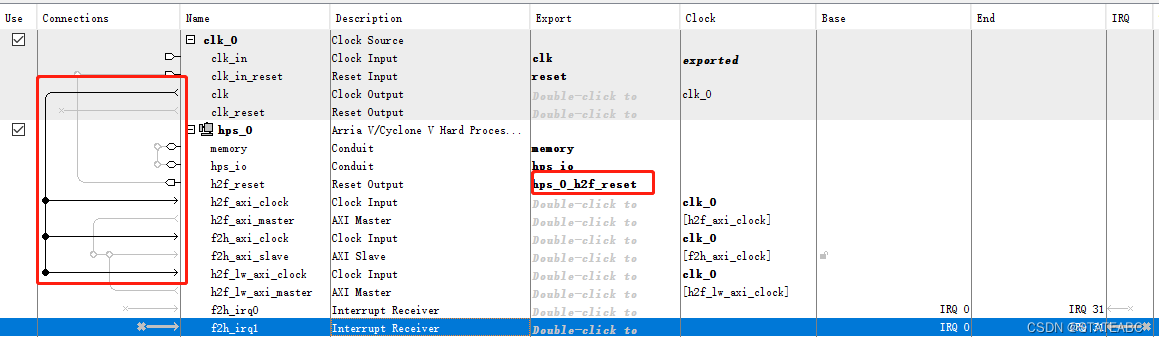

所有设置完成后点击右下角finish,将h2f_reset引出,将三个clock连接clk

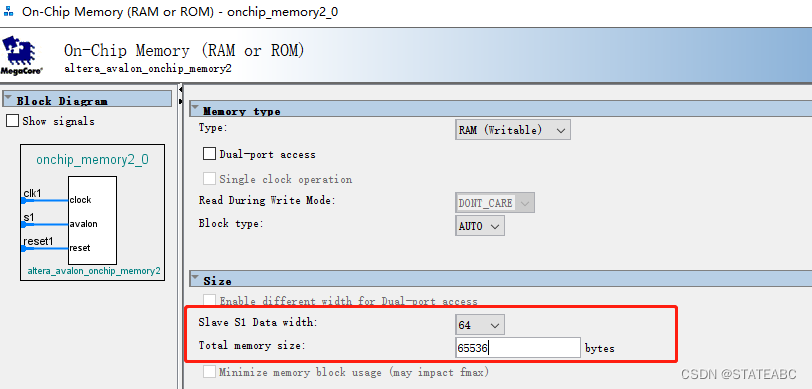

1.3 添加其他组件

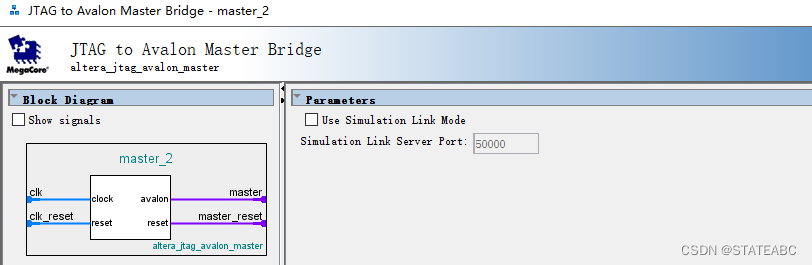

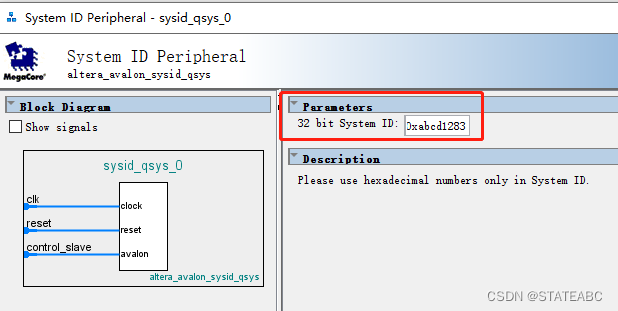

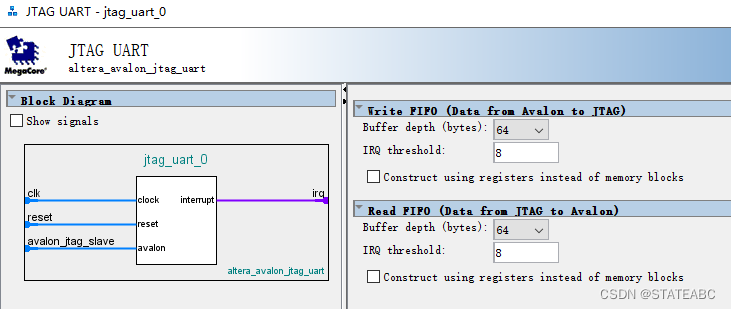

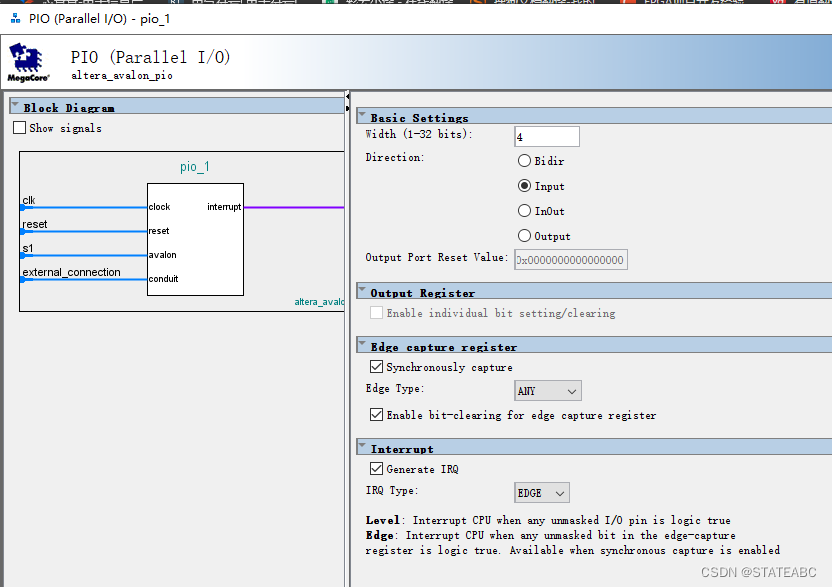

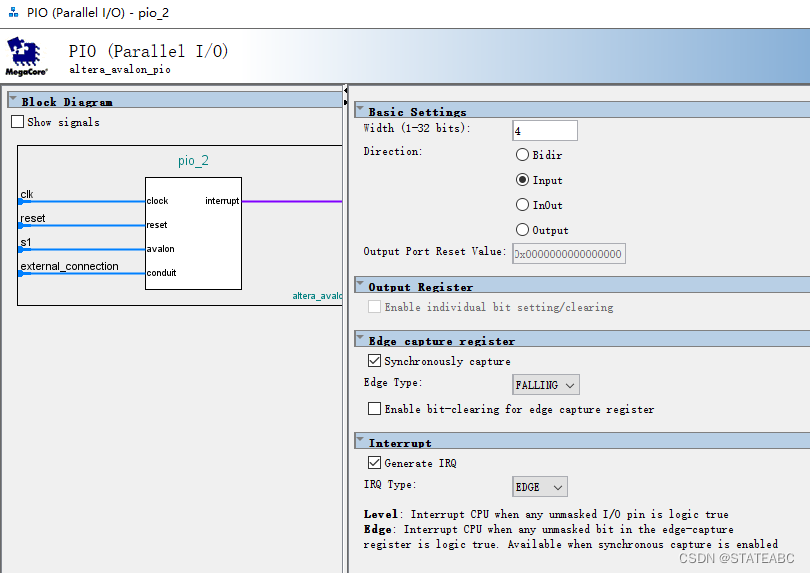

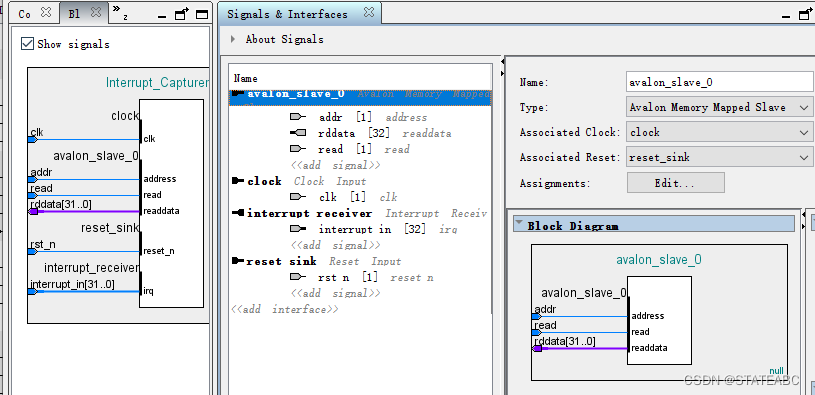

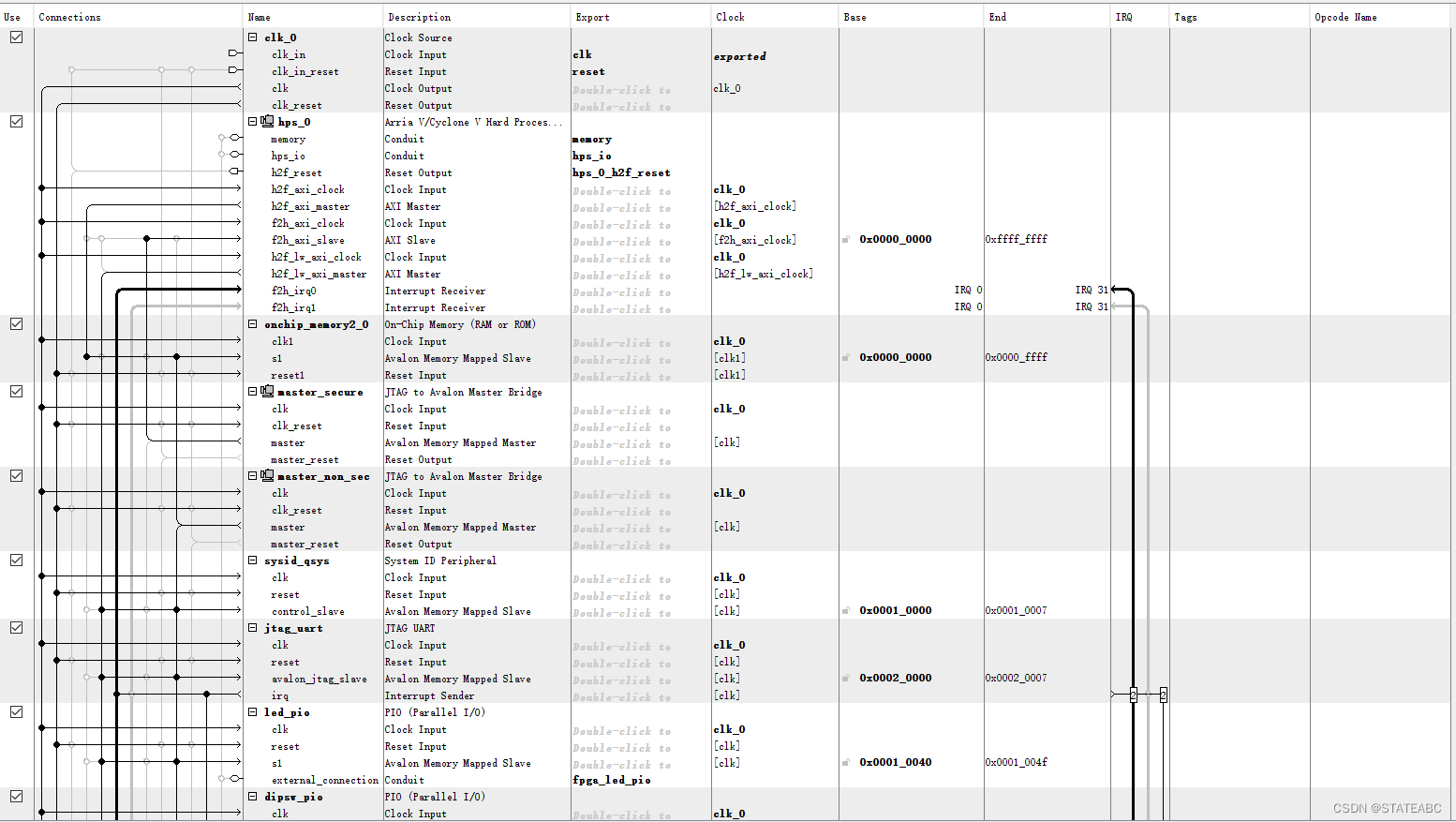

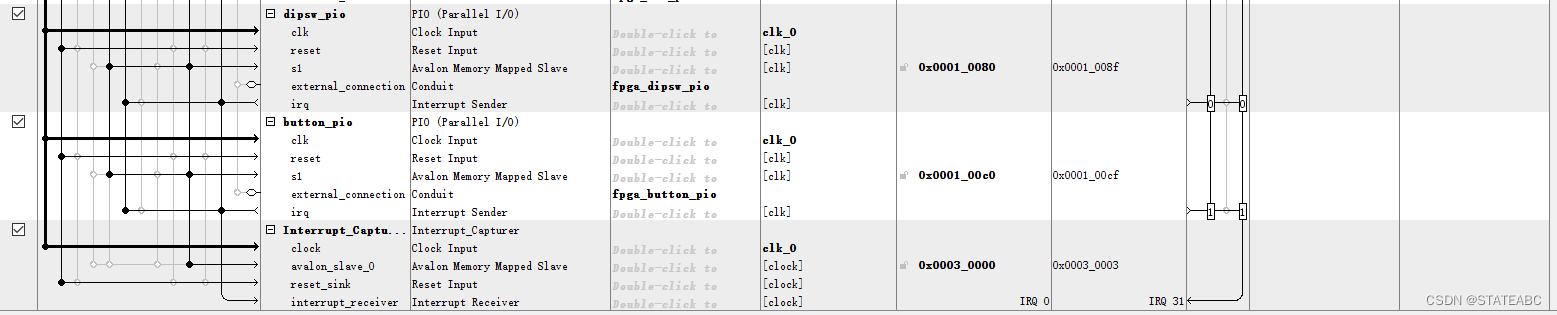

添加On-chip Memory、两个JTAG to Avalon Master Bridge、System ID Peripheral、JTAG UART、LED PIO、拨码开关PIO、按键PIO、自定义中断捕获模块

自定义中断捕获模块

module intr_capturer #(parameter NUM_INTR = 32// active high level interrupt is expected for the input of this capturer module

)(input clk,input rst_n,input [NUM_INTR-1:0] interrupt_in,//input [31:0] wrdata,input addr,input read,output [31:0] rddata

);reg [NUM_INTR-1:0] interrupt_reg;reg [31:0] readdata_with_waitstate;wire [31:0] act_readdata;wire [31:0] readdata_lower_intr;wire [31:0] readdata_higher_intr;wire access_lower_32;wire access_higher_32;always @(posedge clk or negedge rst_n) beginif (!rst_n) interrupt_reg <= 'b0;else interrupt_reg <= interrupt_in;endgenerateif (NUM_INTR>32) begin : two_intr_reg_neededassign access_higher_32 = read & (addr == 1);assign readdata_lower_intr = interrupt_reg[31:0] & {(32){access_lower_32}};assign readdata_higher_intr = interrupt_reg[NUM_INTR-1:32] & {(NUM_INTR-32){access_higher_32}};endelse begin : only_1_regassign readdata_lower_intr = interrupt_reg & {(NUM_INTR){access_lower_32}};assign readdata_higher_intr = {32{1'b0}};endendgenerateassign access_lower_32 = read & (addr == 0);assign act_readdata = readdata_lower_intr | readdata_higher_intr;assign rddata = readdata_with_waitstate;always @(posedge clk or negedge rst_n) beginif (!rst_n) readdata_with_waitstate <= 32'b0;else readdata_with_waitstate <= act_readdata;endendmodule

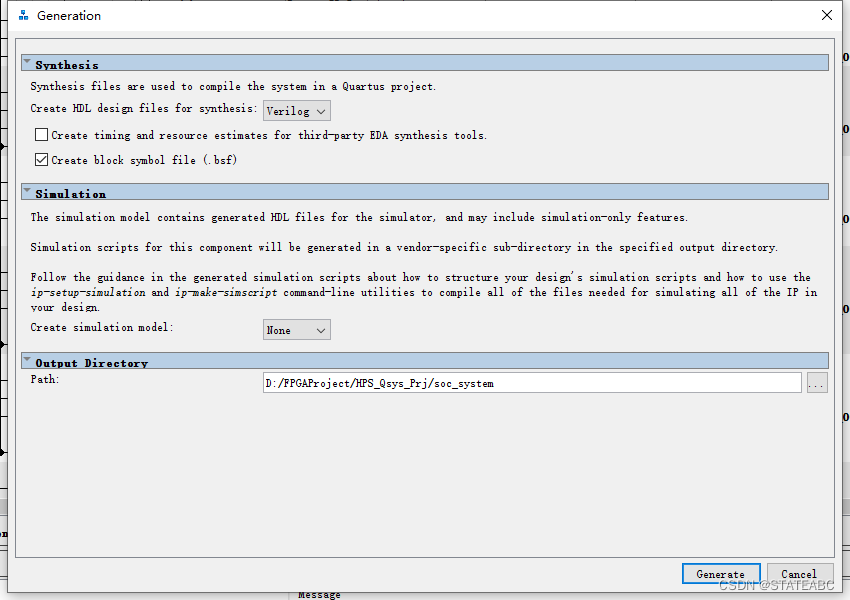

1.4 产生Qsys系统

连线、设置中断、手动分配相应外设的基地址

产生Qsys系统

Qsys将产生指定格式的硬件描述语言(HDL)文件用于Quartus工程编译,同时产生一组与硬件系统定义相关的文件,包括定义了选定的HPS外设默认引脚分配的Tcl(Tool Command Language)文件,定义了HPS与FPGA中多端口存储器控制器的Tcl文件,定义了系统所用IP和用于TimeQuest时序约束的QIP文件,可以在synthesis目录找到。

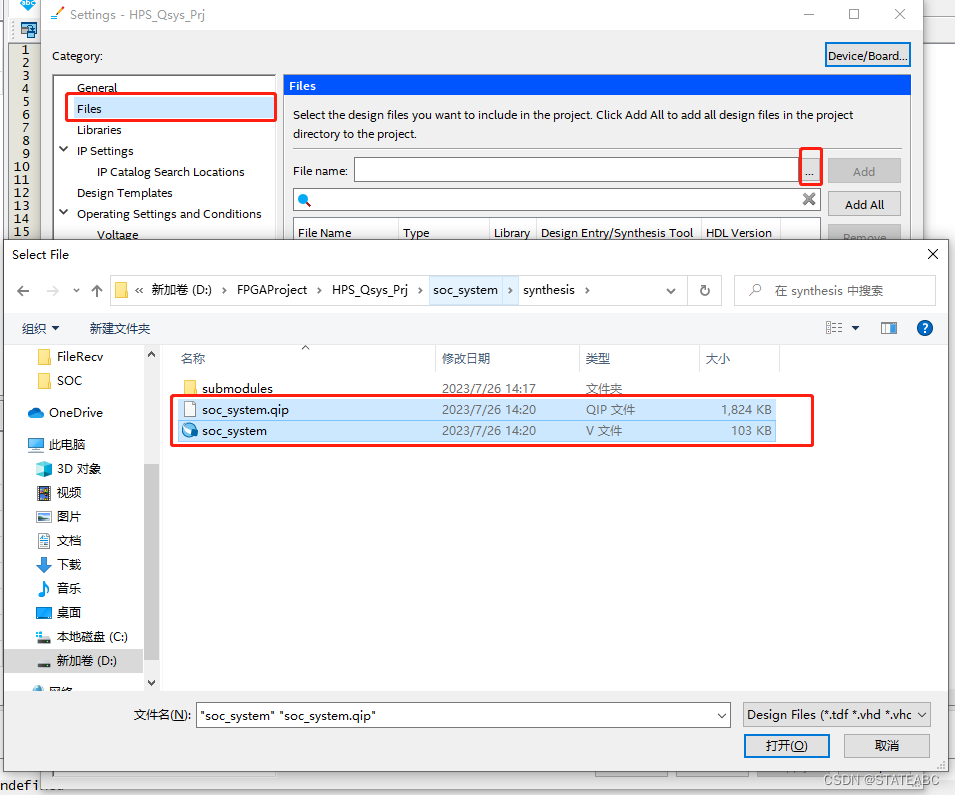

1.5 编译Quartus工程

在Quartus的工程中添加soc_system.qip和soc_system.v文件

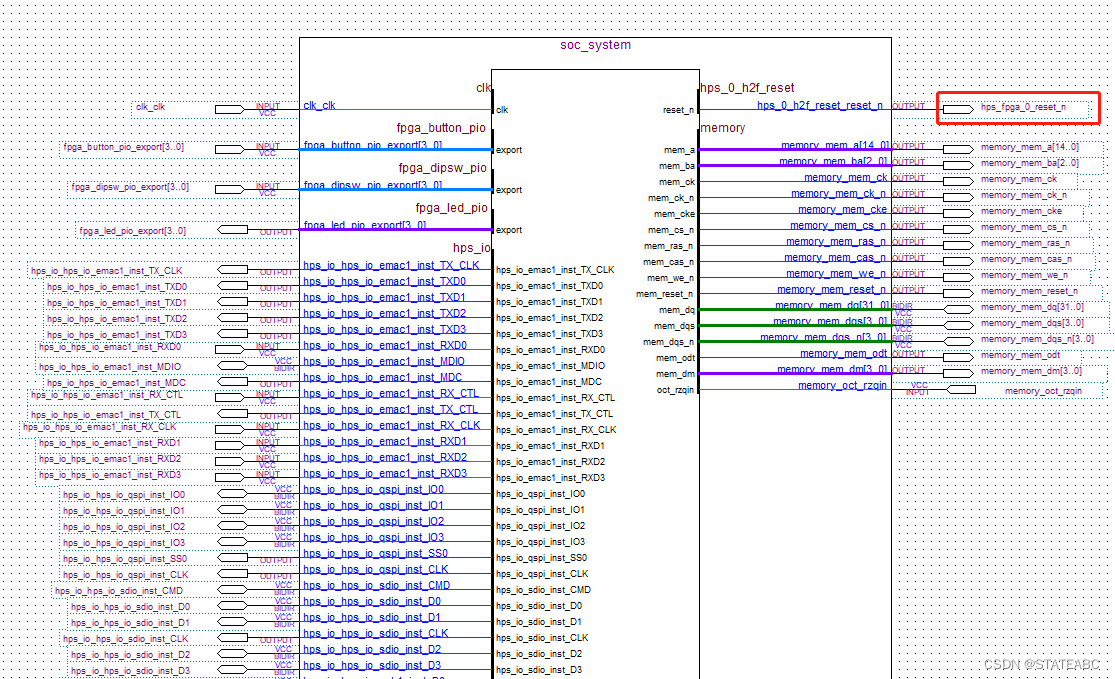

点击工具栏中的File->New->Block Diagram/Schematic File,新建一个原理图文件

再右键点击原理图空白处选择Insert->Symbol,将soc_system添加入原理图文件中,右键点击soc_system->Generate Pins for Symbol Ports,为元件添加输入/输出端口

将两处hps_0_h2f_reset的输出(命名为hps_fpga_reset_n)连接到系统的复位reset信号上,然后保存

添加顶层文件

module HPS_Qsys_prj(

///HPS Interface // input wire reset_reset_n, // reset.reset_n

// input wire clk_clk, // clk.clkoutput wire [14:0] memory_mem_a, // memory.mem_aoutput wire [2:0] memory_mem_ba, // .mem_baoutput wire memory_mem_ck, // .mem_ckoutput wire memory_mem_ck_n, // .mem_ck_noutput wire memory_mem_cke, // .mem_ckeoutput wire memory_mem_cs_n, // .mem_cs_noutput wire memory_mem_ras_n, // .mem_ras_noutput wire memory_mem_cas_n, // .mem_cas_noutput wire memory_mem_we_n, // .mem_we_noutput wire memory_mem_reset_n, // .mem_reset_ninout wire [31:0] memory_mem_dq, // .mem_dqinout wire [3:0] memory_mem_dqs, // .mem_dqsinout wire [3:0] memory_mem_dqs_n, // .mem_dqs_noutput wire memory_mem_odt, // .mem_odtoutput wire [3:0] memory_mem_dm, // .mem_dminput wire memory_oct_rzqin, // .oct_rzqinoutput wire hps_0_hps_io_hps_io_emac1_inst_TX_CLK, // hps_0_hps_io.hps_io_emac1_inst_TX_CLKoutput wire hps_0_hps_io_hps_io_emac1_inst_TXD0, // .hps_io_emac1_inst_TXD0output wire hps_0_hps_io_hps_io_emac1_inst_TXD1, // .hps_io_emac1_inst_TXD1output wire hps_0_hps_io_hps_io_emac1_inst_TXD2, // .hps_io_emac1_inst_TXD2output wire hps_0_hps_io_hps_io_emac1_inst_TXD3, // .hps_io_emac1_inst_TXD3input wire hps_0_hps_io_hps_io_emac1_inst_RXD0, // .hps_io_emac1_inst_RXD0inout wire hps_0_hps_io_hps_io_emac1_inst_MDIO, // .hps_io_emac1_inst_MDIOoutput wire hps_0_hps_io_hps_io_emac1_inst_MDC, // .hps_io_emac1_inst_MDCinput wire hps_0_hps_io_hps_io_emac1_inst_RX_CTL, // .hps_io_emac1_inst_RX_CTLoutput wire hps_0_hps_io_hps_io_emac1_inst_TX_CTL, // .hps_io_emac1_inst_TX_CTLinput wire hps_0_hps_io_hps_io_emac1_inst_RX_CLK, // .hps_io_emac1_inst_RX_CLKinput wire hps_0_hps_io_hps_io_emac1_inst_RXD1, // .hps_io_emac1_inst_RXD1input wire hps_0_hps_io_hps_io_emac1_inst_RXD2, // .hps_io_emac1_inst_RXD2input wire hps_0_hps_io_hps_io_emac1_inst_RXD3, // .hps_io_emac1_inst_RXD3inout wire hps_0_hps_io_hps_io_qspi_inst_IO0, // .hps_io_qspi_inst_IO0inout wire hps_0_hps_io_hps_io_qspi_inst_IO1, // .hps_io_qspi_inst_IO1inout wire hps_0_hps_io_hps_io_qspi_inst_IO2, // .hps_io_qspi_inst_IO2inout wire hps_0_hps_io_hps_io_qspi_inst_IO3, // .hps_io_qspi_inst_IO3output wire hps_0_hps_io_hps_io_qspi_inst_SS0, // .hps_io_qspi_inst_SS0output wire hps_0_hps_io_hps_io_qspi_inst_CLK, // .hps_io_qspi_inst_CLKinout wire hps_0_hps_io_hps_io_sdio_inst_CMD, // .hps_io_sdio_inst_CMDinout wire hps_0_hps_io_hps_io_sdio_inst_D0, // .hps_io_sdio_inst_D0inout wire hps_0_hps_io_hps_io_sdio_inst_D1, // .hps_io_sdio_inst_D1output wire hps_0_hps_io_hps_io_sdio_inst_CLK, // .hps_io_sdio_inst_CLKinout wire hps_0_hps_io_hps_io_sdio_inst_D2, // .hps_io_sdio_inst_D2inout wire hps_0_hps_io_hps_io_sdio_inst_D3, // .hps_io_sdio_inst_D3inout wire hps_0_hps_io_hps_io_usb1_inst_D0, // .hps_io_usb1_inst_D0inout wire hps_0_hps_io_hps_io_usb1_inst_D1, // .hps_io_usb1_inst_D1inout wire hps_0_hps_io_hps_io_usb1_inst_D2, // .hps_io_usb1_inst_D2inout wire hps_0_hps_io_hps_io_usb1_inst_D3, // .hps_io_usb1_inst_D3inout wire hps_0_hps_io_hps_io_usb1_inst_D4, // .hps_io_usb1_inst_D4inout wire hps_0_hps_io_hps_io_usb1_inst_D5, // .hps_io_usb1_inst_D5inout wire hps_0_hps_io_hps_io_usb1_inst_D6, // .hps_io_usb1_inst_D6inout wire hps_0_hps_io_hps_io_usb1_inst_D7, // .hps_io_usb1_inst_D7input wire hps_0_hps_io_hps_io_usb1_inst_CLK, // .hps_io_usb1_inst_CLKoutput wire hps_0_hps_io_hps_io_usb1_inst_STP, // .hps_io_usb1_inst_STPinput wire hps_0_hps_io_hps_io_usb1_inst_DIR, // .hps_io_usb1_inst_DIRinput wire hps_0_hps_io_hps_io_usb1_inst_NXT, // .hps_io_usb1_inst_NXToutput wire hps_0_hps_io_hps_io_spim0_inst_CLK, // .hps_io_spim0_inst_CLKoutput wire hps_0_hps_io_hps_io_spim0_inst_MOSI, // .hps_io_spim0_inst_MOSIinput wire hps_0_hps_io_hps_io_spim0_inst_MISO, // .hps_io_spim0_inst_MISOoutput wire hps_0_hps_io_hps_io_spim0_inst_SS0, // .hps_io_spim0_inst_SS0output wire hps_0_hps_io_hps_io_spim1_inst_CLK, // .hps_io_spim1_inst_CLKoutput wire hps_0_hps_io_hps_io_spim1_inst_MOSI, // .hps_io_spim1_inst_MOSIinput wire hps_0_hps_io_hps_io_spim1_inst_MISO, // .hps_io_spim1_inst_MISOoutput wire hps_0_hps_io_hps_io_spim1_inst_SS0, // .hps_io_spim1_inst_SS0input wire hps_0_hps_io_hps_io_uart0_inst_RX, // .hps_io_uart0_inst_RXoutput wire hps_0_hps_io_hps_io_uart0_inst_TX, // .hps_io_uart0_inst_TXinout wire hps_0_hps_io_hps_io_i2c1_inst_SDA, // .hps_io_i2c1_inst_SDAinout wire hps_0_hps_io_hps_io_i2c1_inst_SCL, // .hps_io_i2c1_inst_SCLinout wire hps_0_hps_io_hps_io_gpio_inst_GPIO0, // .hps_io_gpio_inst_GPIO0inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI1,inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI2,inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI3,inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI4,inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI5,inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI6,inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI7,inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI8,inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI9,inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI10,inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI11,inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI12,inout wire hps_0_hps_io_hps_io_gpio_inst_HLGPI13,inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO09, // .hps_io_gpio_inst_GPIO09inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO35, // .hps_io_gpio_inst_GPIO35inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO48, // .hps_io_gpio_inst_GPIO48inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO53, // .hps_io_gpio_inst_GPIO53inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO54, // .hps_io_gpio_inst_GPIO54inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO55, // .hps_io_gpio_inst_GPIO55inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO56, // .hps_io_gpio_inst_GPIO56inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO61, // .hps_io_gpio_inst_GPIO61inout wire hps_0_hps_io_hps_io_gpio_inst_GPIO62, // .hps_io_gpio_inst_GPIO62FPGA Interface //FPGA-GPLL-CLK------------------------//X pinsinput clk_100m_fpga, //2.5V //100 MHz (2nd copy to max)input clk_50m_fpga, //2.5V //50MHz (2nd copy to max) input clk_top1, //2.5V //156.25 MHz adjustableinput clk_bot1, //1.5V //100 MHz ajustableinput fpga_resetn, //2.5V //FPGA Reset Pushbutton SiLabs Clock Generator I/F /// output wire clk_i2c_sclk, // I2C Clock inout wire clk_i2c_sdat, // I2C Data `ifdef user_peripheral//FPGA-User-IO-------------------------//14 pins //--------------------------input [3:0] user_dipsw_fpga, //output [3:0] user_led_fpga, //input [3:0] user_pb_fpga, //input wire irda_rxd, // IRDA Receive LED output wire fan_ctrl // control for fan

`endif`ifdef ddr3

//FPGA-DDR3-400Mx32--------------------//74 pins //--------------------------output [14:0] ddr3_fpga_a, //SSTL15 //Addressoutput [2:0] ddr3_fpga_ba, //SSTL15 //Bank Addressoutput ddr3_fpga_casn, //SSTL15 //Column Address Strobeoutput ddr3_fpga_cke, //SSTL15 //Clock Enableoutput ddr3_fpga_clk_n, //SSTL15 //Diff Clock - Negoutput ddr3_fpga_clk_p, //SSTL15 //Diff Clock - Posoutput ddr3_fpga_csn, //SSTL15 //Chip Selectoutput [3:0] ddr3_fpga_dm, //SSTL15 //Data Write Maskinout [31:0] ddr3_fpga_dq, //SSTL15 //Data Businout [3:0] ddr3_fpga_dqs_n, //SSTL15 //Diff Data Strobe - Neginout [3:0] ddr3_fpga_dqs_p, //SSTL15 //Diff Data Strobe - Posoutput ddr3_fpga_odt, //SSTL15 //On-Die Termination Enableoutput ddr3_fpga_rasn, //SSTL15 //Row Address Strobeoutput ddr3_fpga_resetn, //SSTL15 //Resetoutput ddr3_fpga_wen, //SSTL15 //Write Enableinput ddr3_fpga_rzq, //OCT_rzqin //On-die termination enable

// input oct_rdn, //SSTL15 //On-die termination enable

// input oct_rup, //SSTL15 //On-die termination enable

`endif`ifdef temp_senseTemp. Sensor I/F // SPI interface //output wire temp_cs_n, // Chip Selectoutput wire temp_sclk, // Slave Clock output wire temp_mosi, // Data Out input wire temp_miso, // Data In

`endif`ifdef vgaVIDEO output wire vga_clk, // Video Clockoutput wire vga_hs, // Horizontal Synchoutput wire vga_vs, // Vertical Synch output wire [7:0] vga_r, // Red output wire [7:0] vga_g, // Greenoutput wire [7:0] vga_b, // Blue output wire vga_blank_n, // Composite Blank Controloutput wire vga_sync_n, // Composite Synch Control

`endif`ifdef audioAUDIO input wire aud_adcdat, // ADC Serial Data or I2C_SCLKinput wire aud_adclrck, // FDDR3e clockinput wire aud_bclk, // Bit Clock output wire aud_dacdat, // DAC Serial Data inout wire aud_daclrck, // FDDR3e Clockoutput wire aud_i2c_sclk, inout wire aud_i2c_sdat, output wire aud_mute, output wire aud_xck,

`endif`ifdef hsma

//HSMC-Port-A----------------------------------------------------

// input [2:1] hsmc_clkin_n, input [2:1] hsmc_clkin_p,

// output [2:1] hsmc_clkout_n, output [2:1] hsmc_clkout_p, input hsmc_clk_in0, output hsmc_clk_out0, inout [3:0] hsmc_d,

`ifdef HSMC_XCVR

// input [7:0] hsmc_gxb_rx_n, input [7:0] hsmc_gxb_rx_p,

// output [7:0] hsmc_gxb_tx_n, output [7:0] hsmc_gxb_tx_p,

// input hsmc_ref_clk_n, input hsmc_ref_clk_p,

`endif

// input [16:0] hsmc_rx_n, input [16:0] hsmc_rx_p, output hsmc_scl, inout hsmc_sda,

// output [16:0] hsmc_tx_n, output [16:0] hsmc_tx_p `endifQSPI Flash I/F /// inout wire [3:0] fpga_epqc_data, // Flash Data output wire fpga_epqc_dclk, // Data Clock output wire fpga_epqc_ncso // Chip Select);// internal wires and registers declarationwire [3:0] fpga_led_internal;wire hps_fpga_reset_n;// connection of internal logics

// assign user_led_fpga = ~fpga_led_internal;assign user_led_fpga = fpga_led_internal;soc_system u0 (.clk_clk (clk_bot1), // clk.clk.fpga_button_pio_export (user_pb_fpga), // fpga_button_pio.export.fpga_dipsw_pio_export (user_dipsw_fpga), // fpga_dipsw_pio.export.fpga_led_pio_export (fpga_led_internal), // fpga_led_pio.export.hps_0_h2f_reset_reset_n (hps_fpga_reset_n), // hps_0_h2f_reset.reset_n.hps_io_hps_io_emac1_inst_TX_CLK (hps_0_hps_io_hps_io_emac1_inst_TX_CLK), // hps_io.hps_io_emac1_inst_TX_CLK.hps_io_hps_io_emac1_inst_TXD0 (hps_0_hps_io_hps_io_emac1_inst_TXD0), // .hps_io_emac1_inst_TXD0.hps_io_hps_io_emac1_inst_TXD1 (hps_0_hps_io_hps_io_emac1_inst_TXD1), // .hps_io_emac1_inst_TXD1.hps_io_hps_io_emac1_inst_TXD2 (hps_0_hps_io_hps_io_emac1_inst_TXD2), // .hps_io_emac1_inst_TXD2.hps_io_hps_io_emac1_inst_TXD3 (hps_0_hps_io_hps_io_emac1_inst_TXD3), // .hps_io_emac1_inst_TXD3.hps_io_hps_io_emac1_inst_RXD0 (hps_0_hps_io_hps_io_emac1_inst_RXD0), // .hps_io_emac1_inst_RXD0.hps_io_hps_io_emac1_inst_MDIO (hps_0_hps_io_hps_io_emac1_inst_MDIO), // .hps_io_emac1_inst_MDIO.hps_io_hps_io_emac1_inst_MDC (hps_0_hps_io_hps_io_emac1_inst_MDC), // .hps_io_emac1_inst_MDC.hps_io_hps_io_emac1_inst_RX_CTL (hps_0_hps_io_hps_io_emac1_inst_RX_CTL), // .hps_io_emac1_inst_RX_CTL.hps_io_hps_io_emac1_inst_TX_CTL (hps_0_hps_io_hps_io_emac1_inst_TX_CTL), // .hps_io_emac1_inst_TX_CTL.hps_io_hps_io_emac1_inst_RX_CLK (hps_0_hps_io_hps_io_emac1_inst_RX_CLK), // .hps_io_emac1_inst_RX_CLK.hps_io_hps_io_emac1_inst_RXD1 (hps_0_hps_io_hps_io_emac1_inst_RXD1), // .hps_io_emac1_inst_RXD1.hps_io_hps_io_emac1_inst_RXD2 (hps_0_hps_io_hps_io_emac1_inst_RXD2), // .hps_io_emac1_inst_RXD2.hps_io_hps_io_emac1_inst_RXD3 (hps_0_hps_io_hps_io_emac1_inst_RXD3), // .hps_io_emac1_inst_RXD3.hps_io_hps_io_qspi_inst_IO0 (hps_0_hps_io_hps_io_qspi_inst_IO0), // .hps_io_qspi_inst_IO0.hps_io_hps_io_qspi_inst_IO1 (hps_0_hps_io_hps_io_qspi_inst_IO1), // .hps_io_qspi_inst_IO1.hps_io_hps_io_qspi_inst_IO2 (hps_0_hps_io_hps_io_qspi_inst_IO2), // .hps_io_qspi_inst_IO2.hps_io_hps_io_qspi_inst_IO3 (hps_0_hps_io_hps_io_qspi_inst_IO3), // .hps_io_qspi_inst_IO3.hps_io_hps_io_qspi_inst_SS0 (hps_0_hps_io_hps_io_qspi_inst_SS0), // .hps_io_qspi_inst_SS0.hps_io_hps_io_qspi_inst_CLK (hps_0_hps_io_hps_io_qspi_inst_CLK), // .hps_io_qspi_inst_CLK.hps_io_hps_io_sdio_inst_CMD (hps_0_hps_io_hps_io_sdio_inst_CMD), // .hps_io_sdio_inst_CMD.hps_io_hps_io_sdio_inst_D0 (hps_0_hps_io_hps_io_sdio_inst_D0), // .hps_io_sdio_inst_D0.hps_io_hps_io_sdio_inst_D1 (hps_0_hps_io_hps_io_sdio_inst_D1), // .hps_io_sdio_inst_D1.hps_io_hps_io_sdio_inst_CLK (hps_0_hps_io_hps_io_sdio_inst_CLK), // .hps_io_sdio_inst_CLK.hps_io_hps_io_sdio_inst_D2 (hps_0_hps_io_hps_io_sdio_inst_D2), // .hps_io_sdio_inst_D2.hps_io_hps_io_sdio_inst_D3 (hps_0_hps_io_hps_io_sdio_inst_D3), // .hps_io_sdio_inst_D3.hps_io_hps_io_usb1_inst_D0 (hps_0_hps_io_hps_io_usb1_inst_D0), // .hps_io_usb1_inst_D0.hps_io_hps_io_usb1_inst_D1 (hps_0_hps_io_hps_io_usb1_inst_D1), // .hps_io_usb1_inst_D1.hps_io_hps_io_usb1_inst_D2 (hps_0_hps_io_hps_io_usb1_inst_D2), // .hps_io_usb1_inst_D2.hps_io_hps_io_usb1_inst_D3 (hps_0_hps_io_hps_io_usb1_inst_D3), // .hps_io_usb1_inst_D3.hps_io_hps_io_usb1_inst_D4 (hps_0_hps_io_hps_io_usb1_inst_D4), // .hps_io_usb1_inst_D4.hps_io_hps_io_usb1_inst_D5 (hps_0_hps_io_hps_io_usb1_inst_D5), // .hps_io_usb1_inst_D5.hps_io_hps_io_usb1_inst_D6 (hps_0_hps_io_hps_io_usb1_inst_D6), // .hps_io_usb1_inst_D6.hps_io_hps_io_usb1_inst_D7 (hps_0_hps_io_hps_io_usb1_inst_D7), // .hps_io_usb1_inst_D7.hps_io_hps_io_usb1_inst_STP (hps_0_hps_io_hps_io_usb1_inst_STP), // .hps_io_usb1_inst_STP.hps_io_hps_io_usb1_inst_DIR (hps_0_hps_io_hps_io_usb1_inst_DIR), // .hps_io_usb1_inst_DIR.hps_io_hps_io_usb1_inst_NXT (hps_0_hps_io_hps_io_usb1_inst_NXT), // .hps_io_usb1_inst_NXT.hps_io_hps_io_spim0_inst_CLK (hps_0_hps_io_hps_io_spim0_inst_CLK), // .hps_io_spim0_inst_CLK.hps_io_hps_io_spim0_inst_MOSI (hps_0_hps_io_hps_io_spim0_inst_MOSI), // .hps_io_spim0_inst_MOSI.hps_io_hps_io_spim0_inst_MISO (hps_0_hps_io_hps_io_spim0_inst_MISO), // .hps_io_spim0_inst_MISO.hps_io_hps_io_spim0_inst_SS0 (hps_0_hps_io_hps_io_spim0_inst_SS0), // .hps_io_spim0_inst_SS0.hps_io_hps_io_spim1_inst_CLK (hps_0_hps_io_hps_io_spim1_inst_CLK), // .hps_io_spim1_inst_CLK.hps_io_hps_io_spim1_inst_MOSI (hps_0_hps_io_hps_io_spim1_inst_MOSI), // .hps_io_spim1_inst_MOSI.hps_io_hps_io_spim1_inst_MISO (hps_0_hps_io_hps_io_spim1_inst_MISO), // .hps_io_spim1_inst_MISO.hps_io_hps_io_spim1_inst_SS0 (hps_0_hps_io_hps_io_spim1_inst_SS0), // .hps_io_spim1_inst_SS0.hps_io_hps_io_uart0_inst_RX (hps_0_hps_io_hps_io_uart0_inst_RX), // .hps_io_uart0_inst_RX.hps_io_hps_io_uart0_inst_TX (hps_0_hps_io_hps_io_uart0_inst_TX), // .hps_io_uart0_inst_TX.hps_io_hps_io_i2c1_inst_SDA (hps_0_hps_io_hps_io_i2c1_inst_SDA), // .hps_io_i2c1_inst_SDA.hps_io_hps_io_i2c1_inst_SCL (hps_0_hps_io_hps_io_i2c1_inst_SCL), // .hps_io_i2c1_inst_SCL.hps_io_hps_io_gpio_inst_HLGPI0 (hps_0_hps_io_hps_io_gpio_inst_GPIO0), // .hps_io_gpio_inst_HLGPI0.hps_io_hps_io_gpio_inst_HLGPI1 (hps_0_hps_io_hps_io_gpio_inst_HLGPI1), // .hps_io_gpio_inst_HLGPI1.hps_io_hps_io_gpio_inst_HLGPI2 (hps_0_hps_io_hps_io_gpio_inst_HLGPI2), // .hps_io_gpio_inst_HLGPI2.hps_io_hps_io_gpio_inst_HLGPI3 (hps_0_hps_io_hps_io_gpio_inst_HLGPI3), // .hps_io_gpio_inst_HLGPI3.hps_io_hps_io_gpio_inst_HLGPI4 (hps_0_hps_io_hps_io_gpio_inst_HLGPI4), // .hps_io_gpio_inst_HLGPI4.hps_io_hps_io_gpio_inst_HLGPI5 (hps_0_hps_io_hps_io_gpio_inst_HLGPI5), // .hps_io_gpio_inst_HLGPI5.hps_io_hps_io_gpio_inst_HLGPI6 (hps_0_hps_io_hps_io_gpio_inst_HLGPI6), // .hps_io_gpio_inst_HLGPI6.hps_io_hps_io_gpio_inst_HLGPI7 (hps_0_hps_io_hps_io_gpio_inst_HLGPI7), // .hps_io_gpio_inst_HLGPI7.hps_io_hps_io_gpio_inst_HLGPI8 (hps_0_hps_io_hps_io_gpio_inst_HLGPI8), // .hps_io_gpio_inst_HLGPI8.hps_io_hps_io_gpio_inst_HLGPI9 (hps_0_hps_io_hps_io_gpio_inst_HLGPI9), // .hps_io_gpio_inst_HLGPI9.hps_io_hps_io_gpio_inst_HLGPI10 (hps_0_hps_io_hps_io_gpio_inst_HLGPI10), // .hps_io_gpio_inst_HLGPI10.hps_io_hps_io_gpio_inst_HLGPI11 (hps_0_hps_io_hps_io_gpio_inst_HLGPI11), // .hps_io_gpio_inst_HLGPI11.hps_io_hps_io_gpio_inst_HLGPI12 (hps_0_hps_io_hps_io_gpio_inst_HLGPI12), // .hps_io_gpio_inst_HLGPI12.hps_io_hps_io_gpio_inst_HLGPI13 (hps_0_hps_io_hps_io_gpio_inst_HLGPI13), // .hps_io_gpio_inst_HLGPI13.hps_io_hps_io_gpio_inst_GPIO09 (hps_0_hps_io_hps_io_gpio_inst_GPIO09), // .hps_io_gpio_inst_GPIO09.memory_mem_a (memory_mem_a), // memory.mem_a.memory_mem_ba (memory_mem_ba), // .mem_ba.memory_mem_ck (memory_mem_ck), // .mem_ck.memory_mem_ck_n (memory_mem_ck_n), // .mem_ck_n.memory_mem_cke (memory_mem_cke), // .mem_cke.memory_mem_cs_n (memory_mem_cs_n), // .mem_cs_n.memory_mem_ras_n (memory_mem_ras_n), // .mem_ras_n.memory_mem_cas_n (memory_mem_cas_n), // .mem_cas_n.memory_mem_we_n (memory_mem_we_n), // .mem_we_n.memory_mem_reset_n (memory_mem_reset_n), // .mem_reset_n.memory_mem_dq (memory_mem_dq), // .mem_dq.memory_mem_dqs (memory_mem_dqs), // .mem_dqs.memory_mem_dqs_n (memory_mem_dqs_n), // .mem_dqs_n.memory_mem_odt (memory_mem_odt), // .mem_odt.memory_mem_dm (memory_mem_dm), // .mem_dm.memory_oct_rzqin (memory_oct_rzqin), // .oct_rzqin.reset_reset_n (hps_fpga_reset_n) // reset.reset_n);endmodule

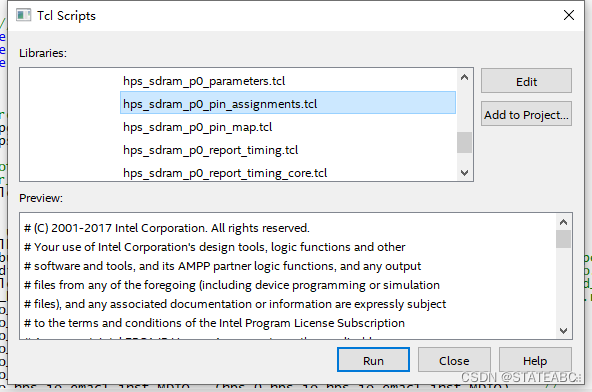

对工程文件进行分析综合

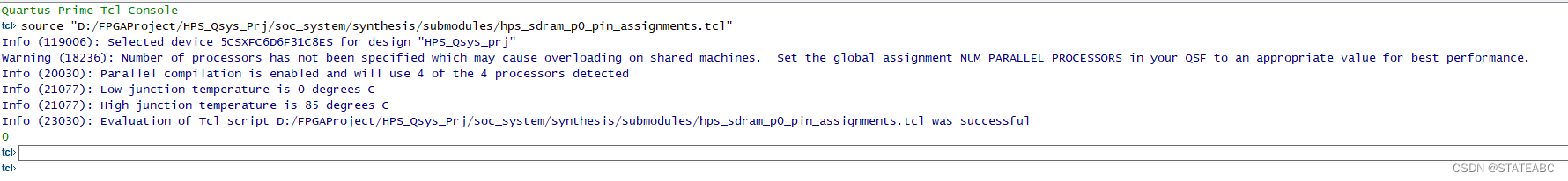

由于系统中的HPS是在Qsys集成工具中例化得到,因此除了所使用的外部存储器引脚以外,其他的专用引脚不需要再Quartus中进行分配,而是在HSP例化过程中由Qsys自动完成HPS的引脚分配,并把相关信息保存在XML格式的文件中提供给软件开发工具使用。但是HPS的外部存储器引脚需要在Quartus中进行引脚分配,该引脚分配信息同样保存在Tcl脚本文件中,只需要执行该脚本文件即可。

Tool->Tcl Scripts->hps_sdram_p0_pin_assignments.tcl->run

执行完后可以在Tcl Console总查看执行结果

最后进行外设引脚分配、工程编译产生.sof文件、下载到FPGA开发板上,整个硬件平台建立完毕

1.6 硬件系统外设的输入/输出测试

系统控制台(Syetem Console)是一种硬件调试工具,通过Tcl脚本命令可以对Qsys中定制的FPGA部分的外设进行测试。在Syetem Console中通过执行Tcl命令可以读取输入PIO寄存器的状态,也可以向输出PIO寄存器写入需要输出的结果

1.7 相关代码

基于Qsys的HPS模型设计资源-CSDN文库

参考文献:

基于FPGA的嵌入式系统设计—Altera Soc FPGA

Cyclone V SoC FPGA和 Arria V SoC FPGA设计指南概述 (intel.cn)

Cyclone V SoC GSRD | Documentation | RocketBoards.org

相关文章:

SOC FPGA之HPS模型设计(一)

目录 一、建立HPS硬件系统模型 1.1 GHRD 1.2 从0开始搭建HPS 1.2.1 FPGA Interfaces 1.2.1.1 General 1.2.1.2 AXI Bridge 1.2.1.3 FPGA-to-HPS SDRAM Interface 1.2.1.4 DMA Peripheral Request 1.2.1.5 Interrupts 1.2.1.6 EMAC ptp interface 1.2.2 Peripheral P…...

解决openstack重启swift服务后报错

swift重启报错 问题描述解决办法 问题描述 swift服务正常状态如下 [rootcontroller ~]# swift statAccount: AUTH_8bde12ff804e42498661b7454994c446Containers: 0Objects: 0Bytes: 0X-Put-Timestamp: 1690507907.67931X-Timestamp: 1690507907.67931X-Trans-Id: tx56d22fa13…...

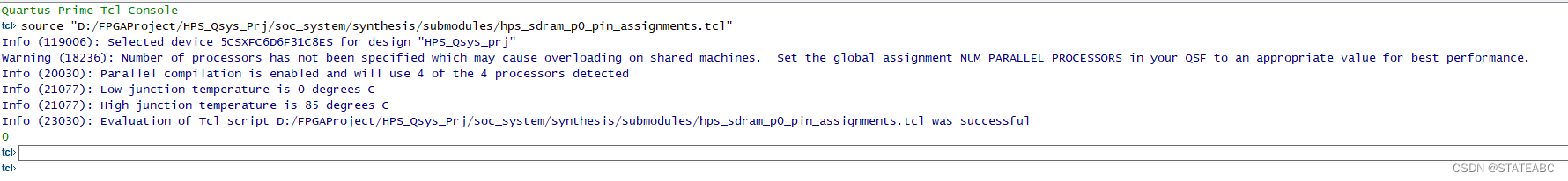

[Linux]进程控制详解!!(创建、终止、等待、替换)

hello,大家好,这里是bang___bang_,在上两篇中我们讲解了进程的概念、状态和进程地址空间,本篇讲解进程的控制!!包含内容有进程创建、进程等待、进程替换、进程终止!! 附上前2篇文章…...

全面适配 | 走近openGauss数据库+鲲鹏欧拉操作系统

引入 全面适配 | openEuler操作系统 openGauss数据库 开篇 1、openEuler欧拉操作系统 百度百科:openEuler是覆盖全场景的创新平台,在引领内核创新,夯实云化基座的基础上,面向计算架构互联总线、存储介质发展新趋势,…...

2023Robocom CAIP省赛 第四题 相对论大师

原题链接: PTA | 程序设计类实验辅助教学平台 题面: 在某个直播间里,观众常常会发送类似这样的弹幕: 鱼越大,鱼刺越大;鱼刺越大,肉越少;肉越少,鱼越小;所以鱼…...

【TypeScript】TS入门级基础学习(一)

【TypeScript】TS入门级基础学习(一) 一、前言 TypeScript 是一种用于应用程序规模的 JavaScript 语言。 TypeScript 向 JavaScript 添加了可选类型,支持用于任何浏览器、任何主机、任何操作系统的大规模 JavaScript 应用程序的工具。 Type…...

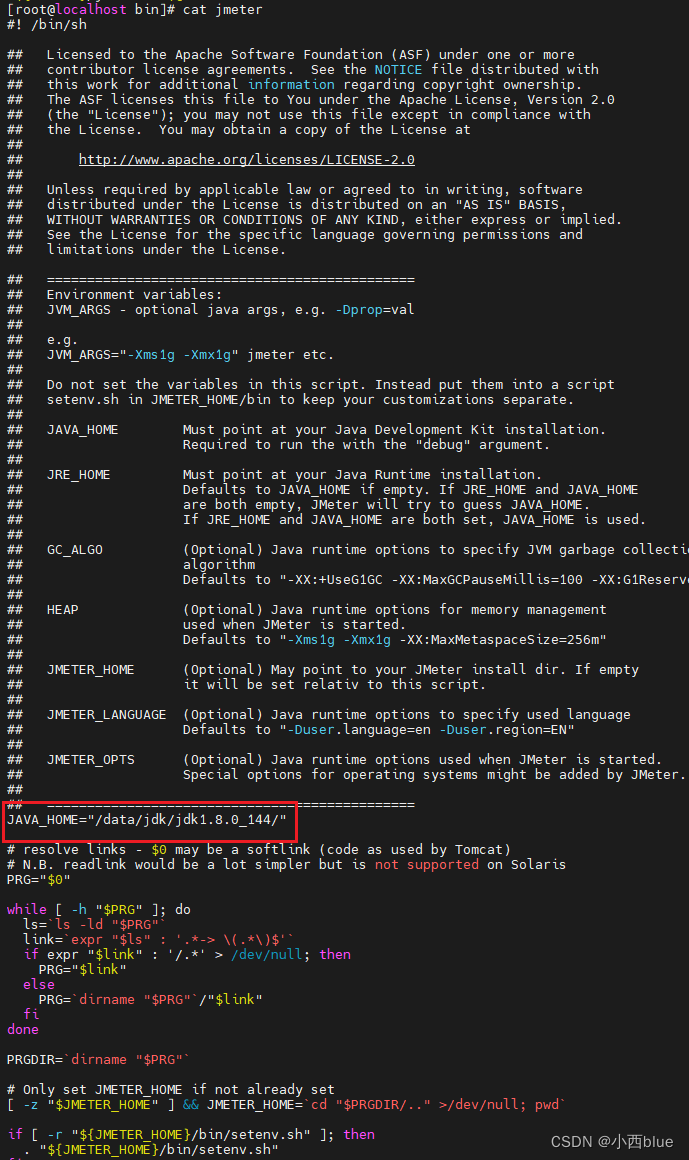

jenkins执行jmeter时,报Begin size 1 is not equal to fixed size 5

jenkins执行jmeter脚本的时候一直提示如下错误: Tidying up ... Fri Jul 28 17:03:53 CST 2023 (1690535033178) Error generating the report: org.apache.jmeter.report.dashboard.GenerationException: Error while processing samples: Consumer failed wi…...

在 “小小容器” WasmEdge 里运行小小羊驼 llama 2

昨天,特斯拉前 AI 总监、OpenAI 联合创始人 Andrej Karpathy 开源了 llama2.c 。 只用 500 行纯 C 语言就能训练和推理 llama 2 模型的框架,没有任何繁杂的 python 依赖。这个项目一推出就受到大家的追捧,24 小时内 GitHub 收获 4000 颗星&am…...

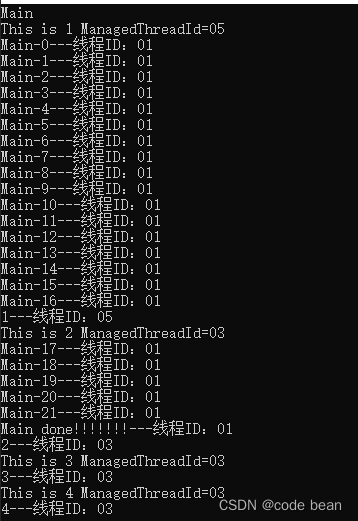

【C#】async和await 续

前言 在文章《async和await》中,我们观察到了一下客观的规律,但是没有讲到本质,而且还遗留了一个问题: 这篇文章中,我们继续看看这个问题如何解决! 我们再看看之前写的代码: static public void TestWait2() {var t…...

)

【Matlab】基于粒子群优化算法优化BP神经网络的数据回归预测(Excel可直接替换数据)

【Matlab】基于粒子群优化算法优化 BP 神经网络的数据回归预测(Excel可直接替换数据) 1.模型原理2.数学公式3.文件结构4.Excel数据5.分块代码5.1 fun.m5.2 main.m6.完整代码6.1 fun.m6.2 main.m7.运行结果1.模型原理 基于粒子群优化算法(Particle Swarm Optimization, PSO)…...

QPainter绘制雷达界面

文章目录 功能实现定义的结构体定义的函数效果图gitee源码链接 功能实现 相较于上一版,这一版添加的功能有: 1、自适应窗口 2、扫描方式(圆周扫描、扇形扫描(指定起始角度和结束角度)) 3、扫描方向&#x…...

flutter:BottomNavigationBar和TabBar

区别 BottomNavigationBarr和TabBar都是用于创建导航栏的组件,但它们有一些区别。 位置不同:BottomNavigationBar通常位于屏幕底部,用于主要导航;而TabBar通常位于屏幕顶部或底部,用于切换不同的视图或页面。 样式不…...

【图论】Prim算法

一.介绍 Prim算法是一种用于解决最小生成树问题的贪心算法。最小生成树问题是指在一个连通无向图中找到一个生成树,使得树中所有边的权重之和最小。 Prim算法的基本思想是从一个起始顶点开始,逐步扩展生成树,直到覆盖所有顶点。具体步骤如下…...

第九十二回 在Flutter中解析JSON数据

文章目录 概念介绍解析方法convert库插件工具 示例代码经验总结 我们在上一章回中介绍了"对dio库进行封装"相关的内容,本章回中将介绍 如何在Flutter中解析JSON数据.闲话休提,让我们一起Talk Flutter吧。 概念介绍 我们在前面章回中介绍了通…...

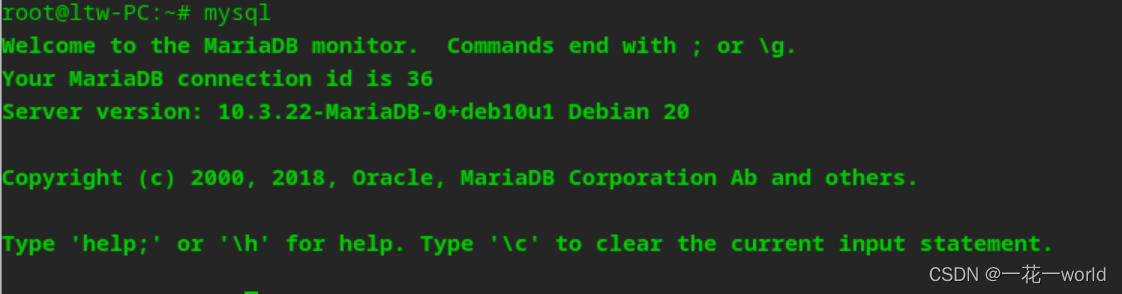

银河麒麟安装mysql数据库(mariadb)-银河麒麟安装JDK-银河麒麟安装nginx(附安装包)

银河麒麟离线全套安装教程(手把手教程) 1.银河麒麟服务器系统安装mysql数据库(mariadb) 2.银河麒麟桌面系统安装mysql数据库(mariadb) 3.银河麒麟服务器系统安装JDK 4.银河麒麟桌面系统安装JDK 5.银河麒麟…...

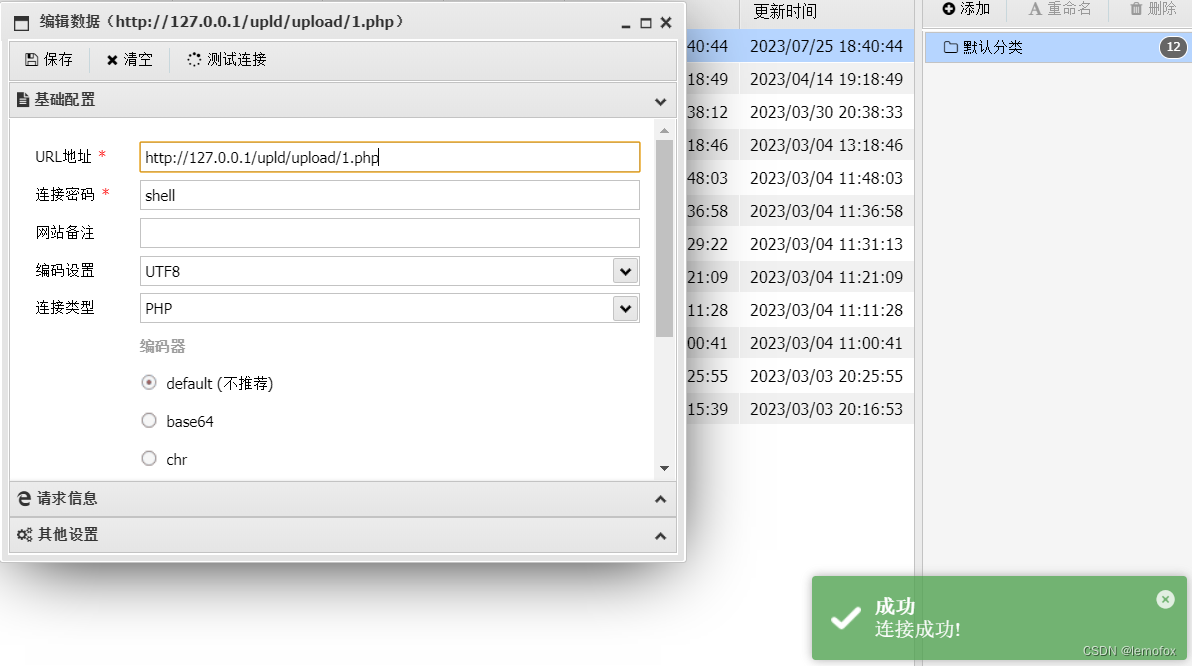

文件上传

js绕过 打开网页尝试上传一句话木马,发现只能上传图片文件 审计源代码,发现使用一个checkfile函数js对文件类型进行了屏蔽 于是我们修改网页代码,去除返回值的检查函数 checkFile() 上传成功,使用蚁剑连接 连接成功 .htaccess绕…...

tinkerCAD案例:22. Backpack Zipper Pull 背包拉链头

tinkerCAD案例:21. Custom Stamp 定制印章 原文 tinkerCAD案例:22. Backpack Zipper Pull 背包拉链头 Lesson Overview: 课程概述: Now we’re going to make a zipper pull! 现在我们要做一个拉链头! Your backpack, howev…...

Unity 性能优化四:UI耗时函数、资源加载、卸载API

UI耗时函数 1.1 Canvas.SendWillRenderCanvases 这个函数是由于自身UI的更新,产生的耗时 1. 这里更新的是vertex 属性,比如 color、tangent、position、uv,修改recttransform的position、scale,rotation并不会导致顶点属性改变…...

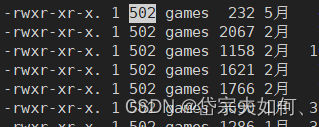

【Linux】用户相关内容

如果命令ll 出现以上信息,UID为具体的数字,代表之前UID为502的用户被删除了。 更改目录或文件所属用户和所属组 在Linux中,创建一个文件时,该文件的拥有者都是创建该文件的用户。 更改所属用户 chown 用户名 文件名/目录名 更…...

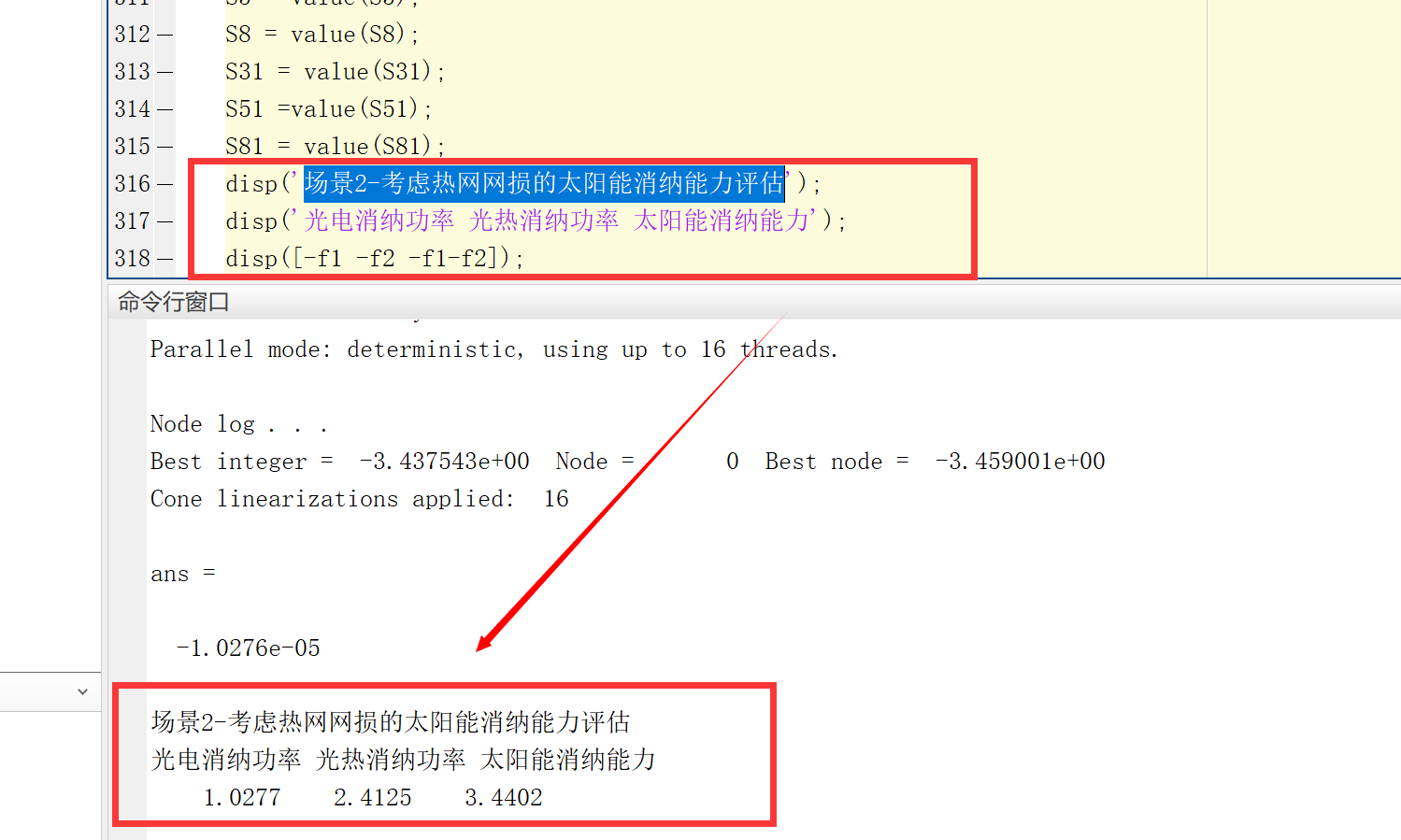

基于多场景的考虑虑热网网损的太阳能消纳能力评估研究(Matlab代码实现)

💥💥💞💞欢迎来到本博客❤️❤️💥💥 🏆博主优势:🌞🌞🌞博客内容尽量做到思维缜密,逻辑清晰,为了方便读者。 ⛳️座右铭&a…...

大数据零基础学习day1之环境准备和大数据初步理解

学习大数据会使用到多台Linux服务器。 一、环境准备 1、VMware 基于VMware构建Linux虚拟机 是大数据从业者或者IT从业者的必备技能之一也是成本低廉的方案 所以VMware虚拟机方案是必须要学习的。 (1)设置网关 打开VMware虚拟机,点击编辑…...

(转)什么是DockerCompose?它有什么作用?

一、什么是DockerCompose? DockerCompose可以基于Compose文件帮我们快速的部署分布式应用,而无需手动一个个创建和运行容器。 Compose文件是一个文本文件,通过指令定义集群中的每个容器如何运行。 DockerCompose就是把DockerFile转换成指令去运行。 …...

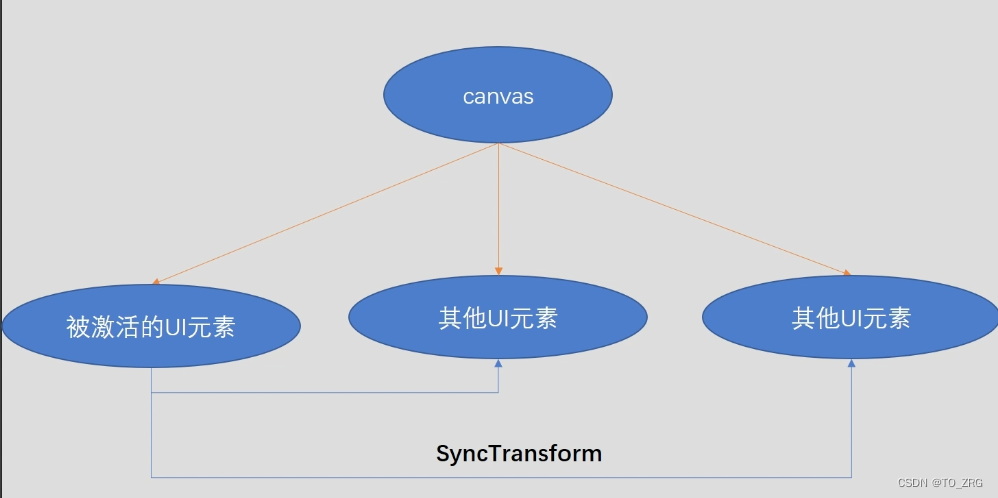

Unity UGUI Button事件流程

场景结构 测试代码 public class TestBtn : MonoBehaviour {void Start(){var btn GetComponent<Button>();btn.onClick.AddListener(OnClick);}private void OnClick(){Debug.Log("666");}}当添加事件时 // 实例化一个ButtonClickedEvent的事件 [Formerl…...

适应性Java用于现代 API:REST、GraphQL 和事件驱动

在快速发展的软件开发领域,REST、GraphQL 和事件驱动架构等新的 API 标准对于构建可扩展、高效的系统至关重要。Java 在现代 API 方面以其在企业应用中的稳定性而闻名,不断适应这些现代范式的需求。随着不断发展的生态系统,Java 在现代 API 方…...

小木的算法日记-多叉树的递归/层序遍历

🌲 从二叉树到森林:一文彻底搞懂多叉树遍历的艺术 🚀 引言 你好,未来的算法大神! 在数据结构的世界里,“树”无疑是最核心、最迷人的概念之一。我们中的大多数人都是从 二叉树 开始入门的,它…...

xmind转换为markdown

文章目录 解锁思维导图新姿势:将XMind转为结构化Markdown 一、认识Xmind结构二、核心转换流程详解1.解压XMind文件(ZIP处理)2.解析JSON数据结构3:递归转换树形结构4:Markdown层级生成逻辑 三、完整代码 解锁思维导图新…...

ThreadLocal 源码

ThreadLocal 源码 此类提供线程局部变量。这些变量不同于它们的普通对应物,因为每个访问一个线程局部变量的线程(通过其 get 或 set 方法)都有自己独立初始化的变量副本。ThreadLocal 实例通常是类中的私有静态字段,这些类希望将…...

Axure零基础跟我学:展开与收回

亲爱的小伙伴,如有帮助请订阅专栏!跟着老师每课一练,系统学习Axure交互设计课程! Axure产品经理精品视频课https://edu.csdn.net/course/detail/40420 课程主题:Axure菜单展开与收回 课程视频:...

C#中用于控制自定义特性(Attribute)

我们来详细解释一下 [AttributeUsage(AttributeTargets.Class, AllowMultiple false, Inherited false)] 这个 C# 属性。 在 C# 中,Attribute(特性)是一种用于向程序元素(如类、方法、属性等)添加元数据的机制。Attr…...

Server - 使用 Docker 配置 PyTorch 研发环境

欢迎关注我的CSDN:https://spike.blog.csdn.net/ 本文地址:https://spike.blog.csdn.net/article/details/148421901 免责声明:本文来源于个人知识与公开资料,仅用于学术交流,欢迎讨论,不支持转载。 建议使…...