Verilog零基础入门(边看边练与测试仿真)-状态机-笔记(7-10讲)

文章目录

- 第七讲

- 第八讲

- 第九讲

- 第十讲

第七讲

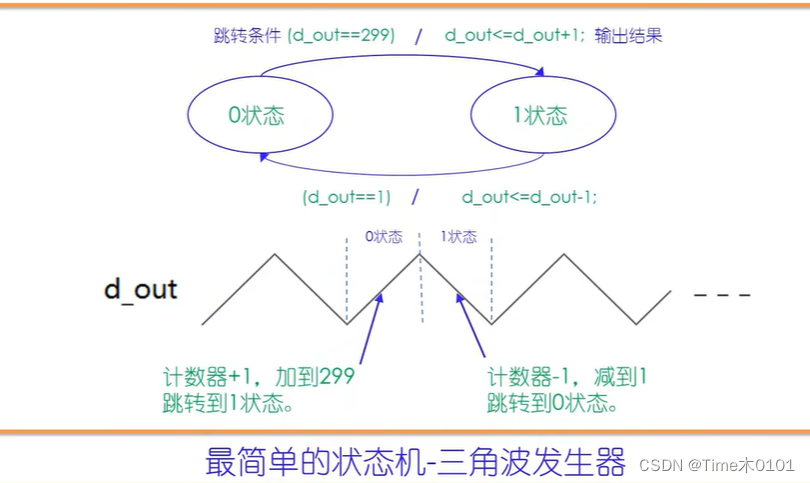

1、最简单的状态机-三角波发生器

1、两种状态的代码:

//最简单的状态机,三角波发生器;

`timescale 1ns/10ps

module tri_gen(clk,res,d_out);

input clk;

input res;

output[8:0] d_out;reg state;//主状态机寄存器

reg[8:0] d_out;always@(posedge clk or negedge res )

if(~res)beginstate<=0;d_out<=0;

end

else begincase(state)0://上升;begind_out<=d_out+1;if(d_out==299)beginstate<=1;endend1://下降begind_out<=d_out-1;if(d_out==1)beginstate<=0;endend endcase

endendmodule//---------testbench of tri_gen-----

module tri_gen_tb;

reg clk,res;

wire[8:0] d_out;

tri_gen U1(.clk(clk),.res(res),.d_out(d_out));initial beginclk<=0;res<=0;#17 res<=1;#8000 $stop;

endalways #5 clk<=~clk;

endmodule

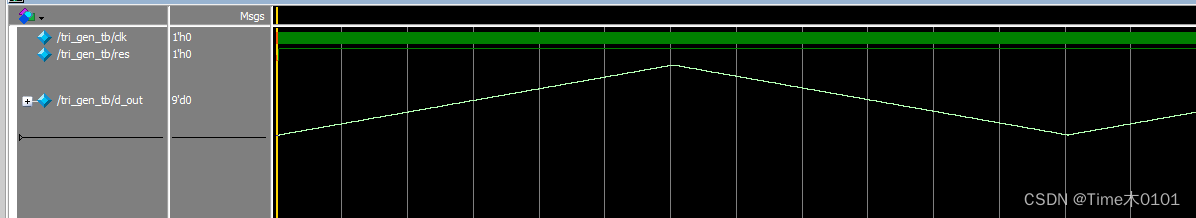

仿真结果:

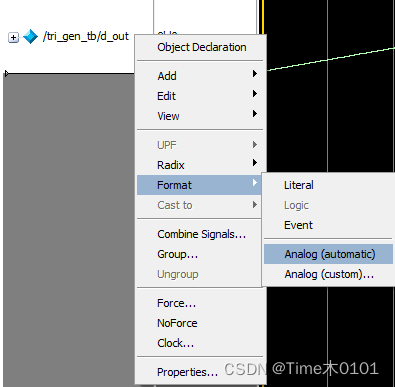

另一种波形查看方法

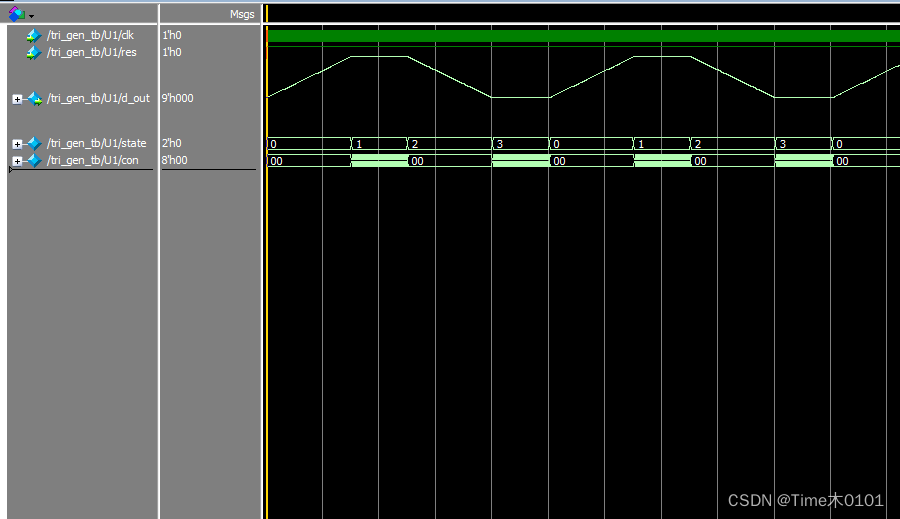

2、四种状态的代码

//2023-0913,time

//最简单的状态机,三角波发生器;

`timescale 1ns/10ps

module tri_gen(clk,res,d_out);

input clk;

input res;

output[8:0] d_out;reg[1:0] state;//主状态机寄存器

reg[8:0] d_out;reg[7:0] con;//计数器,记录平顶周期个数always@(posedge clk or negedge res )

if(~res)beginstate<=0;d_out<=0;con<=0;

end

else begincase(state)0://上升;begind_out<=d_out+1;if(d_out==299)beginstate<=1;endend1://平顶beginif(con==200)beginstate<=2;con<=0;endelse begincon<=con+1;end end2://下降begind_out<=d_out-1;if(d_out==1)beginstate<=3;endend 3://平顶beginif(con==200)beginstate<=0;con<=0;endelse begincon<=con+1;end endendcase

endendmodule//---------testbench of tri_gen-----

module tri_gen_tb;

reg clk,res;

wire[8:0] d_out;

tri_gen U1(.clk(clk),.res(res),.d_out(d_out));initial beginclk<=0;res<=0;#17 res<=1;#40000 $stop;

endalways #5 clk<=~clk;

endmodule

仿真波形:

3、如果state定义的[1:0],也就是有四种状态,那么如果有没用到的状态,应该用default写完全。

第八讲

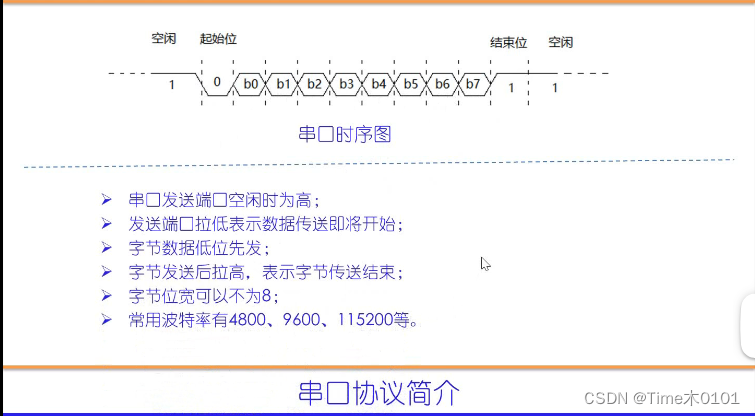

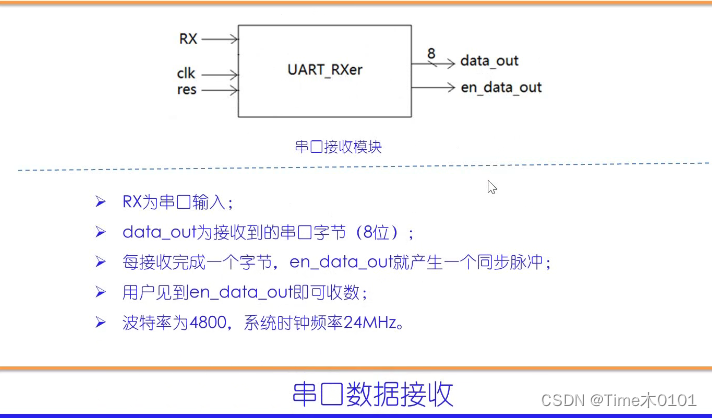

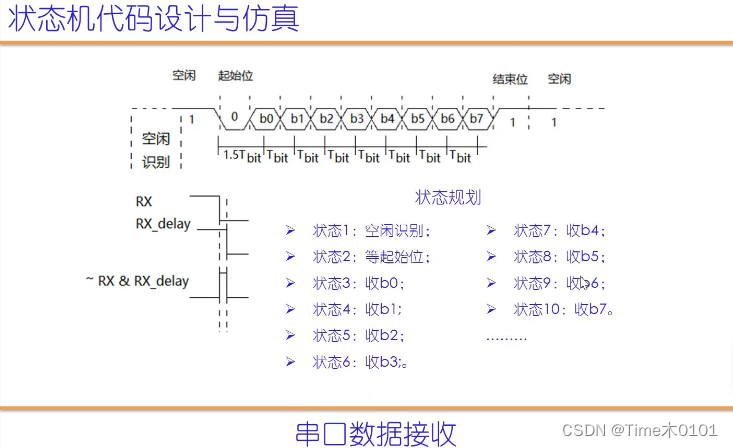

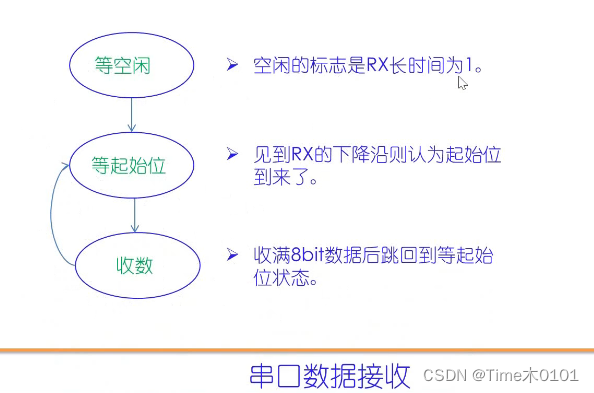

1、串口数据接收

代码:

//2023-09-18,time

//串口数据接收

`timescale 1ns/10ps

module UART_RXer(clk,res,RX,data_out,en_data_out);

input clk;

input res;

input RX;

output[7:0] data_out;//接受字节输出;

output en_data_out;//输出势能;reg[7:0] data_out;

reg[7:0] state;//主状态机;

reg[12:0] con;//用于计算比特宽度;

reg[3:0] con_bits;// 用于计算比特数;reg RX_delay;//RX的延时;

reg en_data_out;

always@(posedge clk or negedge res)

if(~res)beginstate<=0;con<=0;con_bits<=0;RX_delay<=0;en_data_out<=0;data_out<=0;

end

else beginRX_delay<=RX;case(state)0://等空闲:beginif(con==5000-1)begincon<=0;endelse begincon<=con+1;endif(con==0)beginif(RX)begincon_bits<=con_bits+1;endelse begincon_bits<=0;endendif(con_bits==12)beginstate<=1;end end1://等起始位beginen_data_out<=0;if(~RX&RX_delay)beginstate<=2;endend2://收最低位b0;beginif(con==7500-1)begincon<=0;data_out[0]<=RX;state<=3;endelse begincon<=con+1;endend3://收最低位b1;beginif(con==5000-1)begincon<=0;data_out[1]<=RX;state<=4;endelse begincon<=con+1;endend4://收最低位b2;beginif(con==5000-1)begincon<=0;data_out[2]<=RX;state<=5;endelse begincon<=con+1;endend5://收最低位b3;beginif(con==5000-1)begincon<=0;data_out[3]<=RX;state<=6;endelse begincon<=con+1;endend6://收最低位b4;beginif(con==5000-1)begincon<=0;data_out[4]<=RX;state<=7;endelse begincon<=con+1;endend7://收最低位b5;beginif(con==5000-1)begincon<=0;data_out[5]<=RX;state<=8;endelse begincon<=con+1;endend8://收最低位b6;beginif(con==5000-1)begincon<=0;data_out[6]<=RX;state<=9;endelse begincon<=con+1;endend9://收最低位b7;beginif(con==5000-1)begincon<=0;data_out[7]<=RX;state<=10;endelse begincon<=con+1;endend10://产生使能信号脉冲;beginen_data_out<=1;state<=1;enddefault://beginstate<=0;con<=0;con_bits<=0;en_data_out<=0;endendcase

endendmodule//-------testbench of UART_RXer-------

module UART_RXer_tb;

reg clk,res;

wire RX;

wire[7:0] data_out;

wire en_data_out;reg[25:0] RX_send;//里面装有串口字节发送数据

assign RX=RX_send[0];//连接RX;reg[12:0] con;UART_RXer UART_RXer( //同名例化;clk,res,RX,data_out,en_data_out);

initial beginclk<=0;res<=0;RX_send<={1'b1,8'haa,1'b0,16'hffff};con<=0;#17 res<=1;#4000000 $stop;

endalways #5 clk<=~clk;always@(posedge clk) beginif(con==5000-1)begincon<=0;endelse begincon<=con+1;endif(con==0)beginRX_send[24:0]<=RX_send[25:1];RX_send[25]<=RX_send[0];endend

endmodule

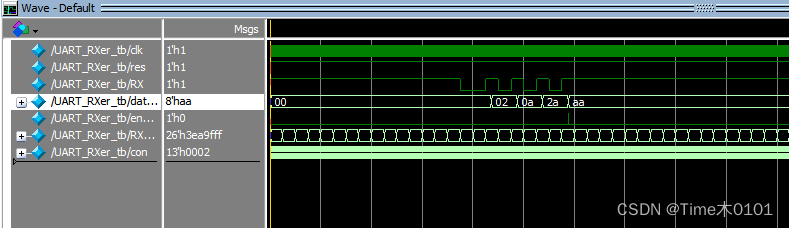

仿真波形:

小结:

第九讲

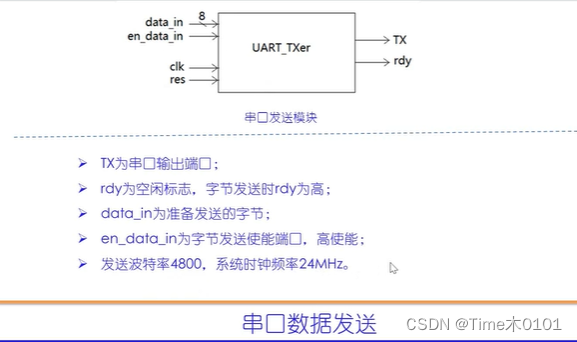

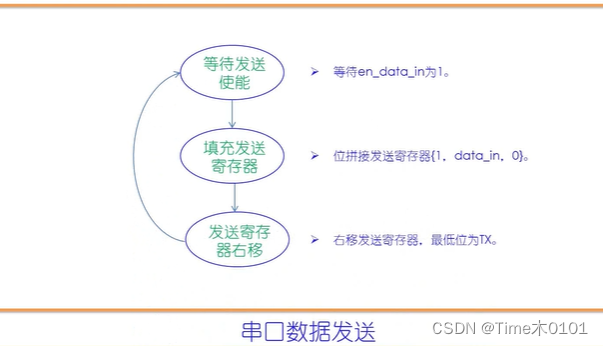

1、串口数据发送

代码:

//2023-09-18,time

//串口发送模块

`timescale 1ns/10ps

module UART_TXer(clk,res,data_in,en_data_in,TX,rdy);

input clk;

input res;

input[7:0] data_in;//准备发送的数据

input en_data_in;//发送使能

output TX;

output rdy;//空闲标志,0表示空闲reg[3:0] state;//主状态机寄存器;

reg[9:0] send_buf;//发送寄存器;

assign TX=send_buf[0];//连接TX;reg[9:0] send_flag;//用于判断右移结束;reg[12:0] con;//用于计算波特周期;

reg rdy;always@(posedge clk or negedge res)

if(~res)beginstate<=0;send_buf<=1;con<=0;send_flag<=10'b10_0000_0000;rdy<=0;

end

else begincase(state)0://等待使能信号beginif(en_data_in)beginsend_buf={1'b1,data_in,1'b0};send_flag<=10'b10_0000_0000;rdy<=1;state<=1;endend1://串口发送,寄存器右移;beginif(con==5000-1)begincon<=0;endelse begincon<=con+1;endif(con==5000-1)beginsend_buf[8:0]<=send_buf[9:1];send_flag[8:0]<=send_flag[9:1];endif(send_flag[0])beginrdy<=0;state<=0;endendendcase

end

endmodule//------testbench of UART_TXer--------

module UART_TXer_tb;

reg clk,res;

reg[7:0] data_in;

reg en_data_in;

wire TX;

wire rdy;

UART_TXer UART_TXer(clk,res,data_in,en_data_in,TX,rdy);initial beginclk<=0;res<=0;data_in<=8'h7f;en_data_in<=0;#17 res<=1;#30 en_data_in<=1;#10 en_data_in<=0;#2000000 $stop;

endalways #5 clk=~clk;endmodule

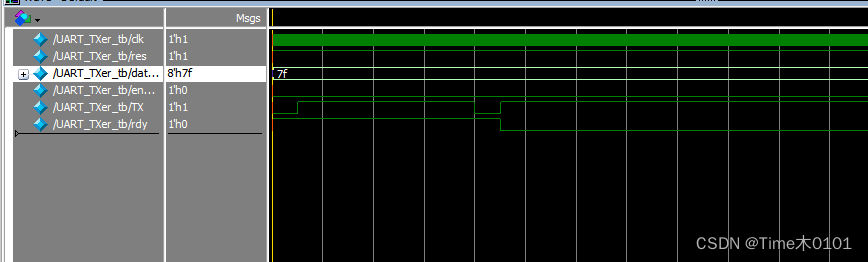

仿真波形:

小结:

第十讲

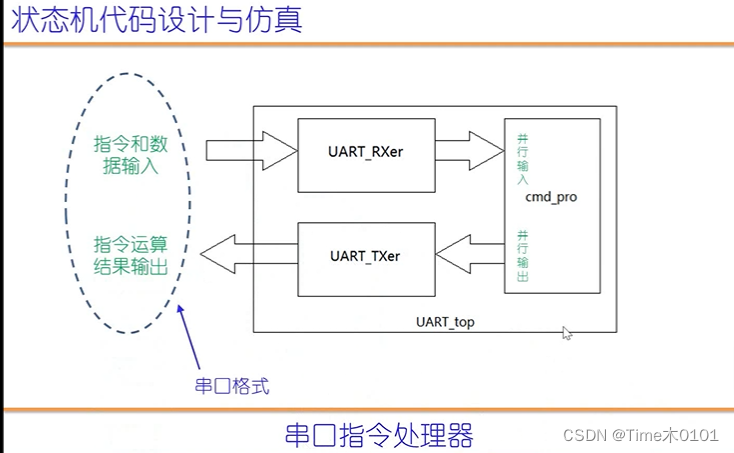

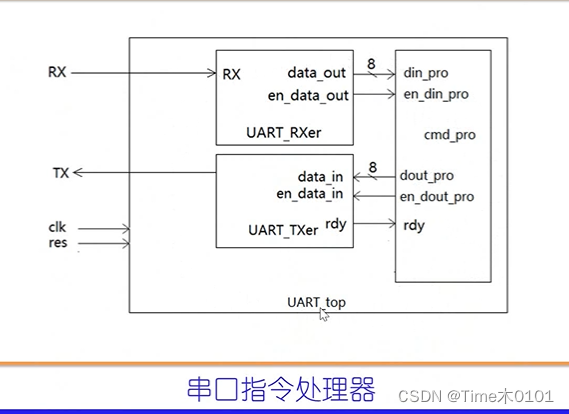

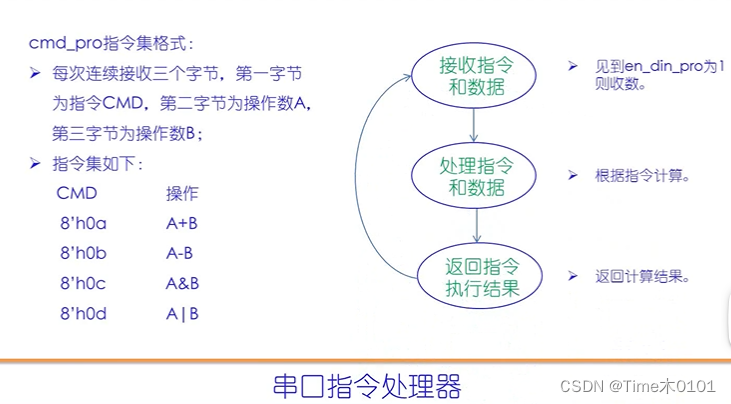

1、串口指令处理器

代码:

//2023-09-19,time

//指令处理器

module cmd_pro(clk,res,din_pro,en_din_pro,dout_pro,en_dout_pro,rdy);

input clk;

input res;

input[7:0] din_pro;//指令和数据输入端口;

input en_din_pro;//输入使能;

output[7:0] dout_pro;//指令执行结果;

output en_dout_pro;//指令输出使能;

output rdy;//串口发送模块空闲标志,0表示空闲;parameter add_ab=8'h0a;

parameter sub_ab=8'h0b;

parameter and_ab=8'h0c;

parameter or_ab =8'h0d;reg[2:0] state;//主状态机寄存器

reg[7:0] cmd_reg,A_reg,B_reg;//存放指令、A和B;

reg[7:0] dout_pro;

reg en_dout_pro;always@(posedge clk or negedge res)begin

if(~res)beginstate<=0;cmd_reg<=0;A_reg<=0;B_reg<=0;dout_pro<=0;en_dout_pro<=0;

end

else begincase(state)0://等指令;beginen_dout_pro<=0;if(en_din_pro)begincmd_reg<=din_pro;state<=1;endend1://收Abeginif(en_din_pro)beginA_reg<=din_pro;state<=2;endend2://收Bbeginif(en_din_pro)beginB_reg<=din_pro;state<=3;endend3://指令译码和执行;beginstate<=4;//指令译码一个时钟周期就可以,所以可以没条件case(cmd_reg)add_ab: begin dout_pro<=A_reg+B_reg; endsub_ab: begin dout_pro<=A_reg-B_reg; endand_ab: begin dout_pro<=A_reg&B_reg; endor_ab: begin dout_pro<=A_reg|B_reg; endendcaseend4://发送指令执行结果;beginif(~rdy)beginen_dout_pro<=1;state<=0;endenddefault://beginstate<=0;en_dout_pro<=0;endendcase

end

endmodule

//2023-09-19,time

//串口指令处理器;

`timescale 1ns/10ps

module UART_top(clk,res,RX,TX);

input clk;

input res;

input RX;

output TX;wire[7:0] din_pro;

wire en_din_pro;

wire[7:0] dout_pro;

wire en_dout_pro;

wire rdy;UART_RXer UART_RXer( .clk(clk),.res(res),.RX(RX),.data_out(din_pro),.en_data_out(en_din_pro));UART_TXer UART_TXer( .clk(clk),.res(res),.data_in(dout_pro),.en_data_in(en_data_),.TX(TX),.rdy(rdy));cmd_pro cmd_pro(.clk(clk),.res(res),.din_pro(din_pro),.en_din_pro(en_din_pro),.dout_pro(dout_pro),.en_dout_pro(en_dout_pro),.rdy(rdy));

endmodule //-------testbench of UART_top------

module UART_top_tb;

reg clk,res;

wire RX;

wire TX;reg[45:0] RX_send;//里面装有串口字节发送数据

assign RX=RX_send[0];//连接RX;reg[12:0] con;UART_top UART_top(clk,res,RX,TX);initial beginclk<=0;res<=0;RX_send<={1'b1,8'h09,1'b0,1'b1,8'h06,1'b0,1'b1,8'h0a,1'b0,16'hffff};con<=0;#17 res<=1;#4000000 $stop;

endalways #5 clk<=~clk;always@(posedge clk) beginif(con==5000-1)begincon<=0;endelse begincon<=con+1;endif(con==0)beginRX_send[44:0]<=RX_send[45:1];RX_send[45]<=RX_send[0];endend

endmodule

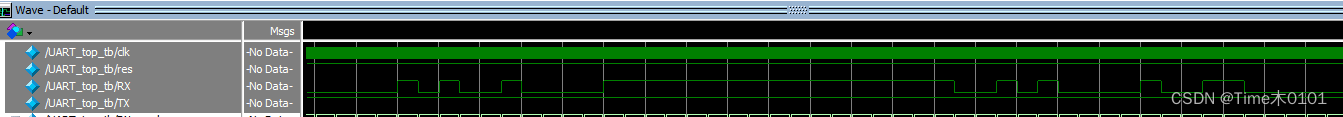

仿真波形:

小结:

相关文章:

Verilog零基础入门(边看边练与测试仿真)-状态机-笔记(7-10讲)

文章目录 第七讲第八讲第九讲第十讲 第七讲 1、最简单的状态机-三角波发生器 1、两种状态的代码: //最简单的状态机,三角波发生器; timescale 1ns/10ps module tri_gen(clk,res,d_out); input clk; input res; o…...

【Hadoop】HDFS API 操作大全

🍁 博主 "开着拖拉机回家"带您 Go to New World.✨🍁 🦄 个人主页——🎐开着拖拉机回家_Linux,大数据运维-CSDN博客 🎐✨🍁 🪁🍁 希望本文能够给您带来一定的帮助…...

Webpack打包图片

一、在js文件中引入图片 二、在package.config.js中配置加载器 module.exports {mode: "production", // 设置打包的模式:production生产模式 development开发模式module: {rules: [// 配置img加载器{test: /\.(jpg|png|gif)$/i,type:"asset/resou…...

DipC 构建基因组 3D 结构(学习笔记)

背景 本文主要记录了 DipC 数据的复现过程、学习笔记及注意事项。 目录 下载 SRA 数据使用 SRA Toolkit 转换 SRA 数据为 Fastq 格式使用 bwa 比对测序数据使用 Hickit 计算样本的基因组 3D 结构使用散点图展示 3D 结构计算 3D 结构重复模拟的稳定性其他 步骤 1. 下载 SRA…...

Qt中音频的使用

对于音频我们在使用的过程中一般是录制音频、播放音频。针对这两个需求介绍Qt中音频的使用。 Qt中音频的录制 步骤: 1、获取系统中的音频设备。 2、创建QAudioRecorder对象,指定使用的音频设备,通过QAudioRecorder的setAudioInput函数设置…...

[centos]centos7源码编译cmake报错Could NOT find OpenSSL

测试环境: centos7.9 cmake3.25.0 ./bootstrap以后报错如下: Could NOT find OpenSSL, try to set the path to OpenSSL root folder in the system variable OPENSSL_ROOT_DIR (missing: OPENSSL_CRYPTO_LIBRARY OPENSSL_INCLUDE_DIR) CMake Error …...

vue若依前端项目搭建

1.项目搭建 首先进入到你需要创建的项目目录下面,然后输入命令vue create .创建项目 接下来选择手动搭建,然后把下面图片中的内容选上 再然后继续配置一些参数信息 接下来运行npm run serve项目就启动起来了 2.配置登录界面文件 首先修改src/router…...

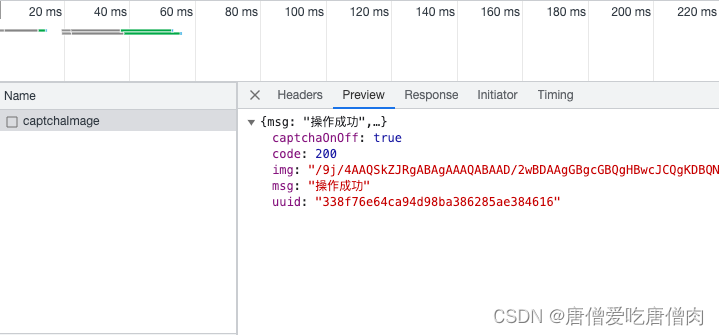

基于win32实现TB登陆滑动验证

这里写目录标题 滑动验证触发条件:失败条件:解决方法:清除cooKie 滑动验证方式一:win32 api获取窗口句柄,选择固定位置 成功率高方式二: 原自动化滑动,成功率中 案例 先谈理论,淘宝 taobao.com …...

vue学习-07todoList案例与浏览器本地存储

TodoList Todo List(任务列表)是一个简单的Web应用程序示例,用于管理任务、代办事项或清单。Vue.js 是一个非常适合构建这种类型应用程序的框架,因为它提供了数据绑定、组件化、响应式和轻松管理用户界面的能力。 以下是一个基本…...

探索智能应用的基石:多模态大模型赋能文档图像处理

目录 0 写在前面1 文档图像分析新重点2 token荒:电子文档助力大模型3 大模型赋能智能文档分析4 文档图像大模型应用可能性4.1 专有大模型4.2 多模态模型4.3 设计思路 总结 0 写在前面 中国智能产业高峰论坛(CIIS2023)旨在为政企研学各界学者专家提供同台交流的机会…...

自动化发布npm包小记

1.注册npm账号 打开npm官网,并注册自己的npm账号 2.申请AccessToken 1.登录npm官网,登录成功后,点开右上角头像,并点击Access Tokens选项 2.点开Generate New Token下拉框,点击Classic Token(和Granular Access To…...

详解机器视觉性能指标相关概念——混淆矩阵、IoU、ROC曲线、mAP等

目录 0. 前言 1. 图像分类性能指标 1.1 混淆矩阵(Confusion Matrix) 1.2 准确率(Precision) 1.3 召回率(Recall) 1.4 F1值(F1 score) 1.5 ROC曲线(接收者工作特征曲线,Receiver Operating Characteristic curve) 1.6 mAP(mean Average Precision) 2. 图像分…...

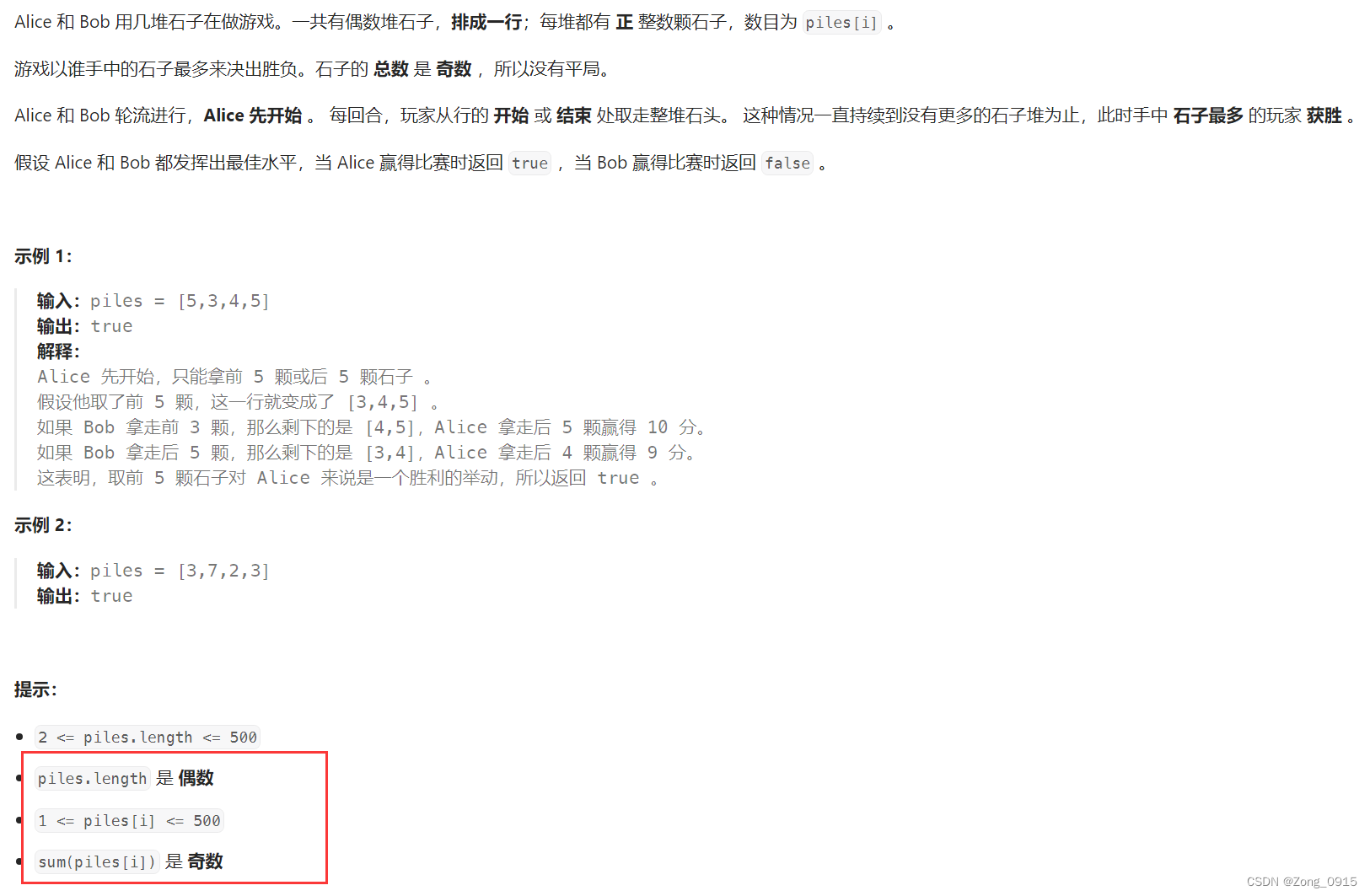

想要精通算法和SQL的成长之路 - 预测赢家

想要精通算法和SQL的成长之路 - 预测赢家 前言一. 预测赢家二. 石子游戏(预测赢家的进阶版)2.1 博弈论 前言 想要精通算法和SQL的成长之路 - 系列导航 一. 预测赢家 原题链接 主要思路: 我们定义dp[i][j]:在区间 [i, j] 之间先…...

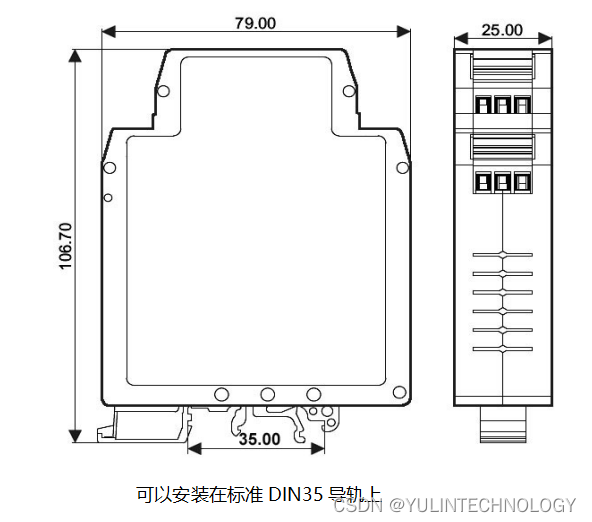

高精度PWM脉宽调制信号转模拟信号隔离变送器1Hz~10KHz转0-5V/0-10V/1-5V/0-10mA/0-20mA/4-20mA

主要特性: >>精度等级:0.1级。产品出厂前已检验校正,用户可以直接使用 >>辅助电源:8-32V 宽范围供电 >>PWM脉宽调制信号输入: 1Hz~10KHz >>输出标准信号:0-5V/0-10V/1-5V,0-10mA/0-20mA/4-20mA等&…...

Vue路由和Node.js环境搭建

文章目录 一、vue路由1.1 简介1.2 SPA1.3 实例 二、Node.js环境搭建2.1 Node.js简介2.2 npm2.3 环境搭建2.3.1 下载解压2.3.2 配置环境变量2.3.3 配置npm全局模块路径和cache默认安装位置2.3.4 修改npm镜像提高下载速度 2.4 运行项目 一、vue路由 1.1 简介 Vue 路由是 Vue.js…...

【Vue】使用vue-cli搭建SPA项目的路由,嵌套路由

一、SPA项目的构建 1、前期准备 我们的前期的准备是搭建好Node.js,测试: node -v npm -v2、利用Vue-cli来构建spa项目 2.1、什么是Vue-cli Vue CLI 是一个基于 Vue.js 的官方脚手架工具,用于自动生成vue.jswebpack的项目模板,它可以帮助开发者…...

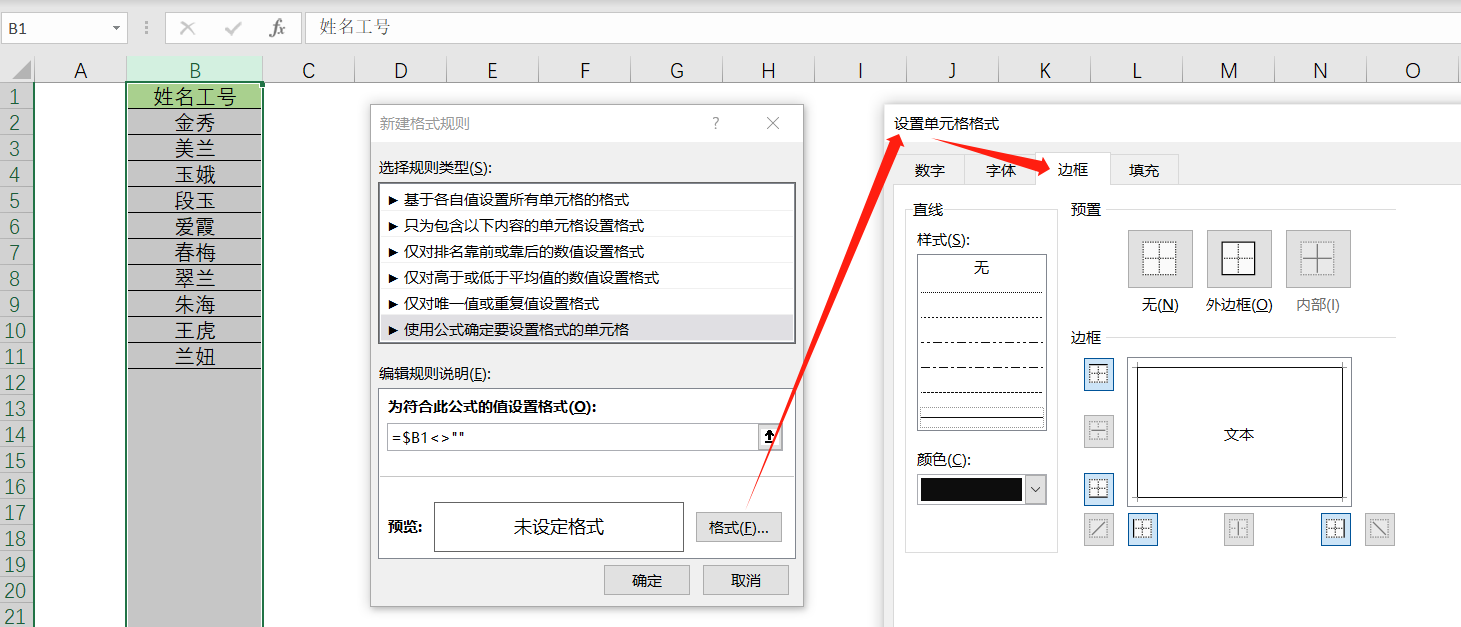

Excel 通过条件格式自动添加边框

每录入一次数据就需要手动添加一次边框,非常麻烦,这不是我们想要的。 那么有没有办法,在我们录入数据后,自动帮我们加上边框呢? 选中要自动添加边框的列,然后按箭头流程操作 ↓ ↓ ↓ ↓...

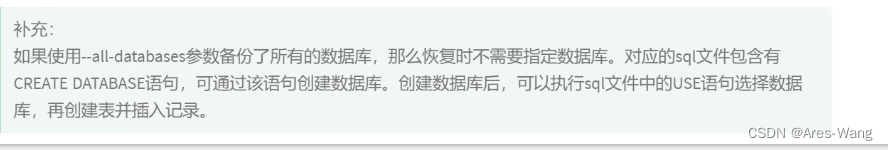

mysql 备份和还原 mysqldump

因window系统为例 在mysql安装目录中的bin目录下 cmd 备份 备份一个数据库 mysqldump -uroot -h hostname -p 数据库名 > 备份的文件名.sql 备份部分表 mysqldump -uroot -h hostname -p 数据库名 [表 [表2…]] > 备份的文件名.sql ## 多个表 空格隔开,中间…...

ELK日志分析系统+ELFK(Filebeat)

本章结构: 1、ELK日志分析系统简介 2、Elasticsearch介绍(简称ES) 3、Logstash介绍 4、Kibana介绍 5、实验,ELK部署 一、ELK日志分析系统简介 ELK平台是一套完整的日志集中处理解决方案,将 ElasticSearch、Logst…...

ULID 在 Java 中的应用: 使用 `getMonotonicUlid` 生成唯一标识符

🌷🍁 博主猫头虎 带您 Go to New World.✨🍁 🦄 博客首页——猫头虎的博客🎐 🐳《面试题大全专栏》 文章图文并茂🦕生动形象🦖简单易学!欢迎大家来踩踩~🌺 &a…...

搞定2026年生鲜促销图,我的经验是别直接套模板

搞定2026年生鲜促销图,我的经验是别直接套模板我是生鲜电商店铺的运营,上周老板让我负责新品豇豆的推广,要求在周三下午之前做一张吸引人的线上促销海报。这是一个急活,但我自己用手机拍的几张豇豆照片,背景杂乱&#…...

三方备付金·非同充值+非同代付+D0秒到

一、主体与资质• 业务主体:企业对公主体• 资质需求:持牌第三方支付机构通道• 账户类型:三方备付金账户(资金存管、隔离)二、核心功能需求1. 非同名充值◦ 支持他人/其他企业向我方备付金账户充值◦ 支持对公/对私转…...

)

欧意下载okxz.run复制打开 最新地址分享(安卓苹果通用)

欧意下载okxz.run复制打开 最新地址分享(安卓苹果通用)1983年8月18日中午11 - 13点出生的人,其性格、运势与命运有着独特的轨迹。在这个特定的时空点降临世间,他们带着彼时星辰赋予的特质,开启了人生之旅。这类人往往性…...

如何优化WebAssembly Design数学库:线性代数与微积分计算的终极指南

如何优化WebAssembly Design数学库:线性代数与微积分计算的终极指南 【免费下载链接】design WebAssembly Design Documents 项目地址: https://gitcode.com/gh_mirrors/de/design WebAssembly Design数学库是WebAssembly生态系统中处理线性代数与微积分计算…...

【为AI,提升五笔打字速度】200个常用易错五笔汉字整理

📝 200个常用易错五笔汉字整理 横起笔类(GFDSA) 这类字起笔为“一”,容易在字根的拆分顺序和相交关系上出错。汉字五笔编码易错点解析未FII容易与“末(GSI)”混淆。编码不同:未是“二小”,末是“一木”。末…...

Vulnhub DC-3 --手搓sql

DC-3 主机扫描 端口扫描 目录扫描 存在目录administrator 只开放80端口,访问页面 根据flag提示,只有一个flag,需要获取到root权限 访问扫描出的adminstrator页面 页面显示joomla 基于PHP和MySQL开发的开源内容管理系统(CMS&…...

全年出货33万吨创纪录!尚太科技北苏二期投产背后的增长密码

全年出货33万吨创纪录!尚太科技北苏二期投产背后的增长密码2025年,尚太科技以33万吨负极材料出货量刷新行业纪录,营收同比激增61.83%至33.88亿元,净利润达4.79亿元,同比增长34.37%,扣非净利润增速更高达40.…...

结构体变量和指针的构建和访问

导言:大家在学习C语言的指针和结构体内容时,我们会尝试用一种更简单方便的方式去访问我们定义的结构体:定义结构体变量和结构体指针的方式.那这两个变量有什么区别呢?第一行中的S为结构体_StuInfo的结构变量,第二行中的P为结构体_…...

德赛西威西班牙工厂封顶倒计时

今天讲的出海案例是德赛西威,国内智能座舱和智能驾驶域控制器的双料龙头,在西班牙安达卢西亚自治区利纳雷斯市投建智能工厂,2026年量产后首批供应车载显示屏。在2026年3月10日的投资者关系活动记录表中,德赛西威提到西班牙智能工厂…...

IDEA配置目录迁移指南:告别C盘束缚,实现灵活存储

1. 为什么需要迁移IDEA配置目录? 每次重装系统或者升级IDEA时,最让人头疼的就是那些精心调整的配置和插件全部消失。我经历过三次这样的痛苦,最后一次终于下定决心要把配置目录从C盘解放出来。你可能不知道,IDEA默认会把所有用户配…...