Vivado下PLL实验

文章目录

- 前言

- 一、CMT(时钟管理单元)

- 1、CMT 简介

- 2、FPGA CMT 框图

- 3、MMCM 框图

- 4、PLL 框图

- 二、创建工程

- 1、创建工程

- 2、PLL IP 核配置

- 3、进行例化

- 三、进行仿真

- 1、创建仿真文件

- 2、进行仿真设置

- 3、进行行为级仿真

- 四、硬件验证

- 1、引脚绑定

- 2、生成比特流文件

- 3、验证

- 五、资源自取

前言

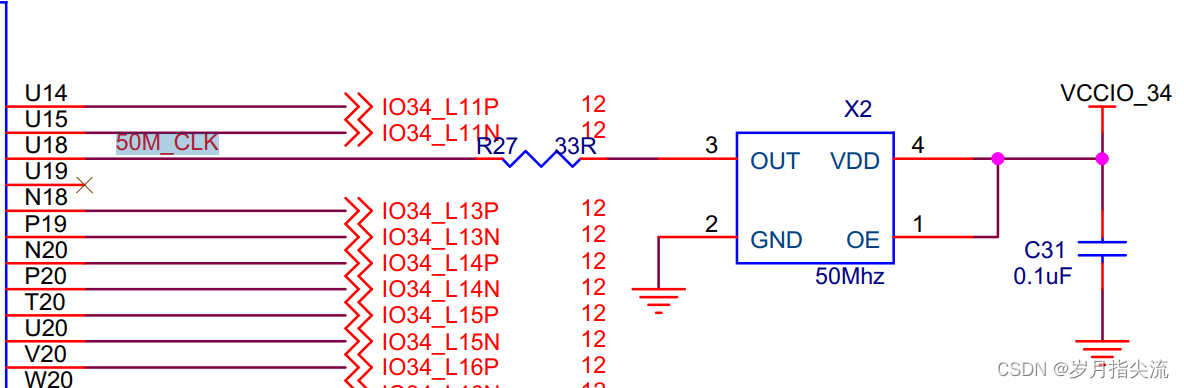

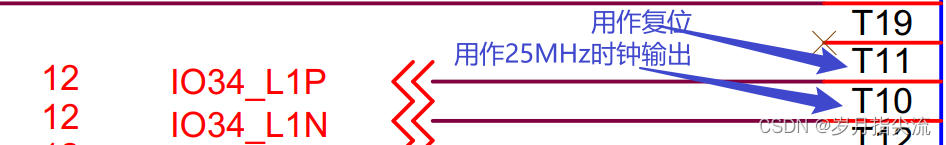

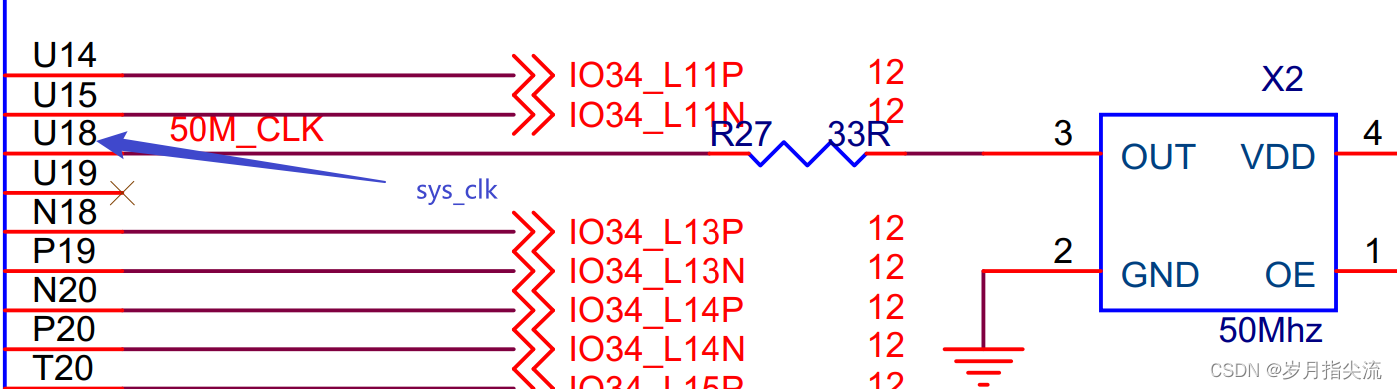

本节介绍一下赛灵思锁相环的一个使用方法,我手头的 AC7020 fpga 开发板上面有一个 50MHz 的晶振连接在 PL 端,晶振输出链接到 FPGA 的全局时钟(MRCC),这个 CLK 可以用来驱动 FPGA 内的用户逻辑电路,该时钟源的原理图如图所示:

但是在我们实际应用当中呢我们可能想要使用特定大小的频率,比如 25MHz 或者 100MHz,那么我们可以使用赛灵思的锁相环的 IP 实现它的时钟分频或者倍频。

一、CMT(时钟管理单元)

1、CMT 简介

Xilinx7 系列器件中的时钟资源包含了CMT(全称 Clock Management Tile,即时钟管理单元),每个 CMT 由一个 MMCM(全称 Mixed-Mode Clock Manager,即混合模式时钟管理)和一个 PLL(全称 Phase Locked Loop,即锁相环)组成,

- MMCM(混合模式时钟管理):是基于 PLL 的新型混合模式时钟管理器,实现了最低的抖动和抖动滤波,为高性能的 FPGA 设计提供更高性能的时钟管理功能。

- MMCM 在 PLL 的基础上加上了相位动态调整功能,

- PLL:为锁相回路或锁相环,用来统一整合时钟信号,使高频器件正常工作,如内存的存取数据 等。PLL 用于振荡器中的反馈技术。

- 锁相环拥有强大的性能,可以对输入到 FPGA 的时钟信号进行任意分频、倍频、相位调整、占空比调整,从而输出一个期望时钟;

MMCM 相对 PLL 的优势就是相位可以动态调整,但 PLL 占用的面积更小,而在大部分的设计当中大家使用 MMCM 或者 PLL 来对系统时钟进行分频、倍频和相位偏移都是完全可以的。

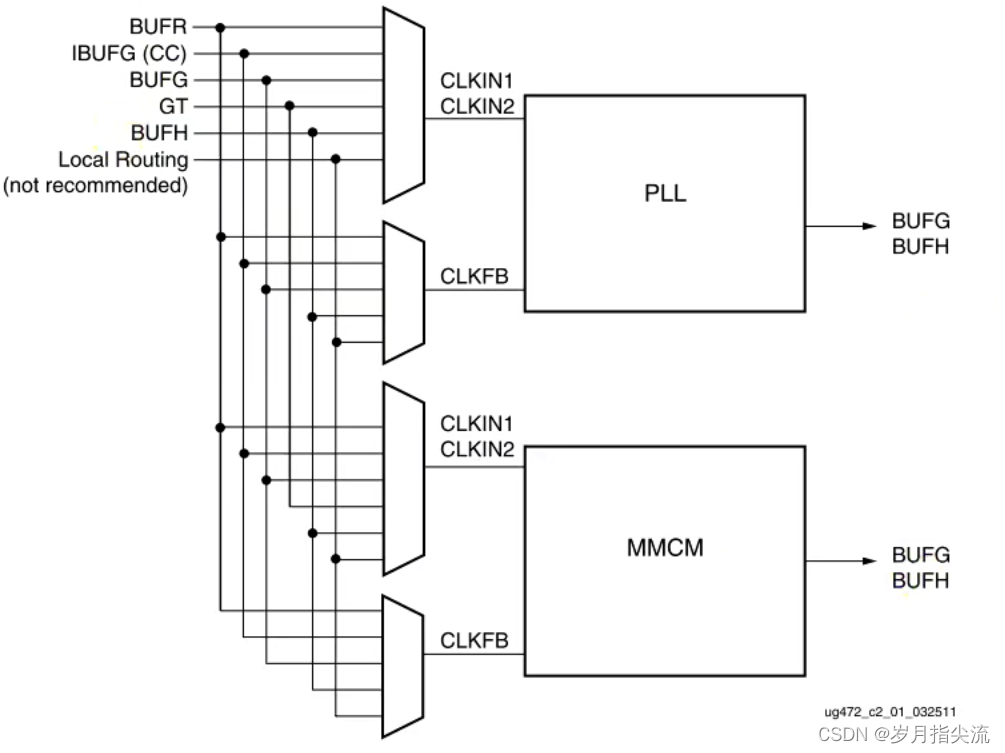

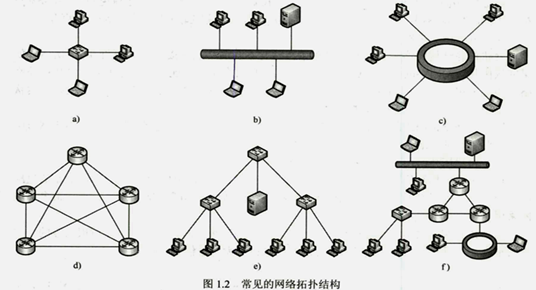

2、FPGA CMT 框图

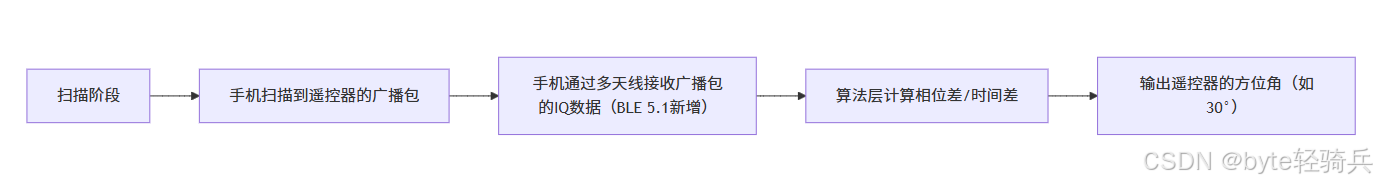

下图为 7 系列 FPGA CMT 的一个简单的结构,最左边是输入的一些时钟源,最右边是输出。

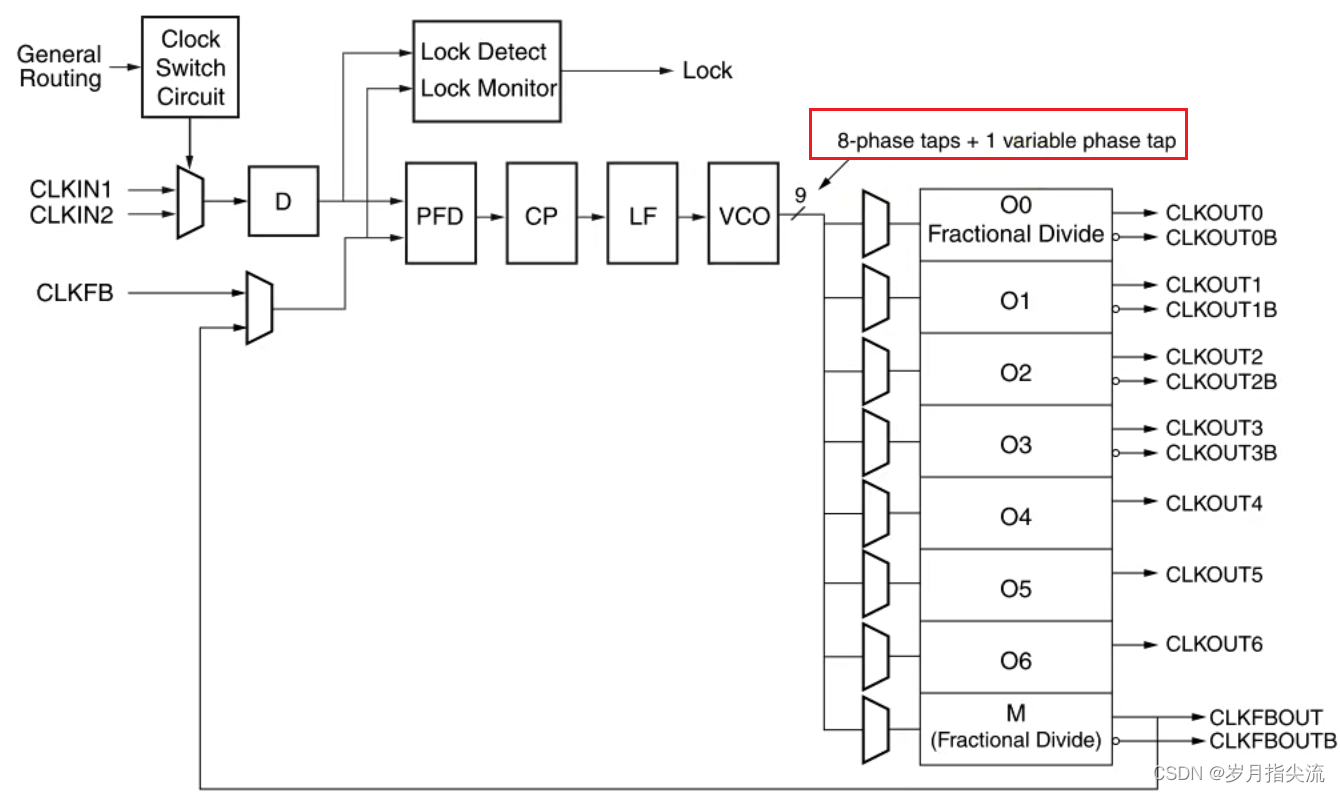

3、MMCM 框图

下图是 MMCM 的框图,可以看到它包含 8 个相位的拍 + 1 个可变相位拍

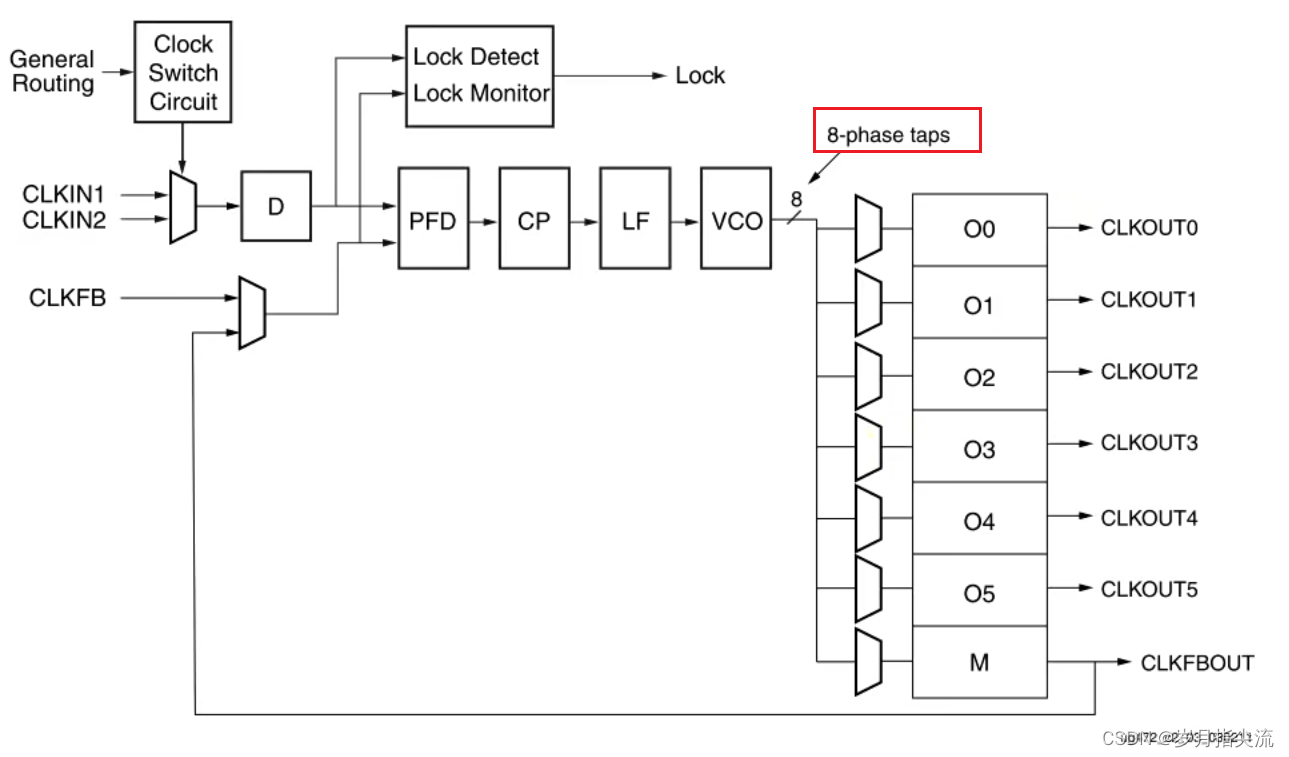

4、PLL 框图

下图是 PLL 的框图,可以看到它只包含 8 个相位的拍

二、创建工程

1、创建工程

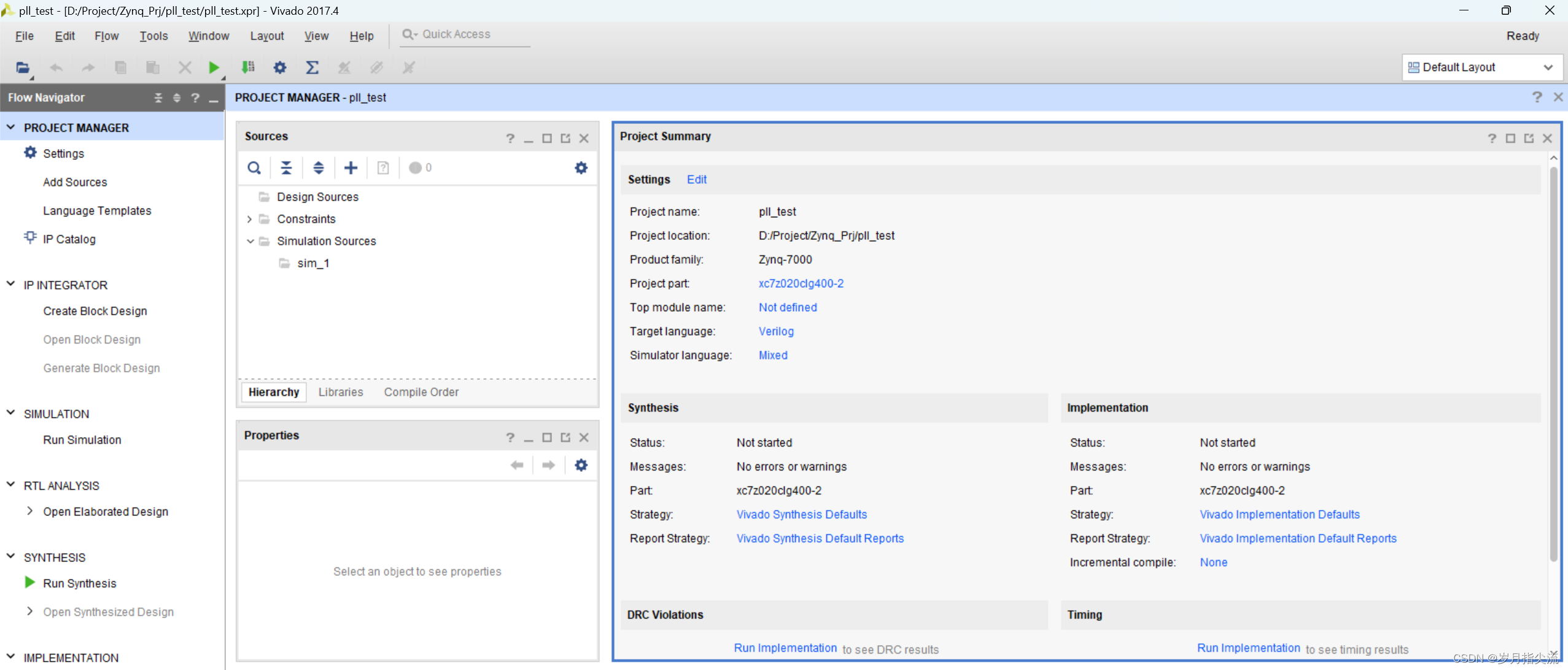

创建一个名字为 pll_test 的工程

2、PLL IP 核配置

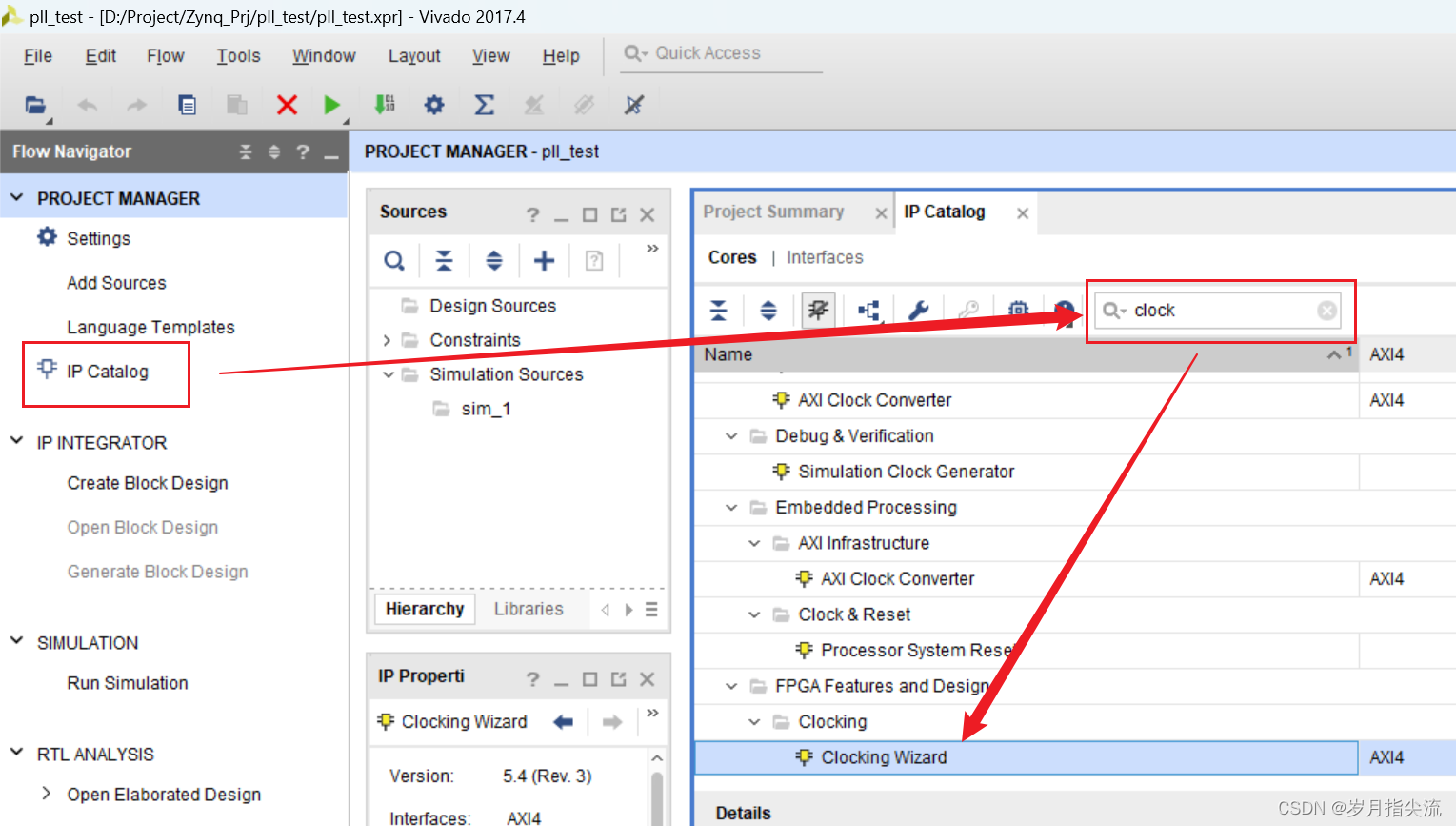

1、点击 IP Catalog,搜索 clock,找到 Clocking Wizard 并双击

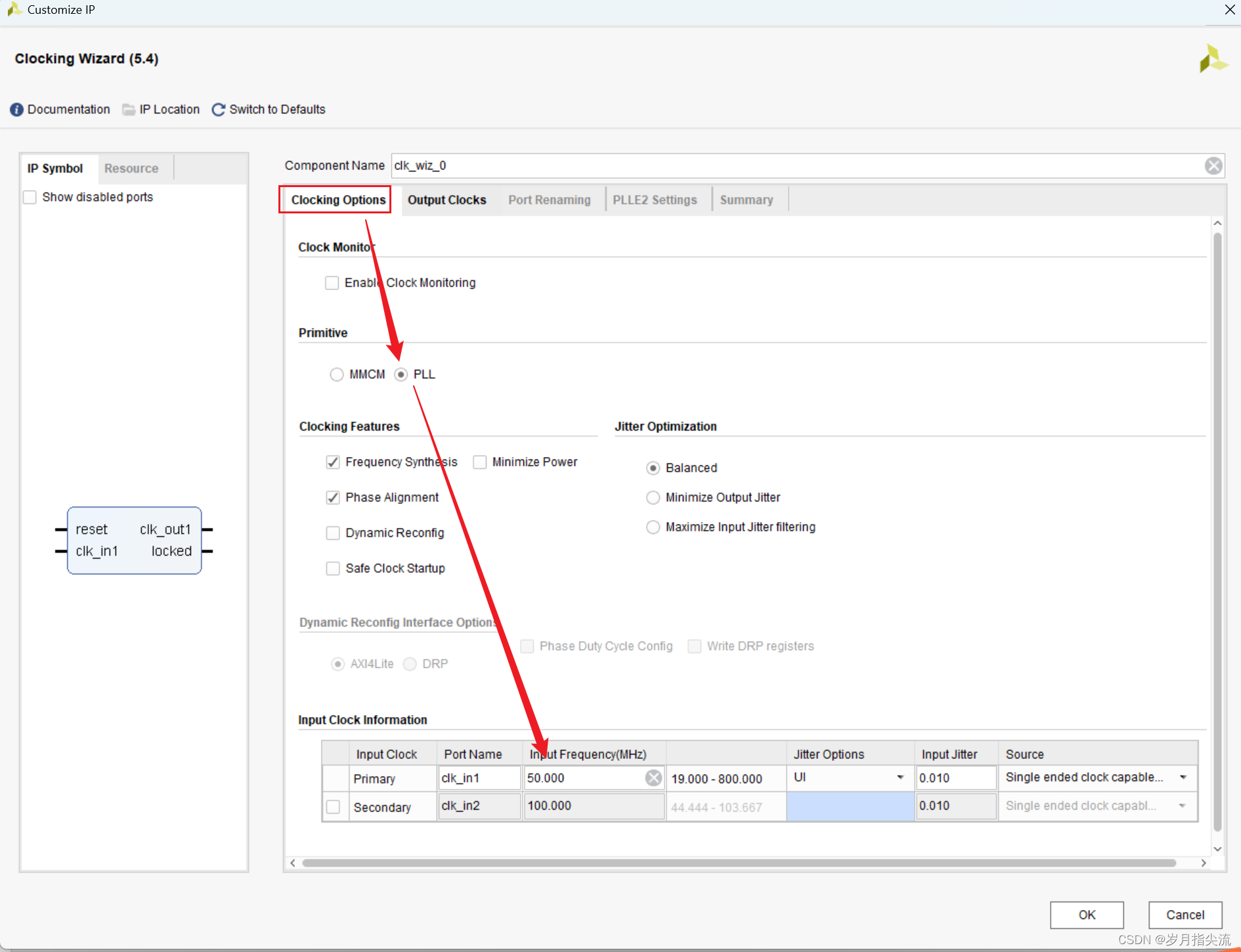

2、在 Clocking Option 下按如下图进行配置

- Primitive 选择 PLL

- Input Clock Information 中的主时钟的输入频率填上我们板子晶振频率:50MHz

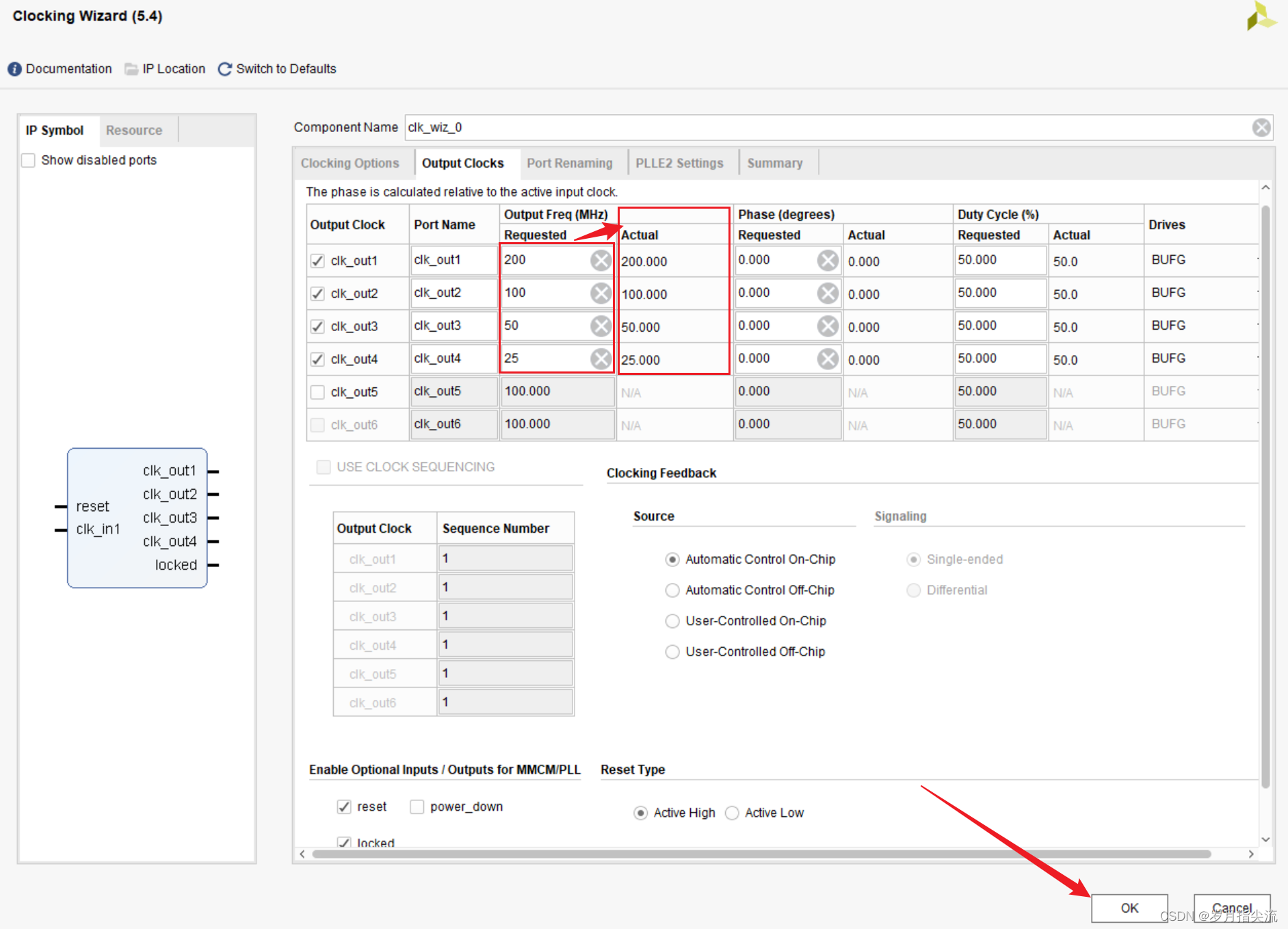

3、在 Output Clocks 下按如下图进行配置,并点击 OK

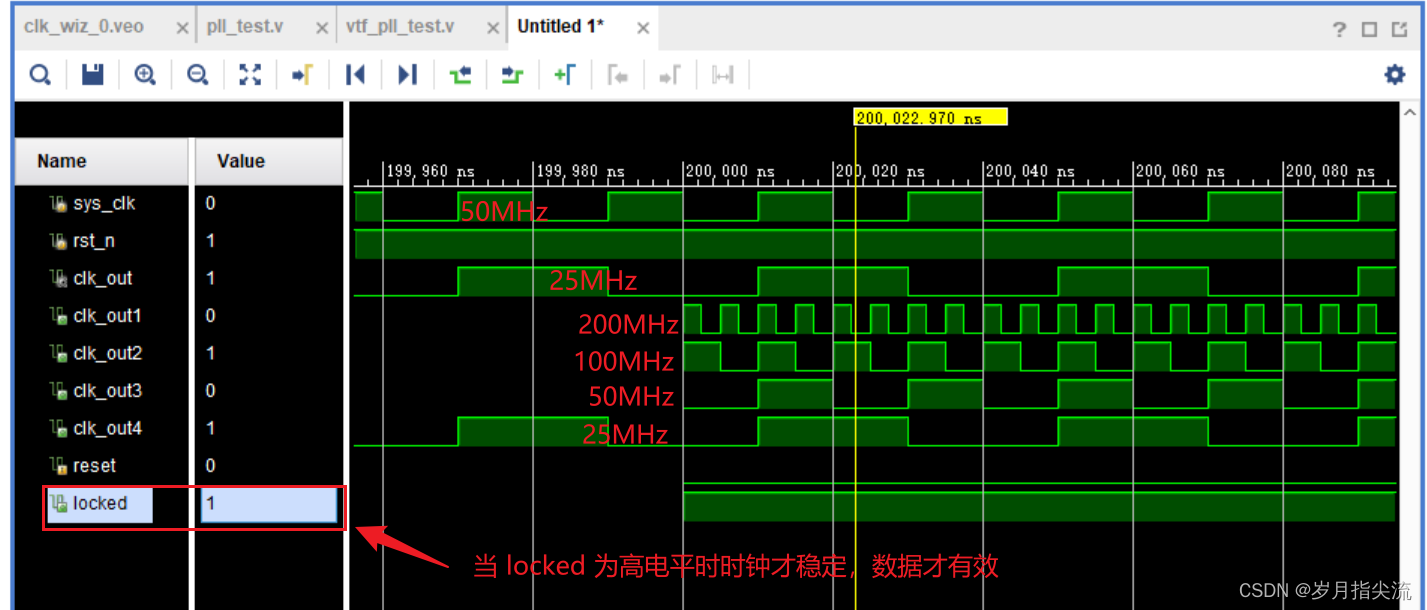

我们输出 200MHz、100MHz、50MHz、25MHz 这么四路不同频率的时钟

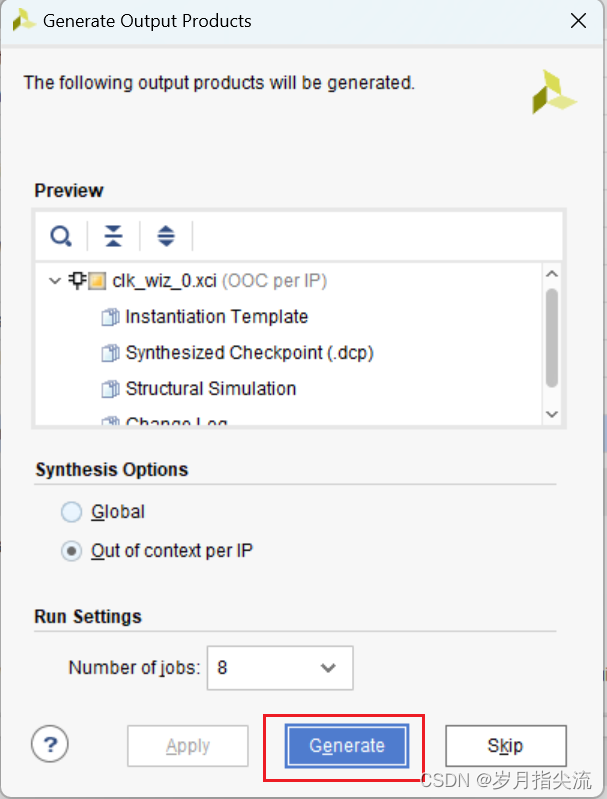

4、点击生成 Generate

3、进行例化

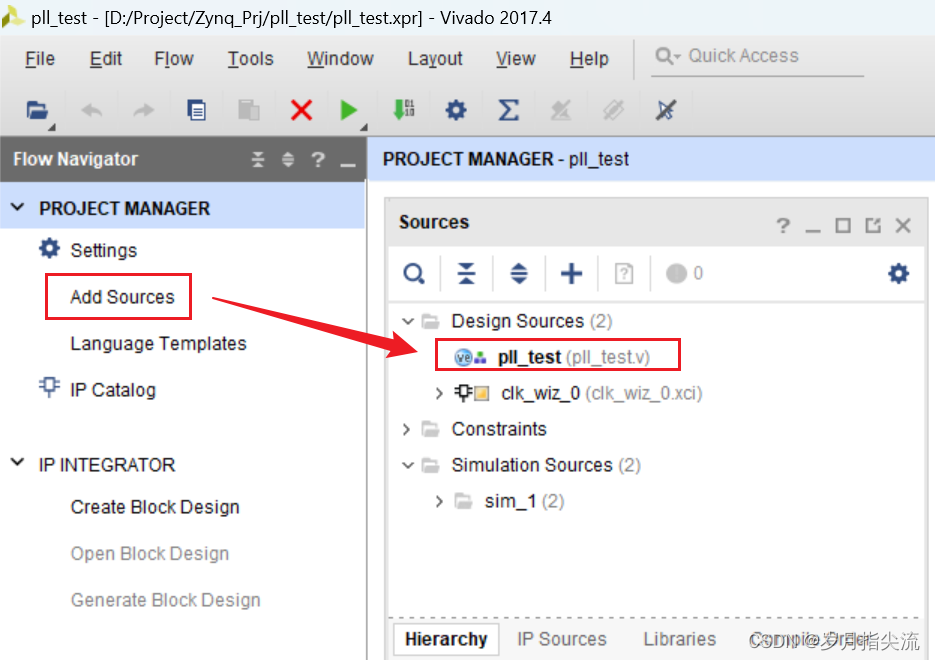

1、创建一个名为 pll_test.v 文件

2、复制例化模板到我们刚创建的 pll_test.v 文件中

3、对 pll_test.v 文件进行修改,修改之后的代码如下(这里我们只输出 25MHz 信号)

`timescale 1ns / 1psmodule pll_test(input sys_clk, // 50MHzinput rst_n,output clk_out);wire pll_locked; clk_wiz_0 clk_inst(// Clock out ports.clk_out1(), // output clk_out1.clk_out2(), // output clk_out2.clk_out3(), // output clk_out3.clk_out4(clk_out), // output clk_out4// Status and control signals.reset(~rst_n), // input reset.locked(pll_locked), // output locked// Clock in ports.clk_in1(sys_clk)); // input clk_in1 endmodule

三、进行仿真

1、创建仿真文件

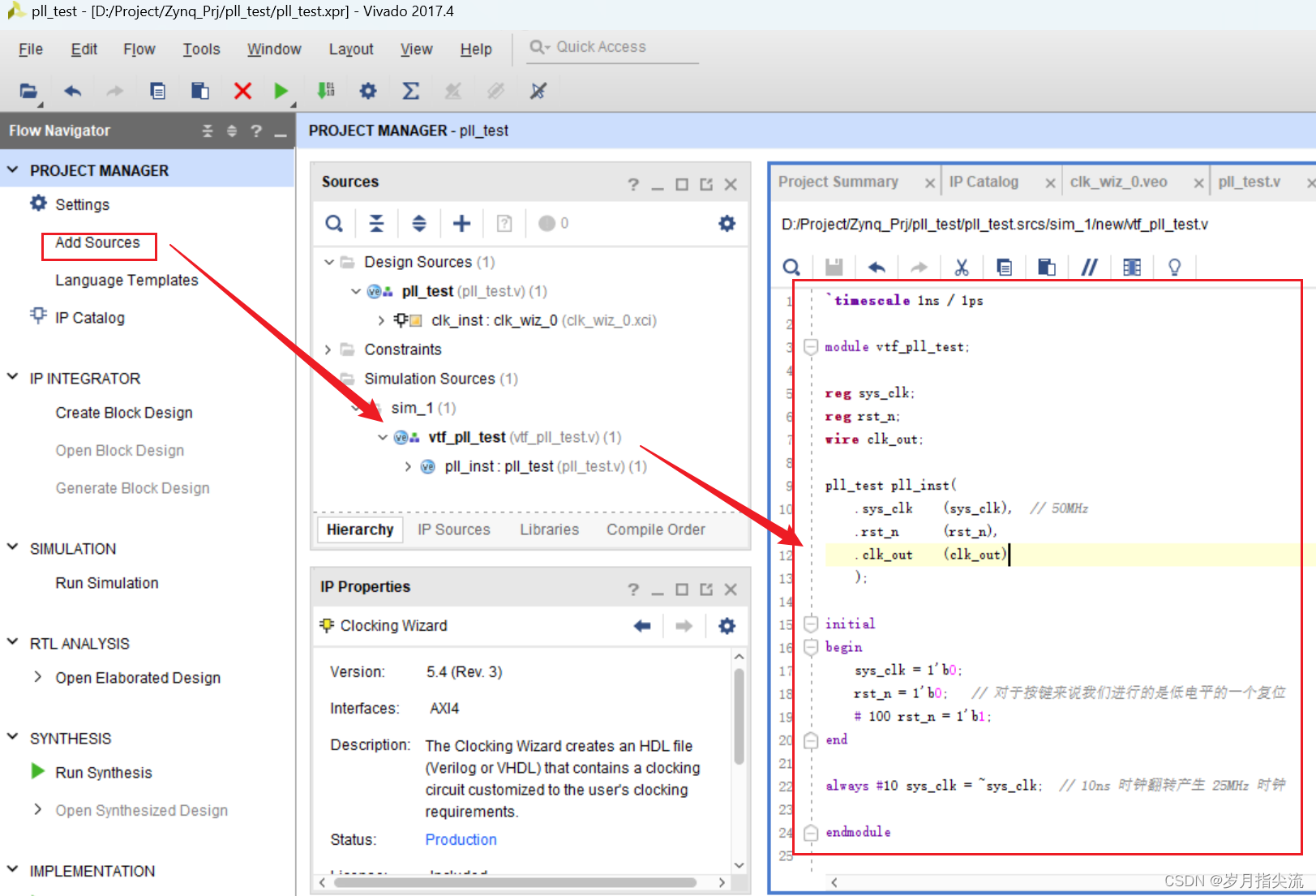

创建名为 vtf_pll_test.v 的仿真文件,并进行例化编写 verilog 仿真程序

`timescale 1ns / 1psmodule vtf_pll_test;reg sys_clk;

reg rst_n;

wire clk_out;pll_test pll_inst(.sys_clk (sys_clk), // 50MHz.rst_n (rst_n),.clk_out (clk_out));initial

beginsys_clk = 1'b0;rst_n = 1'b0; // 对于按键来说我们进行的是低电平的一个复位# 100 rst_n = 1'b1;

endalways #10 sys_clk = ~sys_clk; // 10ns 时钟翻转产生 25MHz 时钟endmodule

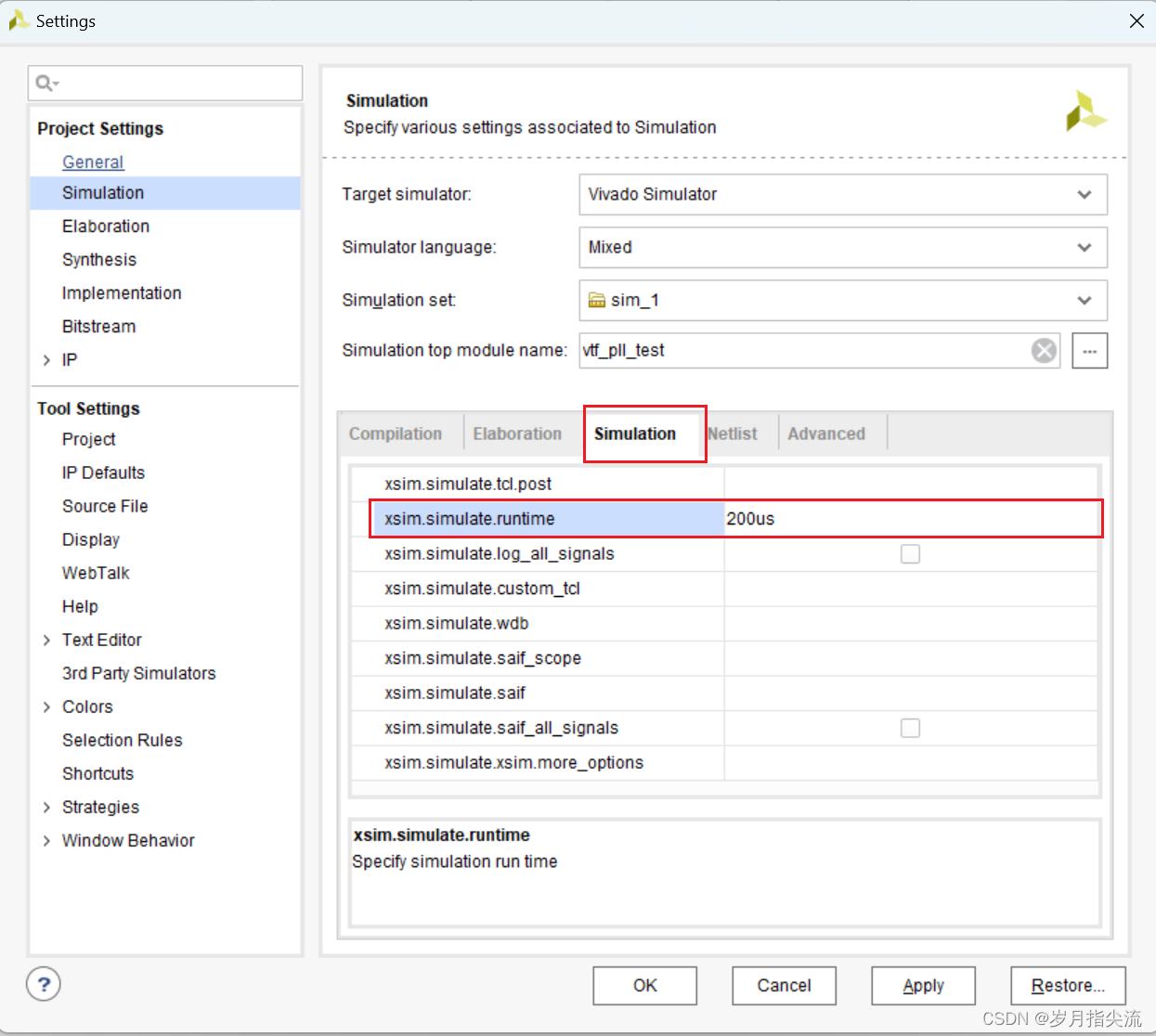

2、进行仿真设置

①、右键 Run Simulation -> Simulation Settings…

②、设置仿真时间,这里填 200us 即可

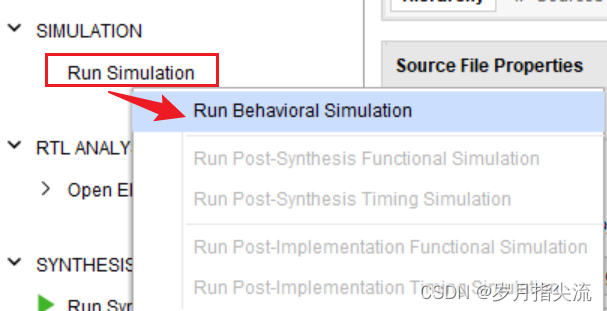

3、进行行为级仿真

①、左键 Run Simulation -> Run Behavioral Simulation

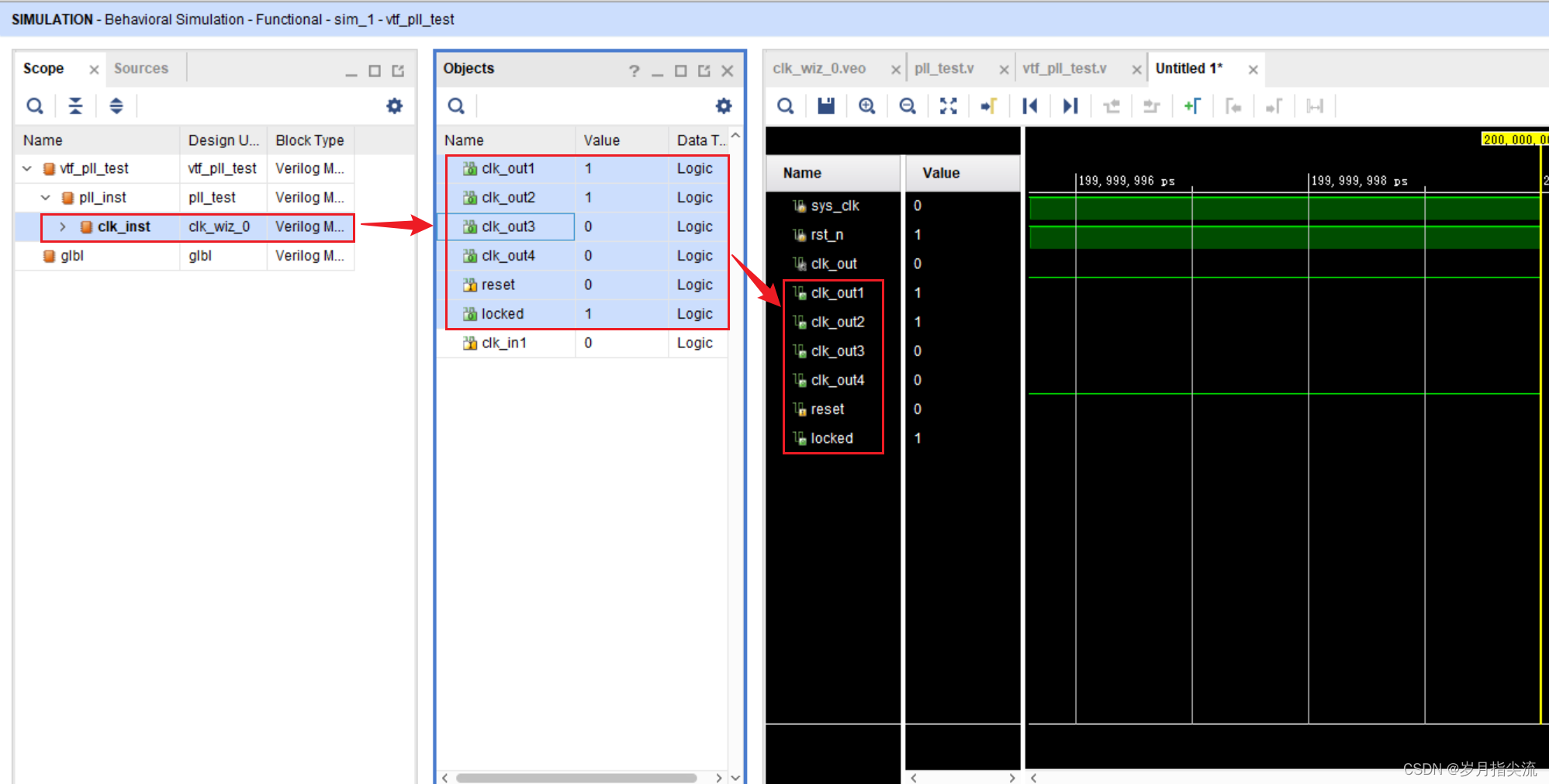

②、将 vtf_pll_test 下的 pll_inst 下的 clk_inst 的 clk_out1、clk_out2、clk_out3、clk_out_4、reset、locked 拖拽到仿真界面 Name 栏下

③、点击 Run for 10us,可以看下图结果

四、硬件验证

1、引脚绑定

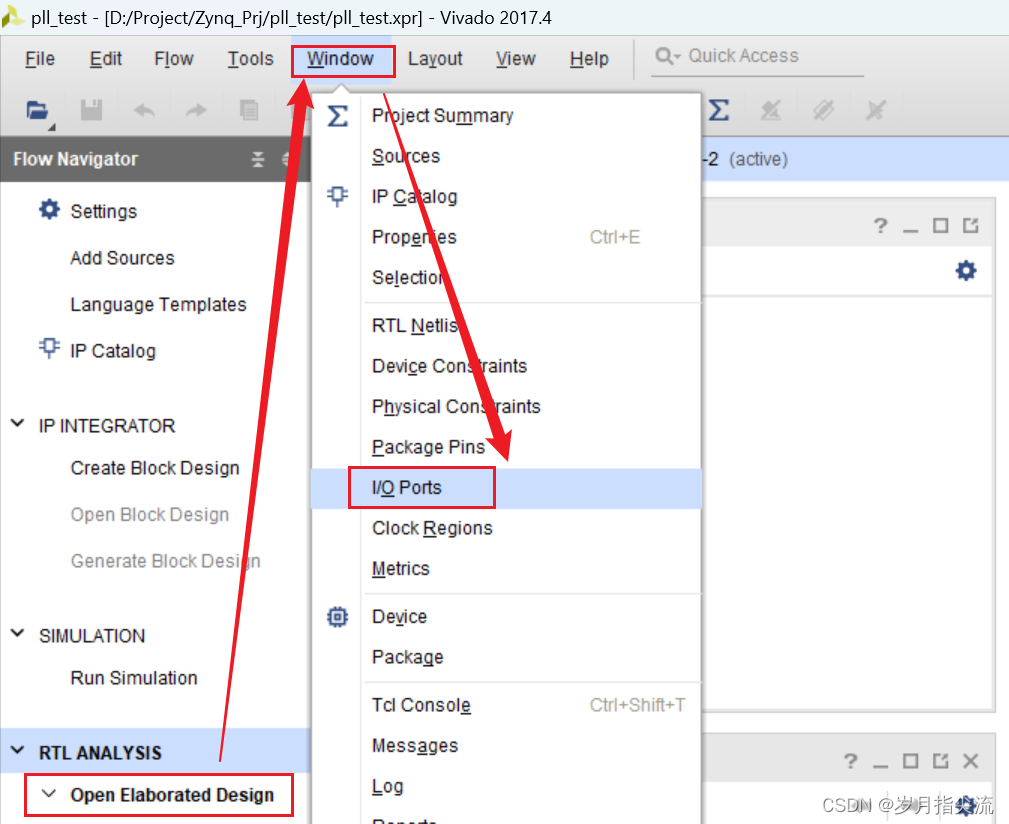

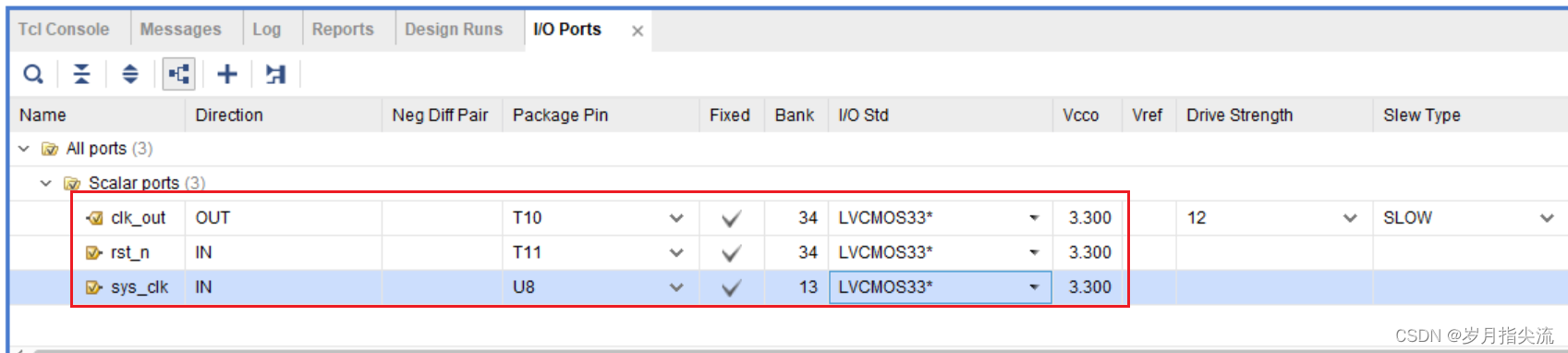

1、点击 “Open Elaborated Design”,再打开 Window 下的 I/O Ports

2、查看原理图

①、T11 -> rst_n,T0 -> clk_out

②、U18 -> sys_clk

③、因此分配情况如下:

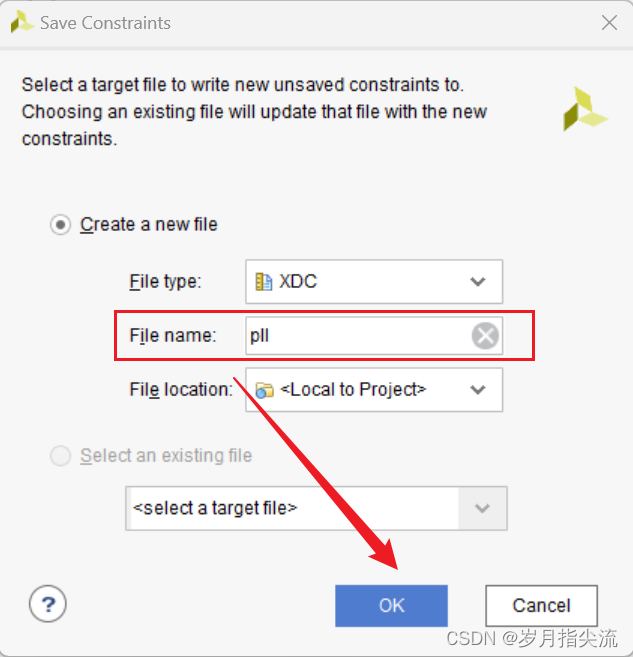

④、进行保存

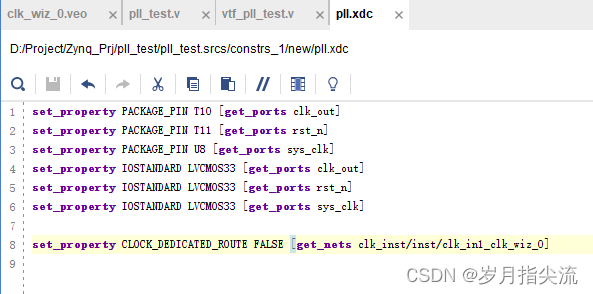

⑤、生成的 pll.xdc 文件如下图:

2、生成比特流文件

①、点击 “Generate Bitstream”,直接生成 bit 文件

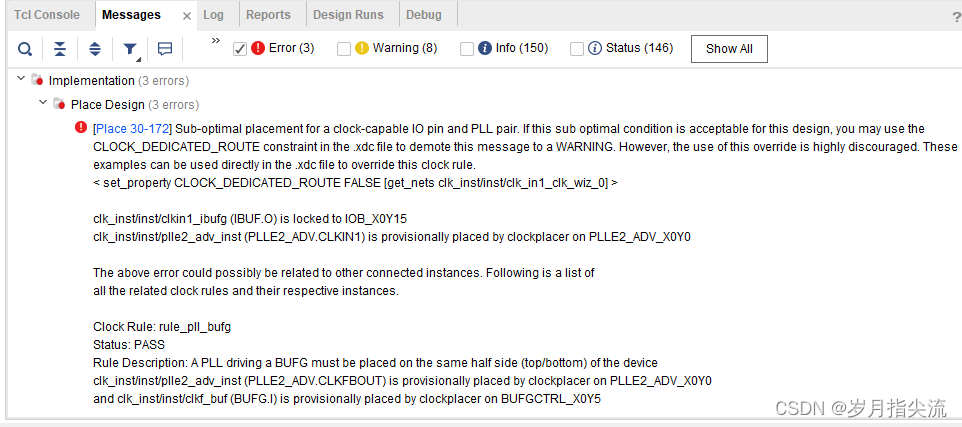

出现了如下报错:

[Place 30-172] Sub-optimal placement for a clock-capable IO pin and PLL pair. If this sub optimal condition is acceptable for this design, you may use the CLOCK_DEDICATED_ROUTE constraint in the .xdc file to demote this message to a WARNING. However, the use of this override is highly discouraged. These examples can be used directly in the .xdc file to override this clock rule.

< set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clk_inst/inst/clk_in1_clk_wiz_0] >

clk_inst/inst/clkin1_ibufg (IBUF.O) is locked to IOB_X0Y15clk_inst/inst/plle2_adv_inst (PLLE2_ADV.CLKIN1) is provisionally placed by clockplacer on PLLE2_ADV_X0Y0The above error could possibly be related to other connected instances. Following is a list of

all the related clock rules and their respective instances.Clock Rule: rule_pll_bufg

Status: PASS

Rule Description: A PLL driving a BUFG must be placed on the same half side (top/bottom) of the deviceclk_inst/inst/plle2_adv_inst (PLLE2_ADV.CLKFBOUT) is provisionally placed by clockplacer on PLLE2_ADV_X0Y0and clk_inst/inst/clkf_buf (BUFG.I) is provisionally placed by clockplacer on BUFGCTRL_X0Y5

把这条提示加入 XDC 约束文件里面即可,原理就是绕过 PAR 的检查。

set_property CLOCK_DEDICATED_ROUTE FALSE [get_nets clk_inst/inst/clk_in1_clk_wiz_0]

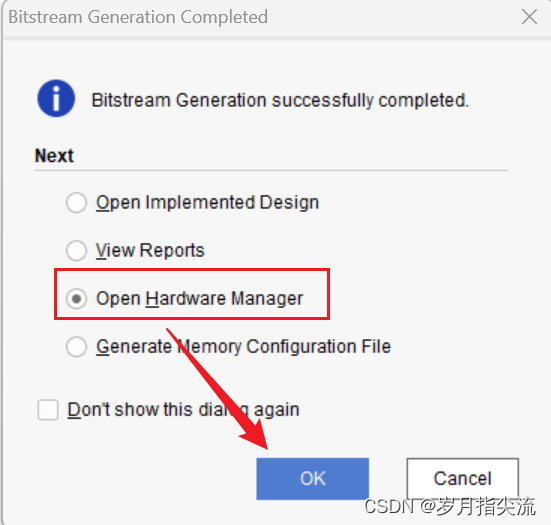

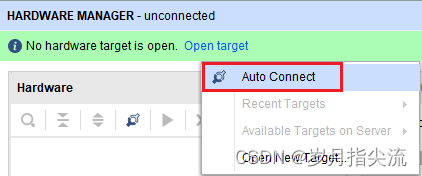

②、选择 Open Hardware Manager 并点击 OK

③、插上 fpga 仿真器及其电源,选择 Auto Connect

④、右键 xc7z020_1 -> Program Device

3、验证

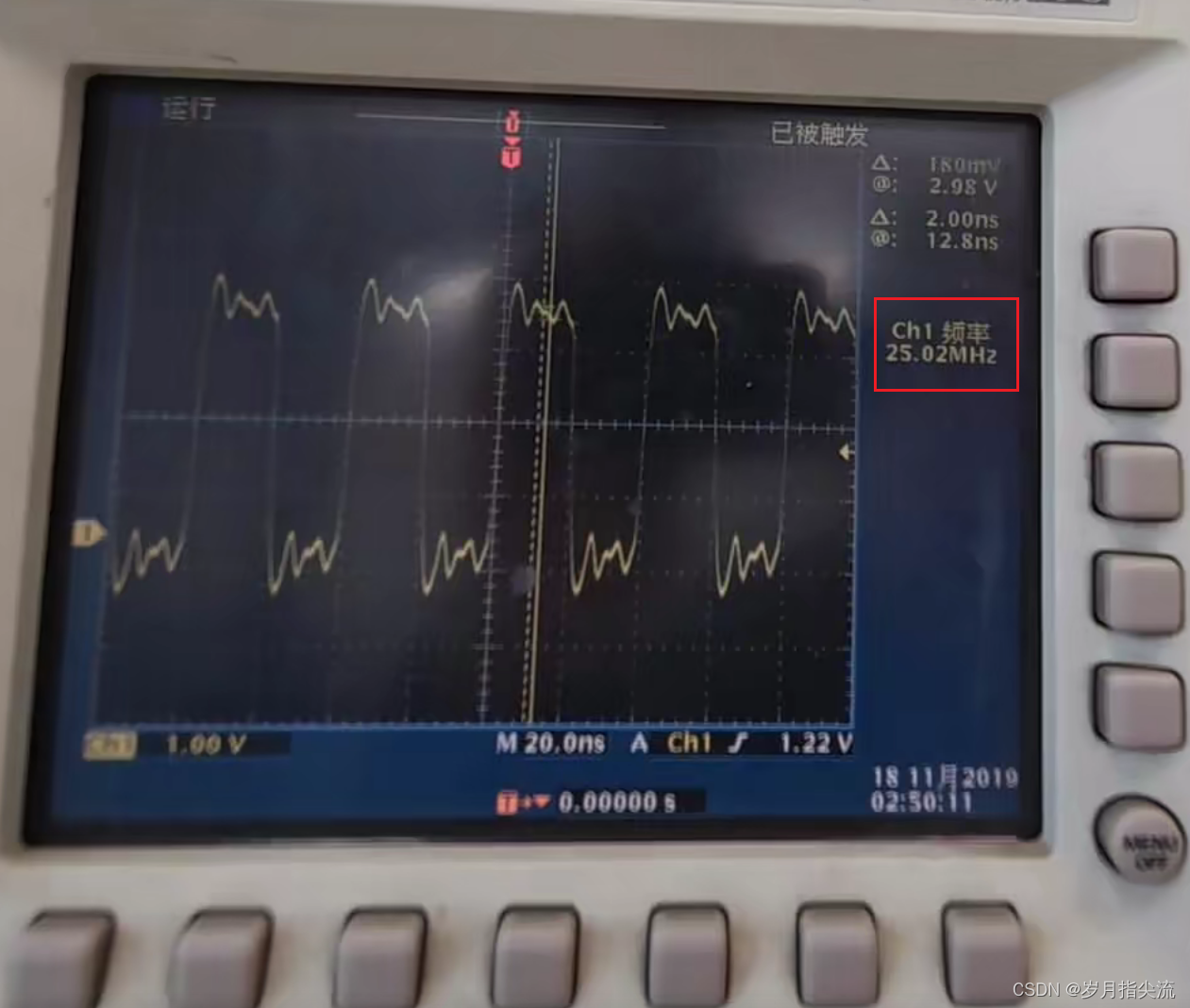

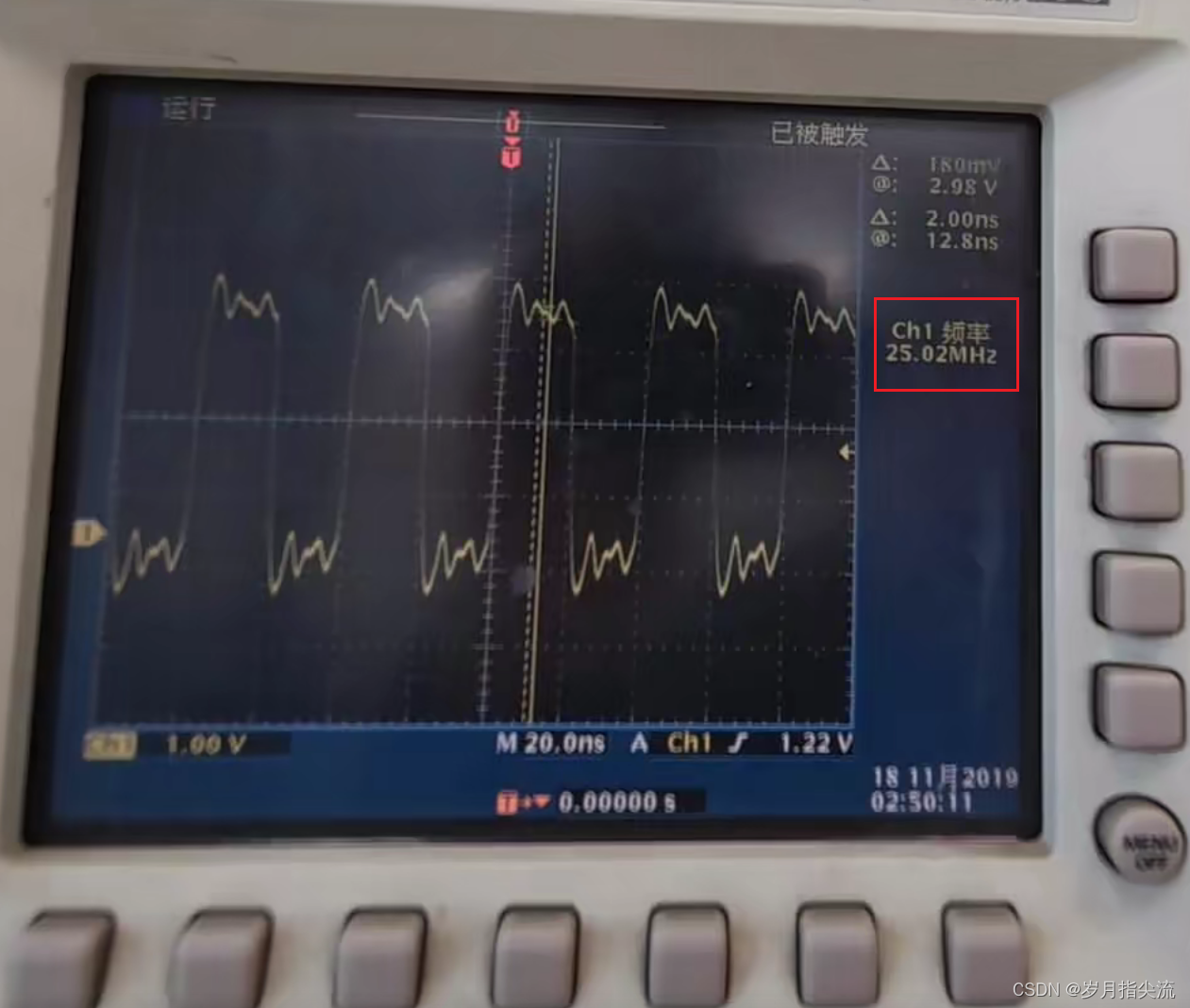

找一个示波器用探头接到 T10 引脚查看输出,可以看到 25MHz 方波信号

五、资源自取

基于vivado 2017.4 的 pll 测试

我的qq:2442391036,欢迎交流!

相关文章:

Vivado下PLL实验

文章目录 前言一、CMT(时钟管理单元)1、CMT 简介2、FPGA CMT 框图3、MMCM 框图4、PLL 框图 二、创建工程1、创建工程2、PLL IP 核配置3、进行例化 三、进行仿真1、创建仿真文件2、进行仿真设置3、进行行为级仿真 四、硬件验证1、引脚绑定2、生成比特流文…...

简单理解推挽输出和开漏输出

推挽输出原理图: 特点: 1、INT1时,OUTVDD;INT0时,OUTGND。 2、推挽输出的两种输出状态,一种是PMOS管S级端的电压VDD,一种是NMOS管S端的地GND。 开漏输出原理图: 特点: …...

C++之va_start、vasprintf、va_end应用总结(二百二十六)

简介: CSDN博客专家,专注Android/Linux系统,分享多mic语音方案、音视频、编解码等技术,与大家一起成长! 优质专栏:Audio工程师进阶系列【原创干货持续更新中……】🚀 人生格言: 人生…...

)

OpenCV自学笔记十一:形态学操作(一)

目录 1、腐蚀 2、膨胀 3、通用形态学函数 4、开运算 5、闭运算 1、腐蚀 腐蚀(Erosion)是数字图像处理中的一种形态学操作,用于消除图像中边界附近的细小区域或缩小对象的大小。腐蚀操作通过卷积输入图像与结构元素(也称为腐…...

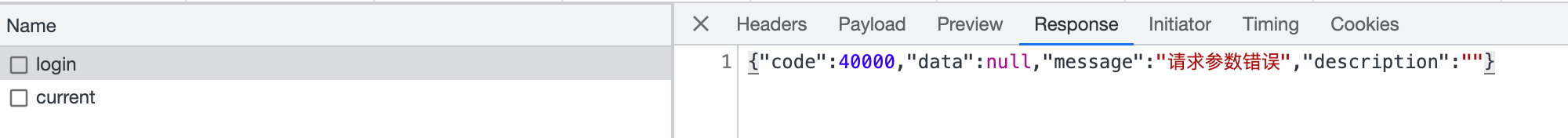

封装全局异常处理

文章目录 1 定义错误码类2 定义业务异常类3 全局异常处理器4 使用5 前端请求效果总结 1 定义错误码类 可以定义各种错误码枚举,比如业务,系统相关的报错信息 /*** 错误代码* 错误码** author leovany* date 2023/09/23*/ public enum ErrorCode {SU…...

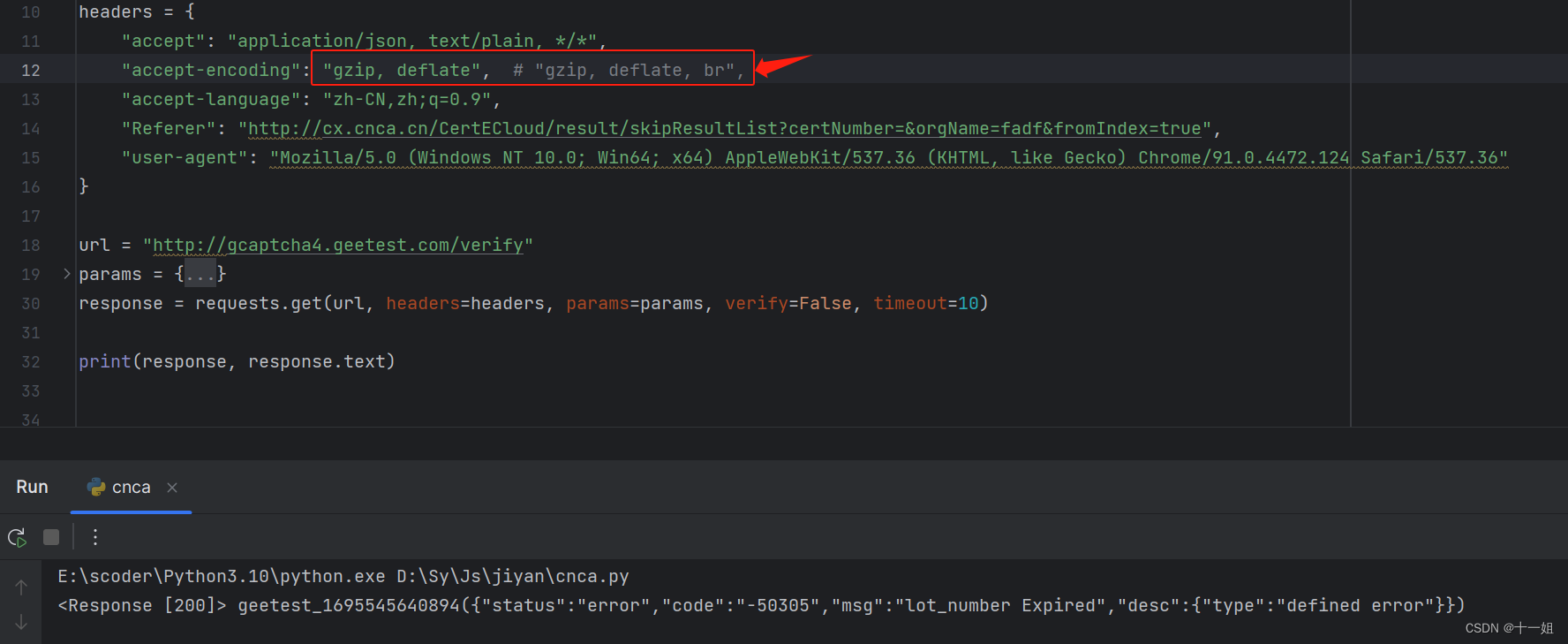

python的requests响应请求,结果乱码,即使设置了response.encoding也没有用的解决方法

一、问题 如图: 一般出现乱码,我们会有三种解决方式,如下但是图中解决了发现还是不行, response.encodingresponse.apparent_encoding通过看网页源码对response.encodingutf8指定编码格式或者直接通过response.content.decode()来获得源码 出…...

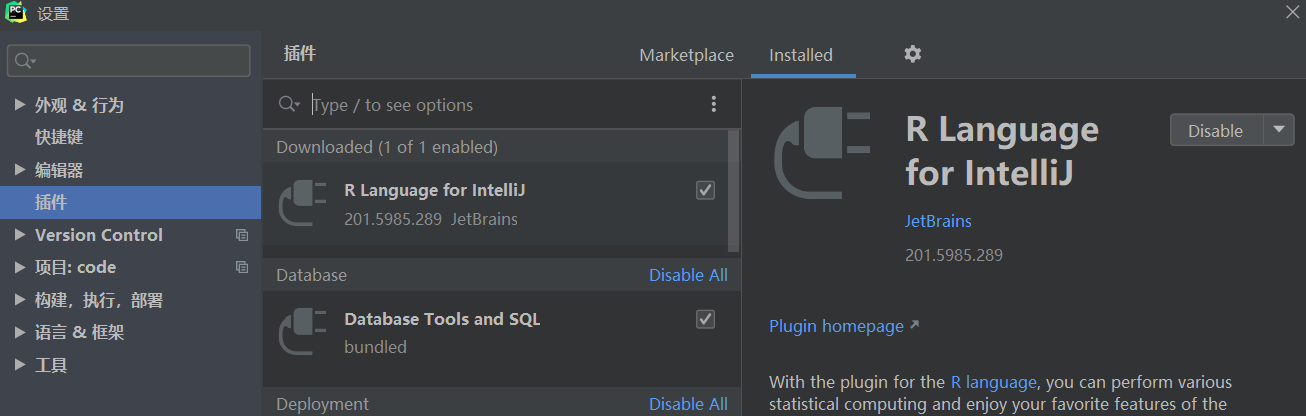

PyCharm 手动下载插件

插件模块一直加载失败,报错信息: Marketplace plugins are not loaded. Check the internet connection and refresh. 尝试了以下方法,均告失败: pip 换源Manage Plugin Repositories...HTTP 代理设置...关闭三个防火墙 最后选…...

Gnomon绑定基础(约束 IK 节点)

点约束 方向约束 父约束 目标约束 修改后 对象方向 IK控制柄 直的骨骼,指定IK怎么弯曲 直的骨骼,指定IK怎么弯曲 样条曲线 数学节点 乘除节点 混合节点 注意...

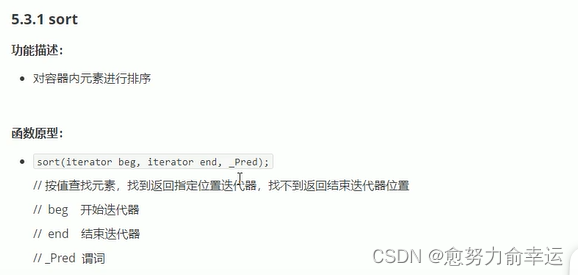

STL常用遍历,查找,算法

目录 1.遍历算法 1.1for_earch 1.2transform 2.常用查找算法 2.1find,返回值是迭代器 2.1.1查找内置数据类型 2.1.2查找自定义数据类型 2.2fin_if 按条件查找元素 2.2.1查找内置的数据类型 2.2.2查找内置数据类型 2.3查找相邻元素adjeacent_find 2.4查找指…...

)

BCC源码内容概览(1)

接前一篇文章:BCC源码编译和安装 本文参考官网中的Contents部分的介绍。 BCC源码根目录的文件,其中一些是同时包含C和Python的单个文件,另一些是.c和.py的成对文件,还有一些是目录。 跟踪(Tracing) exam…...

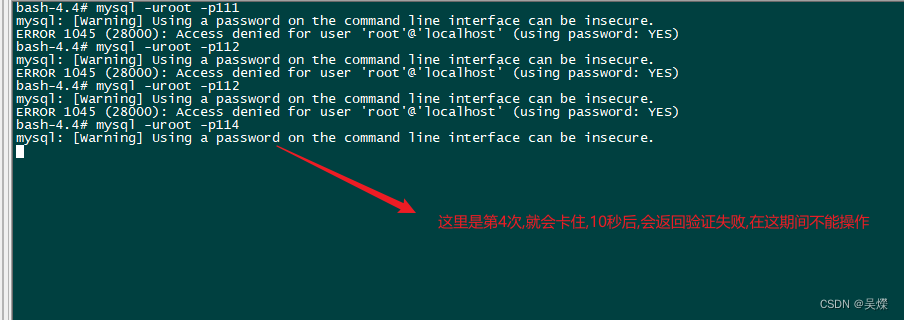

mysql限制用户登录失败次数,限制时间

mysql用户登录限制设置 mysql 需要进行用户登录次数限制,当使用密码登录超过 3 次认证链接失败之后,登录锁住一段时间,禁止登录这里使用的 mysql: 8.1.0 这种方式不用重启数据库. 配置: 首先进入到 mysql 命令行:然后需要安装两个插件: 在 mysql 命令行中执行: mysql> INS…...

)

从利用Arthas排查线上Fastjson问题到Java动态字节码技术(下)

上一篇从Arthas的源码引出了Java动态字节码技术,那么这一篇就从几种Java字节码技术出发,看看Arthas是如何通过动态字节码技术做到无侵入的源码增强; Java大部分情况下都是解释执行的,也就是解释.class文件,所以如果我们…...

Ubuntu中安装Anaconda 如何将 路径导入为全局变量

第一步:将你的anaconda 路径复制下来,在终端输入对应路径。 echo export PATH"/home/你的用户名/anaconda3/bin:$PATH" >> ~/.bashrc 第二步:在终端输入下面命令或者重启系统。 source ~/.bashrc 在对应的anaconda安装目…...

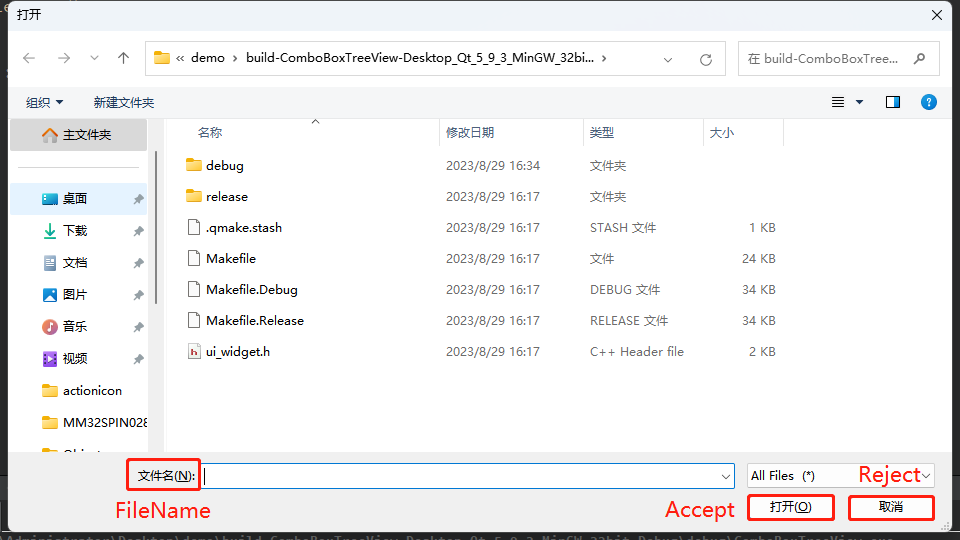

【QT】Qt的随身笔记(持续更新...)

目录 Qt 获取当前电脑桌面的路径Qt 获取当前程序运行路径Qt 创建新的文本文件txt,并写入内容如何向QPlainTextEdit 写入内容QTimerQMessageBox的使用QLatin1StringQLayoutC在c头文件中写#include类的头文件与直接写class加类名有何区别mutable关键字前向声明 QFontQ…...

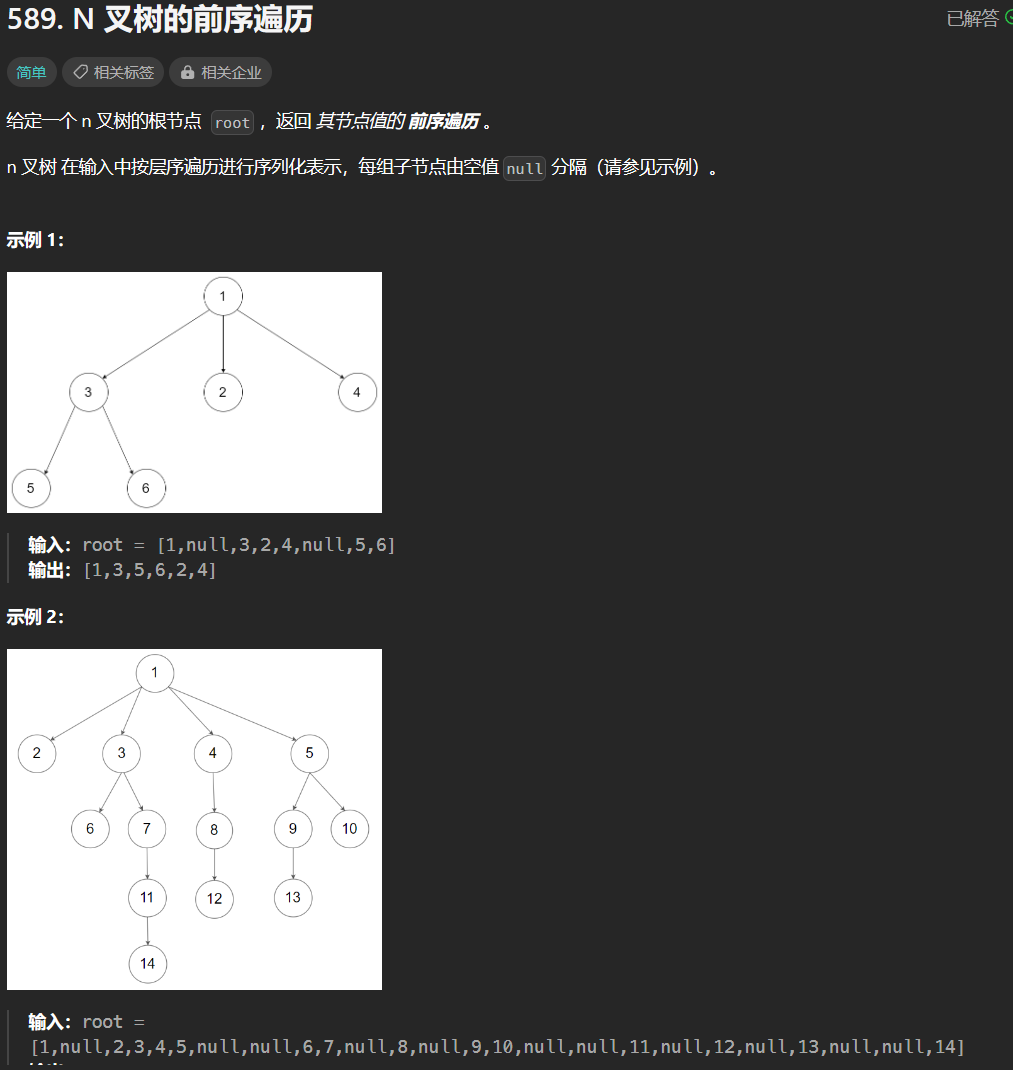

【LeetCode-简单题】589. N 叉树的前序遍历

文章目录 题目方法一:单循环栈做法方法二:递归 题目 方法一:单循环栈做法 关键在于子节点的入栈顺序,决定了子节点的出栈顺序, 因为是前序遍历 所以压栈顺序先让右边的入栈 依次往左 这样左边的节点会在栈顶 这样下次…...

Linphone3.5.2 ARM RV1109音视频对讲开发记录

Linphone3.5.2 ARM RV1109音视频对讲开发记录 说明 这是一份事后记录,主要记录的几个核心关键点,有可能很多细节没有记上,主要是方便后面自己再找回来! 版本 3.5.2 一些原因选的是这样一个旧的版本! 新的开发最好选新一些的版…...

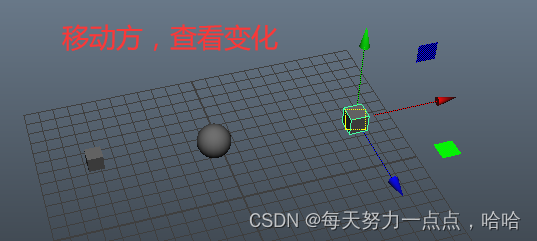

Unity用相机实现的镜子效果

首先登场 场景中的元素 mirror是镜子,挂着我们的脚本,Quad是一个面片。Camera是用来生成RenderTexture给面片的。里面的test1是我用来调试位置的球。 镜子size是大小,x是-2,为了反转一下贴图 相机直接可以禁用掉,用…...

计算机网络分类

按照覆盖范围分类 (1)个域网:通常覆盖范围在1~10m。 (2)局域网:通常覆盖范围在10m~1km。 (3)城域网:覆盖范围通常在5~50 km 。 &…...

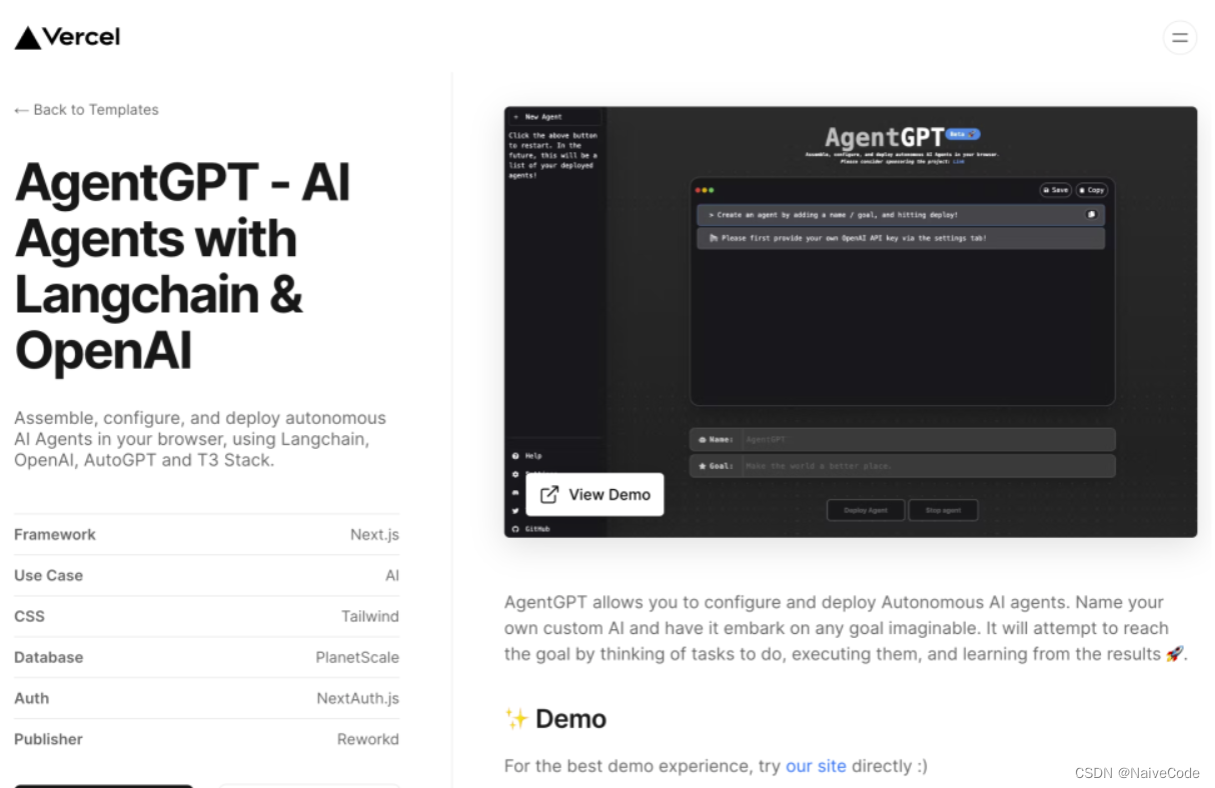

AI AIgents时代 - (三.) AutoGPT和AgentGPT

前两篇讲解了Agent的原理和组件,这节我将给大家介绍两个agent项目,给出它们的工作原理和区别,并教大家亲手尝试使用 Agents🎉 🟢 AutoGPT🤖️ 我们的老朋友,之前文章也专门写过。AutoGPT 是一…...

Jmeter接口自动化和Python接口自动化,如何选择?

选择Jmeter或Python进行接口自动化测试取决于您的具体需求和环境。以下是一些可以考虑的因素: 1. 语言熟悉度:如果您对Java更熟悉,那么Jmeter可能是更好的选择。而如果您的团队或个人对Python更熟悉,那么Python可能是更好的选择。…...

Cesium相机控制)

三维GIS开发cesium智慧地铁教程(5)Cesium相机控制

一、环境搭建 <script src"../cesium1.99/Build/Cesium/Cesium.js"></script> <link rel"stylesheet" href"../cesium1.99/Build/Cesium/Widgets/widgets.css"> 关键配置点: 路径验证:确保相对路径.…...

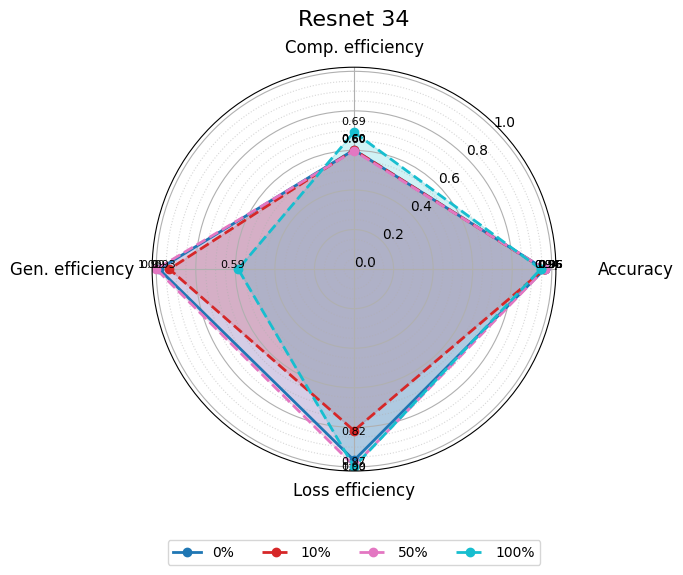

使用分级同态加密防御梯度泄漏

抽象 联邦学习 (FL) 支持跨分布式客户端进行协作模型训练,而无需共享原始数据,这使其成为在互联和自动驾驶汽车 (CAV) 等领域保护隐私的机器学习的一种很有前途的方法。然而,最近的研究表明&…...

YSYX学习记录(八)

C语言,练习0: 先创建一个文件夹,我用的是物理机: 安装build-essential 练习1: 我注释掉了 #include <stdio.h> 出现下面错误 在你的文本编辑器中打开ex1文件,随机修改或删除一部分,之后…...

蓝牙 BLE 扫描面试题大全(2):进阶面试题与实战演练

前文覆盖了 BLE 扫描的基础概念与经典问题蓝牙 BLE 扫描面试题大全(1):从基础到实战的深度解析-CSDN博客,但实际面试中,企业更关注候选人对复杂场景的应对能力(如多设备并发扫描、低功耗与高发现率的平衡)和前沿技术的…...

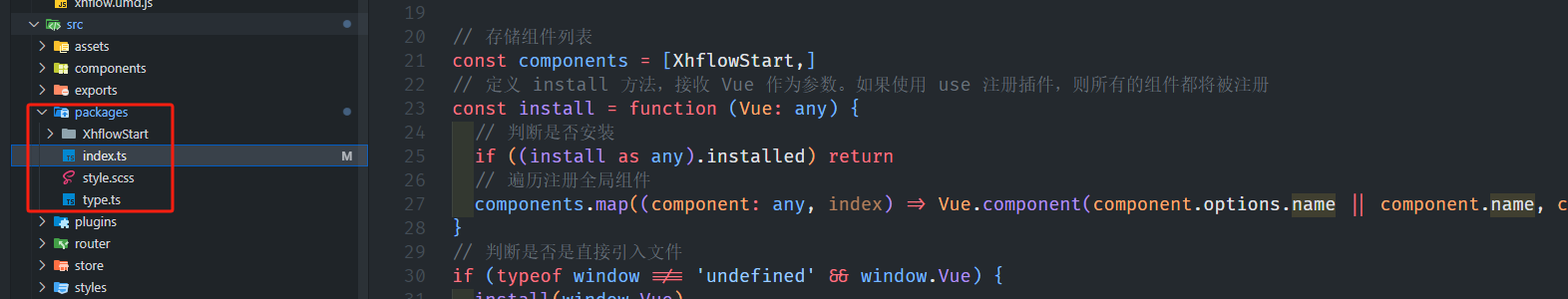

基于当前项目通过npm包形式暴露公共组件

1.package.sjon文件配置 其中xh-flowable就是暴露出去的npm包名 2.创建tpyes文件夹,并新增内容 3.创建package文件夹...

)

【服务器压力测试】本地PC电脑作为服务器运行时出现卡顿和资源紧张(Windows/Linux)

要让本地PC电脑作为服务器运行时出现卡顿和资源紧张的情况,可以通过以下几种方式模拟或触发: 1. 增加CPU负载 运行大量计算密集型任务,例如: 使用多线程循环执行复杂计算(如数学运算、加密解密等)。运行图…...

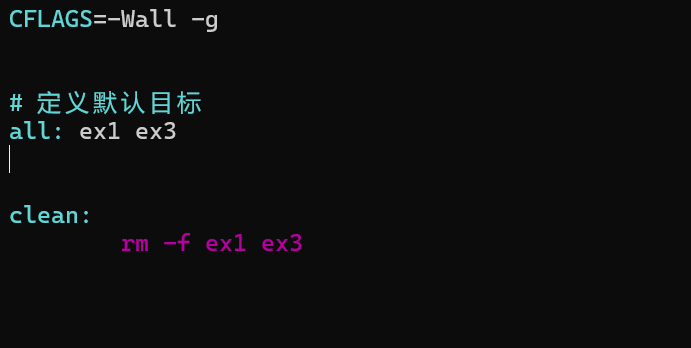

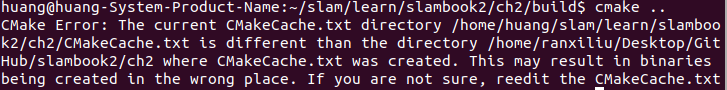

视觉slam十四讲实践部分记录——ch2、ch3

ch2 一、使用g++编译.cpp为可执行文件并运行(P30) g++ helloSLAM.cpp ./a.out运行 二、使用cmake编译 mkdir build cd build cmake .. makeCMakeCache.txt 文件仍然指向旧的目录。这表明在源代码目录中可能还存在旧的 CMakeCache.txt 文件,或者在构建过程中仍然引用了旧的路…...

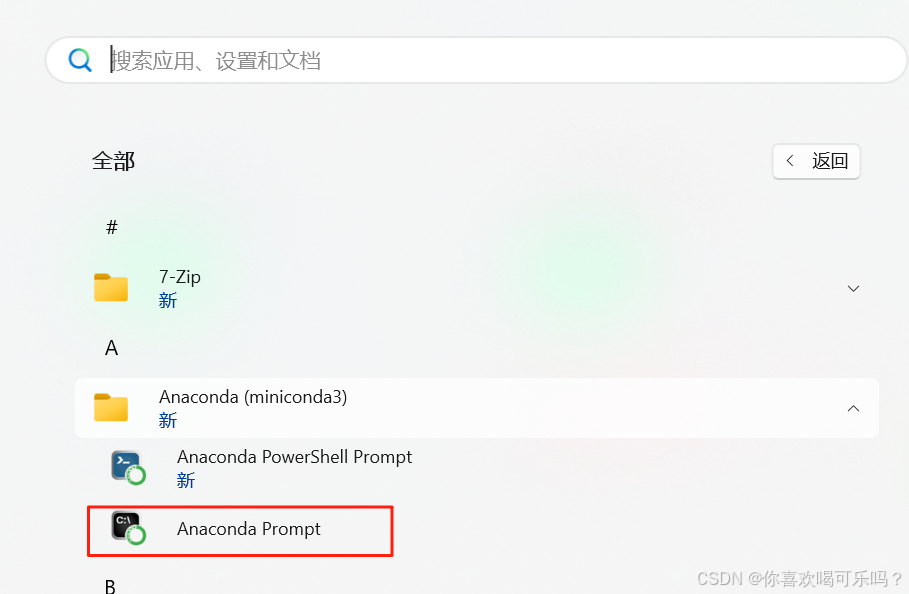

Windows安装Miniconda

一、下载 https://www.anaconda.com/download/success 二、安装 三、配置镜像源 Anaconda/Miniconda pip 配置清华镜像源_anaconda配置清华源-CSDN博客 四、常用操作命令 Anaconda/Miniconda 基本操作命令_miniconda创建环境命令-CSDN博客...

Vite中定义@软链接

在webpack中可以直接通过符号表示src路径,但是vite中默认不可以。 如何实现: vite中提供了resolve.alias:通过别名在指向一个具体的路径 在vite.config.js中 import { join } from pathexport default defineConfig({plugins: [vue()],//…...

python爬虫——气象数据爬取

一、导入库与全局配置 python 运行 import json import datetime import time import requests from sqlalchemy import create_engine import csv import pandas as pd作用: 引入数据解析、网络请求、时间处理、数据库操作等所需库。requests:发送 …...