FPGA高端项目:图像缩放+GTP+UDP架构,高速接口以太网视频传输,提供2套工程源码加QT上位机源码和技术支持

目录

- 1、前言

- 免责声明

- 本项目特点

- 2、相关方案推荐

- 我这里已有的 GT 高速接口解决方案

- 我这里已有的以太网方案

- 我这里已有的图像处理方案

- 3、设计思路框架

- 设计框图

- 视频源选择

- ADV7611 解码芯片配置及采集

- 动态彩条

- 跨时钟FIFO

- 图像缩放模块详解

- 设计框图

- 代码框图

- 2种插值算法的整合与选择

- GTP 全网最细解读

- GTP 基本结构

- GTP 发送和接收处理流程

- GTP 的参考时钟

- GTP 发送接口

- GTP 接收接口

- GTP IP核调用和使用

- 数据对齐

- 视频数据解包

- 图像缓存

- UDP数据组包

- UDP协议栈

- UDP协议栈数据发送

- IP地址、端口号的修改

- Tri Mode Ethernet MAC介绍以及移植注意事项

- RTL8211

- QT上位机和源码

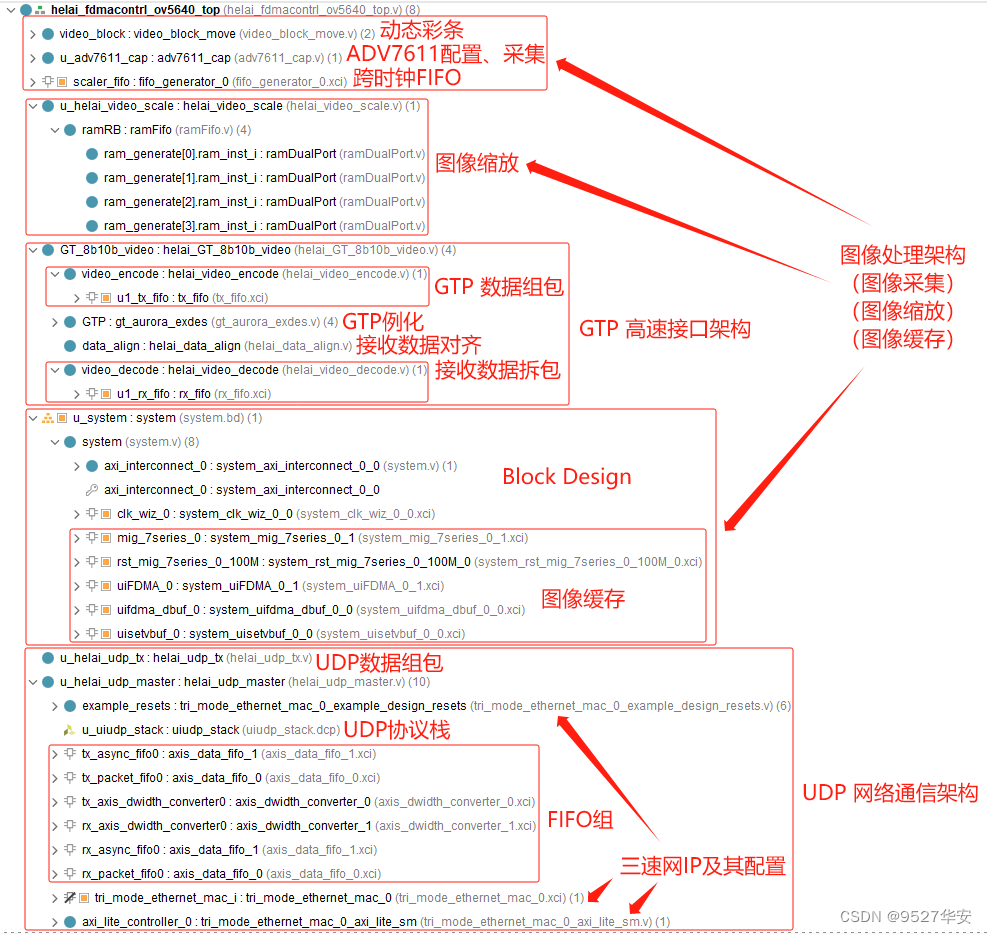

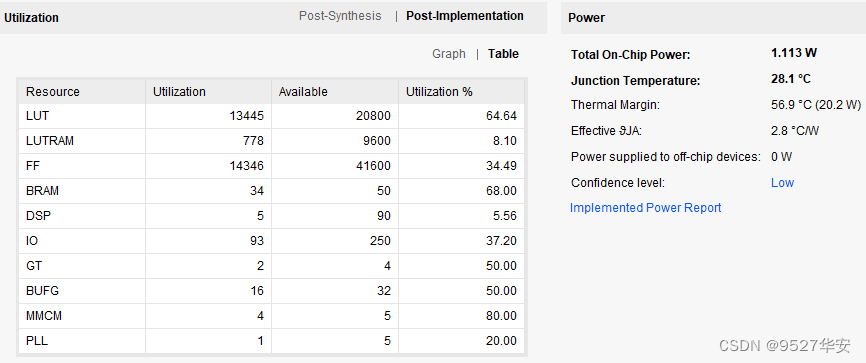

- 4、vivado工程1-->1路SFP传输

- 5、vivado工程2-->2路SFP传输

- 6、工程移植说明

- vivado版本不一致处理

- FPGA型号不一致处理

- 其他注意事项

- 7、上板调试验证并演示

- 准备工作

- ping一下

- 静态演示

- 动态演示

- 8、福利:工程源码获取

FPGA高端项目:图像缩放+GTP+UDP架构,高速接口以太网视频传输,提供2套工程源码加QT上位机源码和技术支持

1、前言

没玩过图像处理、GT高速接口、UDP网络通信,都不好意思说自己玩儿过FPGA,这是CSDN某大佬说过的一句话,鄙人深信不疑。。。GT资源是Xilinx系列FPGA的重要卖点,也是做高速接口的基础,不管是PCIE、SATA、MAC等,都需要用到GT资源来做数据高速串化和解串处理,Xilinx不同的FPGA系列拥有不同的GT资源类型,低端的A7由GTP,K7有GTX,V7有GTH,更高端的U+系列还有GTY等,他们的速度越来越高,应用场景也越来越高端。。。

本文使用Xilinx的Artix7 FPGA的GTP资源和板载的RTL8211网络PHY做GTP aurora 8b/10b编解码 UDP网络视频传输实验;视频源有两种,分别对应开发板有没有HDMI输入接口的情况;一种是使用开发板自带的HDMI输入接口,我的板子HDMI输入采用ADV7611芯片解码方案;如果你的开发板没有HDMI输入接口,或者你的开发板HDMI输入接口不是ADV7611芯片解码,则可使用代码内部生成的动态彩条模拟摄像头视频;视频源的选择通过代码顶层的define宏定义进行,上电默认使用HDMI输入作为视频源;FPGA采集到视频数据后,首先进行图像缩放,将输入分辨率为19201080的视频缩小为1280720,然后将视频数据进行数据组包,然后调用GTP IP核,配置为8b/10b编解码模式,将组包的视频数据送入GTP编码发送出去,然后再GTP解码接收,用verilog编写视频数据对齐和视频数据解包模块解析出有效的视频数据,并恢复行场等时序,然后将视频送到DDR3进行缓存,再读出视频送UDP协议栈进行UDP协议编码,再调用Xilinx官方的Tri Mode Ethernet MAC作为MAC层,最后通过板载的RTL8211将视频通过网络数据形式发送PC,PC端用QT上位机接收图像并显示出来;

提供2套vivado2019.1版本的工程源码;2套工程的区别在于使用1个SFP光口还是使用2个SFP光口,详情请看第3章节的设计思路框架;工程代码可综合编译上板调试,可直接项目移植,适用于在校学生、研究生项目开发,也适用于在职工程师做学习提升,可应用于医疗、军工等行业的高速接口或图像处理领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

免责声明

本工程及其源码即有自己写的一部分,也有网络公开渠道获取的一部分(包括CSDN、Xilinx官网、Altera官网等等),若大佬们觉得有所冒犯,请私信批评教育;基于此,本工程及其源码仅限于读者或粉丝个人学习和研究,禁止用于商业用途,若由于读者或粉丝自身原因用于商业用途所导致的法律问题,与本博客及博主无关,请谨慎使用。。。

本项目特点

本项目是一个综合性的高端项目,从宏观上可以分为硬件和软件的结合,硬件指的是FPGA逻辑的实现,软件指的是PC端QT上位机的实现;从FPGA应用领域上可以分为图像处理、高速接口、网络传输三大领域,这三大领域是目前FPGA的主流应用,图像处理属于基础应用,网络传输属于中等应用,高速接口属于高端应用;这个工程直接将三者结合,在实际应用中很有需求,但市面上会的人很少。。。

2、相关方案推荐

我这里已有的 GT 高速接口解决方案

我的主页有FPGA GT 高速接口专栏,该专栏有 GTP 、 GTX 、 GTH 、 GTY 等GT 资源的视频传输例程和PCIE传输例程,其中 GTP基于A7系列FPGA开发板搭建,GTX基于K7或者ZYNQ系列FPGA开发板搭建,GTH基于KU或者V7系列FPGA开发板搭建,GTY基于KU+系列FPGA开发板搭建;以下是专栏地址:

点击直接前往

我这里已有的以太网方案

目前我这里有大量UDP协议的工程源码,包括UDP数据回环,视频传输,AD采集传输等,也有TCP协议的工程,还有RDMA的NIC 10G 25G 100G网卡工程源码,对网络通信有需求的兄弟可以去看看:直接点击前往

其中10G万兆TCP协议的工程博客如下:

直接点击前往

我这里已有的图像处理方案

目前我这里已有的图像处理方案有很多,包括图像缩放、图像拼接、图像旋转、图像识别跟踪、图像去雾等等,所有工程均在自己的板子上跑通验证过,保证代码的可靠性,对图像处理感兴趣或有项目需求的兄弟可以参考我的图像处理专栏,里面包含了上述工程源码的详细设计方案和验证视频演示:直接点击前往

3、设计思路框架

本文使用Xilinx的Artix7 FPGA的GTP资源和板载的RTL8211网络PHY做GTP aurora 8b/10b编解码 UDP网络视频传输实验;视频源有两种,分别对应开发板有没有HDMI输入接口的情况;一种是使用开发板自带的HDMI输入接口,我的板子HDMI输入采用ADV7611芯片解码方案;如果你的开发板没有HDMI输入接口,或者你的开发板HDMI输入接口不是ADV7611芯片解码,则可使用代码内部生成的动态彩条模拟摄像头视频;视频源的选择通过代码顶层的define宏定义进行,上电默认使用HDMI输入作为视频源;FPGA采集到视频数据后,首先进行图像缩放,将输入分辨率为19201080的视频缩小为1280720,然后将视频数据进行数据组包,然后调用GTP IP核,配置为8b/10b编解码模式,将组包的视频数据送入GTP编码发送出去,然后再GTP解码接收,用verilog编写视频数据对齐和视频数据解包模块解析出有效的视频数据,并恢复行场等时序,然后将视频送到DDR3进行缓存,再读出视频送UDP协议栈进行UDP协议编码,再调用Xilinx官方的Tri Mode Ethernet MAC作为MAC层,最后通过板载的RTL8211将视频通过网络数据形式发送PC,PC端用QT上位机接收图像并显示出来;

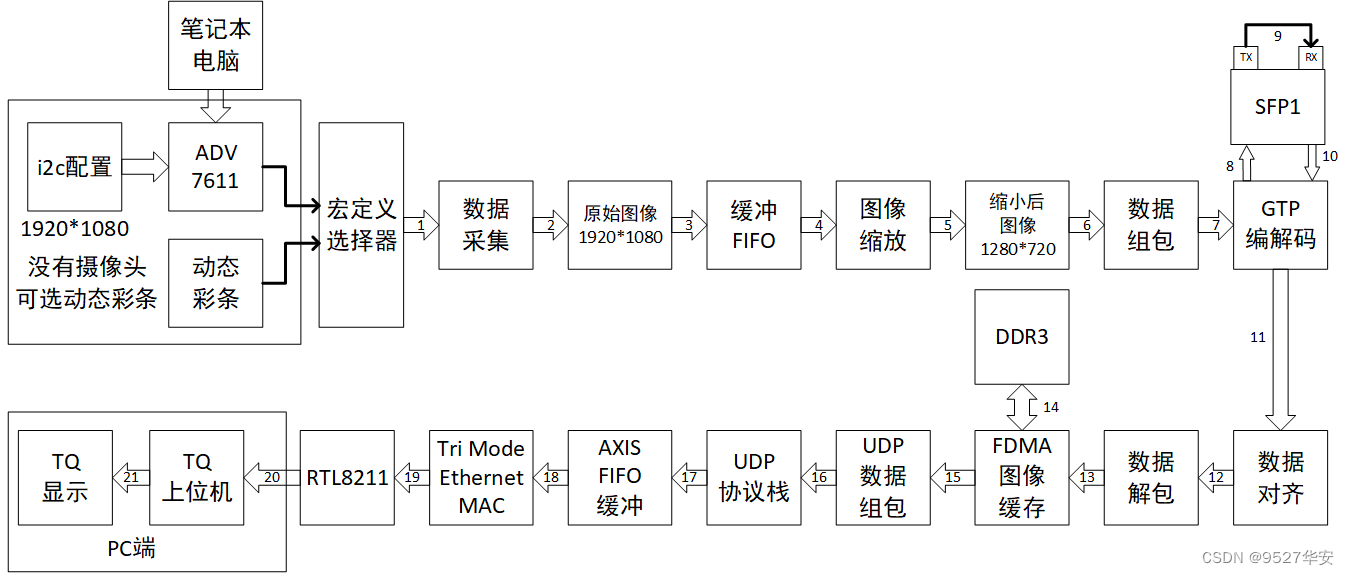

设计框图

使用1个SFP光口框图如下:

注意:框图中的数字表示数据流向的顺序;

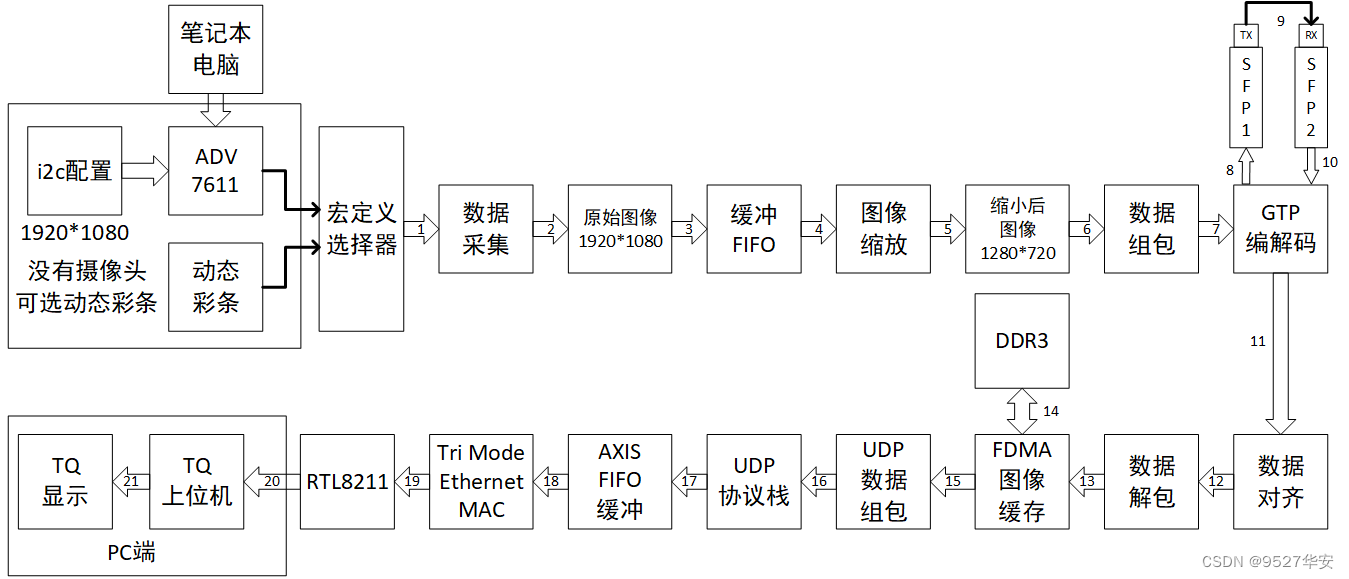

使用2个SFP光口框图如下:

注意:框图中的数字表示数据流向的顺序;

视频源选择

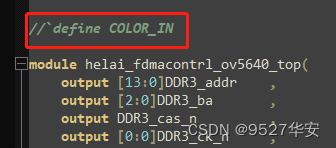

视频源有两种,分别对应开发板有没有HDMI输入接口的情况;一种是使用开发板自带的HDMI输入接口,我的板子HDMI输入采用IT6802芯片解码方案;如果你的开发板没有HDMI输入接口,或者你的开发板HDMI输入接口不是IT6802芯片解码,则可使用代码内部生成的动态彩条模拟摄像头视频;视频源的选择通过代码顶层的define宏定义进行,上电默认使用HDMI输入作为视频源;视频源的选择通过代码顶层的`define宏定义进行;如下:

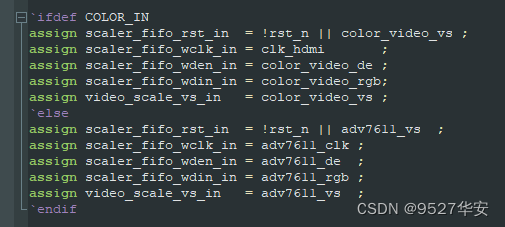

选择逻辑代码部分如下:

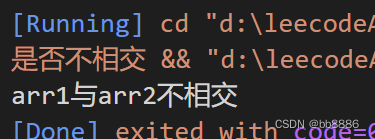

选择逻辑如下:

当(注释) define COLOR_IN时,输入源视频是HDMI输入;

当(不注释) define COLOR_IN时,输入源视频是动态彩条;

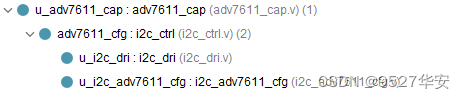

ADV7611 解码芯片配置及采集

ADV7611 解码芯片需要i2c配置才能使用,ADV7611 解码芯片配置及采集这两部分均用verilog代码模块实现,代码位置如下:

代码中配置为1920x1080分辨率;

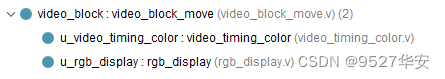

动态彩条

动态彩条可配置为不同分辨率的视频,视频的边框宽度,动态移动方块的大小,移动速度等都可以参数化配置,我这里配置为辨率1920x1080,动态彩条模块代码位置和顶层接口和例化如下:

跨时钟FIFO

跨时钟FIFO的作用是为了解决跨时钟域的问题,当视频不进行缩放时不存在视频跨时钟域问题,但当视频缩小或放大时就存在此问题,用FIFO缓冲可以使图像缩放模块每次读到的都是有效的输入数据,注意,原视频的输入时序在这里就已经被打乱了;

图像缩放模块详解

因为我们的QT上位机目前只支持1280x720,所以才需要缩放,即从输入的1920x1080分辨率缩小为1280x720;用笔记本电脑模拟HDMI视频输入源;

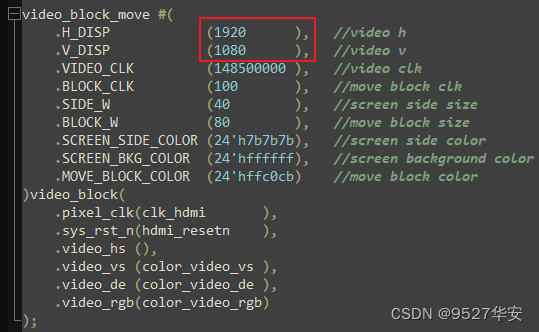

设计框图

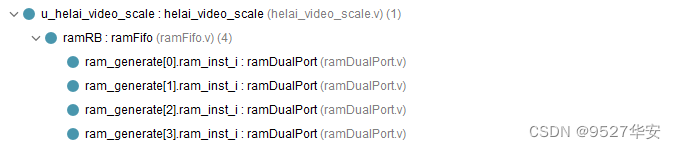

本设计将常用的双线性插值和邻域插值算法融合为一个代码中,通过输入参数选择某一种算法;代码使用纯verilog实现,没有任何ip,可在Xilinx、Intel、国产FPGA间任意移植;代码以ram和fifo为核心进行数据缓存和插值实现,设计架构如下:

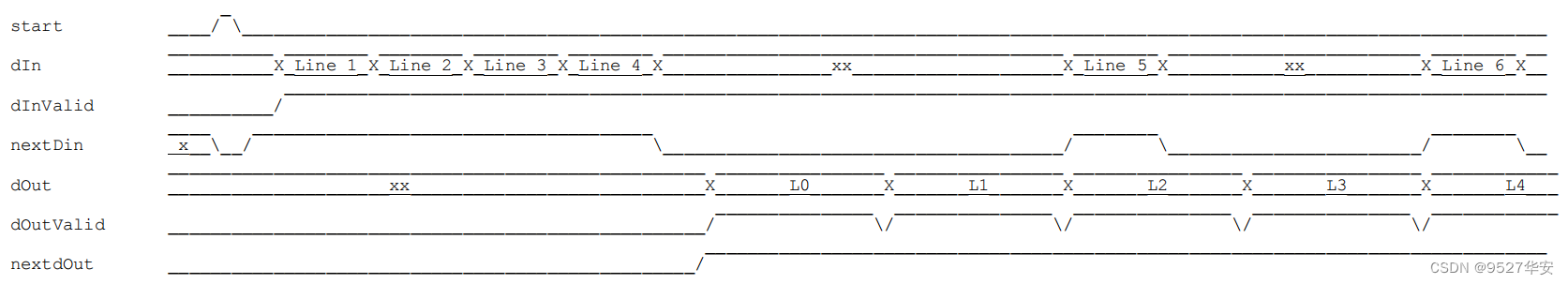

视频输入时序要求如下:

输入像素数据在dInValid和nextDin同时为高时方可改变;

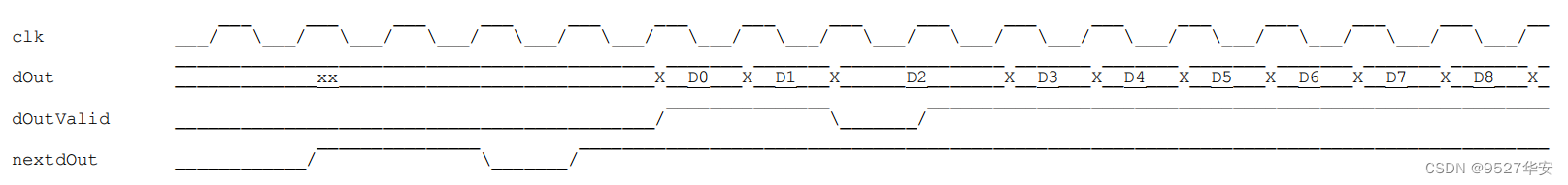

视频输出时序要求如下:

输出像素数据在dOutValid 和nextdOut同时为高时才能输出;

代码框图

代码使用纯verilog实现,没有任何ip,可在Xilinx、Intel、国产FPGA间任意移植;

图像缩放的实现方式很多,最简单的莫过于Xilinx的HLS方式实现,用opencv的库,以c++语言几行代码即可完成,关于HLS实现图像缩放请参考我之前写的文章HLS实现图像缩放

网上也有其他图像缩放例程代码,但大多使用了IP,导致在其他FPGA器件上移植变得困难,通用性不好;相比之下,本设计代码就具有通用性;代码架构如图;

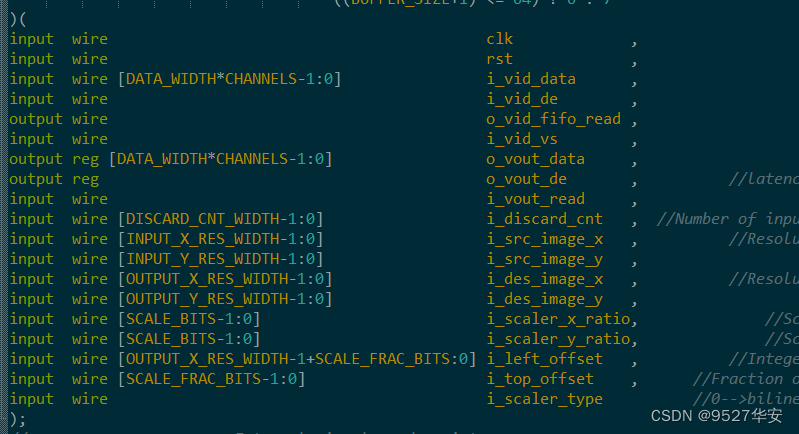

其中顶层接口部分如下:

2种插值算法的整合与选择

本设计将常用的双线性插值和邻域插值算法融合为一个代码中,通过输入参数选择某一种算法;

具体选择参数如下:

input wire i_scaler_type //0-->bilinear;1-->neighbor

通过输入i_scaler_type 的值即可选择;

输入0选择双线性插值算法;

输入1选择邻域插值算法;

关于这两种算法的数学差异,请参考我之前写的文章HLS实现图像缩放

GTP 全网最细解读

关于GTP介绍最详细的肯定是Xilinx官方的《ug482_7Series_GTP_Transceivers》,我们以此来解读:

《ug482_7Series_GTP_Transceivers》的PDF文档我已放在了资料包里,文章末尾有获取方式;

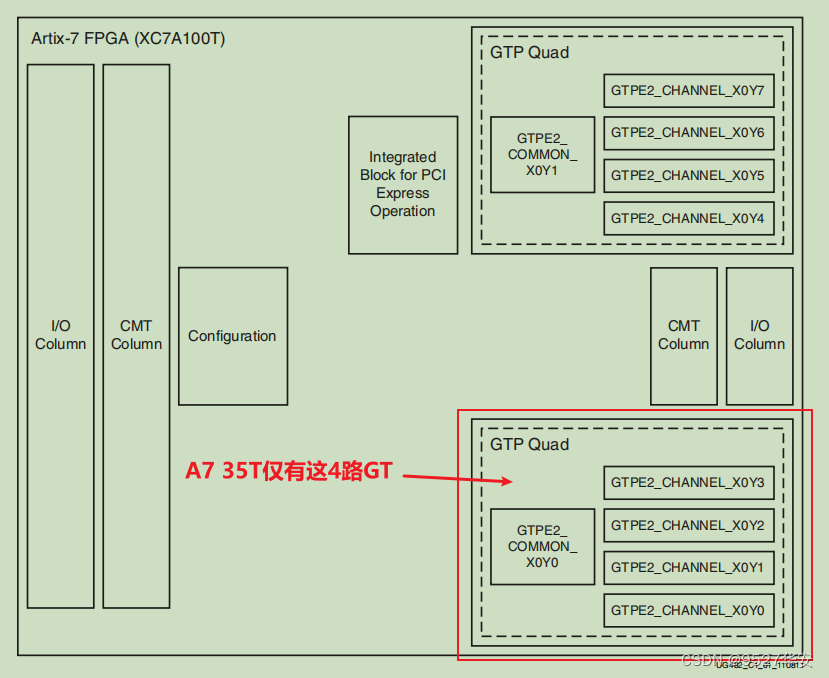

我用到的开发板FPGA型号为Xilinx Artix7 xc7a35tfgg484-2;带有4路GTP资源,每通道的收发速度为 500 Mb/s 到 6.6 Gb/s 之间。GTP 收发器支持不同的串行传输接口或协议,比如 PCIE 1.1/2.0 接口、万兆网 XUAI 接口、OC-48、串行 RapidIO 接口、 SATA(Serial ATA) 接口、数字分量串行接口(SDI)等等;

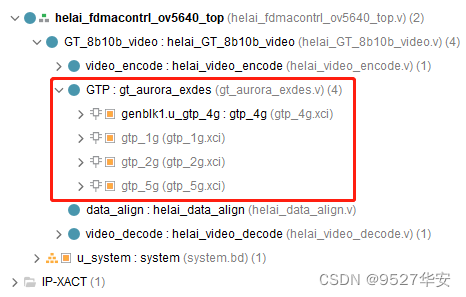

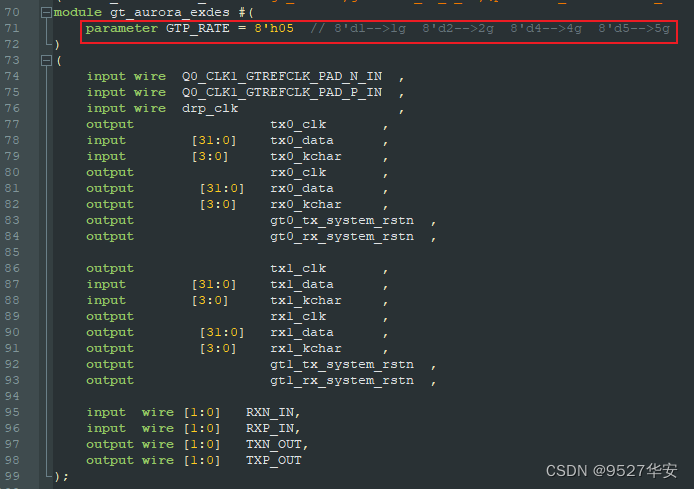

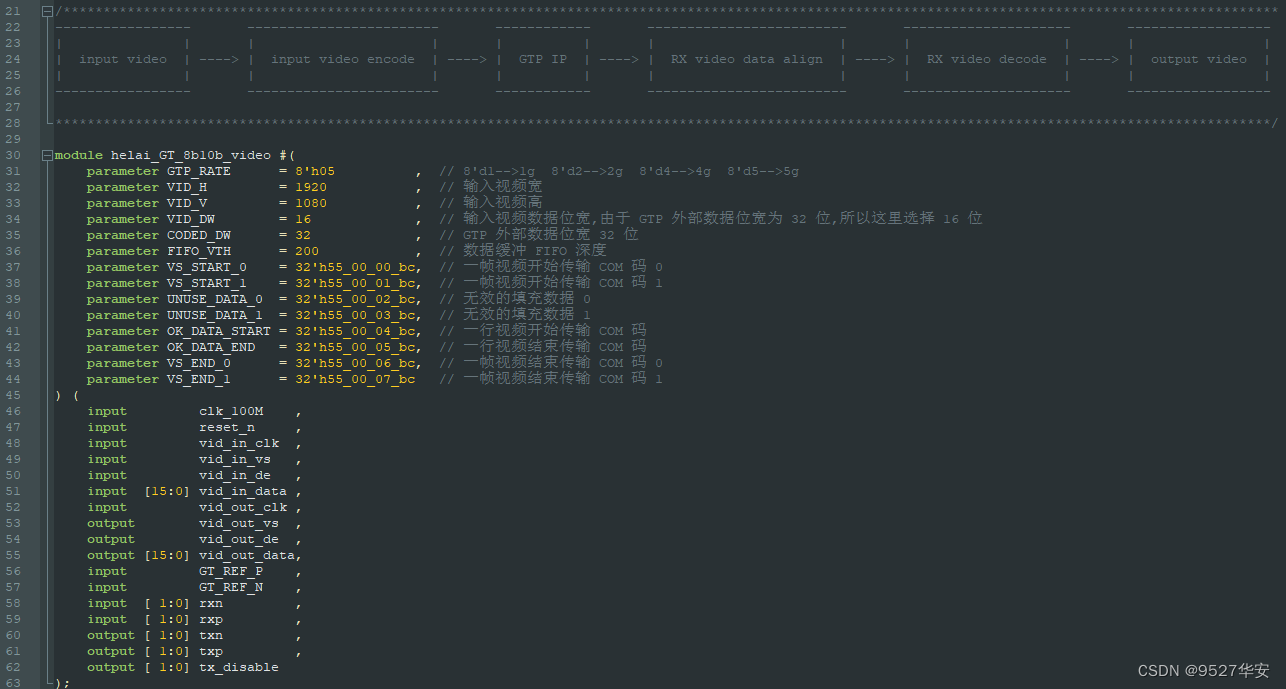

调用GTP做aurora 8b/10b协议的数据编解码,前面已经对GTP做了详细概述,这里不讲;代码位置如下:

需要注意的是,我一共调用了5个GTP,速率分别为1G、2G、4G、5G;代码中用一个参数选择速率,如下:

GTP_RATE=8’d1,GTP以1G线速率运行;

GTP_RATE=8’d2,GTP以2G线速率运行;

GTP_RATE=8’d4,GTP以4G线速率运行;

GTP_RATE=8’d5,GTP以5G线速率运行;

以我的测试来看,GTP以4G线速率运行时视频传输效果最佳;

GTP 基本结构

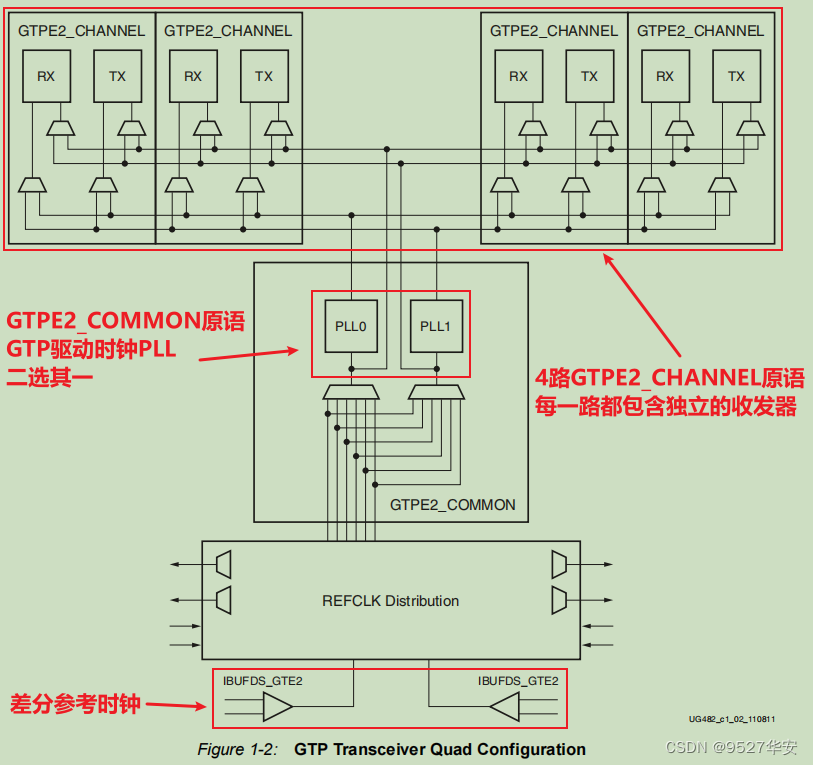

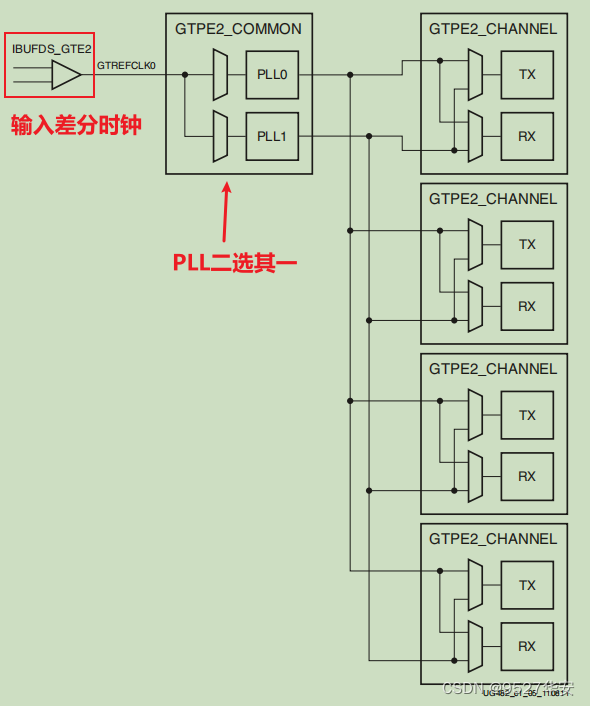

Xilinx 以 Quad 来对串行高速收发器进行分组,四个串行高速收发器和一个 COMMOM(QPLL)组成一个 Quad,每一个串行高速收发器称为一个 Channel(通道),下图为四路 GTP 收发器在Artix-7 FPGA 芯片中的示意图:《ug482_7Series_GTP_Transceivers》第13页;

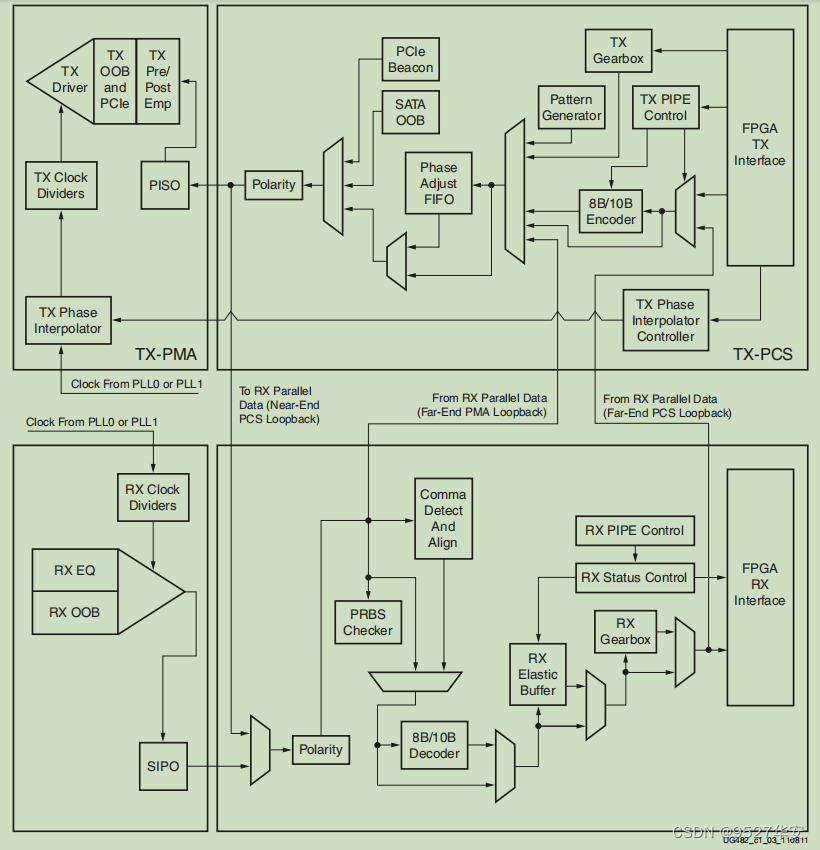

GTP 的具体内部逻辑框图如下所示,它由四个收发器通道 GTPE2_CHANNEL原语 和一个GTPE2_COMMON 原语 组成。每路 GTPE2_CHANNEL 包含发送电路 TX 和接收电路 RX;《ug482_7Series_GTP_Transceivers》第14页;

每个 GTPE2_CHANNEL 的逻辑电路如下图所示:《ug482_7Series_GTP_Transceivers》第15页;

GTPE2_CHANNEL 的发送端和接收端功能是独立的,均由 PMA(Physical Media Attachment,物理媒介适配层)和 PCS(Physical Coding Sublayer,物理编码子层)两个子层组成。其中 PMA 子层包含高速串并转换(Serdes)、预/后加重、接收均衡、时钟发生器及时钟恢复等电路。PCS 子层包含8B/10B 编解码、缓冲区、通道绑定和时钟修正等电路。

这里说多了意义不大,因为没有做过几个大的项目是不会理解这里面的东西的,对于初次使用或者想快速使用者而言,更多的精力应该关注IP核的调用和使用,后面我也会重点将到IP核的调用和使用;

GTP 发送和接收处理流程

首先用户逻辑数据经过 8B/10B 编码后,进入一个发送缓存区(Phase Adjust FIFO),该缓冲区主要是 PMA 子层和 PCS 子层两个时钟域的时钟隔离,解决两者时钟速率匹配和相位差异的问题,最后经过高速 Serdes 进行并串转换(PISO),有必要的话,可以进行预加重(TX Pre-emphasis)、后加重。值得一提的是,如果在 PCB 设计时不慎将 TXP 和 TXN 差分引脚交叉连接,则可以通过极性控制(Polarity)来弥补这个设计错误。接收端和发送端过程相反,相似点较多,这里就不赘述了,需要注意的是 RX 接收端的弹性缓冲区,其具有时钟纠正和通道绑定功能。这里的每一个功能点都可以写一篇论文甚至是一本书,所以这里只需要知道个概念即可,在具体的项目中回具体用到,还是那句话:对于初次使用或者想快速使用者而言,更多的精力应该关注IP核的调用和使用。

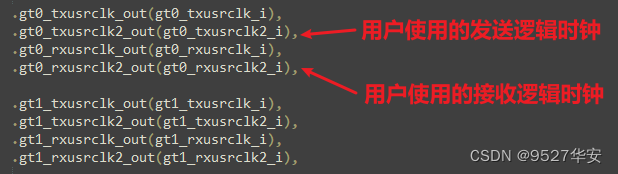

GTP 的参考时钟

GTP 模块有两个差分参考时钟输入管脚(MGTREFCLK0P/N 和 MGTREFCLK1P/N),作为 GTP模块的参考时钟源,用户可以自行选择。一般的A7系列开发板上,都有一路 125Mhz 的 GTP 参考时钟连接到 MGTREFCLK0/1上,作为 GTP 的参考时钟。差分参考时钟通过IBUFDS 模块转换成单端时钟信号进入到 GTPE2_COMMOM 的 PLL0 和 PLL1 中,产生 TX 和 RX 电路中所需的时钟频率。TX 和 RX 收发器速度相同的话,TX 电路和 RX 电路可以使用同一个 PLL 产生的时钟,如果 TX 和 RX收发器速度不相同的话,需要使用不同的 PLL 时钟产生的时钟。参考时钟这里Xilinx给出的GT参考例程已经做得很好了,我们调用时其实不用修改;GTP 的参考时钟结构图如下:《ug482_7Series_GTP_Transceivers》第21页;

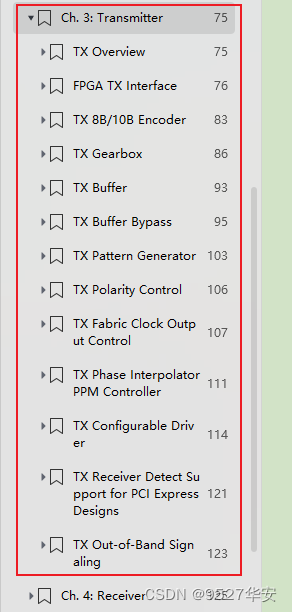

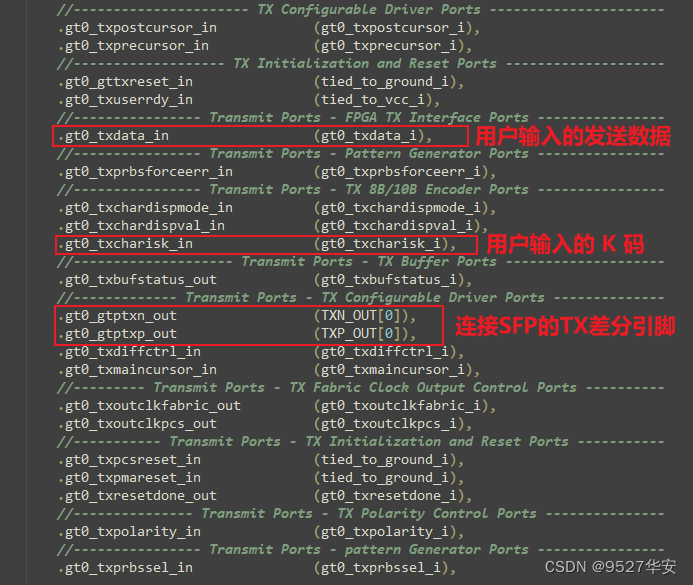

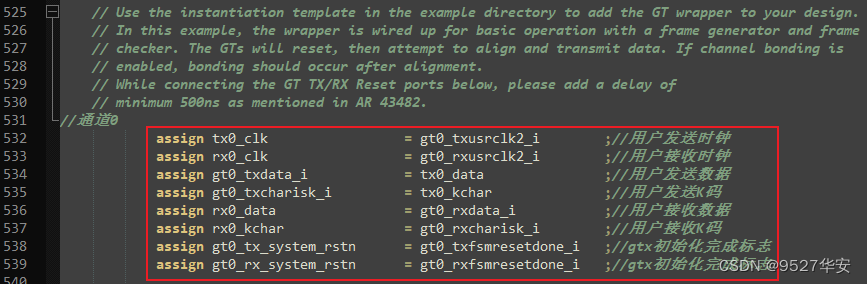

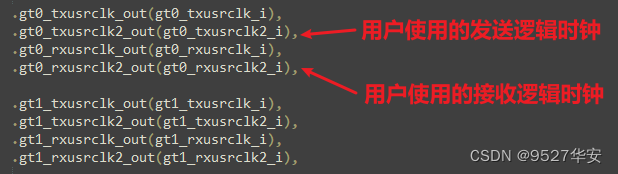

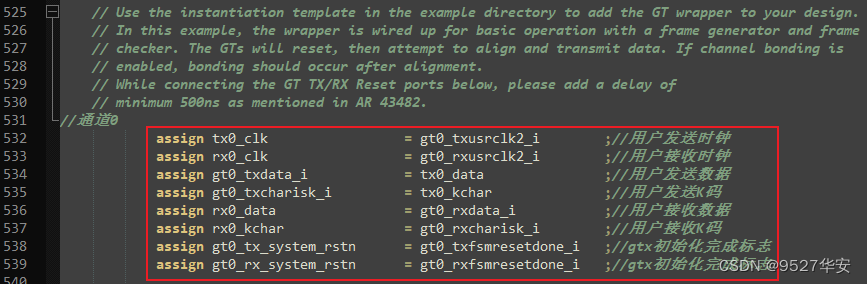

GTP 发送接口

《ug482_7Series_GTP_Transceivers》的第75到123页详细介绍了发送处理流程,其中大部分内容对于用户而言可以不去深究,因为手册讲的基本都是他自己的设计思想,留给用户可操作的接口并不多,基于此思路,我们重点讲讲GTP例化时留给用户的发送部分需要用到的接口;

用户只需要关心发送接口的时钟和数据即可,GTP例化模块的这部分接口如下:

在代码中我已为你们重新绑定并做到了模块的顶层,代码部分如下:

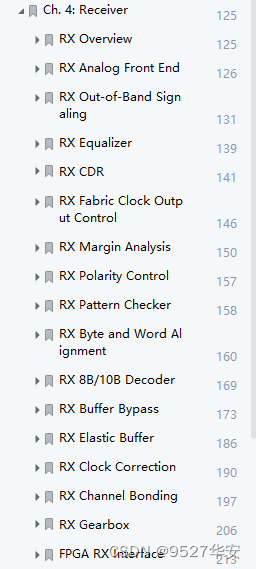

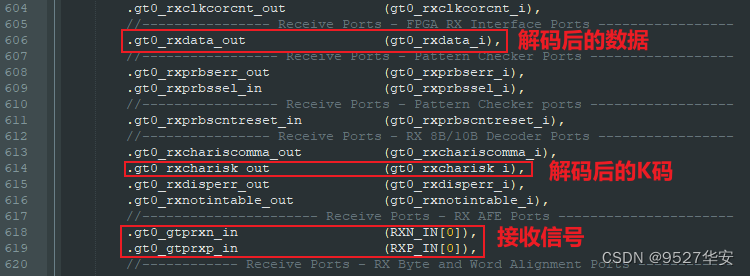

GTP 接收接口

《ug482_7Series_GTP_Transceivers》的第125到213页详细介绍了发送处理流程,其中大部分内容对于用户而言可以不去深究,因为手册讲的基本都是他自己的设计思想,留给用户可操作的接口并不多,基于此思路,我们重点讲讲GTP例化时留给用户的发送部分需要用到的接口;

用户只需要关心接收接口的时钟和数据即可,GTP例化模块的这部分接口如下:

在代码中我已为你们重新绑定并做到了模块的顶层,代码部分如下:

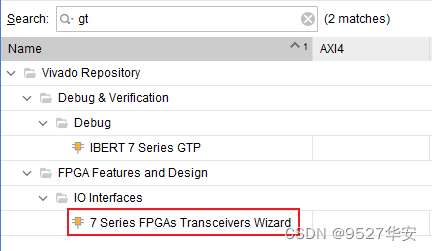

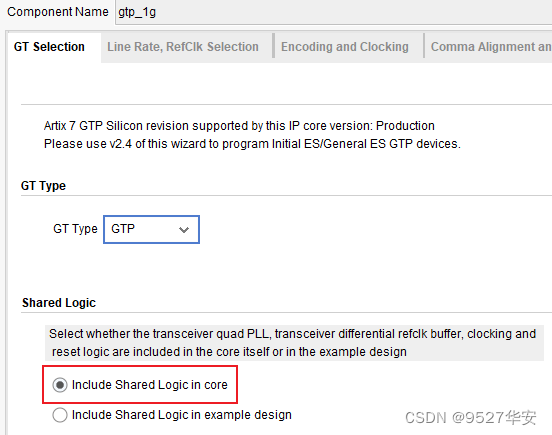

GTP IP核调用和使用

有别于网上其他博主的教程,我个人喜欢用如下图的共享逻辑:

这样选择的好处有两个,一是方便DRP变速,二是便于IP核的修改,修改完IP核后直接编译即可,不再需要打开example工程,再复制下面的一堆文件放到自己的工程什么的,玩儿个GTP需要那么复杂么?

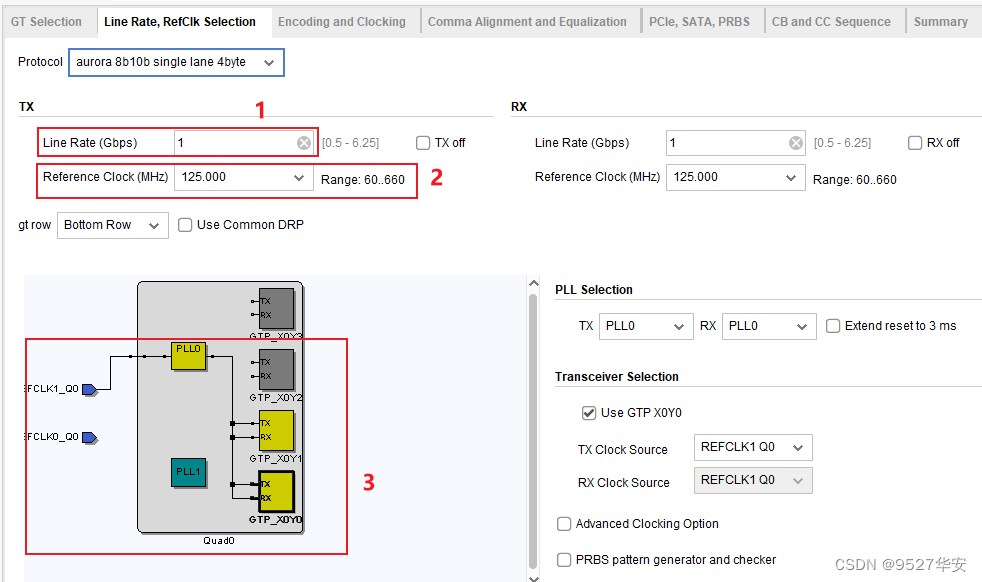

这里对上图的标号做解释:

1:线速率,根据自己的项目需求来,GTP的范围是0.5到6.25G,由于我的项目是视频传输,所以在GTP的速率范围内均可,为了通用性,我在vivado工程中例化了5个GTP,速率分别为1G、2G、4G、5G;

2:参考时钟,这个得根据你的原理图来,可以是80M、125M、148.5M、156.25M等等,我的开发板是125M;

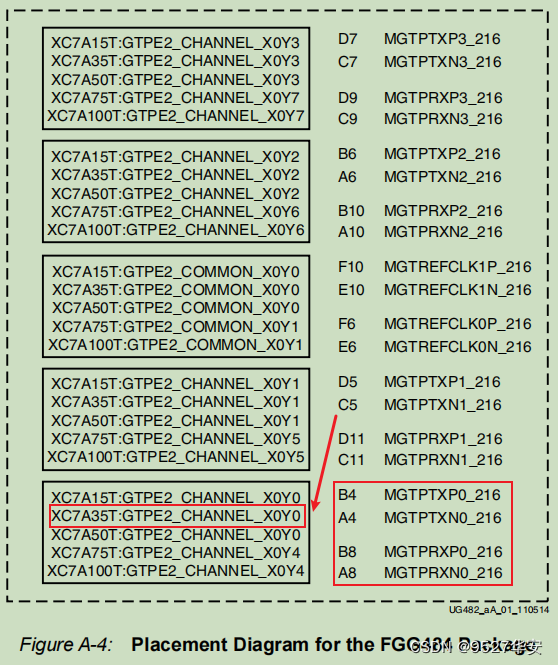

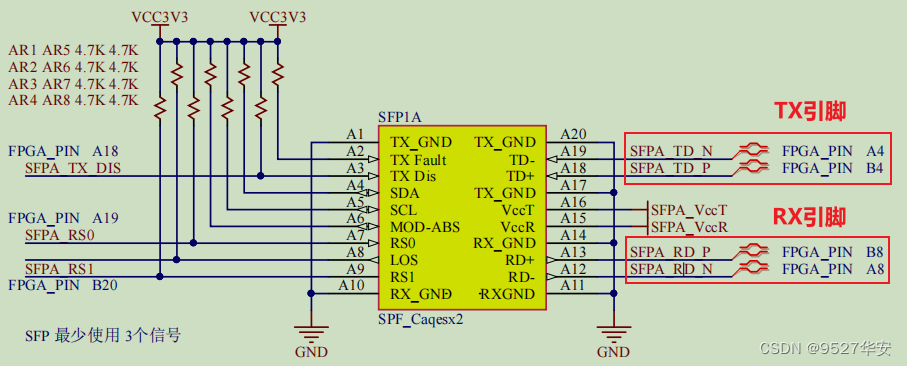

4:GTP组的绑定,这个很重要,他的绑定参考依据有两个,已是你的开发板原理图,而是官方的参考资料《ug482_7Series_GTP_Transceivers》,官方将GTP资源分成了4组,名字分别为X0Y0、X0Y1、X0Y2、X0Y3,由于GT资源是Xilinx系列FPGA的专用资源,占用专用的Bnak,所以引脚也是专用的,那么这些GTP组和引脚是怎么对应的呢?《ug482_7Series_GTP_Transceivers》的说明如下:红框内为的我的开发板原理图对应的FPGA引脚;

我的板子原理图如下:

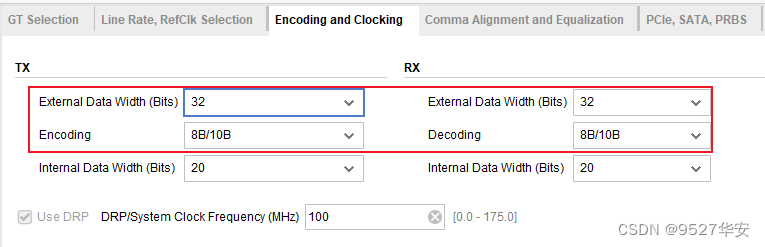

选择外部数据位宽32bit的8b/10b编解码,如下:

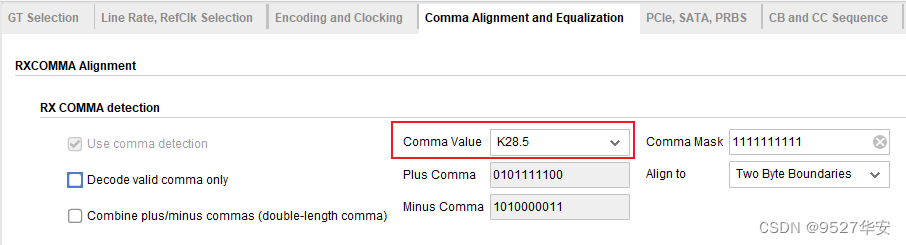

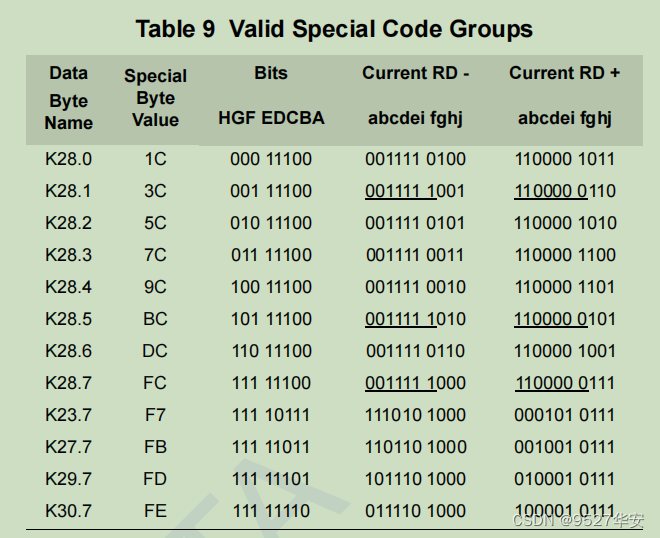

下面这里讲的是K码检测:

这里选择K28.5,也就是所谓的COM码,十六进制为bc,他的作用很多,可以表示空闲乱序符号,也可以表示数据错位标志,这里用来标志数据错位,8b/10b协议对K码的定义如下:

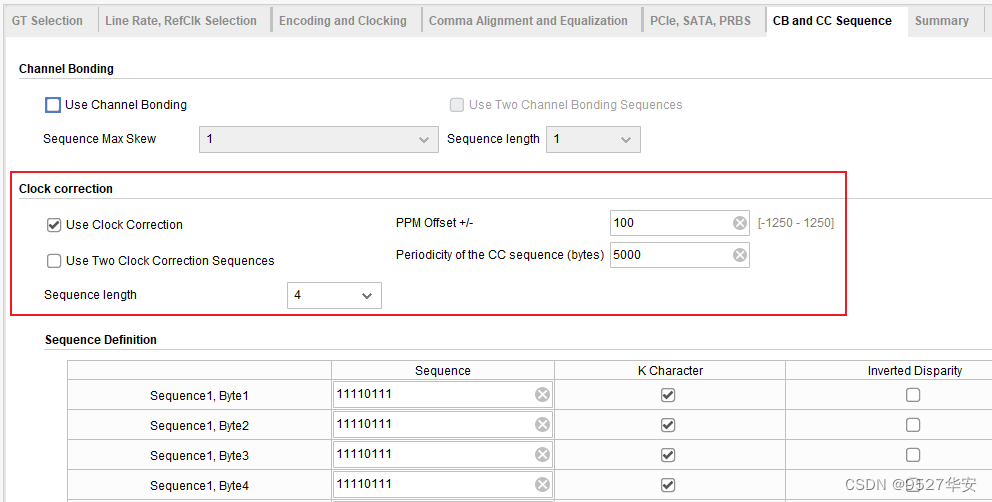

下面讲的是时钟矫正,也就是对应GTP内部接收部分的弹性buffer;

这里有一个时钟频偏的概念,特别是收发双方时钟不同源时,这里设置的频偏为100ppm,规定每隔5000个数据包发送方发送一个4字节的序列,接收方的弹性buffer会根据这4字节的序列,以及数据在buffer中的位置来决定删除或者插入一个4字节的序列中的一个字节,目的是确保数据从发送端到接收端的稳定性,消除时钟频偏的影响;

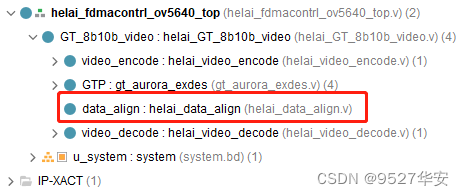

数据对齐

由于GT资源的aurora 8b/10b数据收发天然有着数据错位的情况,所以需要对接受到的解码数据进行数据对齐处理,数据对齐模块代码位置如下:

我定义的 K 码控制字符格式为:XX_XX_XX_BC,所以用一个rx_ctrl 指示数据是否为 K 码 的 COM 符号;

rx_ctrl = 4’b0000 表示 4 字节的数据没有 COM 码;

rx_ctrl = 4’b0001 表示 4 字节的数据中[ 7: 0] 为 COM 码;

rx_ctrl = 4’b0010 表示 4 字节的数据中[15: 8] 为 COM 码;

rx_ctrl = 4’b0100 表示 4 字节的数据中[23:16] 为 COM 码;

rx_ctrl = 4’b1000 表示 4 字节的数据中[31:24] 为 COM 码;

基于此,当接收到有K码时就对数据进行对齐处理,也就是将数据打一拍,和新进来的数据进行错位组合,这是FPGA的基础操作,这里不再赘述;

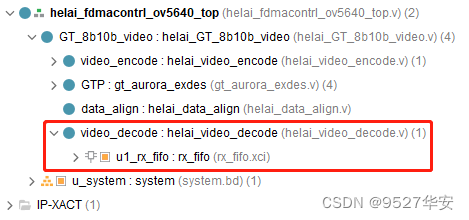

视频数据解包

数据解包是数据组包的逆过程,代码位置如下:

GTP解包时根据固定的指令恢复视频的场同步信号和视频有效信号;这些信号是作为后面图像缓存的重要信号;

至此,数据进出GTP部分就已经讲完了,整个过程的框图我在代码中描述了,如下:

图像缓存

经常看我博客的老粉应该都知道,我做图像缓存的套路是FDMA,他的作用是将图像送入DDR中做3帧缓存再读出显示,目的是匹配输入输出的时钟差和提高输出视频质量,关于FDMA,请参考我之前的博客,博客地址:点击直接前往

需要注意的是,为了适应UDP视频传输,这里的FDMA已被我修改,和以往版本不同,具体参考代码;

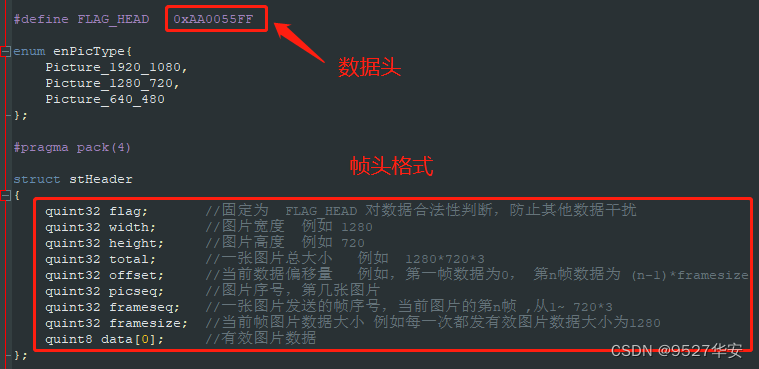

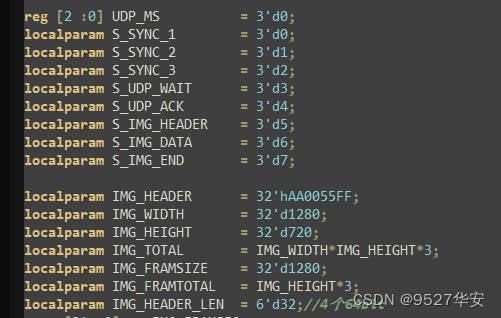

UDP数据组包

实现UDP数据的组包,UDP数据发送必须与QT上位机的接受程序一致,上位机定义的UDP帧格式包括帧头个UDP数据,帧头定义如下:

FPGA端的UDP数据组包代码必须与上图的数据帧格式对应,否则QT无法解析,代码中定义了数据组包状态机以及数据帧,如下:

另外,由于UDP发送是64位数据位宽,而图像像素数据是24bit位宽,所以必须将UDP数据重新组合,以保证像素数据的对齐,这部分是整个工程的难点,也是所有FPGA做UDP数据传输的难点;

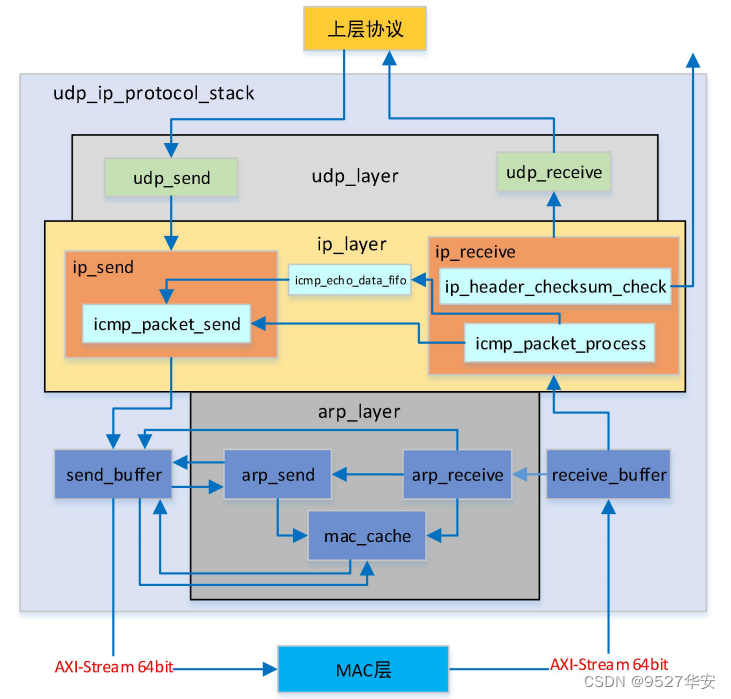

UDP协议栈

本UDP协议栈方案需配合Xilinx的Tri Mode Ethernet MAC三速网IP一起使用,使用UDP协议栈网表文件,虽看不见源码但可正常实现UDP通信,该协议栈目前并不开源,只提供网表文件,但不影响使用,该协议栈带有用户接口,使得用户无需关心复杂的UDP协议而只需关心简单的用户接口时序即可操作UDP收发,非常简单;

协议栈架构如下:

协议栈性能表现如下:

1:支持 UDP 接收校验和检验功能,暂不支持 UDP 发送校验和生成;

2:支持 IP 首部校验和的生成和校验,同时支持 ICMP 协议中的 PING 功能,可接收并响应同一个子网内部设备的 PING 请求;

3:可自动发起或响应同一个子网内设备的 ARP 请求,ARP 收发完全自适应。ARP 表可保存同一个子网内部256 个 IP 和 MAC 地址对;

4:支持 ARP 超时机制,可检测所需发送数据包的目的 IP 地址是否可达;

5:协议栈发送带宽利用率可达 93%,高发送带宽下,内部仲裁机制保证 PING 和 ARP 功能不受任何影响;

6:发送过程不会造成丢包;

7:提供64bit位宽AXI4-Stream形式的MAC接口,可与Xilinx官方的千兆以太网IP核Tri Mode Ethernet MAC,以及万兆以太网 IP 核 10 Gigabit Ethernet Subsystem、10 Gigabit Ethernet MAC 配合使用;

有了此协议栈,我们无需关心复杂的UDP协议的实现了,直接调用接口即可使用。。。

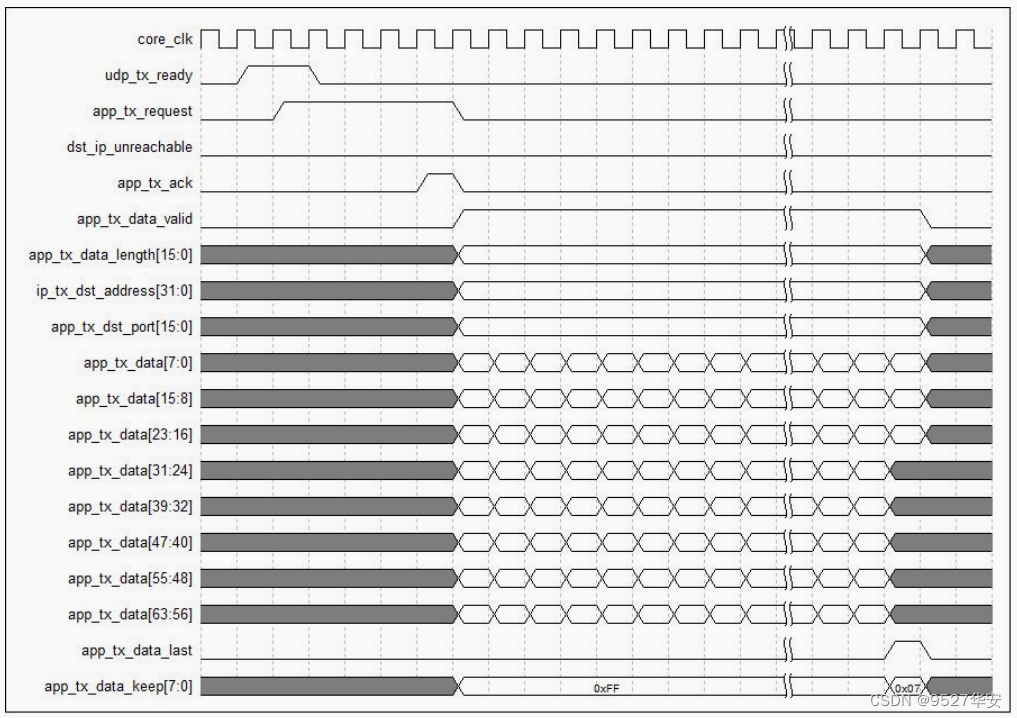

本UDP协议栈用户接口发送时序如下:

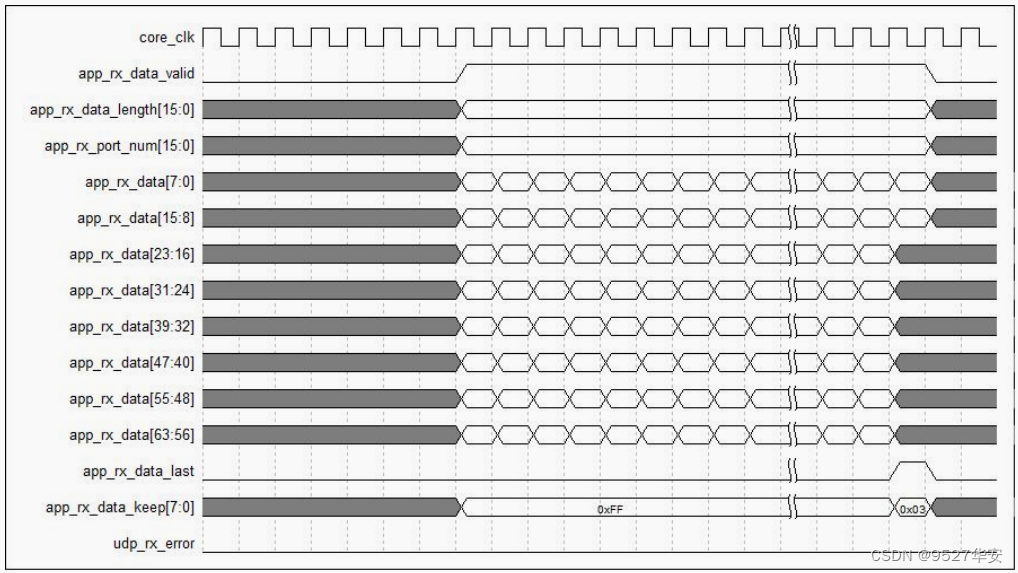

本UDP协议栈用户接口接收时序如下:

UDP协议栈数据发送

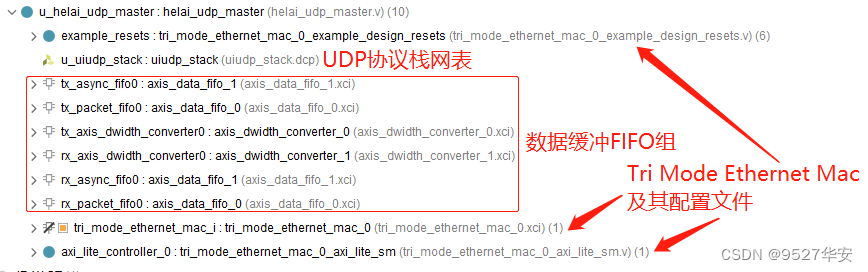

UDP协议栈具有发送和接收功能,但这里仅用到了发送,此部分代码架构如下:

UDP协议栈代码组我已经做好,用户可直接拿去使用;

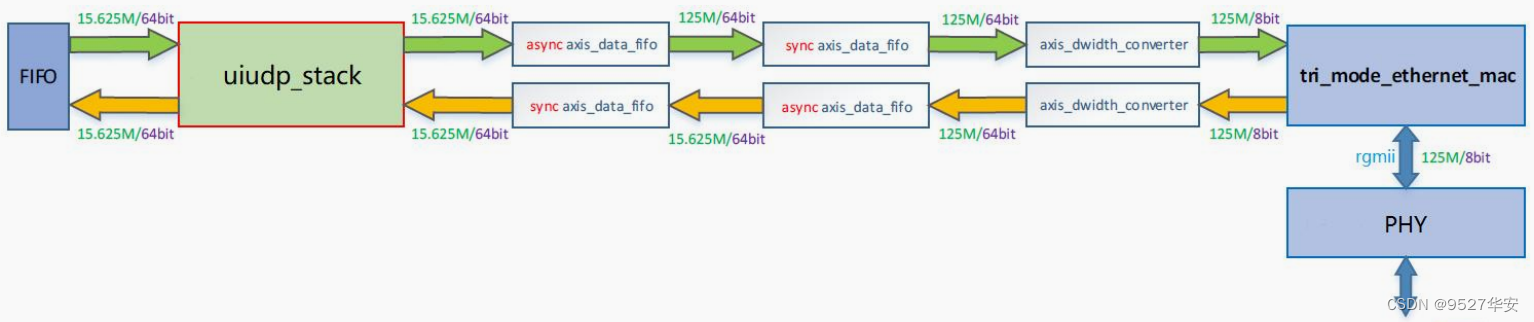

这里对代码中用到的数据缓冲FIFO组做如下解释:

由于 UDP IP 协议栈的 AXI-Stream 数据接口位宽为 64bit,而 Tri Mode Ethernet MAC 的 AXI-Stream数据接口位宽为 8bit。因此,要将 UDP IP 协议栈与 Tri Mode Ethernet MAC 之间通过 AXI-Stream 接口互联,需要进行时钟域和数据位宽的转换。实现方案如下图所示:

收发路径(本设计只用到了发送)都使用了2个AXI-Stream DATA FIFO,通过其中1个FIFO实现异步时钟域的转换,1个FIFO实

现数据缓冲和同步Packet mode功能;由于千兆速率下Tri Mode Ethernet MAC的AXI-Stream数据接口同步时钟信号为125MHz,此时,UDP协议栈64bit的AXI-Stream数据接口同步时钟信号应该为125MHz/(64/8)=15.625MHz,因此,异步

AXI-Stream DATA FIFO两端的时钟分别为125MHz(8bit),15.625MHz(64bit);UDP IP协议栈的AXI-Stream接口经过FIFO时钟域转换后,还需要进行数据数据位宽转换,数据位宽的转换通过AXI4-Stream Data Width Converter完成,在接收路径中,进行 8bit 到 64bit 的转换;在发送路径中,进行 64bit 到 8bit 的转换;

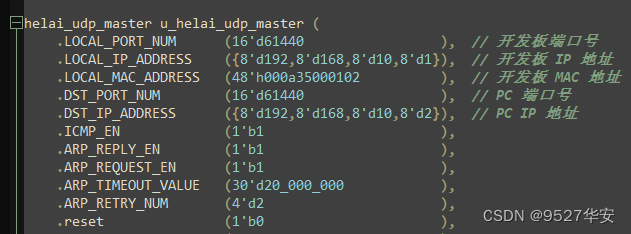

IP地址、端口号的修改

UDP协议栈留出了IP地址、端口号的修改端口供用户自由修改,位置如下:

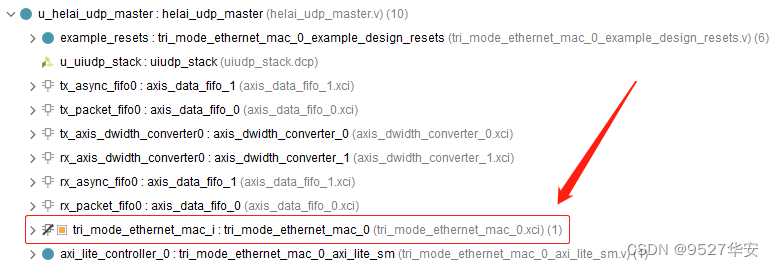

Tri Mode Ethernet MAC介绍以及移植注意事项

本设计调用了Xilinx官方IP:Tri Mode Ethernet MAC,其在代码中的位置如下:

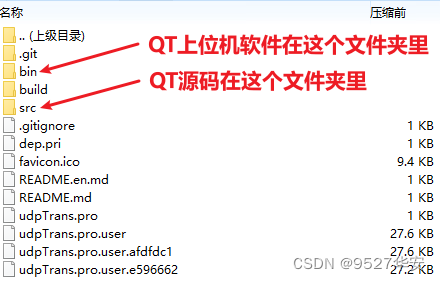

可以看到其中泰处于被锁定状态,这是我们故意为之,目的是根据不同的PHY延时参数而修改其内部代码和内部时序约束代码,由于本设计使用的网络PHY为RTL8211,所以这里重点介绍使用RTL8211时,Tri Mode Ethernet MAC的修改和移植事项,当你需要工程移植,或者你的vivado版本与我的不一致时,Tri Mode Ethernet MAC都需要在vivado中进行升级,但由于该IP已被我们人为锁定,所以升级和修改需要一些高端操作,关于操作方法,我专门写了一篇文档,已附在资料包里,如下:

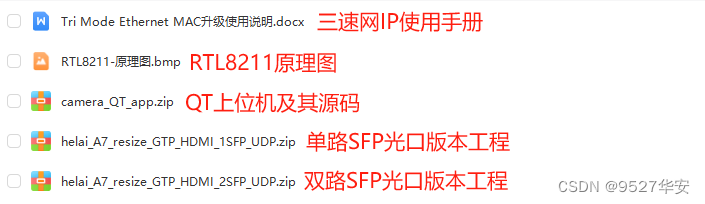

RTL8211

本设计开发板使用的网络PHY为RTL8211,工作在延时模式下,原理图引出了MDIO,但代码中不需要MDIO配置,通过上下拉电阻即可使RTL8211工作于延时模式,该PHY最高支持千兆,且能在10M/100M/1000M之间自动协商,但本设计在Tri Mode Ethernet MAC端固定为1000M;在资料包中,我们提供RTL8211的原理图;

QT上位机和源码

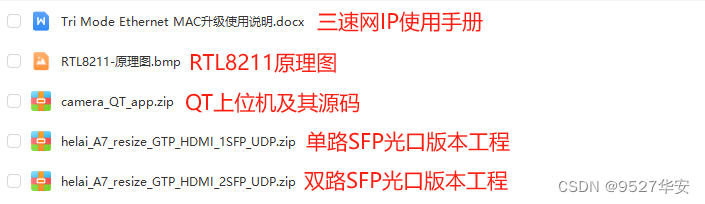

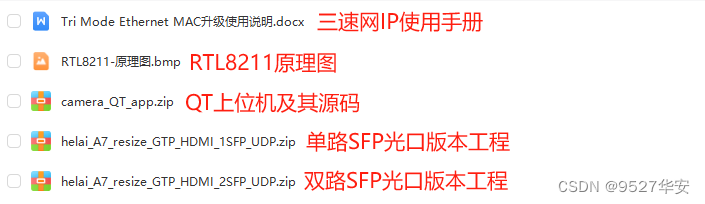

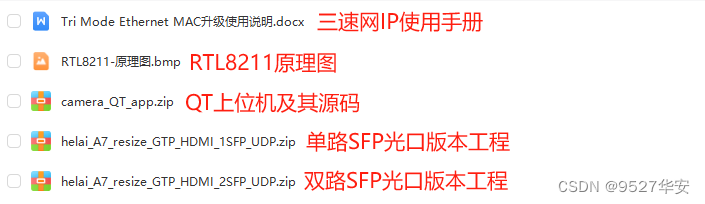

我们提供和UDP通信协议相匹配的QT抓图显示上位机及其源代码,目录如下:

我们的QT目前仅支持1280x720分辨率的视频抓图显示,但同时预留了1080P接口,对QT开发感兴趣的朋友可以尝试修改代码以适应1080P,因为QT在这里只是验证工具,不是本工程的重点,所以不再过多赘述,详情请参考资料包的QT源码,位置如下:

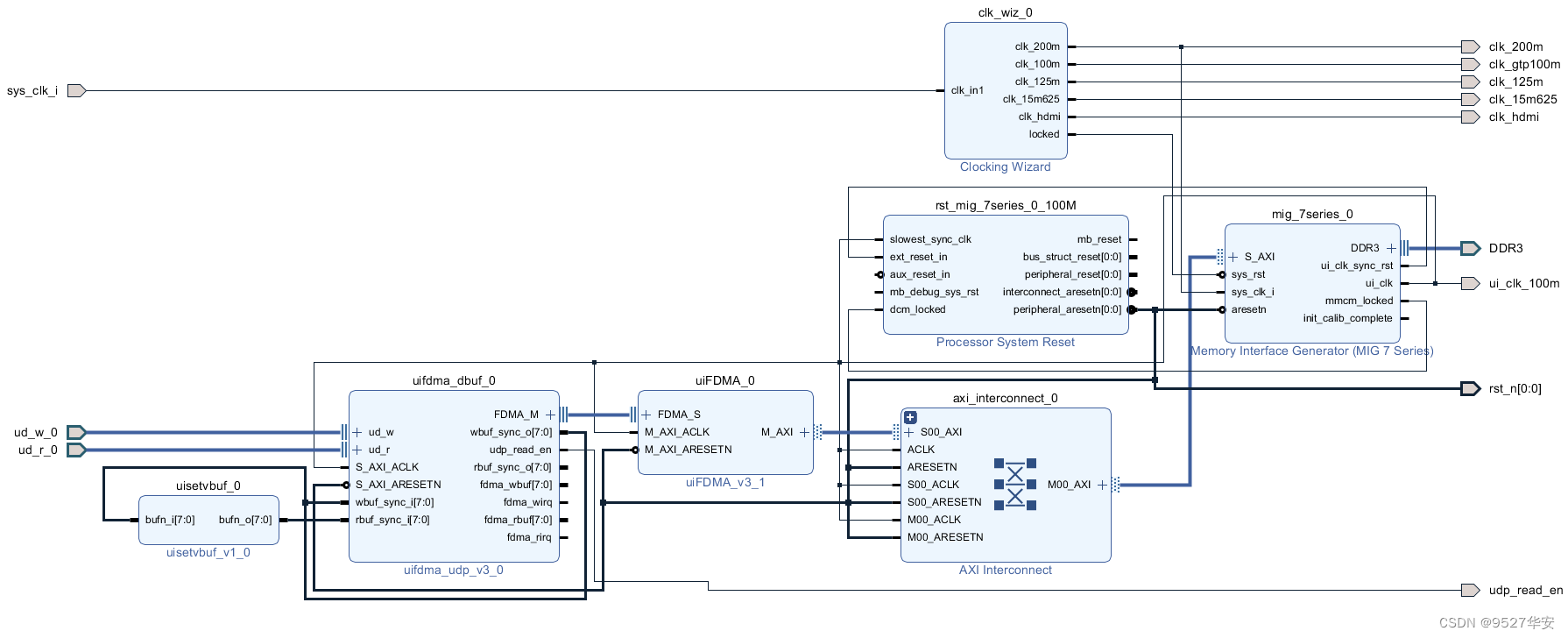

4、vivado工程1–>1路SFP传输

开发板FPGA型号:Xilinx–Artix7–xc7a35tfgg484-2;

开发环境:Vivado2019.1;

输入:HDMI或者动态彩条,分辨率1920x1080@60Hz;

输出:SFP光口/RJ45网口;

网络PHY:RTL8211,延时模式;

应用:FPGA GTP+UDP架构,高速接口以太网视频传输,1路SFP光口;

工程Block Design如下:

工程代码架构如下:

工程的资源消耗和功耗如下:

5、vivado工程2–>2路SFP传输

开发板FPGA型号:Xilinx–Artix7–xc7a35tfgg484-2;

开发环境:Vivado2019.1;

输入:HDMI或者动态彩条,分辨率1920x1080@60Hz;

输出:SFP光口/RJ45网口;

网络PHY:RTL8211,延时模式;

应用:FPGA GTP+UDP架构,高速接口以太网视频传输,2路SFP光口;

工程Block Design、工程代码架构、工程的资源消耗和第4章节的“vivado工程1–>1路SFP传输”一致;

6、工程移植说明

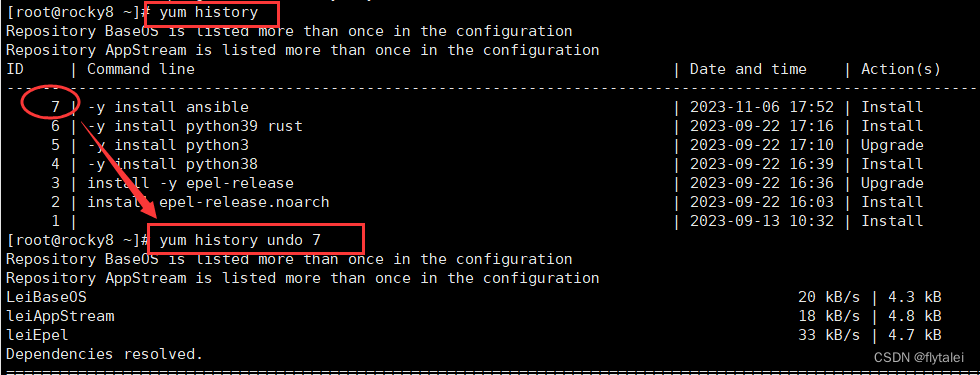

vivado版本不一致处理

1:如果你的vivado版本与本工程vivado版本一致,则直接打开工程;

2:如果你的vivado版本低于本工程vivado版本,则需要打开工程后,点击文件–>另存为;但此方法并不保险,最保险的方法是将你的vivado版本升级到本工程vivado的版本或者更高版本;

3:如果你的vivado版本高于本工程vivado版本,解决如下:

打开工程后会发现IP都被锁住了,如下:

此时需要升级IP,操作如下:

FPGA型号不一致处理

如果你的FPGA型号与我的不一致,则需要更改FPGA型号,操作如下:

更改FPGA型号后还需要升级IP,升级IP的方法前面已经讲述了;

其他注意事项

1:由于每个板子的DDR不一定完全一样,所以MIG IP需要根据你自己的原理图进行配置,甚至可以直接删掉我这里原工程的MIG并重新添加IP,重新配置;

2:根据你自己的原理图修改引脚约束,在xdc文件中修改即可;

3:纯FPGA移植到Zynq需要在工程中添加zynq软核;

7、上板调试验证并演示

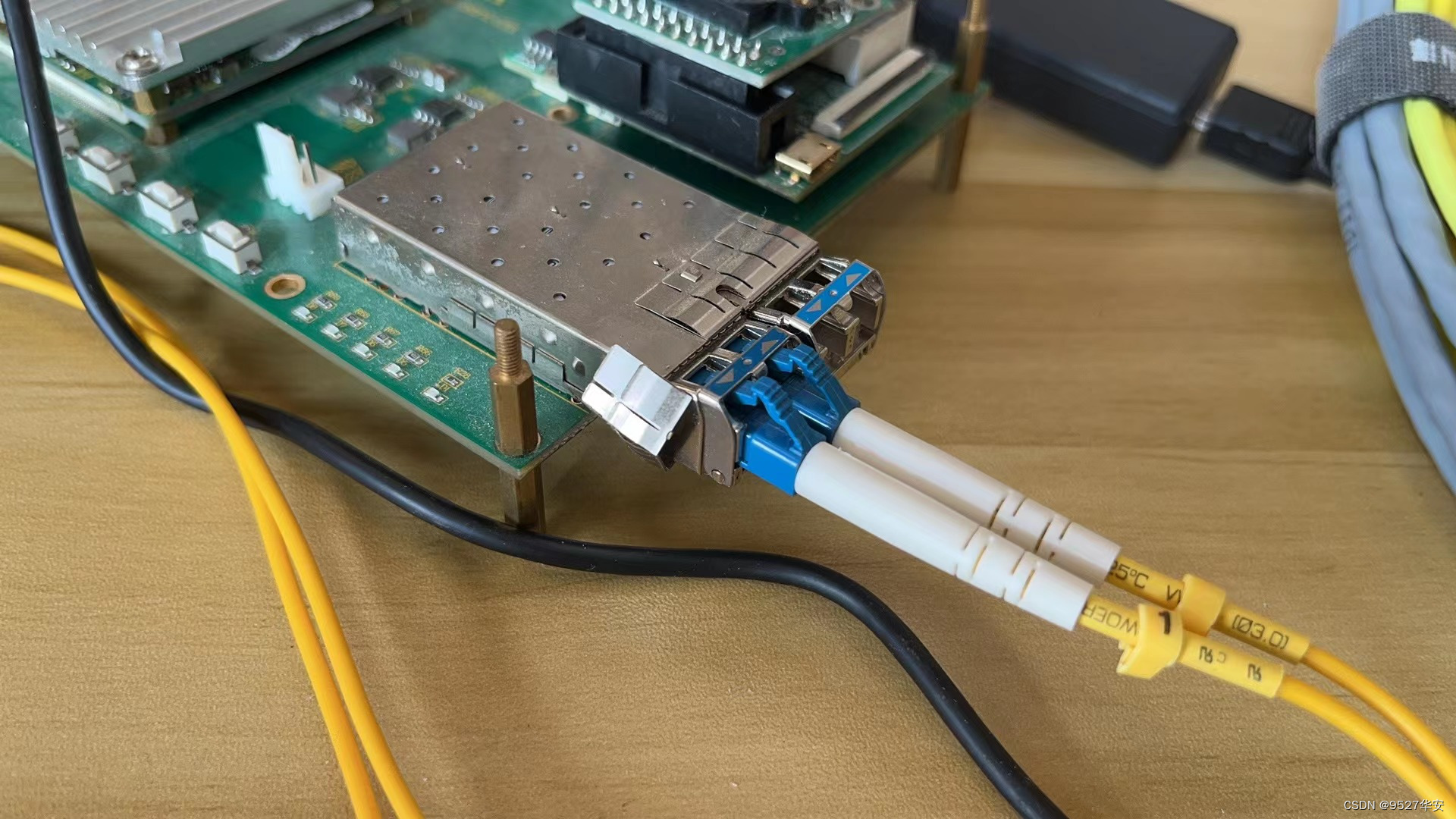

准备工作

需要准备以下物品:

1:FPGA开发板;

2:板载HDMI输入接口,没有则选择代码里的动态彩条;

3:光模块和光纤;

4:网线;

5:上位机电脑,台式或笔记本;

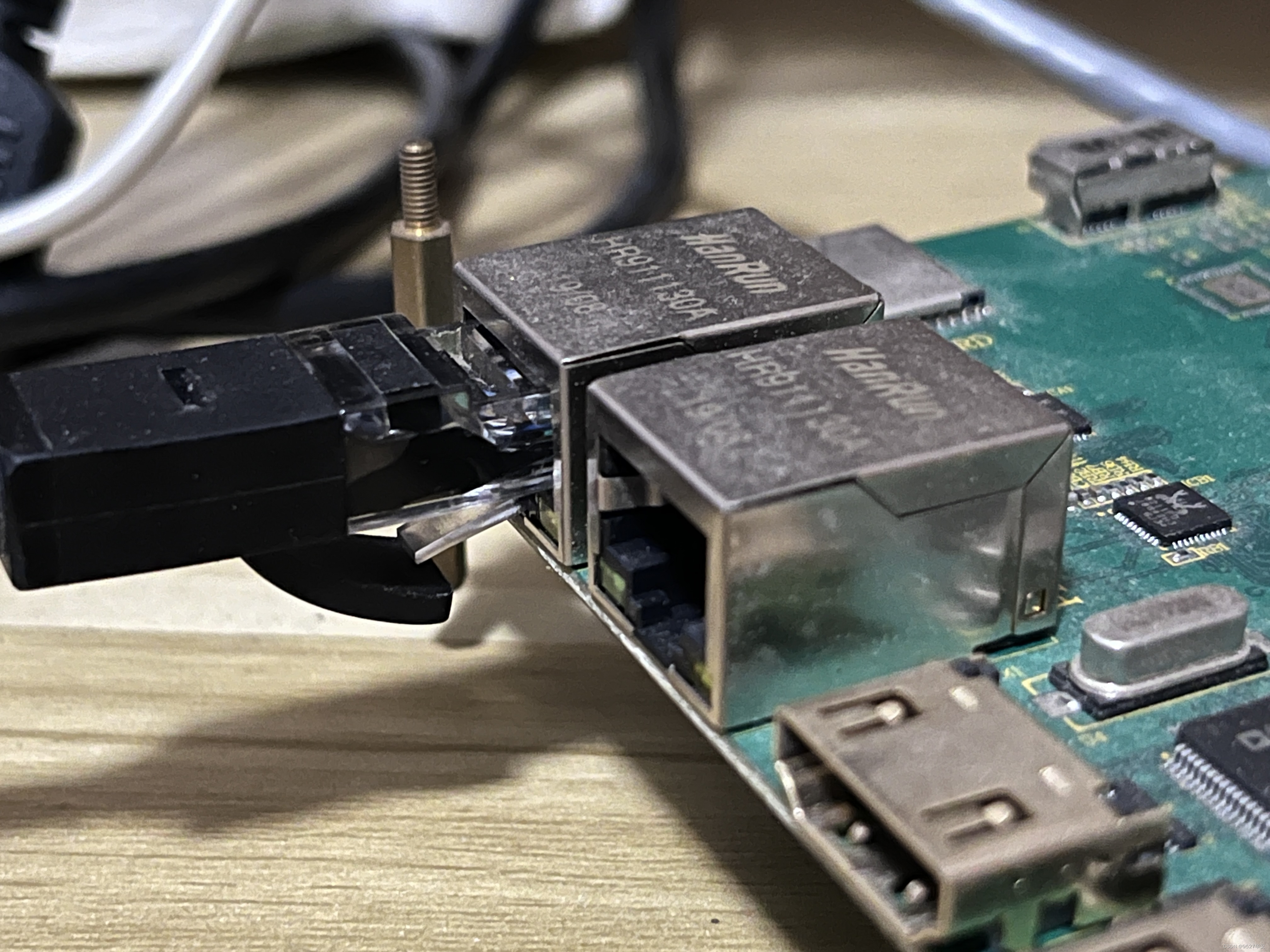

工程1:1路SFP传输的光纤接法如下:

工程2:2路SFP传输的光纤接法如下:

网口连接如下:

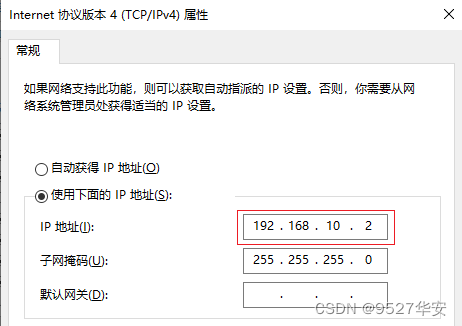

然后将你的电脑IP地址改为和代码里规定的IP一致,当然,代码里的IP是可以任意设置的,但代码里的IP修改后,电脑端的IP也要跟着改,我的设置如下:

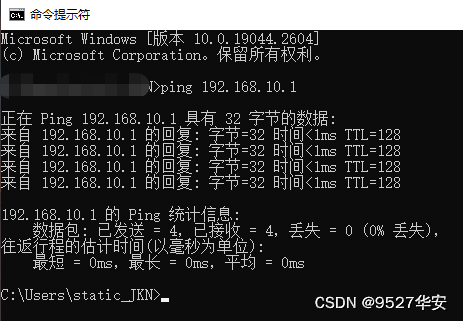

ping一下

在开始测试前,我们先ping一下,测试UDP是否连通,如下:

静态演示

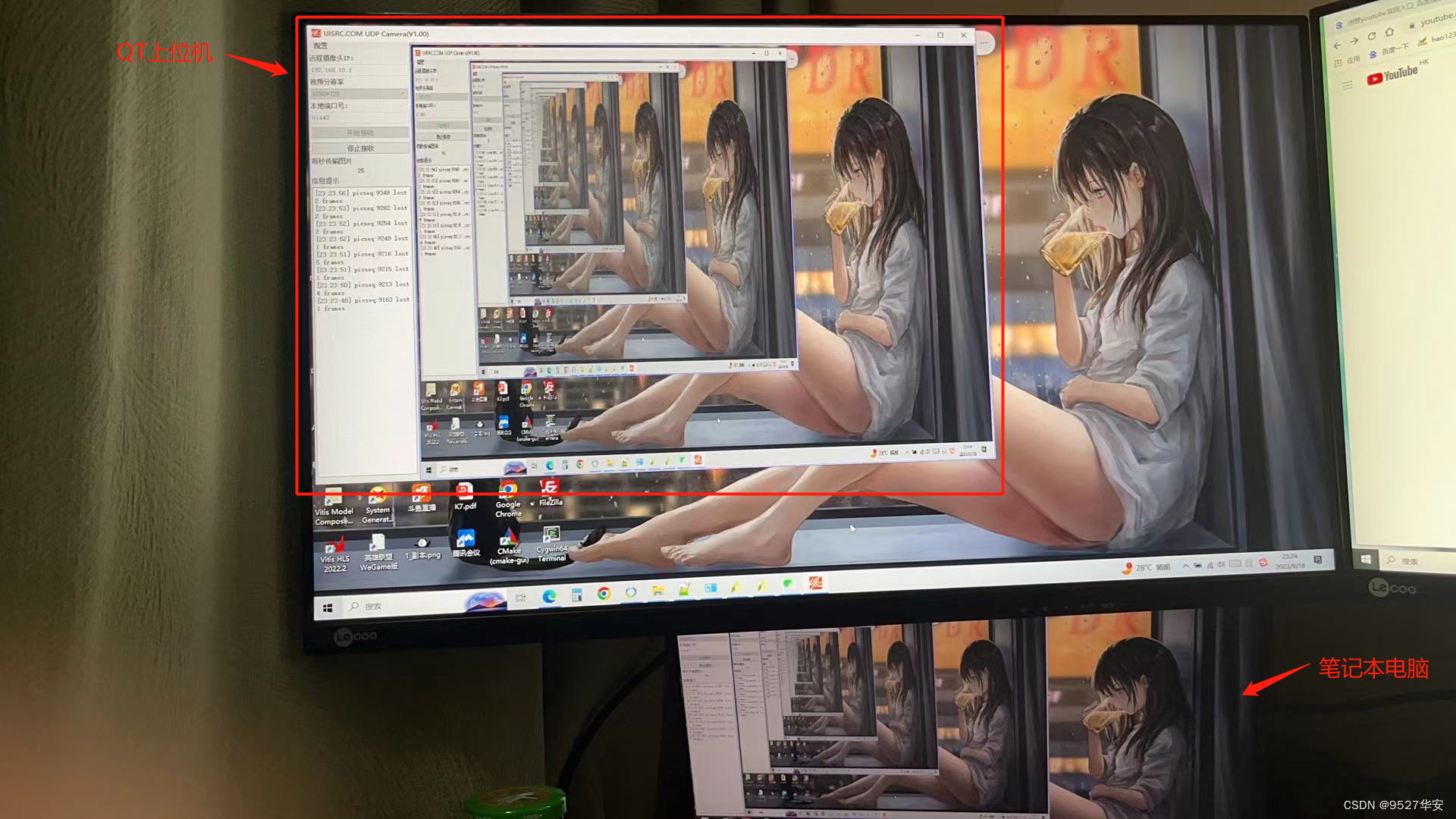

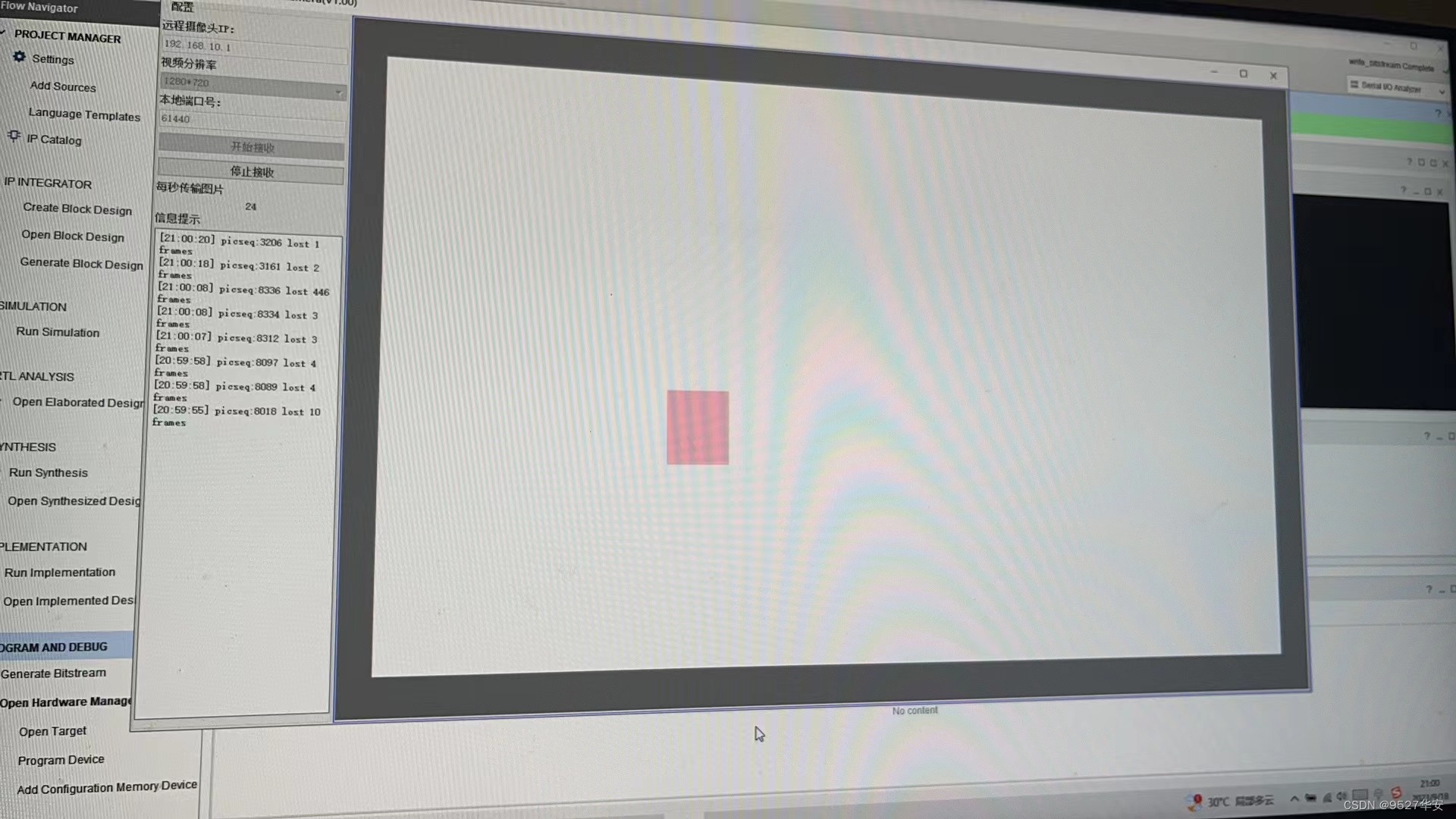

HDMI输入1920x1080缩小到1280x720后UDP网络传输QT上位机显示如下:

动态彩条1920x1080缩小到1280x720后UDP网络传输QT上位机显示如下:

动态演示

动态视频演示如下:

FPGA-GTP-UDP-HDMI

8、福利:工程源码获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

资料获取方式:私,或者文章末尾的V名片。

网盘资料如下:

相关文章:

FPGA高端项目:图像缩放+GTP+UDP架构,高速接口以太网视频传输,提供2套工程源码加QT上位机源码和技术支持

目录 1、前言免责声明本项目特点 2、相关方案推荐我这里已有的 GT 高速接口解决方案我这里已有的以太网方案我这里已有的图像处理方案 3、设计思路框架设计框图视频源选择ADV7611 解码芯片配置及采集动态彩条跨时钟FIFO图像缩放模块详解设计框图代码框图2种插值算法的整合与选择…...

ansible安装和常见模块

文章目录 ansible的安装1.1 yum install epel-release.noarch1.2配置epel源的baseurl1.3安装ansible1.4安装ansible报错问题1.5 yum卸载 ansible的安装 ansible是由epel源提供的,所以需要配置epel源。要么通过配置好的baseos源直接执行“yum install epel-release.…...

【Python基础】 Python设计模式之单例模式介绍

单例模式 1.设计模式2.单例设计模式的应用场景3.new方法4. Python 中的单例 1.设计模式 设计模式 是 前人工作的总结和提炼,通常,被人们广泛流传的设计模式都是针对 某一特定问题 的成熟的解决方案使用 设计模式 是为了可重用代码、让代码更容易被他人理…...

算法小白的心得笔记:关于Nan

NaN 是什么 在C中,NaN(Not a Number)是一种特殊的浮点数值,用于表示无法表示的数值或未定义的操作,例如0除以0。如果你的double类型变量显示为NaN,那么可能是在计算过程中出现了这种未定义的操作。 如果你…...

Photoshop 2023 v24.7

Photoshop是一款强大的图像编辑软件,被广泛应用于图像处理、图形设计、数字绘画等领域。它提供了丰富的图像编辑功能,可以用于调整图像的色彩、亮度、对比度等,添加特效、滤镜,以及进行复杂的图像合成和修复。 以下是Adobe Photo…...

-管道、消息队列、信号量、共享存储、socket)

进程间通信(IPC)-管道、消息队列、信号量、共享存储、socket

进程间通信(IPC,InterProcess Communication)是指在不同进程之间传播或交换信息。 IPC的方式通常有管道(包括无名管道PIPE和命名管道FIFO)、消息队列、信号量、共享存储、Socket、Streams等。其中 Socket和Streams支持…...

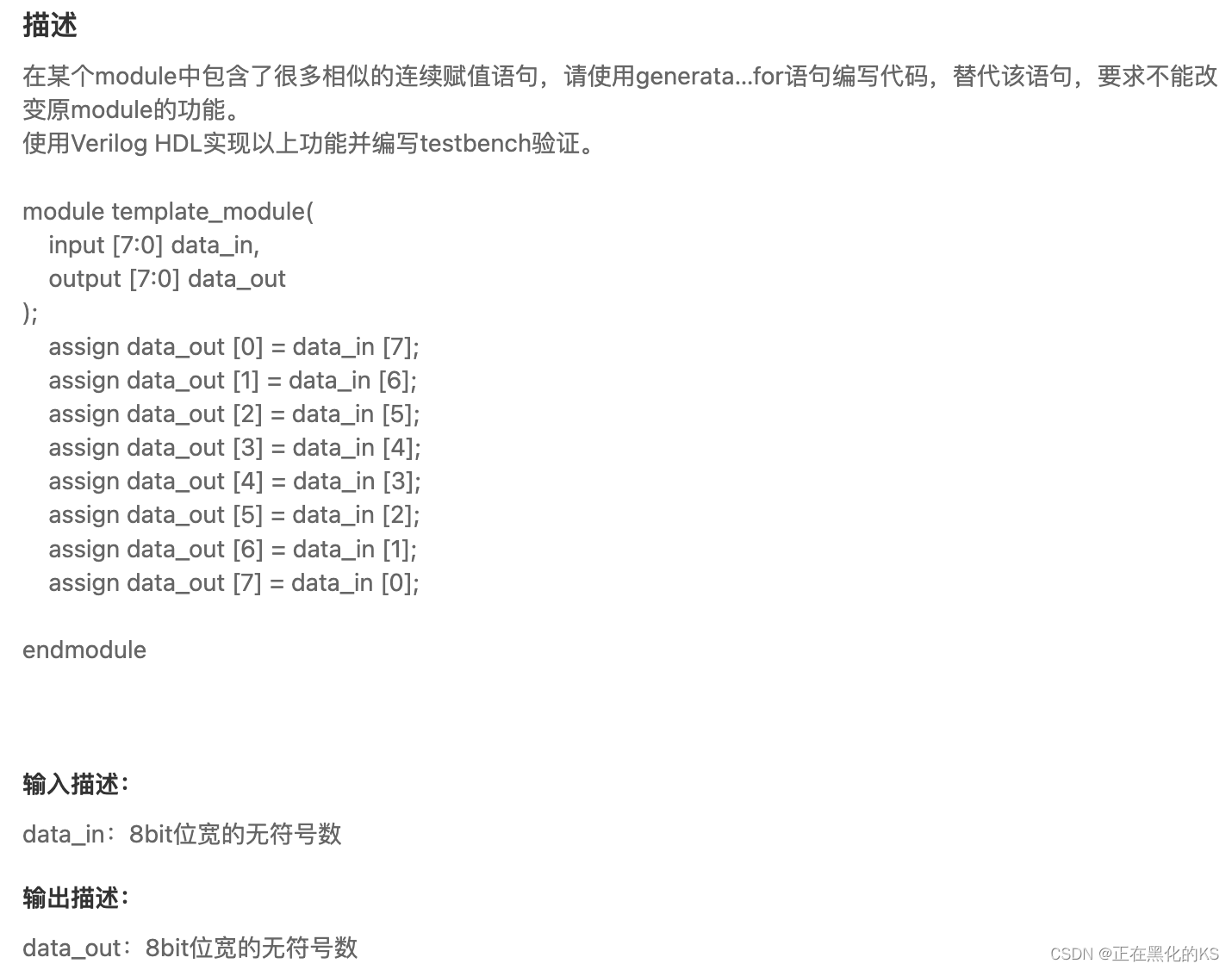

「Verilog学习笔记」使用generate…for语句简化代码

专栏前言 本专栏的内容主要是记录本人学习Verilog过程中的一些知识点,刷题网站用的是牛客网 分析 generate…for语句是Verilog HDL语言特有的语句,使用循环结构编写可综合的多个形式相近的代码,循环变量必须由特定关键字genvar声明。 timesca…...

互联网Java工程师面试题·Spring篇·第七弹

目录 36、什么是基于 Java 的 Spring 注解配置? 给一些注解的例子. 37、什么是基于注解的容器配置? 38、怎样开启注解装配? 39、Required 注解 40、Autowired 注解 41、Qualifier 注解 42、在 Spring 框架中如何更有效地使用 JDBC? 43、JdbcTemplate 44…...

mysql驱动包引起的告警问题using SSL the verifyServerCertificate property is set to ‘false‘

tomcat启动时报以下ssl的连接错误,mysql版本为5.7.17,虽然系统可以使用,但是日志量太大,还是处理下,只需要修改mysql的连接格式: url.db “jdbc:mysql://localhost:3306/disis3?userroot&passwordXXXX…...

draw.io与项目管理——如何利用流程图工具提高项目管理效率

draw.io 是一款强大的图形绘制工具,用于创建各种类型的图表、流程图、组织结构图、网络图和平面设计等。它提供了丰富的绘图工具和预定义的图形库,使用户能够轻松创建专业水平的图形作品。 draw.io具有直观的界面和简单易用的功能,适合各种用…...

LoRaWAN物联网架构

与其他网关一样,LoRaWAN网关也需要在规定的工作频率上工作。在特定国家部署网关时,必须要遵循LoRa联盟的区域参数。不过,它是没有通用频率的,每个国家对使用非授权MHZ频段都有不同的法律规定。例如,中国的LoRaWAN频段是…...

数据结构(五):哈希表及面试常考的算法

一、哈希表介绍 1、定义 哈希表,也叫散列表,是根据关键码和值 (key和value) 直接进行访问的数据结构,通过key和value来映射到集合中的一个位置,这样就可以很快找到集合中的对应元素。例如,下列键(key)为人名…...

水利部加快推进小型水库除险加固,大坝安全监测是重点

国务院常务会议明确到2025年前,完成新出现病险水库的除险加固,配套完善重点小型水库雨水情和安全监测设施,实现水库安全鉴定和除险加固常态化。 为加快推进小型水库除险加固前期工作,水利部协调财政部提前下达了2023年度中央补助…...

实施电子采购的6个有效步骤

耗时又费力,手动采购之苦相信大家都受够了,现在越来越多的企业正在实施电子采购策略。根据CIPS的《2022年采购与供应数字化报告》,多达95%的企业在采购与供应商管理中采用了技术。 但采用技术并不能保证立竿见影的效果。企业需要制定好电子采…...

【Shell脚本6】Shell 运算符

Shell 基本运算符 Shell 和其他编程语言一样,支持多种运算符,包括: 算术运算符关系运算符布尔运算符逻辑运算符字符串运算符文件测试运算符 原生bash不支持简单的数学运算,但是可以通过其他命令来实现,例如 awk 和 …...

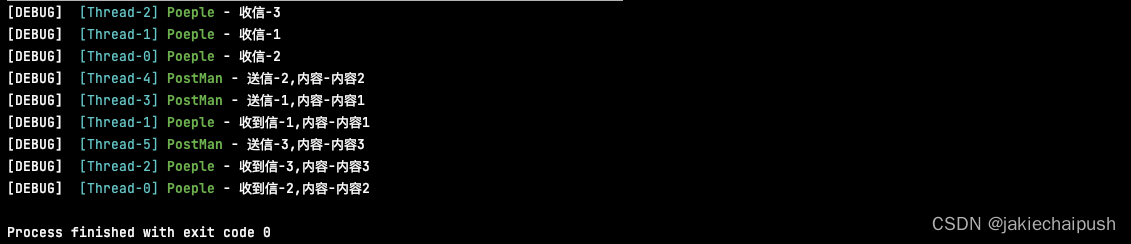

设计模式之保护性暂停

文章目录 1. 定义2. 实现保护性暂停模式3. Join原理4. 保护性暂停模式的扩展 1. 定义 即Guarded Suspension,用在一个线程等待另一个线程的执行结果。 有一个结果需要从一个线程传递给另一个线程,让他们关联到同一个GuarderObject(这就是保…...

UE5、CesiumForUnreal实现加载GeoJson绘制单面(Polygon)功能(StaticMesh方式)

文章目录 1.实现目标2.实现过程2.1 实现原理2.1.1 数据读取2.1.2 三角剖分2.1.3 创建StaticMesh2.2 应用测试2.2.1 具体代码2.2.2 蓝图应用测试3.参考资料1.实现目标 通过读取本地GeoJson数据,在UE中以StaticMeshComponent的形式绘制出面数据,支持Editor和Runtime环境,GIF动…...

Linux 下以其他用户运行程序

需求: 在root的用户下,设置开启自启,这些服务都要用一个swadmin用户运行。 1、创建需要执行的命令脚本 vim /usr/local/bin/start_services.sh#!/bin/bash runuser -l swadmin -c cd /opt/server/ && ./service.sh start s-app-ser…...

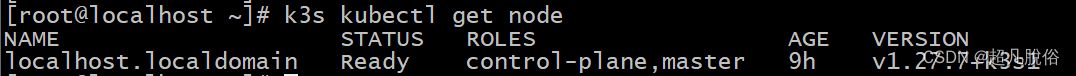

Centos7下安装使用K3S

## K3S简介 K3S官方文档链接 K3s是一个轻量级的、专为容器化应用和Kubernetes集群设计的开源Kubernetes发行版。K3s的目标是提供一个更小、更简单、更易于部署和维护的Kubernetes集群。它是Rancher Labs开发的一个项目,旨在满足边缘计算、IoT设备、开发和测试环境…...

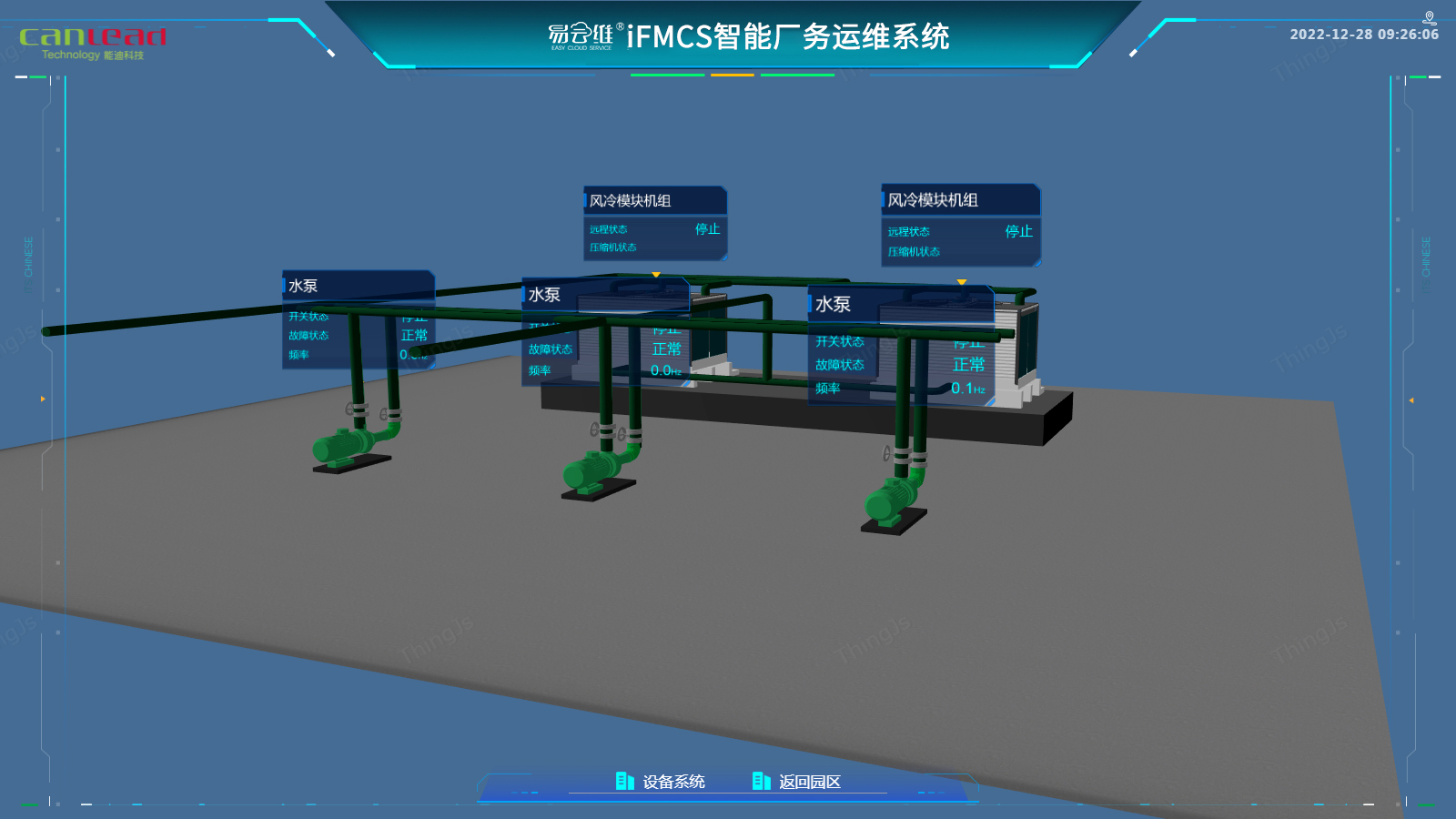

易云维®工厂能耗管理平台系统方案,保证运营质量,推动广东制造企业节能减排

我国《关于完整准确全面贯彻新发展理念推进碳达峰碳中和工作的实施意见》出台,提出了推进碳达峰碳中和工作的总体目标。到2025年,广东具备条件的地区、行业和企业率先实现碳达峰,为全省实现碳达峰、碳中和奠定坚实基础;2030年前实…...

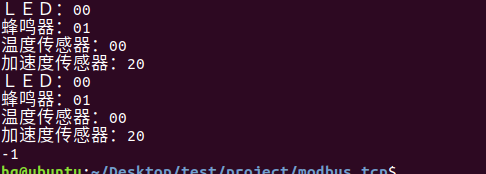

网络编程(Modbus进阶)

思维导图 Modbus RTU(先学一点理论) 概念 Modbus RTU 是工业自动化领域 最广泛应用的串行通信协议,由 Modicon 公司(现施耐德电气)于 1979 年推出。它以 高效率、强健性、易实现的特点成为工业控制系统的通信标准。 包…...

synchronized 学习

学习源: https://www.bilibili.com/video/BV1aJ411V763?spm_id_from333.788.videopod.episodes&vd_source32e1c41a9370911ab06d12fbc36c4ebc 1.应用场景 不超卖,也要考虑性能问题(场景) 2.常见面试问题: sync出…...

【Linux】shell脚本忽略错误继续执行

在 shell 脚本中,可以使用 set -e 命令来设置脚本在遇到错误时退出执行。如果你希望脚本忽略错误并继续执行,可以在脚本开头添加 set e 命令来取消该设置。 举例1 #!/bin/bash# 取消 set -e 的设置 set e# 执行命令,并忽略错误 rm somefile…...

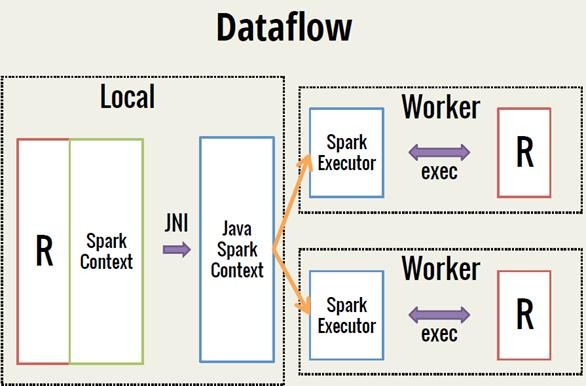

Spark 之 入门讲解详细版(1)

1、简介 1.1 Spark简介 Spark是加州大学伯克利分校AMP实验室(Algorithms, Machines, and People Lab)开发通用内存并行计算框架。Spark在2013年6月进入Apache成为孵化项目,8个月后成为Apache顶级项目,速度之快足见过人之处&…...

C++:std::is_convertible

C++标志库中提供is_convertible,可以测试一种类型是否可以转换为另一只类型: template <class From, class To> struct is_convertible; 使用举例: #include <iostream> #include <string>using namespace std;struct A { }; struct B : A { };int main…...

2024年赣州旅游投资集团社会招聘笔试真

2024年赣州旅游投资集团社会招聘笔试真 题 ( 满 分 1 0 0 分 时 间 1 2 0 分 钟 ) 一、单选题(每题只有一个正确答案,答错、不答或多答均不得分) 1.纪要的特点不包括()。 A.概括重点 B.指导传达 C. 客观纪实 D.有言必录 【答案】: D 2.1864年,()预言了电磁波的存在,并指出…...

【磁盘】每天掌握一个Linux命令 - iostat

目录 【磁盘】每天掌握一个Linux命令 - iostat工具概述安装方式核心功能基础用法进阶操作实战案例面试题场景生产场景 注意事项 【磁盘】每天掌握一个Linux命令 - iostat 工具概述 iostat(I/O Statistics)是Linux系统下用于监视系统输入输出设备和CPU使…...

详解:相对定位 绝对定位 固定定位)

css的定位(position)详解:相对定位 绝对定位 固定定位

在 CSS 中,元素的定位通过 position 属性控制,共有 5 种定位模式:static(静态定位)、relative(相对定位)、absolute(绝对定位)、fixed(固定定位)和…...

Python如何给视频添加音频和字幕

在Python中,给视频添加音频和字幕可以使用电影文件处理库MoviePy和字幕处理库Subtitles。下面将详细介绍如何使用这些库来实现视频的音频和字幕添加,包括必要的代码示例和详细解释。 环境准备 在开始之前,需要安装以下Python库:…...

NPOI操作EXCEL文件 ——CAD C# 二次开发

缺点:dll.版本容易加载错误。CAD加载插件时,没有加载所有类库。插件运行过程中用到某个类库,会从CAD的安装目录找,找不到就报错了。 【方案2】让CAD在加载过程中把类库加载到内存 【方案3】是发现缺少了哪个库,就用插件程序加载进…...