深度学习armv8/armv9 cache的原理

快速链接:

- 【精选】ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈

1、为什么要用cache?

ARM 架构刚开始开发时,处理器的时钟速度和内存的访问速度大致相似。今天的处理器内核要复杂得多,并且时钟频率可以快几个数量级。然而,外部总线和存储设备的频率并没有达到同样的程度。可以实现可以与内核以相同速度运行的小片上 SRAM块,但与标准 DRAM 块相比,这种 RAM 非常昂贵,标准 DRAM 块的容量可能高出数千倍。在许多基于 ARM 处理器的系统中,访问外部存储器需要数十甚至数百个内核周期。

缓存是位于核心和主内存之间的小而快速的内存块。它在主内存中保存项目的副本。对高速缓冲存储器的访问比对主存储器的访问快得多。每当内核读取或写入特定地址时,它首先会在缓存中查找。如果它在高速缓存中找到地址,它就使用高速缓存中的数据,而不是执行对主存储器的访问。通过减少缓慢的外部存储器访问时间的影响,这显着提高了系统的潜在性能。通过避免驱动外部信号的需要,它还降低了系统的功耗

2、背景:架构的变化?

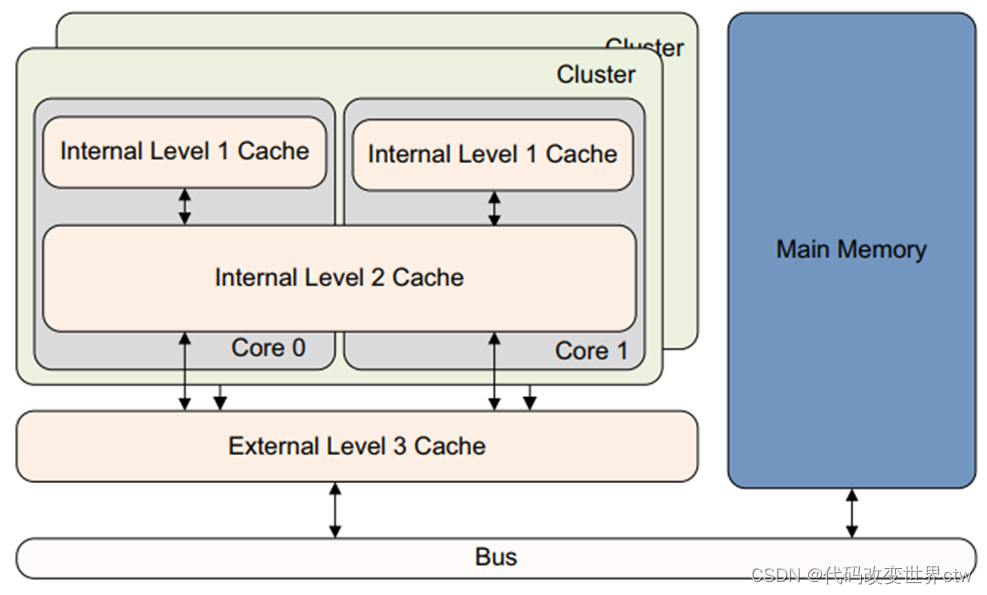

- DynamIQ是Arm公司2017年发表的新一代多核心微架构(microarchitecture)技术,正式名称为DynamIQ big.LITTLE(以下简称为DynamIQ),取代使用多年的big.LITTLE技术

- big.LITTLE技术将多核心处理器IP分为两个clusters,每个cluster最多4个核,两个cluster最多4+4=8核,而DynamIQ的一个cluster,最多支持8个核

- big.LITTLE大核和小核必须放在不同的cluster,例如4+4(4大核+4小核),DynamIQ的一个cluster中,可同时包含大核和小核,达到cluster内的异构(heterogeneous cluster),而且大核和小核可以随意排列组合,例如1+3、1+7等以前无法做到的弹性配置。

- big.LITTLE每个cluster只能用一种电压,也因此同一个cluster内的各核心CPU只有一种频率,DynamIQ内的每个CPU核心都可以有不同的电压和不同的频率

- big.LITTLE每个cluster内的CPU核,共享同一块L2 Cache,DynamIQ内的每个CPU核心,都有专属的L2 Cache,再共享同一块L3 Cache,L2 Cache和L3 Cache的容量大小都是可以选择的,各核专属L2 Cache可以从256KB~512KB,各核共享L3 Cahce可以从1MB~4MB。这样的设计大幅提升了跨核数据交换的速度。 L3 Cache是DynamIQ Shared Unit(DSU)的一部分

2、cache的层级关系 ––big.LITTLE架构(A53为例)

3、cache的层级关系 –-- DynamIQ架构(A76为例)

4、DSU / L3 cache

DSU-AE 实现了系统控制寄存器,这些寄存器对cluster中的所有core都是通用的。 可以从cluster中的任何core访问这些寄存器。 这些寄存器提供:

- 控制cluster的电源管理。

- L3 cache控制。

- CHI QoS 总线控制和scheme ID分配。

- 有关DSU‑AE 硬件配置的信息,包括指定的Split‑Lock 集群执行模式。

- L3 缓存命中和未命中计数信息

L3 cache

- cache size可选 : 512KB, 1MB, 1.5MB, 2MB, or 4MB. cache line = 64bytes

- 1.5MB的cache 12路组相连

- 512KB, 1MB, 2MB, and 4MB的caches 16路组相连

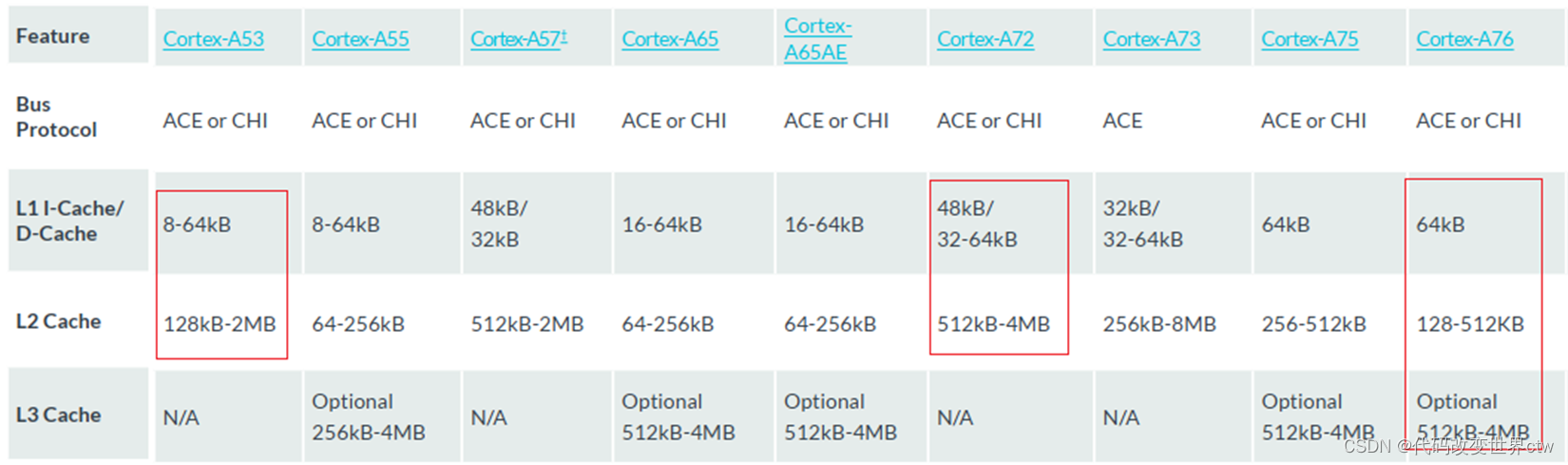

5、L1/L2/L3 cache都是多大呢

需要参考ARM文档,其实每一个core的cache大小都是固定的或可配置的。

6、cache相关的术语介绍

思考 :什么是Set、way、TAG 、index、cache line、entry?

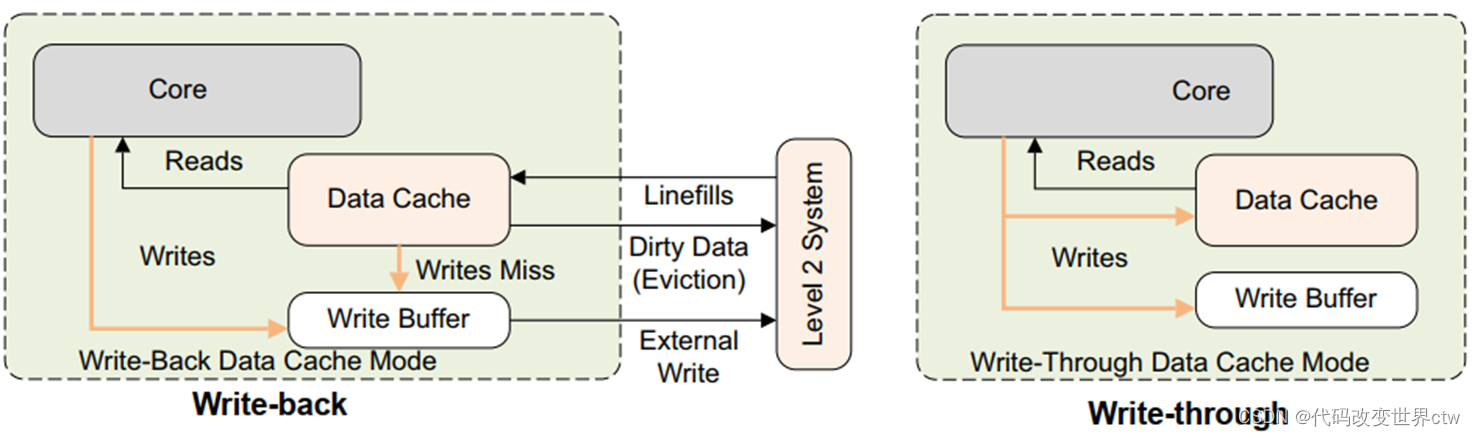

7、cache的分配策略(alocation,write-through, write-back)

-

读分配(read allocation)

当CPU读数据时,发生cache缺失,这种情况下都会分配一个cache line缓存从主存读取的数据。默认情况下,cache都支持读分配。 -

读分配(read allocation)写分配(write allocation)

当CPU写数据发生cache缺失时,才会考虑写分配策略。当我们不支持写分配的情况下,写指令只会更新主存数据,然后就结束了。当支持写分配的时候,我们首先从主存中加载数据到cache line中(相当于先做个读分配动作),然后会更新cache line中的数据。 -

写直通(write through)

当CPU执行store指令并在cache命中时,我们更新cache中的数据并且更新主存中的数据。cache和主存的数据始终保持一致。 -

读分配(read allocation)写回(write back)

当CPU执行store指令并在cache命中时,我们只更新cache中的数据。并且每个cache line中会有一个bit位记录数据是否被修改过,称之为dirty bit(翻翻前面的图片,cache line旁边有一个D就是dirty bit)。我们会将dirty bit置位。主存中的数据只会在cache line被替换或者显示的clean操作时更新。因此,主存中的数据可能是未修改的数据,而修改的数据躺在cache中。cache和主存的数据可能不一致

8、架构中内存的类型

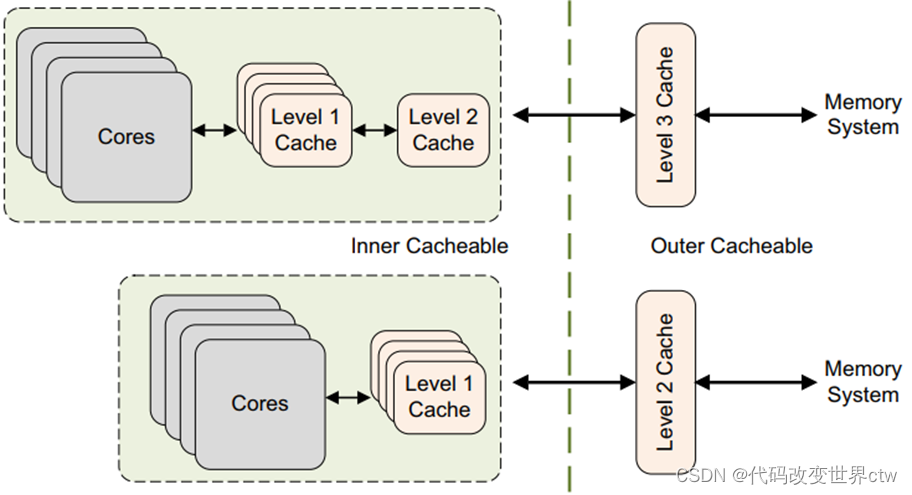

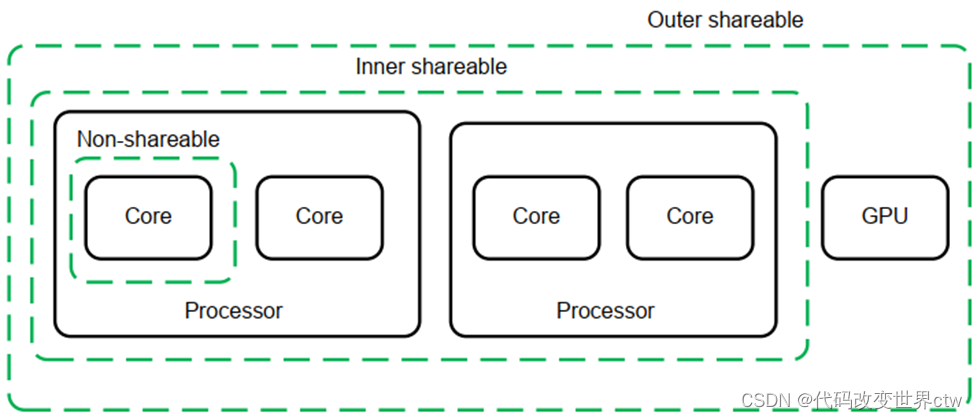

9、架构中定义的cache的范围(inner, outer)

对于cacheable属性,inner和outer描述的是cache的定义或分类。比如把L1/L1看做是inner,把L3看做是outer

通常,内部集成的cache属于inner cache,外部总线AMBA上的cache属于outer cache。例如:

- 对于上述的big.LITTLE架构(A53为例)中,L1/L2属于inner cache,如果SOC上挂了L3的话,则其属于outer cache

- 对于上述的DynamIQ架构(A76为例)中,L1/L2/L3属于inner cache,如果SOC上挂了System cache(或其它名称)的话,则其属于outer cache

然后我们可以对每类cache进行单独是属性配置,例如:

- 配置 inner Non-cacheable 、配置 inner Write-Through Cacheable 、配置 inner Write-back Cacheable

- 配置 outer Non-cacheable 、配置 outer Write-Through Cacheable 、配置 outer Write-back Cacheable

对于shareable属性,inner和outer描述的是cache的范围。比如inner是指L1/L2范围内的cache,outer是指L1/L2/L3范围内的cache

以下再次对Inner/Outer属性做了一个小小的总结:

-

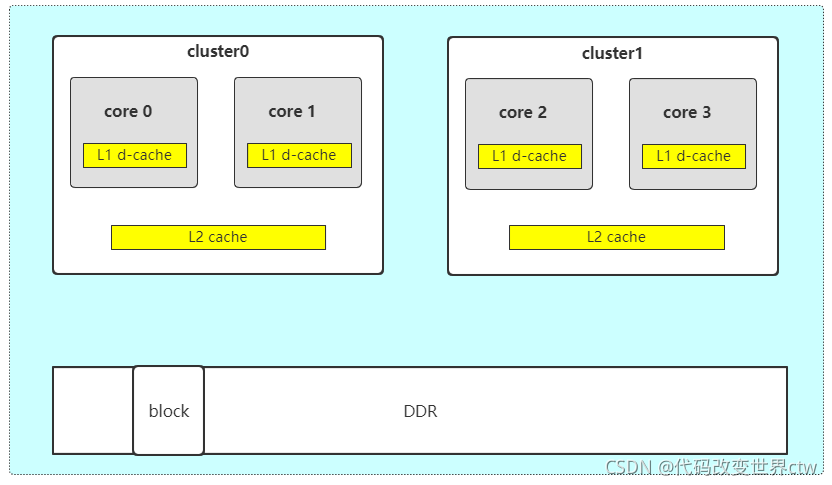

如果将block的内存属性配置成Non-cacheable,那么数据就不会被缓存到cache,那么所有observer看到的内存是一致的,也就说此时也相当于Outer Shareable。

其实官方文档,也有这一句的描述:

在B2.7.2章节 “Data accesses to memory locations are coherent for all observers in the system, and correspondingly are treated as being Outer Shareable” -

如果将block的内存属性配置成write-through cacheable 或 write-back cacheable,那么数据会被缓存cache中。write-through和write-back是缓存策略。

-

如果将block的内存属性配置成 non-shareable, 那么core0访问该内存时,数据缓存的到Core0的L1 d-cache 和 cluster0的L2 cache,不会缓存到其它cache中

-

如果将block的内存属性配置成 inner-shareable, 那么core0访问该内存时,数据只会缓存到core 0和core 1的L1 d-cache中, 也会缓存到clustor0的L2 cache,不会缓存到clustor1中的任何cache里。

-

如果将block的内存属性配置成 outer-shareable, 那么core0访问该内存时,数据会缓存到所有cache中

| Non-cacheable | write-through cacheable | write-back cacheable | |

|---|---|---|---|

| non-shareable | 数据不会缓存到cache (对于观察则而言,又相当于outer-shareable) | Core0读取时,数据缓存的到Core0的L1 d-cache 和 cluster0的L2 cache, 如果core0和core1都读写过该内存,且在core0 core1的L1 d-cache中都缓存了该内存。那么core0在读取数据的时候,core0的L1 Dcache会更新,但core 1的L1 Dcache不会更新 | 同左侧 |

| inner-shareable | 数据不会缓存到cache (对于观察则而言,又相当于outer-shareable) | Core0读取时,数据缓存的到Cluster0中所有cache | 同左侧 |

| outer-shareable | 数据不会缓存到cache (对于观察则而言,又相当于outer-shareable) | Core0读取时,数据缓存的到所有cache | 同左侧 |

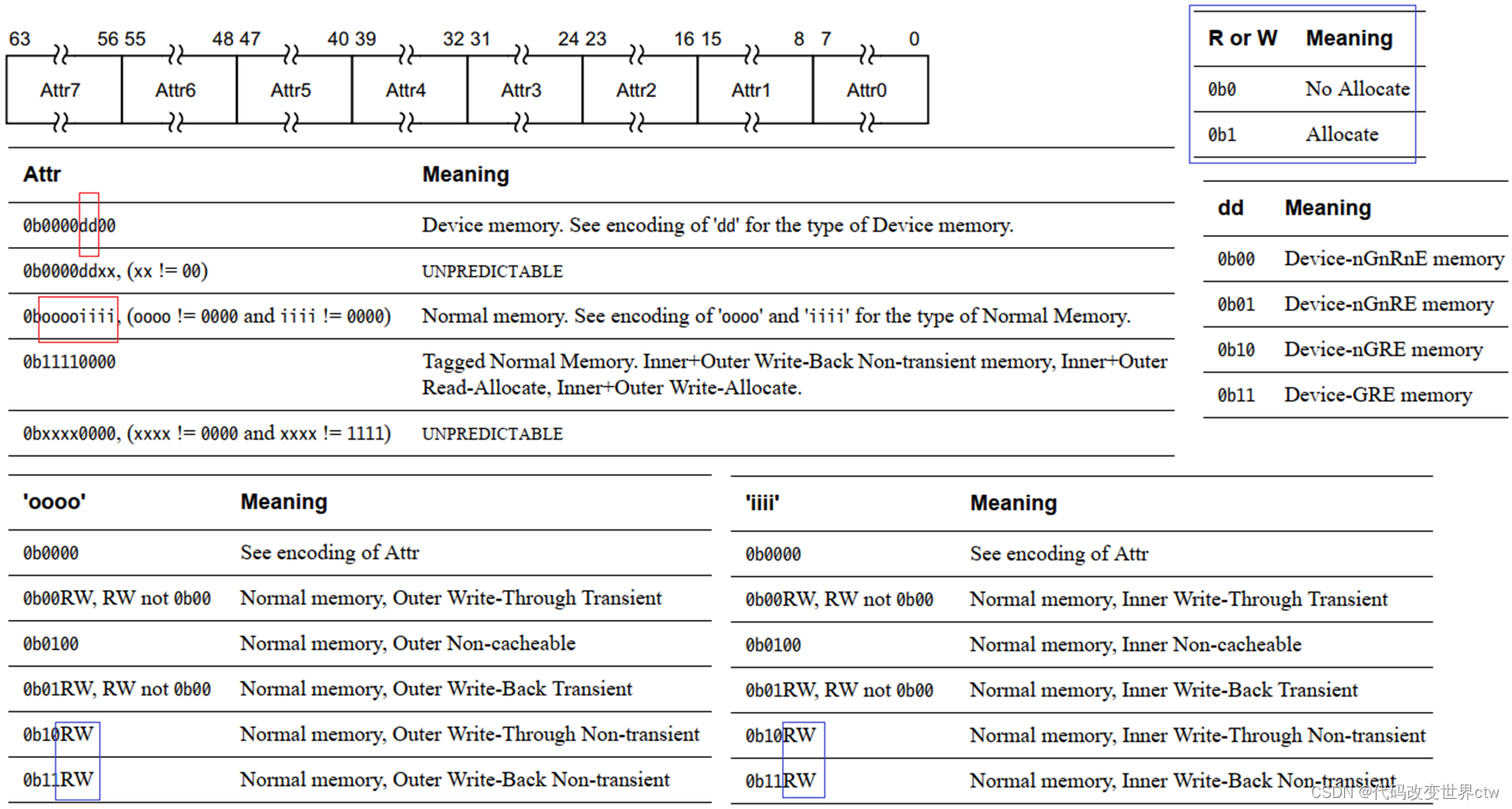

10、架构中内存的类型 (mair_elx寄存器)

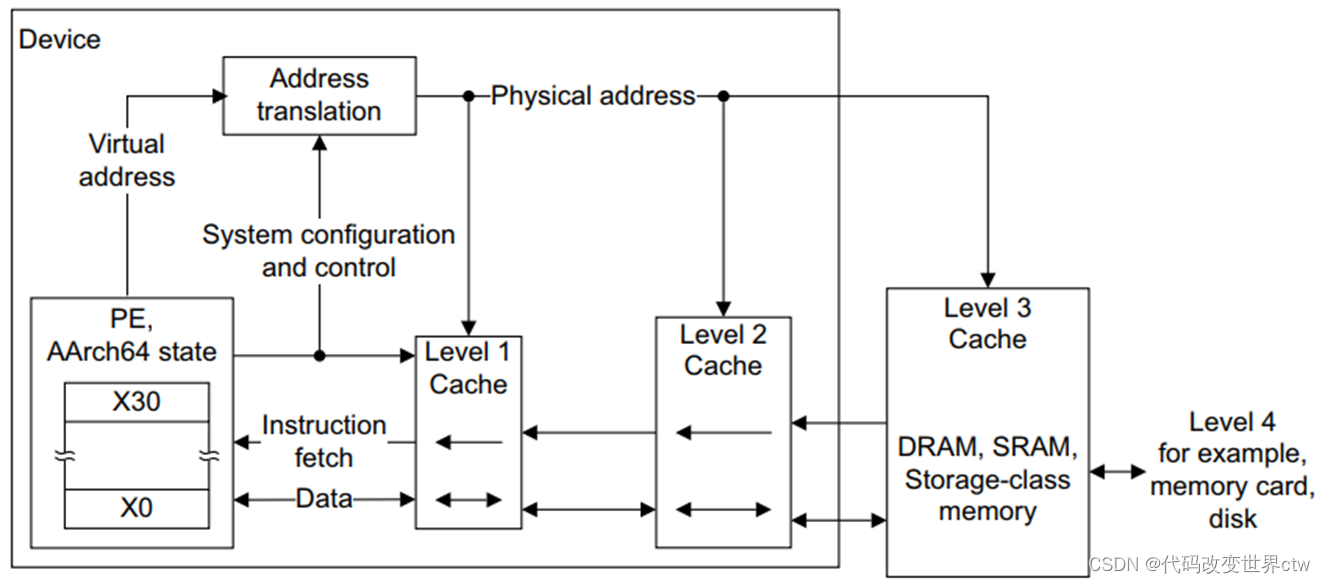

11、cache的种类(VIVT,PIPT,VIPT)

MMU由TLB和Address Translation 组成:

- Translation Lookaside Buffer

- TAddress Translation

cache又分为;

- PIPT

- VIVT

- VIPT

12、Inclusive and exclusive caches

先讨论一个简单的内存读取,单核的. 如LDR X0, [X1], 假设X1指向main memory,且是cacheable.

(1)、Core先去L1 cache读取,hit了,直接返回数据给Core

(2)、Core先去L1 cache读取,miss了,然后会查询L2 cache,hit了,L2的cache数据会返回Core,还会导致这个cache line替换到L1中的某一行cache line

(3)、如果L1 L2都是miss,那么data将会从内存中读取,缓存到L1和L2,并返回给Core

接着我们再看一个复杂的系统,不考虑L3,多核的.

(1)、如果是inclusive cache,那么数据将会被同时缓存到L1和L2

(2)、如果是exclusive cache,那么数据只缓存到L1,不会缓存到L2

- Strictly inclusive: Any cache line present in an L1 cache will also be present in the L2

- Weakly inclusive: Cache line will be allocated in L1 and L2 on a miss, but can later be evicted from L2

- Fully exclusive: Any cache line present in an L1 cache will not be present in the L2

13、cache的查询过程(非官方,白话)

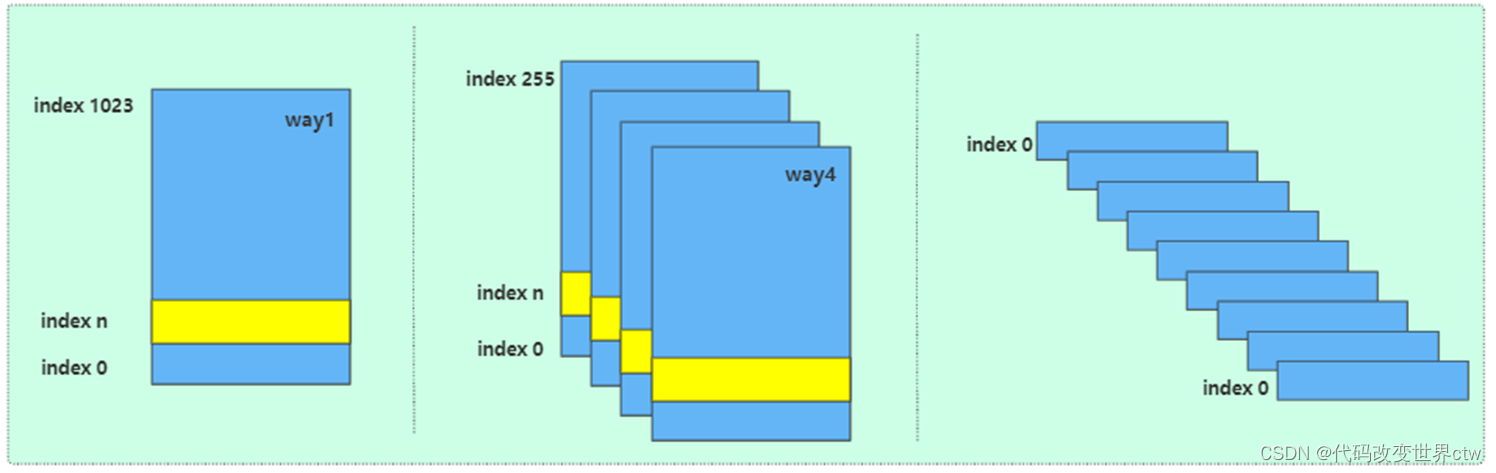

假设一个4路相连的cache,大小64KB, cache line = 64bytes,那么 1 way = 16KB,indexs = 16KB / 64bytes = 256 (注: 0x4000 = 16KB、0x40 = 64 bytes)

0x4000 – index 0

0x4040 – index 1

0x4080 – index 2

…

0x7fc0 – index 2550x8000 – index 0

0x8040 – index 1

0x8080 – index 2

…

0xbfc0 – index 255

14、cache的组织形式(index, way, set)

- 全相连

- 直接相连

- 4路组相连

例如 A76

-

L1 i-cache :64KB,4路256组相连,cache line为64bytes

-

TLB i-cache :全相连,支持4KB, 16KB, 64KB, 2MB,32M的页

-

L1 d-cache :64KB,4路256组相连,cache line位64bytes

-

TLB d-cache :全相连,支持4KB, 16KB, 64KB, 2MB,512MB的页

-

L2 cache :8路相连的cache,大小可选128KB, 256KB, or 512KB

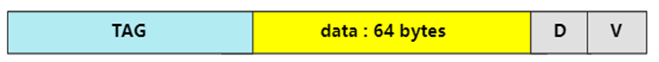

15、cache line里都有什么

Each line in the cache includes:

• A tag value from the associated Physical Address.

• Valid bits to indicate whether the line exists in the cache, that is whether the tag is valid.

Valid bits can also be state bits for MESI state if the cache is coherent across multiple cores.

• Dirty data bits to indicate whether the data in the cache line is not coherent with external memory

• data

那么TAG里又都有什么呢??(S13 才会说这里的TAG等于物理地址里的TAG)

如下以A78为例,展示了TAG里都有什么

补充一点:TLB里都有什么? 同样以为A78为例;

16、cache查询示例

17、cache查询原理

先使用index去查询cache,然后再比较TAG,比较tag的时候还会检查valid标志位

18、cache maintenance

软件维护操作cache的指令有三类:

- Invalidation:其实就是修改valid bit,让cache无效,主要用于读

- Cleaning: 其实就是我们所说的flush cache,这里会将cache数据回写到内存,并清楚dirty标志

- Zero:将cache中的数据清0, 这里其实是我们所说的clean cache.

什么时候需要软件维护cache:

(1)、当有其它的Master改变的external memory,如DMA操作

(2)、MMU的enable或disable的整个区间的内存访问,如REE enable了mmu,TEE disable了mmu.

针对第(2)点,cache怎么和mmu扯上关系了呢?那是因为:

mmu的开启和关闭,影响了内存的permissions, cache policies

19、软件中维护内存一致性 – invalid cache

20、软件中维护内存一致性 – flush cache

21、cache一致性指令介绍

<cache> <operation>{, <Xt>}

22、PoC/PoU point介绍

- PoC is the point at which all observers, for example, cores, DSPs, or DMA engines, that can access memory, are guaranteed to see the same copy of a memory location

- PoU for a core is the point at which the instruction and data caches and translation table walks of the core are guaranteed to see the same copy of a memory location

23、cache一致性指令的总结

24、Kernel中使用cache一致性指令的示例

25、Linux Kernel Cache API

linux/arch/arm64/mm/cache.S

linux/arch/arm64/include/asm/cacheflush.hvoid __flush_icache_range(unsigned long start, unsigned long end);

int invalidate_icache_range(unsigned long start, unsigned long end);

void __flush_dcache_area(void *addr, size_t len);

void __inval_dcache_area(void *addr, size_t len);

void __clean_dcache_area_poc(void *addr, size_t len);

void __clean_dcache_area_pop(void *addr, size_t len);

void __clean_dcache_area_pou(void *addr, size_t len);

long __flush_cache_user_range(unsigned long start, unsigned long end);

void sync_icache_aliases(void *kaddr, unsigned long len);

void flush_icache_range(unsigned long start, unsigned long end)

void __flush_icache_all(void)

26、A76的cache介绍

A76

-

L1 i-cache :64KB,4路256组相连,cache line为64bytes

-

L1 d-cache :64KB,4路256组相连,cache line为64bytes

-

L2 cache :8路相连的cache,大小可选128KB, 256KB, or 512KB

-

L1 TLB i-cache :48 entries, 全相连,支持4KB, 16KB, 64KB, 2MB,32M的页

-

L1 TLB d-cache : 48 entries,全相连,支持4KB, 16KB, 64KB, 2MB,512MB的页

-

L2 TLB cache : 1280 entries, 5路组相连

-

L3 cache

cache size可选 : 512KB, 1MB, 1.5MB, 2MB, or 4MB. cache line = 64bytes

1.5MB的cache 12路组相连

512KB, 1MB, 2MB, and 4MB的caches 16路组相连

27、A78的cache介绍

A78

-

L1 i-cache :32或64KB,4路组相连,cache line为64bytes , VIPT

-

L1 d-cache : 32或64KB,4路组相连,cache line为64bytes, VIPT

-

L1 TLB i-cache :32 entries, 全相连,支持4KB, 16KB, 64KB, 2MB,32M的页

-

L1 TLB d-cache : 32 entries,全相连,支持4KB, 16KB, 64KB, 2MB,512MB的页

-

L2 TLB cache : 1024 entries, 4路组相连

-

L3 cache

cache size可选 : 512KB, 1MB, 1.5MB, 2MB, or 4MB. cache line = 64bytes

1.5MB的cache 12路组相连

512KB, 1MB, 2MB, and 4MB的caches 16路组相连

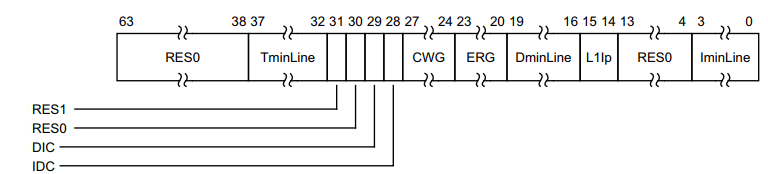

28、armv8/armv9中的cache相关的系统寄存器

ID Register

CTR_EL0, Cache Type Register

- IminLine, bits [3:0]

Log2 of the number of words in the smallest cache line of all the instruction caches that are controlled by the PE. - DminLine, bits [19:16]

Log2 of the number of words in the smallest cache line of all the data caches and unified caches that are controlled by the PE

29、多核之间的cache一致性

对于 Big.LITTLE架构

对于 DynamIQ架构

30、MESI/MOESI的介绍

Events:

- RH = Read Hit

- RMS = Read miss, shared

- RME = Read miss, exclusive

- WH = Write hit

- WM = Write miss

- SHR = Snoop hit on read

- SHI = Snoop hit on invalidate

- LRU = LRU replacement

Bus Transactions:

- Push = Write cache line back to memory

- Invalidate = Broadcast invalidate

- Read = Read cache line from memory

推荐

- ARMv8/ARMv9架构从入门到精通 --博客专栏

- 《Armv8/Armv9架构从入门到精通 第二期》 --大课程

- 8天入门ARM架构 --入门课程

关注"Arm精选"公众号,备注进ARM交流讨论区。

相关文章:

深度学习armv8/armv9 cache的原理

快速链接: 【精选】ARMv8/ARMv9架构入门到精通-[目录] 👈👈👈 1、为什么要用cache? ARM 架构刚开始开发时,处理器的时钟速度和内存的访问速度大致相似。今天的处理器内核要复杂得多,并且时钟频率可以快几个数量级。然…...

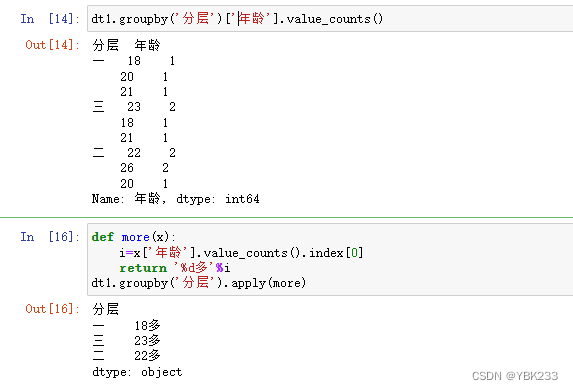

Python基础之pandas:文件读取与数据处理

提示:文章写完后,目录可以自动生成,如何生成可参考右边的帮助文档 文章目录 一、文件读取1.以pd.read_csv()为例:2.数据查看 二、数据离散化、排序1.pd.cut()离散化,以按范围加标签为例2. pd.qcut()实现离散化3.排序4.…...

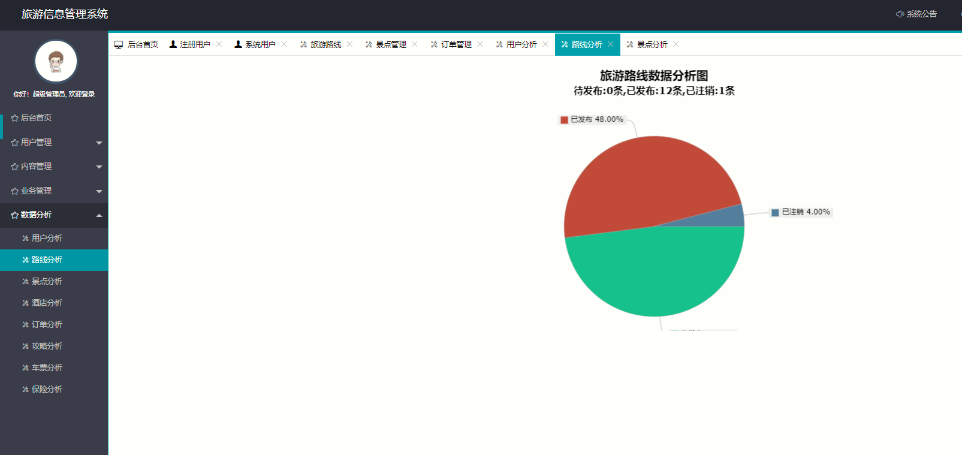

基于Springboot旅游网站管理系统设计和实现

基于Springboot旅游网站管理系统设计和实现 博主介绍:多年java开发经验,专注Java开发、定制、远程、文档编写指导等,csdn特邀作者、专注于Java技术领域 作者主页 央顺技术团队 Java毕设项目精品实战案例《1000套》 欢迎点赞 收藏 ⭐留言 文末获取源码联系…...

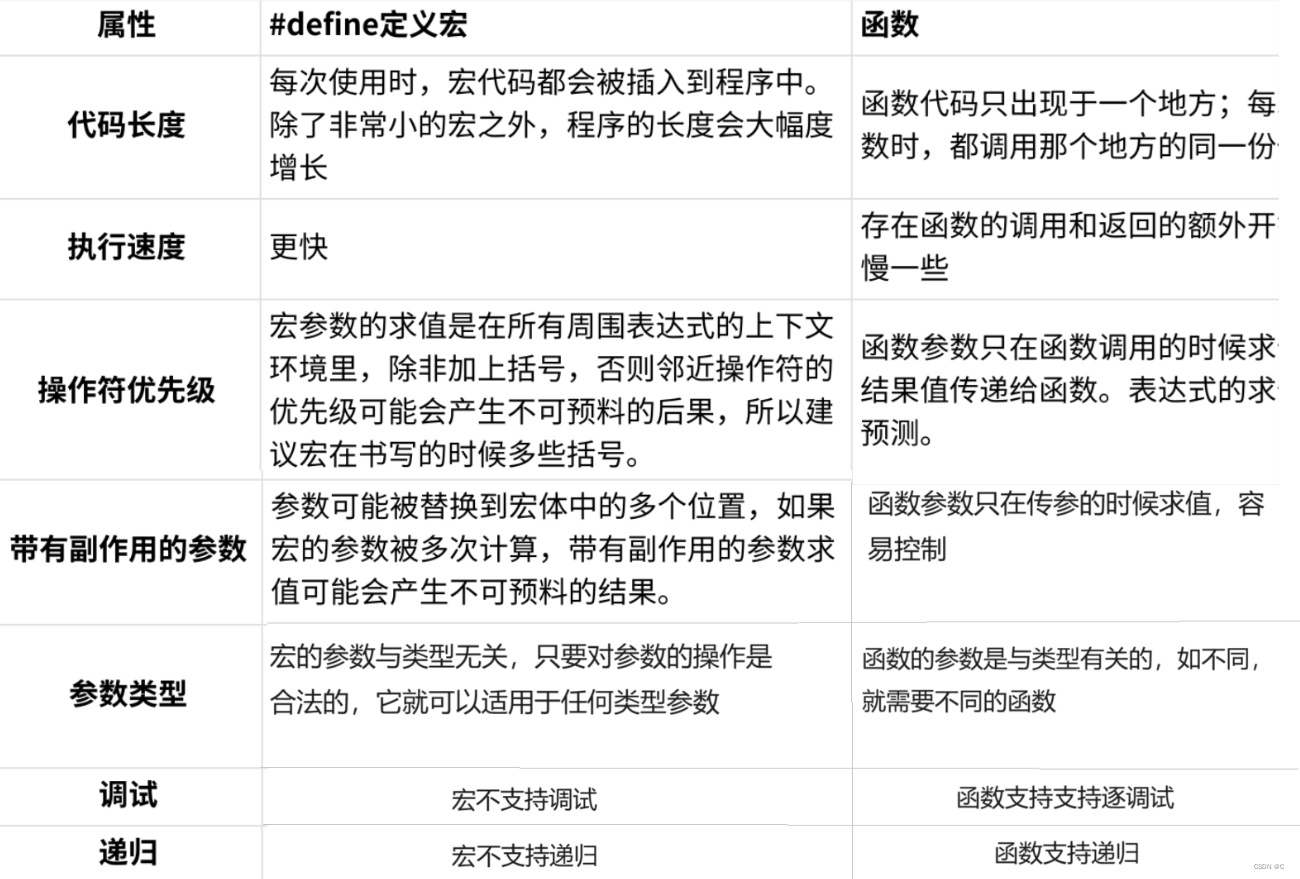

深度解析C语言——预处理详解

对C语言有一定了解的同学,相信对预处理一定不会陌生。今天我们就来聊一聊一些预处理的相关知识。预处理是在编译之前对源文件进行简单加工的过程,主要是处理以#开头的命令,例如#include <stdio.h>、#define等。预处理是C语言的一个重要…...

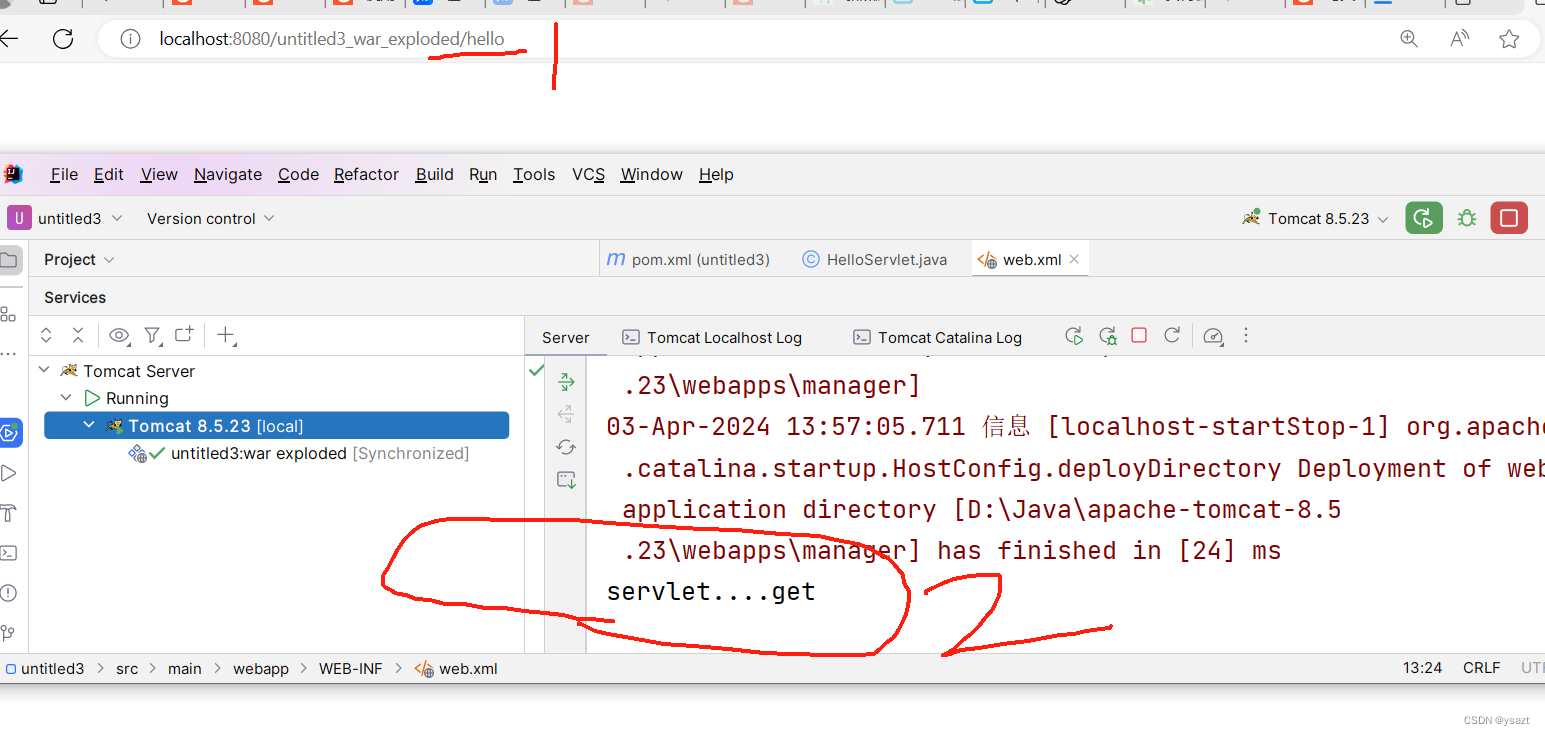

idea2023.2.1 java项目-web项目创建-servlet类得创建

如何创建Java项目 1.1 方式1: 1.2 方式: 1.3 方式 如何创建web项目 方式 ----- 推荐 如何创建servlet类 复制6 中得代码 给servlet 配置一个路径 启动tomcat 成功了...

Ollama教程——入门:开启本地大型语言模型开发之旅

Ollama教程——入门:开启本地大型语言模型开发之旅 引言安装ollamamacOSWindows预览版LinuxDocker ollama的库和工具ollama-pythonollama-js 快速开始运行模型访问模型库 自定义模型从GGUF导入模型自定义提示 CLI参考创建模型拉取模型删除模型复制模型多行输入多模态…...

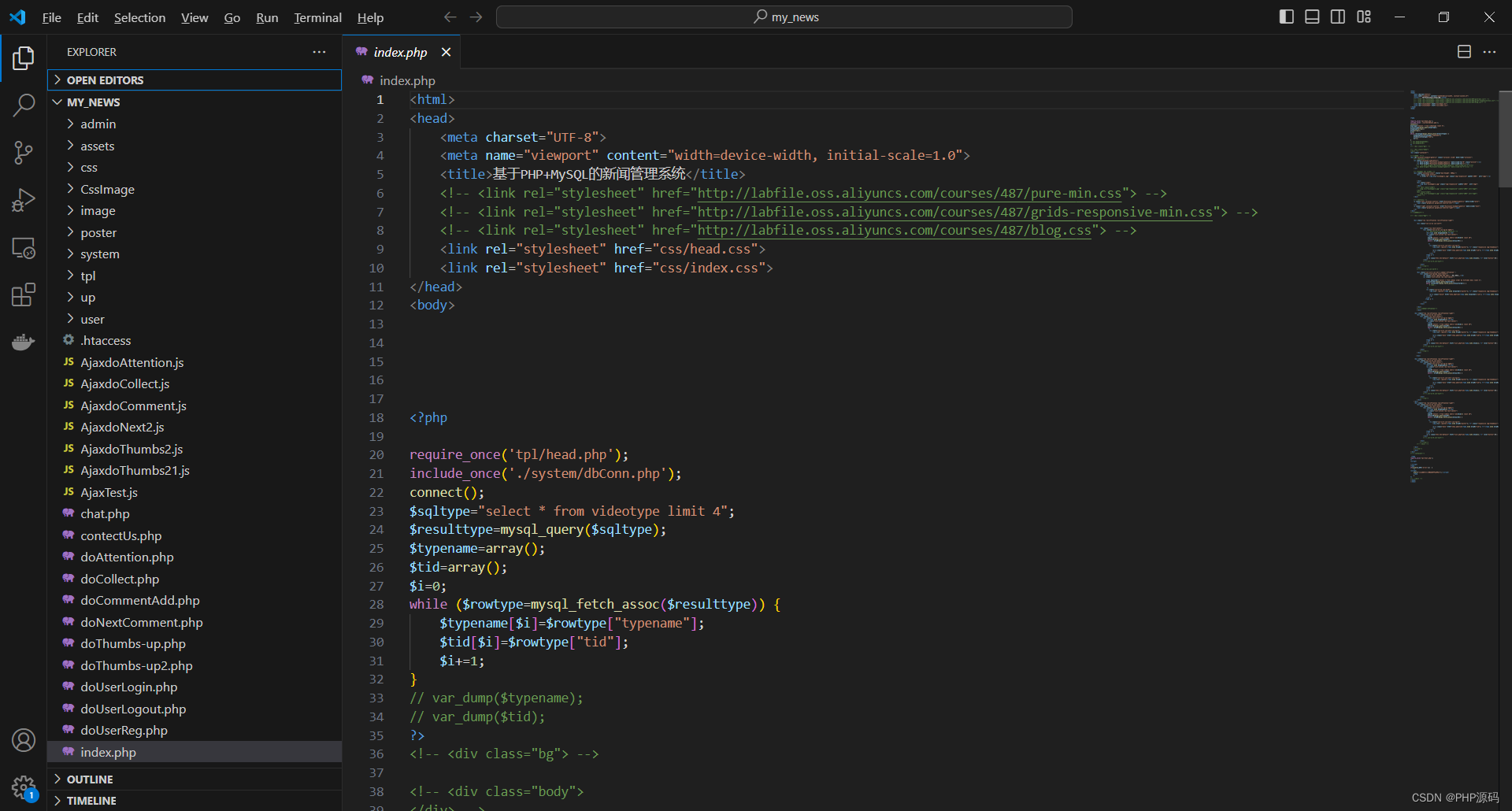

基于PHP的新闻管理系统(用户发布版)

有需要请加文章底部Q哦 可远程调试 基于PHP的新闻管理系统(用户发布版) 一 介绍 此新闻管理系统基于原生PHP开发,数据库mysql,前端bootstrap。系统角色分为用户和管理员。本新闻管理系统采用用户发布新闻,管理员审核后展示模式。 技术栈&am…...

基础篇3 浅试Python爬虫爬取视频,m3u8标准的切片视频

浅试Python爬取视频 1.页面分析 使用虾米视频在线解析使用方式:https://jx.xmflv.cc/?url目标网站视频链接例如某艺的视频 原视频链接 解析结果: 1.1 F12查看页面结构 我们发现页面内容中什么都没有,video标签中的src路径也不是视频的数据。 1.2 …...

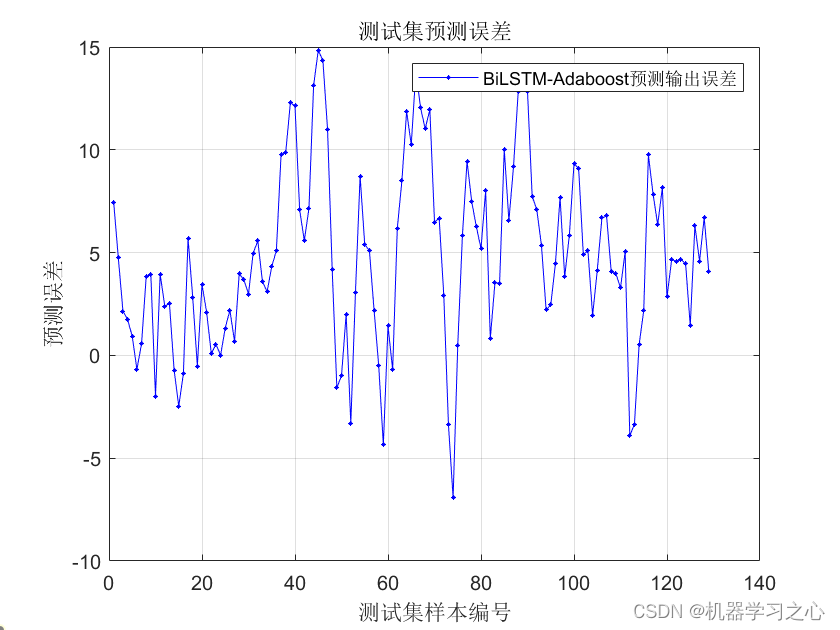

Adaboost集成学习 | Matlab实现基于BiLSTM-Adaboost双向长短期记忆神经网络结合Adaboost集成学习时间序列预测(股票价格预测)

目录 效果一览基本介绍模型设计程序设计参考资料效果一览 基本介绍 Matlab实现基于BiLSTM-Adaboost双向长短期记忆神经网络结合Adaboost集成学习时间序列预测(股票价格预测) 模型设计 股票价格预测是一个具有挑战性的时间序列预测问题,可以使用深度学习模型如双向长短期记忆…...

MySQL两表联查之分组成绩第几问题

MySQL 数据库操作实践:两表联查之分组成绩第几问题 在本篇博客中,我将展示MySQL 从创建表、到插入数据,并进行一些复杂的查询操作。 1. 建立表格 首先,我们创建两个表:department(部门)和 em…...

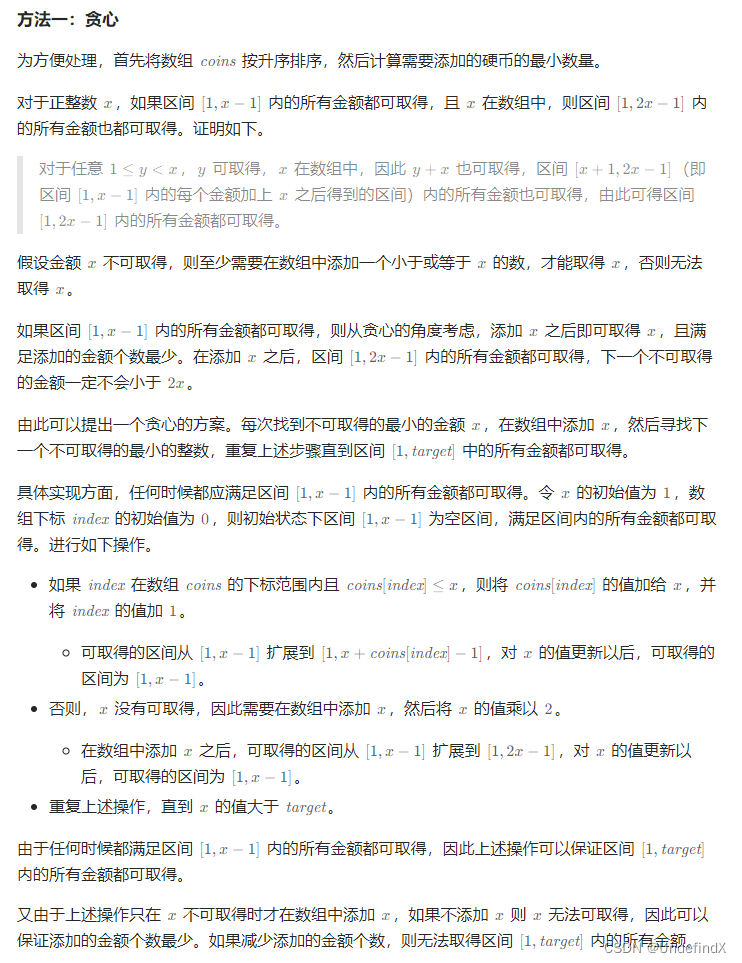

每日一题(leetcode2952):添加硬币最小数量 初识贪心算法

这道题如果整体去思考,情况会比较复杂。因此我们考虑使用贪心算法。 1 我们可以假定一个X,认为[1,X-1]区间的金额都可以取到,不断去扩张X直到大于target。(这里为什么要用[1,X-1]而不是[1,X],总的来说是方便,潜在思想…...

[Errno 2] No such file or directory: ‘g++‘

报错解释: 这个错误表明系统试图访问名为g++的文件或目录,但没有找到。g++是GNU编译器集合(GNU Compiler Collection)中的C++编译器。如果系统中没有安装g++或者g++不在环境变量的路径中,就会出现这个错误。 解决方法: 确认g++是否已安装: 在Linux上,可以尝试运行g+…...

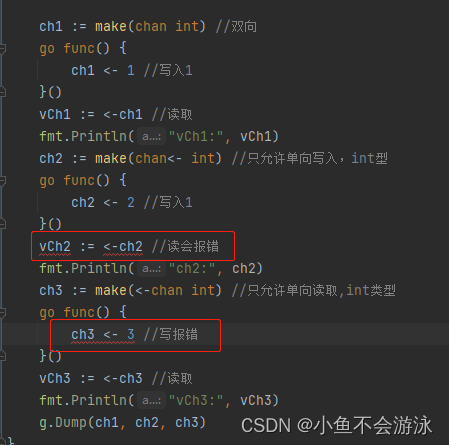

go的通信Channel

一、channel是什么 1.一种通信机制 channel是goroutine与goroutine之间数据通信的一种通信机制。一般都是2个g及以上一起工作。 channel与关键字range和select紧密相关。 二、channel的结构 go源码:GitHub - golang/go: The Go programming language src/runt…...

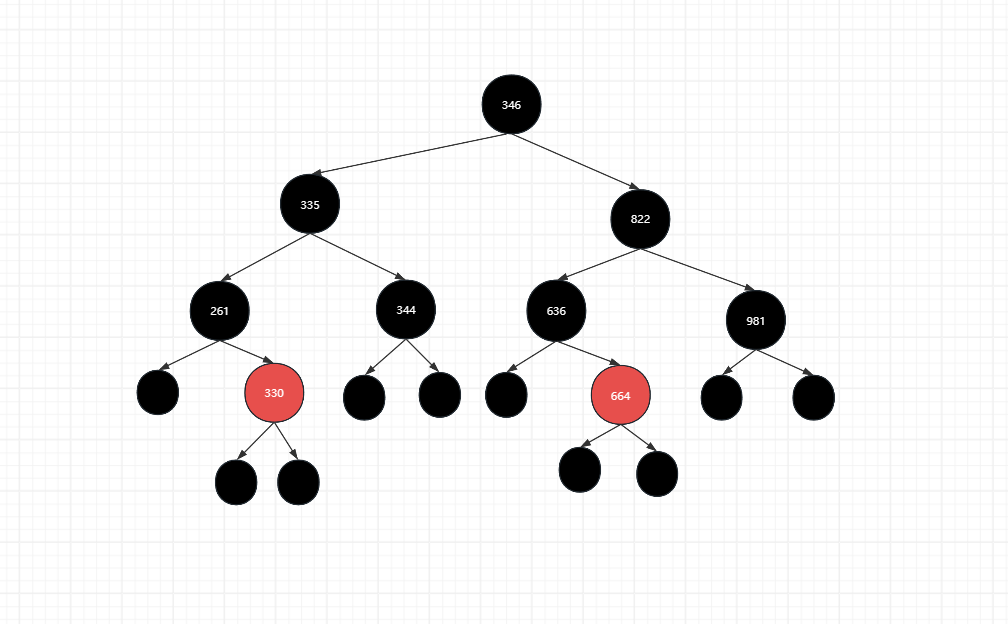

手写红黑树【数据结构】

手写红黑树【数据结构】 前言版权推荐手写红黑树一、理论知识红黑树的特征增加删除 二、手写代码初始-树结点初始-红黑树初始-遍历初始-判断红黑树是否有效查找增加-1.父为黑,直接插入增加-2. 父叔为红,颜色调换增加-3. 父红叔黑,颜色调换&am…...

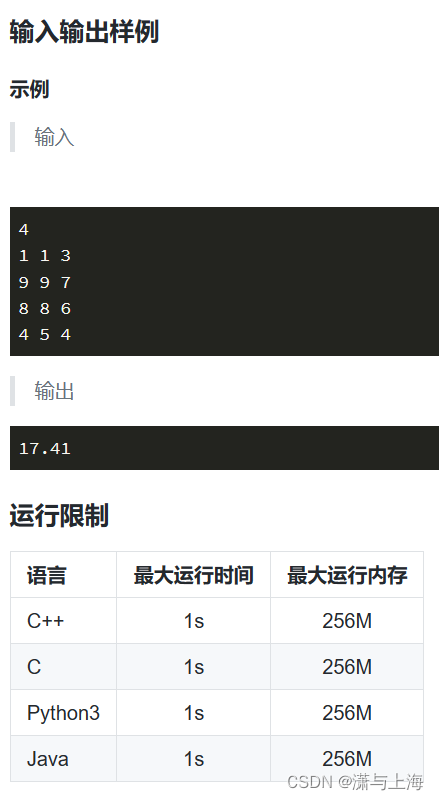

[蓝桥杯练习]通电

kruskal做法(加边) #include <bits/stdc.h> using namespace std; int x[10005],y[10005],z[10005];//存储i点的x与y坐标 int bcj[10005];//并查集 struct Edge{//边 int v1,v2; double w; }edge[2000005]; int cmp(Edge a, Edge b){return a.w < b.w;} int find(i…...

安全算法 - 摘要算法

摘要算法是一种将任意长度的数据转换为固定长度字节串的算法。它具有以下特点和应用。 首先,摘要算法能够生成一个唯一且固定长度的摘要值,用于验证数据的完整性和一致性。无论输入数据有多长,生成的摘要值始终是固定长度的,且即…...

操作系统:动静态库

目录 1.动静态库 1.1.如何制作一个库 1.2.静态库的使用和管理 1.3.安装和使用库 1.4.动态库 1.4.1.动态库的实现 1.4.2.动态库与静态库的区别 1.4.3.共享动态库给系统的方法 2.动态链接 2.1.操作系统层面的动态链接 1.动静态库 静态库(.a)&…...

车载电子电器架构 —— 局部网络管理汇总

车载电子电器架构 —— 局部网络管理汇总 我是穿拖鞋的汉子,魔都中坚持长期主义的汽车电子工程师。 老规矩,分享一段喜欢的文字,避免自己成为高知识低文化的工程师: 屏蔽力是信息过载时代一个人的特殊竞争力,任何消耗你的人和事,多看一眼都是你的不对。非必要不费力证明…...

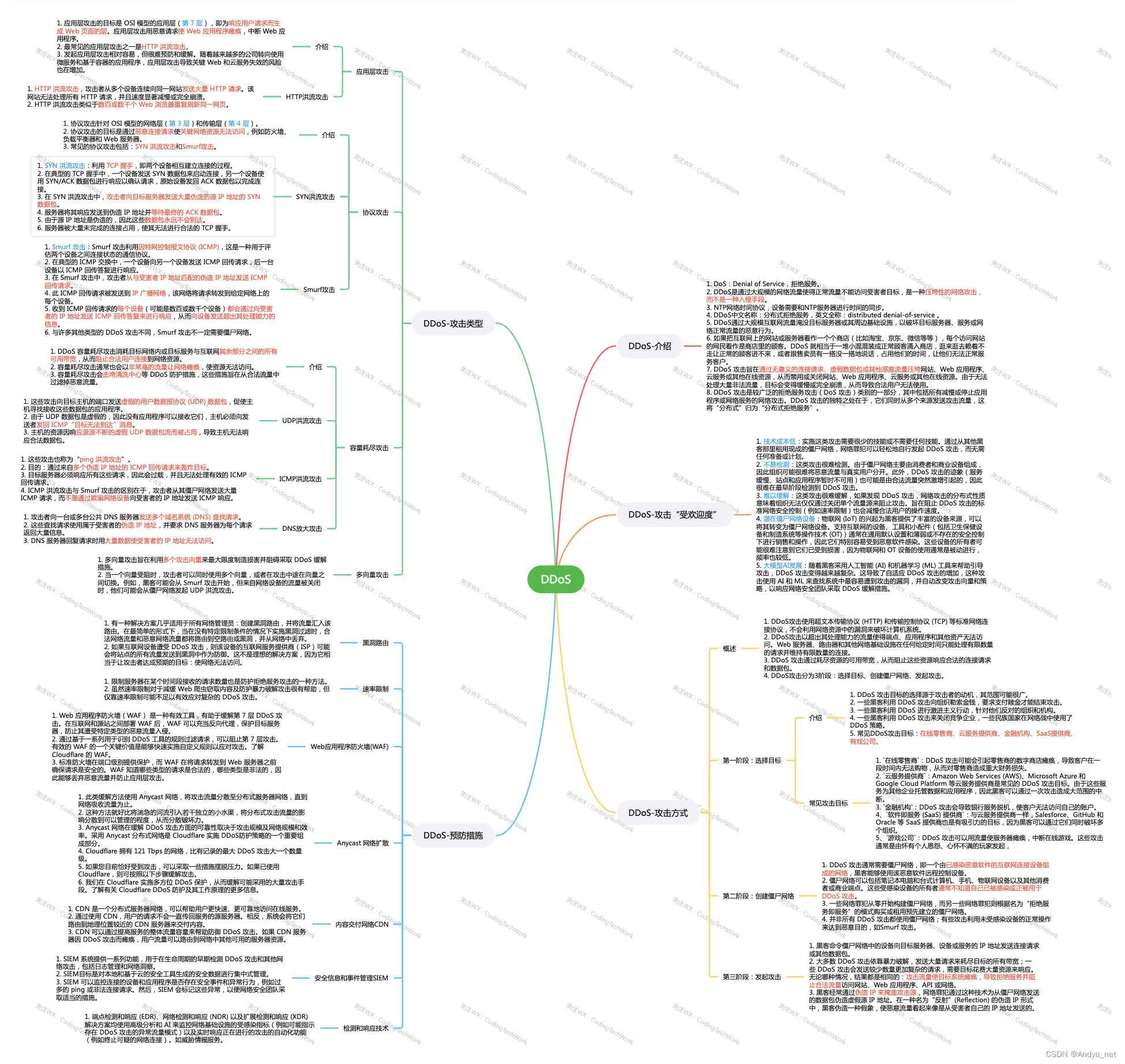

网络安全 | 什么是DDoS攻击?

关注WX:CodingTechWork DDoS-介绍 DoS:Denial of Service,拒绝服务。DDoS是通过大规模的网络流量使得正常流量不能访问受害者目标,是一种压垮性的网络攻击,而不是一种入侵手段。NTP网络时间协议,设备需要…...

[Godot] 3D拾取

CollisionObject3D文档 Camera3D文档 CollisionObject3D有个信号_input_event,可以用于处理3D拾取。 Camera3D也有project_position用于将屏幕空间坐标投影到3D空间。 extends Node3D#是否处于选中状态 var selected : bool false #摄像机的前向量 var front : V…...

Vim 调用外部命令学习笔记

Vim 外部命令集成完全指南 文章目录 Vim 外部命令集成完全指南核心概念理解命令语法解析语法对比 常用外部命令详解文本排序与去重文本筛选与搜索高级 grep 搜索技巧文本替换与编辑字符处理高级文本处理编程语言处理其他实用命令 范围操作示例指定行范围处理复合命令示例 实用技…...

eNSP-Cloud(实现本地电脑与eNSP内设备之间通信)

说明: 想象一下,你正在用eNSP搭建一个虚拟的网络世界,里面有虚拟的路由器、交换机、电脑(PC)等等。这些设备都在你的电脑里面“运行”,它们之间可以互相通信,就像一个封闭的小王国。 但是&#…...

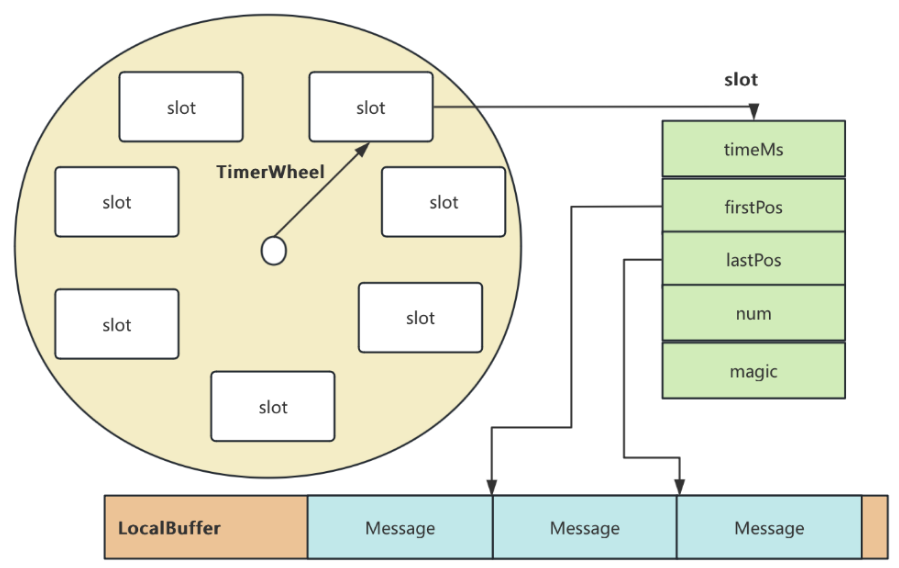

RocketMQ延迟消息机制

两种延迟消息 RocketMQ中提供了两种延迟消息机制 指定固定的延迟级别 通过在Message中设定一个MessageDelayLevel参数,对应18个预设的延迟级别指定时间点的延迟级别 通过在Message中设定一个DeliverTimeMS指定一个Long类型表示的具体时间点。到了时间点后…...

汽车生产虚拟实训中的技能提升与生产优化

在制造业蓬勃发展的大背景下,虚拟教学实训宛如一颗璀璨的新星,正发挥着不可或缺且日益凸显的关键作用,源源不断地为企业的稳健前行与创新发展注入磅礴强大的动力。就以汽车制造企业这一极具代表性的行业主体为例,汽车生产线上各类…...

测试markdown--肇兴

day1: 1、去程:7:04 --11:32高铁 高铁右转上售票大厅2楼,穿过候车厅下一楼,上大巴车 ¥10/人 **2、到达:**12点多到达寨子,买门票,美团/抖音:¥78人 3、中饭&a…...

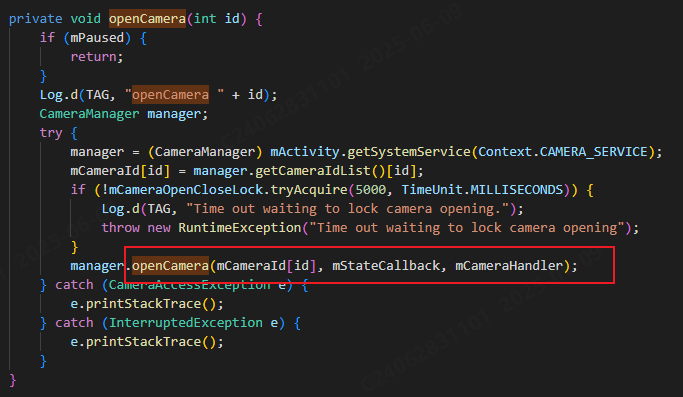

相机从app启动流程

一、流程框架图 二、具体流程分析 1、得到cameralist和对应的静态信息 目录如下: 重点代码分析: 启动相机前,先要通过getCameraIdList获取camera的个数以及id,然后可以通过getCameraCharacteristics获取对应id camera的capabilities(静态信息)进行一些openCamera前的…...

招商蛇口 | 执笔CID,启幕低密生活新境

作为中国城市生长的力量,招商蛇口以“美好生活承载者”为使命,深耕全球111座城市,以央企担当匠造时代理想人居。从深圳湾的开拓基因到西安高新CID的战略落子,招商蛇口始终与城市发展同频共振,以建筑诠释对土地与生活的…...

集成 Mybatis-Plus 和 Mybatis-Plus-Join)

纯 Java 项目(非 SpringBoot)集成 Mybatis-Plus 和 Mybatis-Plus-Join

纯 Java 项目(非 SpringBoot)集成 Mybatis-Plus 和 Mybatis-Plus-Join 1、依赖1.1、依赖版本1.2、pom.xml 2、代码2.1、SqlSession 构造器2.2、MybatisPlus代码生成器2.3、获取 config.yml 配置2.3.1、config.yml2.3.2、项目配置类 2.4、ftl 模板2.4.1、…...

Go语言多线程问题

打印零与奇偶数(leetcode 1116) 方法1:使用互斥锁和条件变量 package mainimport ("fmt""sync" )type ZeroEvenOdd struct {n intzeroMutex sync.MutexevenMutex sync.MutexoddMutex sync.Mutexcurrent int…...

Git常用命令完全指南:从入门到精通

Git常用命令完全指南:从入门到精通 一、基础配置命令 1. 用户信息配置 # 设置全局用户名 git config --global user.name "你的名字"# 设置全局邮箱 git config --global user.email "你的邮箱example.com"# 查看所有配置 git config --list…...