【FPGA】 MIPS 12条整数指令【2】

目录

仿真

代码

完整代码

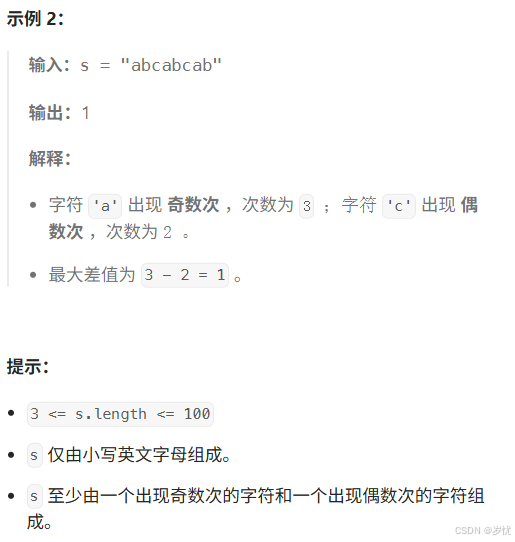

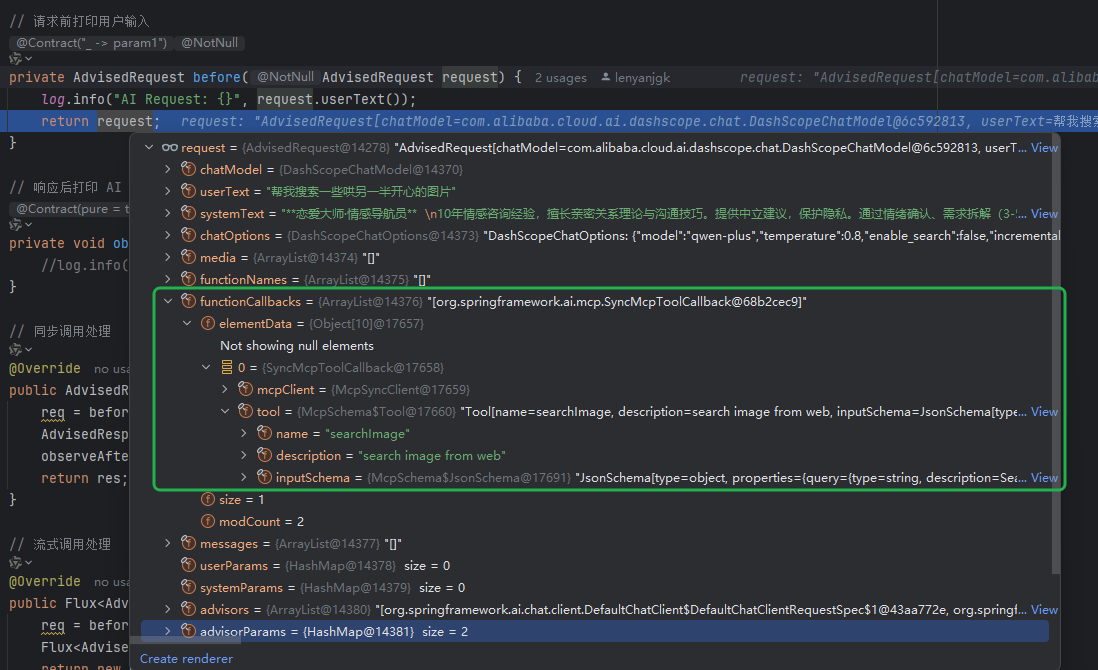

实现slt

仿真

ori r1,r0,1100h

ori r2,r0,0020h

ori r3,r0,ff00h

ori r4,r0,ffffhaddi r5,r0,ffff

slt r6,r5,r4

slt r6,r4,r3

代码

EX

`Slt:regcData = ($signed(regaData)<$signed(regbData))?1'b1:1'b0;ID

`Inst_slt:beginop = `Slt;regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11]; imm = `Zero;end完整代码

`include "define.v";

module ID (input wire rst, input wire [31:0] pc, //Jinput wire [31:0] inst,input wire [31:0] regaData_i,input wire [31:0] regbData_i,output reg [5:0] op, output reg [31:0] regaData,output reg [31:0] regbData,output reg regaRead,output reg regbRead,output reg regcWrite,output reg [4:0] regaAddr,output reg [4:0] regbAddr, output reg [4:0] regcAddr,output reg [31:0] jAddr, //Joutput reg jCe//J);wire [5:0] inst_op = inst[31:26]; reg [31:0] imm;//Rwire[5:0] func = inst[5:0]; //Jwire [31:0] npc = pc + 4;always@(*)if(rst == `RstEnable)beginop = `Nop; regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;imm = `Zero;jCe = `Invalid;//JjAddr = `Zero;//Jendelse beginjCe = `Invalid;//JjAddr = `Zero;//Jcase(inst_op)`Inst_ori:beginop = `Or; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {16'h0, inst[15:0]};end`Inst_andi:beginop = `And; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {16'h0, inst[15:0]};end`Inst_xori:beginop = `Xor; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {16'h0, inst[15:0]};end`Inst_addi:beginop = `Add; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {{16{inst[15]}}, inst[15:0]};end`Inst_subi:beginop = `Sub; regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {{16{inst[15]}}, inst[15:0]};end`Inst_lui:beginop = `Lui; regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = inst[20:16];imm = {inst[15:0],16'h0};end`Inst_r:case(func)`Inst_add:beginop = `Add; regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_or:beginop = `Or;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_sub:beginop = `Sub;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_and:beginop = `And;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_xor:beginop = `Xor;regaRead = `Valid;regbRead = `Valid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11];imm = `Zero;end`Inst_sll:beginop = `Sll;regaRead = `Invalid;regbRead = `Valid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = inst[20:16];regcAddr = inst[15:11];imm = {27'b0,inst[10:6]};end`Inst_srl:beginop = `Srl;regaRead = `Invalid;regbRead = `Valid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = inst[20:16];regcAddr = inst[15:11];imm = {27'b0,inst[10:6]};end`Inst_sra:beginop = `Sra;regaRead = `Invalid;regbRead = `Valid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = inst[20:16];regcAddr = inst[15:11];imm = {27'b0,inst[10:6]};end`Inst_jr:beginop = `Jr;regaRead = `Valid;//rsregbRead = `Invalid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = 5'b11111;jAddr = regaData;jCe = `Valid;imm = `Zero;end`Inst_jalr:beginop = `Jal;regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[15:11]; //jAddr = regaData;jCe = `Valid;imm = npc;end`Inst_slt:beginop = `Slt;regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = inst[15:11]; imm = `Zero;enddefault:beginregaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;imm = `Zero;endendcase//J`Inst_j:beginop = `J;regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;jAddr = {npc[31:28], inst[25:0], 2'b00};jCe = `Valid;imm = `Zero;end `Inst_jal:beginop = `Jal;regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = 5'b11111;jAddr = {npc[31:28], inst[25:0], 2'b00};jCe = `Valid;imm = npc;end//J `Inst_beq:beginop = `Beq;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;jAddr = npc+{{14{inst[15]}},inst[15:0],2'b00};jCe=(regaData==regbData)?`Valid:`Invalid; /* if(regaData==regbData)jCe = `Valid;elsejCe = `Invalid;*/imm = `Zero;end `Inst_bne:beginop = `Bne;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;jAddr = npc+{{14{inst[15]}},inst[15:0],2'b00};jCe=(regaData!=regbData)?`Valid:`Invalid; /* if(regaData!=regbData)jCe = `Valid;elsejCe = `Invalid;*/imm = `Zero;end `Inst_bgtz:beginop = `Bgtz;regaRead = `Valid;regbRead = `Valid;//regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;jAddr = npc+{{14{inst[15]}},inst[15:0],2'b00};jCe = (regaData[31]==0)?`Valid:`Invalid;imm = 32'b0; //end`Inst_bltz:beginop = `Bgtz;regaRead = `Valid;regbRead = `Valid;//regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;jAddr = npc+{{14{inst[15]}},inst[15:0],2'b00};jCe = (regaData[31]==1)?`Valid:`Invalid; //imm = 32'b0; //end`Inst_lw:beginop = `Lw;regaRead = `Valid;regbRead = `Invalid;regcWrite = `Valid;regaAddr = inst[25:21];regbAddr = `Zero;regcAddr = inst[20:16];imm = {{16{inst[15]}},inst[15:0]};end`Inst_sw:beginop = `Sw;regaRead = `Valid;regbRead = `Valid;regcWrite = `Invalid;regaAddr = inst[25:21];regbAddr = inst[20:16];regcAddr = `Zero;imm = {{16{inst[15]}},inst[15:0]};end default:beginop = `Nop; regaRead = `Invalid;regbRead = `Invalid;regcWrite = `Invalid;regaAddr = `Zero;regbAddr = `Zero;regcAddr = `Zero;imm = `Zero;endendcase end/*always@(*)if(rst == `RstEnable)regaData = `Zero;else if(regaRead == `Valid)regaData = regaData_i;else regaData = imm;always@(*)if(rst == `RstEnable)regbData = `Zero; else if(regbRead == `Valid)regbData = regbData_i;elseregbData = imm; */

always@(*) if(rst == `RstEnable) regaData = `Zero; else if(op == `Lw || op == `Sw) regaData = regaData_i + imm; else if(regaRead == `Valid) regaData = regaData_i; else regaData = imm; always@(*) if(rst == `RstEnable) regbData = `Zero; else if(regbRead == `Valid) regbData = regbData_i; else regbData = imm;endmodule`include "define.v";

module DataMem(input wire clk,input wire ce,input wire we,input wire [31:0] addr,input wire [31:0] wtData,output reg [31:0] rdData

);reg [31:0] datamem [1023 : 0];always@(*) if(ce == `RamDisable)rdData = `Zero;elserdData = datamem[addr[11 : 2]]; always@(posedge clk)if(ce == `RamEnable && we == `RamWrite)datamem[addr[11 : 2]] = wtData;else ;endmodule`define RstEnable 1'b1

`define RstDisable 1'b0

`define RomEnable 1'b1

`define RomDisable 1'b0

`define Zero 0

`define Valid 1'b1

`define Invalid 1'b0

//I

`define Inst_ori 6'b001101

`define Inst_addi 6'b001000

`define Inst_andi 6'b001100

`define Inst_xori 6'b001110

`define Inst_lui 6'b001111

`define Inst_subi 6'b001001//lw sw

`define Inst_lw 6'b100011

`define Inst_sw 6'b101011//beq bne

`define Inst_beq 6'b000100

`define Inst_bne 6'b000101//R

`define Inst_r 6'b000000

`define Inst_add 6'b100000

`define Inst_sub 6'b100010

`define Inst_and 6'b100100

`define Inst_or 6'b100101

`define Inst_xor 6'b100110

`define Inst_sll 6'b000000

`define Inst_srl 6'b000010

`define Inst_sra 6'b000011`define Inst_jr 6'b001000

//J

`define Inst_j 6'b000010

`define Inst_jal 6'b000011//12

`define Inst_slt 6'b101010

`define Inst_bgtz 6'b000111

`define Inst_bltz 6'b000001

`define Inst_jalr 6'b001001

`define Inst_mult 6'b011000

`define Inst_multu 6'b011001

`define Inst_div 6'b011010

`define Inst_divu 6'b011011

`define Inst_mfhi 6'b010000

`define Inst_mflo 6'b010010

`define Inst_mthi 6'b010001

`define Inst_mtlo 6'b010011//

`define Inst_ll 6'b110000

`define Inst_sc 6'b111000

`define Inst_mfc0 6'b000000

`define Inst_mtc0 6'b000000

`define Inst_eret 6'b011000

`define syscall 6'b001100`define Nop 6'b000000

`define Or 6'b000001

`define Add 6'b000010

`define And 6'b000011

`define Xor 6'b000100

`define Lui 6'b000101

`define Sub 6'b000110

`define Sll 6'b000111

`define Srl 6'b001000

`define Sra 6'b001001

`define J 6'b001010

`define Jal 6'b001011

`define Beq 6'b001100

`define Bne 6'b001101

`define Jr 6'b001110

`define Lw 6'b010000

`define Sw 6'b010001

`define Bgtz 6'b010010

`define Bltz 6'b010011

`define Slt 6'b010100//MEM

`define RamWrite 1'b1

`define RamUnWrite 1'b0

`define RamEnable 1'b1

`define RamDisable 1'b0`include "define.v"

module EX(input wire rst,//input wire [5:0] op,input wire [5:0] op_i, input wire [31:0] regaData,input wire [31:0] regbData,input wire regcWrite_i,input wire [4:0]regcAddr_i,output reg [31:0] regcData,output wire regcWrite,output wire [4:0] regcAddr,output wire [5:0] op,output wire [31:0] memAddr,output wire [31:0] memData

); assign op = op_i;assign memAddr = regaData;assign memData = regbData;always@(*)if(rst == `RstEnable)regcData = `Zero;elsebegin//case(op)case(op_i)`Or:regcData = regaData | regbData;`Add:regcData = regaData + regbData;`And:regcData = regaData & regbData;`Xor:regcData = regaData ^ regbData;`Lui:regcData = regaData;/*`Lui:regcData = regaData | regbData;*/`Sub:regcData = regaData - regbData;`Sll:regcData = regbData << regaData;`Srl:regcData = regbData >> regaData;`Sra:regcData = ($signed(regbData)) >>> regaData;`J:regcData = `Zero;`Jr:regcData = `Zero;`Jal:regcData = regbData;`Beq:regcData = `Zero;`Bne:regcData = `Zero;`Bltz:regcData = `Zero;`Bgtz:regcData = `Zero;`Slt:regcData = ($signed(regaData)<$signed(regbData))?1'b1:1'b0;default:regcData = `Zero;endcaseendassign regcWrite = regcWrite_i;assign regcAddr = regcAddr_i;

endmodule

`include "define.v"

module IF(input wire clk,input wire rst,input wire [31:0] jAddr,//Jinput wire jCe,//Joutput reg ce,

output reg [31:0] pc

);always@(*)if(rst == `RstEnable)ce = `RomDisable;elsece = `RomEnable;

/* always@(posedge clk)if(ce == `RomDisable)pc = `Zero;elsepc = pc + 4;

*/always@(posedge clk)if(ce == `RomDisable)pc = `Zero;else if(jCe == `Valid)//Jpc = jAddr;elsepc = pc + 4;

endmodule`include "define.v"

module InstMem(input wire ce,input wire [31:0] addr,output reg [31:0] data

);reg [31:0] instmem [1023 : 0]; always@(*) if(ce == `RomDisable)data = `Zero;elsedata = instmem[addr[11 : 2]]; initialbegininstmem [0] = 32'h34011100; //ori r1,r0,1100h r1--32'h0000 1100instmem [1] = 32'h34020020; //ori r2,r0,0020h r2--32'h0000 0020instmem [2] = 32'h3403ff00; //ori r3,r0,ff00h r3--32'h0000 ff00instmem [3] = 32'h3404ffff; //ori r4,r0,ffffh r4--32'h0000 ffffinstmem [4] = 32'h2005ffff; //addi r5,r0,ffff r5--32'hffff ffffinstmem [5] =32'b000000_00101_00100_00110_00000_101010; //slt r6,r5,r4instmem [6] =32'b000000_00100_00011_00110_00000_101010; //slt r6,r4,r3end

endmodule

`include "define.v";

module MEM(input wire rst, input wire [5:0] op,input wire [31:0] regcData,input wire [4:0] regcAddr,input wire regcWr,input wire [31:0] memAddr_i,input wire [31:0] memData, input wire [31:0] rdData,output wire [4:0] regAddr,output wire regWr,output wire [31:0] regData, output wire [31:0] memAddr,output reg [31:0] wtData,output reg memWr, output reg memCe

);assign regAddr = regcAddr; assign regWr = regcWr; assign regData = (op == `Lw) ? rdData : regcData; assign memAddr = memAddr_i;always @(*) if(rst == `RstEnable) begin wtData = `Zero; memWr = `RamUnWrite; memCe = `RamDisable; end elsecase(op) `Lw: begin wtData = `Zero; memWr = `RamUnWrite; memCe = `RamEnable; end `Sw: begin wtData = memData; memWr = `RamWrite; memCe = `RamEnable; enddefault: begin wtData = `Zero; memWr = `RamUnWrite; memCe = `RamDisable; end endcase

endmodule`include "define.v";

module MIPS(input wire clk,input wire rst,input wire [31:0] instruction,input wire [31:0] rdData,//lsoutput wire romCe,output wire [31:0] instAddr,output wire [31:0] wtData,//lsoutput wire [31:0] memAddr,//lsoutput wire memCe,//lsoutput wire memWr//ls

);wire [31:0] regaData_regFile, regbData_regFile;wire [31:0] regaData_id, regbData_id; wire [31:0] regcData_ex;//wire [5:0] op; wire [5:0] op_id; //ls wire regaRead, regbRead;wire [4:0] regaAddr, regbAddr;wire regcWrite_id, regcWrite_ex;wire [4:0] regcAddr_id, regcAddr_ex;//Jwire [31:0] jAddr;wire jCe;//lswire [5:0] op_ex;wire[31:0] memAddr_ex,memData_ex;wire [5:0] regAddr_mem;wire [31:0] regData_mem;wire regWr_mem;IF if0(.clk(clk),.rst(rst),.jAddr(jAddr),//J.jCe(jCe),//J.ce(romCe), .pc(instAddr));ID id0(.rst(rst), .pc(instAddr),//J.inst(instruction),.regaData_i(regaData_regFile),.regbData_i(regbData_regFile),//.op(op),.op(op_id),//ls.regaData(regaData_id),.regbData(regbData_id),.regaRead(regaRead),.regbRead(regbRead),.regaAddr(regaAddr),.regbAddr(regbAddr),.regcWrite(regcWrite_id),.regcAddr(regcAddr_id),.jAddr(jAddr),//J.jCe(jCe)//J);EX ex0(.rst(rst),//.op(op), .op_i(op_id), .regaData(regaData_id),.regbData(regbData_id),.regcWrite_i(regcWrite_id),.regcAddr_i(regcAddr_id),.regcData(regcData_ex),.regcWrite(regcWrite_ex),.regcAddr(regcAddr_ex),.op(op_ex),//ls.memAddr(memAddr_ex),//ls.memData(memData_ex)//ls); MEM mem0(.rst(rst), .op(op_ex),.regcData(regcData_ex),.regcAddr(regcAddr_ex),.regcWr(regcWrite_ex),.memAddr_i(memAddr_ex),.memData(memData_ex), .rdData(rdData),.regAddr(regAddr_mem),.regWr(regWr_mem),.regData(regData_mem), .memAddr(memAddr),.wtData(wtData),.memWr(memWr), .memCe(memCe));RegFile regfile0(.clk(clk),.rst(rst),//.we(regcWrite_ex),.we(regWr_mem),//.waddr(regcAddr_ex),.waddr(regAddr_mem),//.wdata(regcData_ex),.wdata(regData_mem),.regaRead(regaRead),.regbRead(regbRead),.regaAddr(regaAddr),.regbAddr(regbAddr),.regaData(regaData_regFile),.regbData(regbData_regFile));endmodule

`include "define.v"

module RegFile(input wire clk,input wire rst,input wire we,input wire [4:0] waddr,input wire [31:0] wdata,input wire regaRead,input wire regbRead,input wire [4:0] regaAddr,input wire [4:0] regbAddr,output reg [31:0] regaData,output reg [31:0] regbData

);reg [31:0] reg32 [31 : 0]; always@(*)if(rst == `RstEnable)regaData = `Zero;else if(regaAddr == `Zero)regaData = `Zero;elseregaData = reg32[regaAddr];always@(*)if(rst == `RstEnable) regbData = `Zero;else if(regbAddr == `Zero)regbData = `Zero;elseregbData = reg32[regbAddr];always@(posedge clk)if(rst != `RstEnable)if((we == `Valid) && (waddr != `Zero))reg32[waddr] = wdata;else ;

endmodule

module SoC(input wire clk,input wire rst

);wire [31:0] instAddr;wire [31:0] instruction;wire romCe;//lswire memCe, memWr; wire [31:0] memAddr;wire [31:0] rdData;wire [31:0] wtData;MIPS mips0(.clk(clk),.rst(rst),.instruction(instruction),.instAddr(instAddr),.romCe(romCe),.rdData(rdData), .wtData(wtData), .memAddr(memAddr), .memCe(memCe), .memWr(memWr) ); InstMem instrom0(.ce(romCe),.addr(instAddr),.data(instruction));//DataMemDataMem datamem0( .ce(memCe), .clk(clk), .we(memWr), .addr(memAddr), .wtData(wtData), .rdData(rdData) );

endmodule

`include "define.v"

module soc_tb;reg clk;reg rst;initialbeginclk = 0;rst = `RstEnable;#100rst = `RstDisable;#10000 $stop; endalways #10 clk = ~ clk;SoC soc0(.clk(clk), .rst(rst));

endmodule

相关文章:

【FPGA】 MIPS 12条整数指令【2】

目录 仿真 代码 完整代码 实现slt 仿真 ori r1,r0,1100h ori r2,r0,0020h ori r3,r0,ff00h ori r4,r0,ffffh addi r5,r0,ffff slt r6,r5,r4 slt r6,r4,r3 代码 EX Slt:regcData ($signed(regaData)<$signed(regbData))?1b1:1b0; ID Inst_slt:be…...

机器学习--python基础库之Matplotlib (2) 简单易懂!!!

python基础库之Matplotlib(2) python基础库之Matplotlib0 准备1 散点图的绘制2 柱状图绘制3 其他 python基础库之Matplotlib 上篇文章机器学习–python基础库之Matplotlib (1) 超级详细!!!主要讲解了python的基础库matplotlib中绘图的流程以及折线图的…...

mybatis plus 持久化使用技巧及场景

mybatis plus提供了很多强大的持久化工具,新手容易对这些工具使用困难,下面我总结了一下mybatis plus持久化的使用技巧及使用场景。 一、持久化 官方文档:https://baomidou.com/guides/data-interface/ (一)通过ser…...

JVM监控和管理工具

基础故障处理工具 jps jps(JVM Process Status Tool):Java虚拟机进程状态工具 功能 1:列出正在运行的虚拟机进程 2:显示虚拟机执行主类(main()方法所在的类) 3:显示进程ID(PID,Process Identifier) 命令格式 jps […...

记录 | 基于MaxKB的文字生成视频

目录 前言一、安装SDK二、创建视频函数库三、调试更新时间 前言 参考文章:如何利用智谱全模态免费模型,生成大家都喜欢的图、文、视并茂的文章! 自己的感想 本文记录了创建文字生成视频的函数库的过程。如果想复现本文,需要你逐一…...

生成式AI安全最佳实践 - 抵御OWASP Top 10攻击 (下)

今天小李哥将开启全新的技术分享系列,为大家介绍生成式AI的安全解决方案设计方法和最佳实践。近年来生成式 AI 安全市场正迅速发展。据IDC预测,到2025年全球 AI 安全解决方案市场规模将突破200亿美元,年复合增长率超过30%,而Gartn…...

现场流不稳定,EasyCVR视频融合平台如何解决RTSP拉流不能播放的问题?

视频汇聚EasyCVR安防监控视频系统采用先进的网络传输技术,支持高清视频的接入和传输,能够满足大规模、高并发的远程监控需求。平台灵活性强,支持国标GB/T 28181协议、部标JT808、GA/T 1400协议、RTMP、RTSP/Onvif协议、海康Ehome、海康SDK、大…...

文献阅读 250205-Global patterns and drivers of tropical aboveground carbon changes

Global patterns and drivers of tropical aboveground carbon changes 来自 <Global patterns and drivers of tropical aboveground carbon changes | Nature Climate Change> 热带地上碳变化的全球模式和驱动因素 ## Abstract: Tropical terrestrial ecosystems play …...

算法与数据结构(括号匹配问题)

思路 从题干可以看出,只要给出的括号对应关系正确,那么就可以返回true,否则返回false。这个题可以使用栈来解决 解题过程 首先从第一个字符开始遍历,如果是括号的左边(‘(‘,’[‘,’}‘&…...

订单状态监控实战:基于 SQL 的状态机分析与异常检测

目录 1. 背景与问题 2. 数据准备 2.1 表结构设计 3. 场景分析与实现 3.1 场景 1:检测非法状态转换...

C# 中记录(Record)详解

从C#9.0开始,我们有了一个有趣的语法糖:记录(record) 为什么提供记录? 开发过程中,我们往往会创建一些简单的实体,它们仅仅拥有一些简单的属性,可能还有几个简单的方法,比如DTO等等…...

YOLOv11-ultralytics-8.3.67部分代码阅读笔记-autobackend.py

autobackend.py ultralytics\nn\autobackend.py 目录 autobackend.py 1.所需的库和模块 2.def check_class_names(names): 3.def default_class_names(dataNone): 4.class AutoBackend(nn.Module): 1.所需的库和模块 # Ultralytics 🚀 AGPL-3.0 License …...

Docker使用指南(一)——镜像相关操作详解(实战案例教学,适合小白跟学)

目录 1.镜像名的组成 2.镜像操作相关命令 镜像常用命令总结: 1. docker images 2. docker rmi 3. docker pull 4. docker push 5. docker save 6. docker load 7. docker tag 8. docker build 9. docker history 10. docker inspect 11. docker prune…...

Rust 变量特性:不可变、和常量的区别、 Shadowing

Rust 变量特性:不可变、和常量的区别、 Shadowing Rust 是一门以安全性和性能著称的系统编程语言,其变量系统设计独特且强大。本文将从三个角度介绍 Rust 变量的核心特性:可变性(Mutability)、变量与常量的区别&#…...

NFT Insider #167:Champions Tactics 角色加入 The Sandbox;AI 助力 Ronin 游戏生态

引言:NFT Insider 由 NFT 收藏组织 WHALE Members、BeepCrypto 联合出品, 浓缩每周 NFT 新闻,为大家带来关于 NFT 最全面、最新鲜、最有价值的讯息。每期周报将从 NFT 市场数据,艺术新闻类,游戏新闻类,虚拟…...

鹧鸪云无人机光伏运维解决方案

在新能源产业蓬勃发展的当下,光伏电站作为清洁能源供应的关键一环,其稳定运行和高效运维至关重要。随着光伏电站规模持续扩大,数量不断增加,传统人工巡检方式的弊端日益显著。人工巡检不仅效率低、人力和时间成本高,而…...

NeuralCF 模型:神经网络协同过滤模型

实验和完整代码 完整代码实现和jupyter运行:https://github.com/Myolive-Lin/RecSys--deep-learning-recommendation-system/tree/main 引言 NeuralCF 模型由新加坡国立大学研究人员于 2017 年提出,其核心思想在于将传统协同过滤方法与深度学习技术相结…...

【前端】【Ts】【知识点总结】TypeScript知识总结

一、总体概述 TypeScript 是 JavaScript 的超集,主要通过静态类型检查和丰富的类型系统来提高代码的健壮性和可维护性。它涵盖了从基础数据类型到高级类型、从函数与对象的类型定义到类、接口、泛型、模块化及装饰器等众多知识点。掌握这些内容有助于编写更清晰、结…...

JAVA架构师进阶之路

JAVA架构师进阶之路 前言 苦于网络上充斥的各种java知识,多半是互相抄袭,导致很多后来者在学习java知识中味同嚼蜡,本人闲暇之余整理了进阶成为java架构师所必须掌握的核心知识点,后续会不断扩充。 废话少说,直接上正…...

掌握@PostConstruct与@PreDestroy,优化Spring Bean的初始化和销毁

在Spring中,PostConstruct和PreDestroy注解就像是对象的“入职”和“离职”仪式。 1. PostConstruct注解:这个注解标记的方法就像是员工入职后的“岗前培训”。当一个对象(比如一个Bean)被Spring容器创建并注入依赖后,…...

(LeetCode 每日一题) 3442. 奇偶频次间的最大差值 I (哈希、字符串)

题目:3442. 奇偶频次间的最大差值 I 思路 :哈希,时间复杂度0(n)。 用哈希表来记录每个字符串中字符的分布情况,哈希表这里用数组即可实现。 C版本: class Solution { public:int maxDifference(string s) {int a[26]…...

大数据零基础学习day1之环境准备和大数据初步理解

学习大数据会使用到多台Linux服务器。 一、环境准备 1、VMware 基于VMware构建Linux虚拟机 是大数据从业者或者IT从业者的必备技能之一也是成本低廉的方案 所以VMware虚拟机方案是必须要学习的。 (1)设置网关 打开VMware虚拟机,点击编辑…...

全球首个30米分辨率湿地数据集(2000—2022)

数据简介 今天我们分享的数据是全球30米分辨率湿地数据集,包含8种湿地亚类,该数据以0.5X0.5的瓦片存储,我们整理了所有属于中国的瓦片名称与其对应省份,方便大家研究使用。 该数据集作为全球首个30米分辨率、覆盖2000–2022年时间…...

k8s业务程序联调工具-KtConnect

概述 原理 工具作用是建立了一个从本地到集群的单向VPN,根据VPN原理,打通两个内网必然需要借助一个公共中继节点,ktconnect工具巧妙的利用k8s原生的portforward能力,简化了建立连接的过程,apiserver间接起到了中继节…...

自用)

css3笔记 (1) 自用

outline: none 用于移除元素获得焦点时默认的轮廓线 broder:0 用于移除边框 font-size:0 用于设置字体不显示 list-style: none 消除<li> 标签默认样式 margin: xx auto 版心居中 width:100% 通栏 vertical-align 作用于行内元素 / 表格单元格ÿ…...

代理篇12|深入理解 Vite中的Proxy接口代理配置

在前端开发中,常常会遇到 跨域请求接口 的情况。为了解决这个问题,Vite 和 Webpack 都提供了 proxy 代理功能,用于将本地开发请求转发到后端服务器。 什么是代理(proxy)? 代理是在开发过程中,前端项目通过开发服务器,将指定的请求“转发”到真实的后端服务器,从而绕…...

【Java学习笔记】BigInteger 和 BigDecimal 类

BigInteger 和 BigDecimal 类 二者共有的常见方法 方法功能add加subtract减multiply乘divide除 注意点:传参类型必须是类对象 一、BigInteger 1. 作用:适合保存比较大的整型数 2. 使用说明 创建BigInteger对象 传入字符串 3. 代码示例 import j…...

springboot整合VUE之在线教育管理系统简介

可以学习到的技能 学会常用技术栈的使用 独立开发项目 学会前端的开发流程 学会后端的开发流程 学会数据库的设计 学会前后端接口调用方式 学会多模块之间的关联 学会数据的处理 适用人群 在校学生,小白用户,想学习知识的 有点基础,想要通过项…...

使用Spring AI和MCP协议构建图片搜索服务

目录 使用Spring AI和MCP协议构建图片搜索服务 引言 技术栈概览 项目架构设计 架构图 服务端开发 1. 创建Spring Boot项目 2. 实现图片搜索工具 3. 配置传输模式 Stdio模式(本地调用) SSE模式(远程调用) 4. 注册工具提…...

JavaScript基础-API 和 Web API

在学习JavaScript的过程中,理解API(应用程序接口)和Web API的概念及其应用是非常重要的。这些工具极大地扩展了JavaScript的功能,使得开发者能够创建出功能丰富、交互性强的Web应用程序。本文将深入探讨JavaScript中的API与Web AP…...